Fluid Core (A Reconfigurable Pipelined RISC processor)

Project maintainers

Details

Created: Jul 25, 2015

Updated: Jul 27, 2015

SVN Updated: Jul 27, 2015

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:Verilog

Development status:Alpha

Additional info:Design done, Specification done

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

Fluid Core is a soft core processor aimed at being heavily parameterized in order to support reconfiguration. It has a scalable datapath width i.e. the internal ALU and shifter unit can be configured to be either 8, 16 or any number of bits. It is a Pipelined core with Harvard Architecture and Load/Store interface. It has fixed instruction width of 2 bytes, but can be extended.

It supports "Dynamic" reconfiguration.

Dynamic Reconfiguration

Dynamic Reconfiguration refers to the ability of the Processor to update its internal Instruction Decode and Execute stage in order to support new functions, on the fly, while the system is running. This is achieved using two crucial design choices.

First, in the Execute stage, instructions are issued to appropriate functional units by broadcasting its unique identifier on a common bus. The corresponding module, then, reads the data from the data buses and outputs the result on the result bus. Other un-used modules tristate themselves.

Second, in the Decode stage, instructions are decoded by passing specific fields of the instruction as address to the Micro-Op memory. This memory holds microoperations. Each micro-operation has specific bits that correspond to various control signals. For instance, some bits of the microoperation correspond to the Module identifiers that are to be activated in the Ex stage. By changing these bits, the module to be activated can be changed.

Collectively, both these features can be used in the following scenario: A processor is to be deployed in a scenario in which it will be used in two applications (time multiplexed). One application emphasizes use of special function ALU for acceleration. Another application doesn't. A Fluid Core can be deployed in such a scenario with its execute stage containing the accelerator and the generic ALU. But, the internal micro-op memory may only contain references to the generic ALU. When the processor is going to switch applications, a program can instruct the processor to update its micro-op memory to replace the generic ALU reference with the accelerator. Then, the processor can continue to execute the program.

The advantages are:

1. Instruction Width can be conserved, the processor can support 64 functions in all but be able to refer to only 16 at a time. This way 2 bits are conserved.

2. Closely coupled EX stage eliminates need for Co-processor oriented design. This eases the heavy burden of complex embedded design.

Future Work:

The ultimate aim is to adapt the project and extend it to exploit Partial Reconfiguration supported by many FPGA vendors.

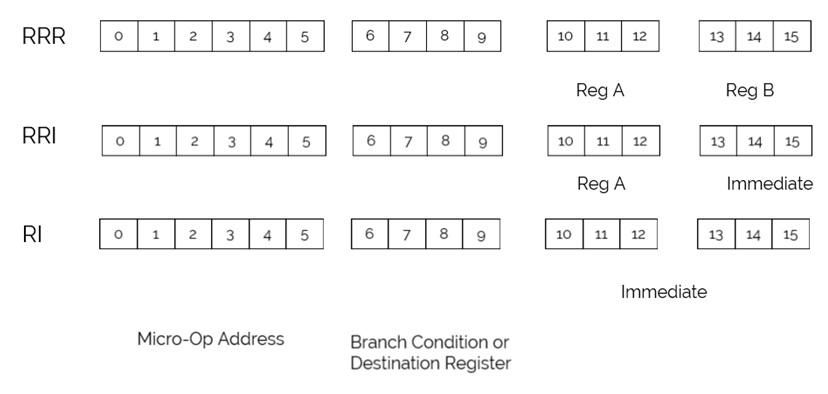

ISA Format

Its a Load/Store Architecture with 3 instruction types. Micro-Op Address field is used to address the Micro-Op Memory in the decode stage and retrieve the Microoperations.

Statistics

Max Frequency @ Spartan 3E starter kit - 135 Mhz

LUTs - 1800+