## CFFT A new radix 4 complex fft processor

## 1. Description

CFFT is a radix-4 fast Fourier transform (FFT) core with configurable data width and a configurable number of sample points in the FFT.

Twiddle factors are implemented using the CORDIC algorithm, causing the gain of the CFFT core to be different from the standard FFT algorithm. This variation in gain is not important for orthogonal frequency division modulation (OFDM) and demodulation. The gain can be corrected, to that of a conventional FFT, by applying a constant multiplying factor.

The input of FFT core is ordered by radix 4 and the output is reverse ordered.

2. Theory of operation

FFT algorithm is described in detail in many text books. We'll just skip it here.

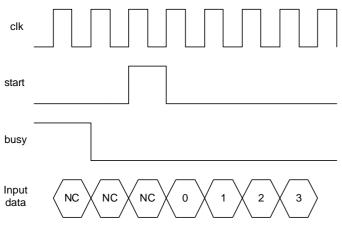

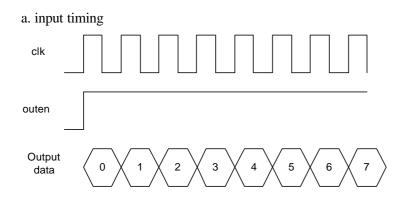

- Rotation Truncation After rotation data Cordic -Input – Selector factor and round generator Write Data -Output-Dual Port select Ram Write Address Read 4 Point Factor start Data FFT Read Address Cfft4 Address -start-Generator busy Outen Address.vhd

- 3. Block diagram

# b. output timing

#### 5. Misc

a. Gain

| Points | Standard FFT | CFFT   | Standard IFFT | CFFT(inverse) |

|--------|--------------|--------|---------------|---------------|

| 256    | 1            | 0.0698 | 1/256         | 17.9          |

| 1024   | 1            | 0.0287 | 1/1024        | 29.4          |

| 4096   | 1            | 0.0118 | 1/4096        | 48.2742       |

|        |              |        |               |               |

The result is obtained by comparison between Matlab simulation and circuit simulation.

# b. Output Order

The output sequence is 2bit reverse ordered. For example, the 789<sup>th</sup> (1100010101) output in an 1024-point FFT is actually at 339 (0101010011).

# c. Synthesis

This core can be synthesized using Synplify70. It can be placed and routed using Xilinx ISE4.1. A 1024 point FFT, with a 12 bit I/Q input can be fitted into an XCV50E-6 and runs at a clock speed of 90MHz.