# **UART IP Core Specification**

Author: Jacob Gorban jacob.gorban@flextronicssemi.com

Rev. 0.1 April 20, 2001

i

## Revision History

| Rev. | Date | Author       | Description |

|------|------|--------------|-------------|

| 0.1  |      | Jacob Gorban | First Draft |

|      |      |              |             |

|      |      |              |             |

|      |      |              |             |

# **Contents**

| Introduction | <br>1  |

|--------------|--------|

| IO ports     | <br>2  |

| Clocks       | <br>3  |

| Registers    | <br>4  |

| Operation    | <br>12 |

| Architecture | 13     |

# Introduction

The UART (Universal Asynchronous Receiver/Transmitter) core provides serial communication capabilities, which allow communication with modem or other external devices, like another computer using a serial cable and RS232 protocol. This core is designed to be maximally compatible with the industry standard National Semiconductors' 16550A device.

#### **Features:**

- WISHBONE interface

- FIFO only operation

- Register level and functionality compatibility with NS16550A (but not 16450).

- A 32-bit Divisor Latch register to support high speed of chip clock.

# **IO** ports

#### 2.1 WISHBONE interface signals

| Port  | Width | Direction | Description                   |

|-------|-------|-----------|-------------------------------|

| CLK_I | 1     | Input     | Block's clock input           |

| RST_I | 1     | Input     | Synchronous Reset             |

| ADR_I | 3     | Input     | Used for register selection   |

| DAT_I | 8     | Input     | Data input                    |

| DAT_O | 8     | Output    | Data output                   |

| WE_I  | 1     | Input     | Write or read cycle selection |

| STB_I | 1     | Input     | Specifies transfer cycle      |

| CYC_I | 1     | Input     | A bus cycle is in progress    |

| ACK_O | 1     | Output    | Acknowledge of a transfer     |

| INT_O | 1     | Output    | Interrupt output              |

<u>Note</u>: [INT\_O] signal is not defined in the standard WISHBONE documentation. It is intended for the interrupt controller on the chip.

#### 2.2 External connections

| Port  | Width | Direction | Description              |

|-------|-------|-----------|--------------------------|

| STX_O | 1     | Output    | The serial output signal |

| SRX_I | 1     | Input     | The serial input signal  |

| RTS_O | 1     | Output    | Request To Send          |

| DTR_O | 1     | Output    | Data Terminal Ready      |

| CTS_I | 1     | Input     | Clear To Send            |

| DSR_I | 1     | Input     | Data Set Ready           |

| RI_I  | 1     | Input     | Ring Indicator           |

| DCD_I | 1     | Input     | Data Carrier Detect      |

# Clocks

#### Clocks table:

| Name   | Source | Rates (MHz) |     | Hz)   | Remarks | Description    |

|--------|--------|-------------|-----|-------|---------|----------------|

|        |        | Max         | Min | Resol |         |                |

|        |        |             |     | ution |         |                |

| clk_wb | Wishbo | ??          | ??  | ??    | ??      | Wishbone clock |

|        | ne bus |             |     |       |         |                |

# Registers

#### 4.1 Registers list

| Name                            | Address | Width | Access | Description               |

|---------------------------------|---------|-------|--------|---------------------------|

| Receiver Buffer                 | 0       | 8     | R      | Receiver FIFO output      |

| Transmitter Holding             | 0       | 8     | W      | Transmit FIFO input       |

| Register (THR)                  |         |       |        |                           |

| Interrupt Enable                | 1       | 8     | RW     | Enable/Mask interrupts    |

|                                 |         |       |        | generated by the UART     |

| <b>Interrupt Identification</b> | 2       | 8     | R      | Get interrupt information |

| FIFO Control                    | 2       | 8     | W      | Control FIFO options      |

| <u>Line Control Register</u>    | 3       | 8     | RW     | Control connection        |

| Modem Control                   | 4       | 8     | W      | Controls modem            |

| <u>Line Status</u>              | 5       | 8     | R      | Status information        |

| Modem Status                    | 6       | 8     | R      | Modem Status              |

In addition, there are 4 Clock Divisor registers that together form one 32-bit register (as opposed to the 2 8-bit registers in the 16550). The expansion is to accommodate higher clock speed of modern systems, especially since this is not a stand-alone chip but a SoC core.

The registers can be accessed when the 7<sup>th</sup> (DLAB) bit of the Line Control Register is set to '1'. At this time the above registers at addresses 0-3 can't be accessed.

| Name                              | Address | Width | Access | Description            |

|-----------------------------------|---------|-------|--------|------------------------|

| <u>Divisor Latch</u> Byte 1 (LSB) | 0       | 8     | RW     | The LSB of the divisor |

|                                   |         |       |        | latch                  |

| Divisor Latch Byte 2              | 1       | 8     | RW     | Second byte of DL      |

| Divisor Latch Byte 3              | 4       | 8     | RW     | Third byte of DL       |

| Divisor Latch Byte 4 (MSB)        | 5       | 8     | RW     | The MSB of the divisor |

|                                   |         |       |        | latch                  |

## **4.2 Interrupt Enable Register (IER)**

This register allows enabling and disabling interrupt generation by the UART.

| Bit# | Access | Description                                  |

|------|--------|----------------------------------------------|

| 0    | RW     | Received Data available interrupt            |

|      |        | '0' – disabled                               |

|      |        | '1' – enabled                                |

| 1    | RW     | Transmitter Holding Register empty interrupt |

|      |        | '0' – disabled                               |

|      |        | '1' – enabled                                |

| 2    | RW     | Receiver Line Status Interrupt               |

|      |        | '0' – disabled                               |

|      |        | '1' – enabled                                |

| 3    | RW     | Modem Status Interrupt                       |

|      |        | '0' – disabled                               |

|      |        | '1' – enabled                                |

| 7-4  | RW     | Reserved. Should be logic '0'.               |

Reset Value: 0000h

#### 4.3 Interrupt Identification Register (IIR)

The IIR enables the programmer to retrieve what is the current highest priority pending interrupt.

**Bit 0** indicates that an interrupt is pending when it's logic '0'. When it's '1' – no interrupt is pending.

The following table displays the list of possible interrupts along with the bits they enable, priority, and their source and reset control.

| Bit 3 | Bit 2 | Bit 1 | Priority        | Interrupt<br>Type                  | Interrupt Source                                                                                                                | Interrupt Reset<br>Control                                               |

|-------|-------|-------|-----------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| 0     | 1     | 1     | 1 <sup>st</sup> | Receiver Line<br>Status            | Parity, Overrun or Framing errors or Break Interrupt                                                                            | Reading the Line<br>Status Register                                      |

| 0     | 1     | 0     | 2 <sup>nd</sup> | Receiver Data available            | FIFO trigger level reached                                                                                                      | FIFO drops below trigger level                                           |

| 1     | 1     | 0     | 2 <sup>nd</sup> | Timeout<br>Indication              | There's at least 1 character in the FIFO but no character has been input to the FIFO or read from it for the last 4 Char times. | Reading from the<br>FIFO (Receiver<br>Buffer Register)                   |

| 0     | 0     | 1     | 3 <sup>rd</sup> | Transmitter Holding Register empty | Transmitter Holding<br>Register Empty                                                                                           | Writing to the<br>Transmitter Holding<br>Register or reading the<br>IIR. |

| 0     | 0     | 0     | 4 <sup>th</sup> | Modem Status                       | CTS, DSR, RI or DCD.                                                                                                            | Reading the Modem status register.                                       |

Bits 4 and 5: Logic '0'.

Bits 6 and 7: Logic '1' for compatibility reason.

## 4.4 FIFO Control Register (FCR)

The FCR allows selection of the FIFO trigger level (the number of bytes in FIFO required to enable the Received Data Available interrupt). In addition, the FIFOs can be cleared using this register.

| Bit# | Access | Description                                                           |

|------|--------|-----------------------------------------------------------------------|

| 0    | W      | Ignored (Used to enable FIFOs in NS16550D). Since this UART           |

|      |        | only supports FIFO mode, this bit is ignored.                         |

| 1    | W      | Writing a '1' to bit 1 clears the Receiver FIFO and resets its logic. |

|      |        | But it doesn't clear the shift register.                              |

| 2    | W      | Writing a '1' to bit 2 clears the Transmitter FIFO and resets its     |

|      |        | logic. The shift register is not cleared.                             |

| 5-3  | W      | Ignored                                                               |

| 7-6  | W      | Define the Receiver FIFO Interrupt trigger level                      |

|      |        | '00' – 1 byte                                                         |

|      |        | '01' – 4 bytes                                                        |

|      |        | '10' – 8 bytes                                                        |

|      |        | '11' – 14 bytes                                                       |

### 4.5 Line Control Register (LCR)

The line control register allows the specification of the format of the asynchronous data communication used. A bit in the register also allows access to the Divisor Latches, which define the baud rate. Reading from the register is allowed to check the current settings of the communication.

| Bit # | Access | Description                                                         |

|-------|--------|---------------------------------------------------------------------|

| 1-0   | RW     | Select number of bits in each character                             |

|       |        | '00' – 5 bits                                                       |

|       |        | '01' – 6 bits                                                       |

|       |        | '10' – 7 bits                                                       |

|       |        | '11' – 8 bits                                                       |

| 2     | RW     | Specify the number of generated stop bits                           |

|       |        | '0' − 1 stop bit                                                    |

|       |        | 1' - 1.5 stop bits when 5-bit character length selected and         |

|       |        | 2 bits otherwise                                                    |

|       |        | Note that the receiver always checks the first stop bit only.       |

| 3     | RW     | Parity Enable                                                       |

|       |        | '0' – No parity                                                     |

|       |        | '1' – Parity bit is generated on each outgoing character and        |

|       |        | is checked on each incoming one.                                    |

| 4     | RW     | Even Parity select                                                  |

|       |        | '0' – Odd number of '1' is transmitted and checked in each          |

|       |        | word (data and parity combined). In other words, if the data has an |

|       |        | even number of '1' in it, then the parity bit is '1'.               |

|       |        | '1' – Even number of '1' is transmitted in each word.               |

| 5     | RW     | Stick Parity bit.                                                   |

|       |        | '0' – Stick Parity disabled                                         |

|       |        | '1' - If bits 3 and 4 are logic '1', the parity bit is transmitted  |

|       |        | and checked as logic '0'. If bit 3 is '1' and bit 4 is '0' then the |

|       |        | parity bit is transmitted and checked as '1'.                       |

| 6     | RW     | Break Control bit                                                   |

|       |        | '1' – the serial out is forced into logic '0' (break state).        |

|       |        | '0' – break is disabled                                             |

| 7     | RW     | Divisor Latch Access bit.                                           |

|       |        | '1' – The divisor latches can be accessed                           |

|       |        | '0' – The normal registers are accessed                             |

## 4.6 Modem Control Register (MCR)

The modem control register allows transferring control signals to a modem connected to the UART.

| Bit # | Access | Description                                                            |

|-------|--------|------------------------------------------------------------------------|

| 0     | W      | Data Terminal Ready (DTR) signal control                               |

|       |        | '0' – DTR is '1'                                                       |

|       |        | '1' – DTR is '0'                                                       |

| 1     | W      | Request To Send (RTS) signal control                                   |

|       |        | '0' – RTS is '1'                                                       |

|       |        | '1' – RTS is '0'                                                       |

| 2     | W      | Out1. In loopback mode, connected Ring Indicator (RI) signal input     |

| 3     | W      | Out2. In loopback mode, connected to Data Carrier Detect (DCD)         |

|       |        | input.                                                                 |

| 4     | W      | Loopback mode                                                          |

|       |        | '0' – normal operation                                                 |

|       |        | '1' – loopback mode. When in loopback mode, the Serial                 |

|       |        | Output Signal (STX_O) is set to logic '1'. The signal of the           |

|       |        | transmitter shift register is internally connected to the input of the |

|       |        | receiver shift register.                                               |

|       |        | The following connections are made:                                    |

|       |        | DTR → DSR                                                              |

|       |        | RTS → CTS                                                              |

|       |        | Out1 → RI                                                              |

|       |        | Out2 → DCD                                                             |

|       |        |                                                                        |

| 7-5   | W      | Ignored                                                                |

## 4.7 Line Status Register (LSR)

| Bit # | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | R      | Data Ready (DR) indicator.  '0' – No characters in the FIFO  '1' – At least one character has been received and is in the                                                                                                                                                                                                                                                                                                                                                                     |

| 1     | R      | Overrun Error (OE) indicator  '1' – If the FIFO is full and another character has been received in the receiver shift register. If another character is starting to arrive, it will overwrite the data in the shift register but the FIFO will remain intact. The bit is cleared upon reading from the register. Generates Receiver Line Status interrupt.                                                                                                                                    |

| 2     | R      | '0' – No overrun state  Parity Error (PE) indicator  '1' – The character that is currently at the top of the FIFO has been received with parity error. The bit is cleared upon reading from the register. Generates Receiver Line Status interrupt.  '0' – No parity error in the current character                                                                                                                                                                                           |

| 3     | R      | Framing Error (FE) indicator  '1' – The received character at the top of the FIFO did not have a valid stop bit. The UART core tries re-synchronizing by assuming that the bit received was a start bit. Of course, generally, it might be that all the following data is corrupt. The bit is cleared upon reading from the register. Generates Receiver Line Status interrupt.  '0' – No framing error in the current character                                                              |

| 4     | R      | Break Interrupt (BI) indicator  '1' – A break condition has been reached in the current character. The break occurs when the line is held in logic 0 for a time of one character (start bit + data + parity + stop bit). In that case, one zero character enters the FIFO and the UART waits for a valid start bit to receive next character. The bit is cleared upon reading from the register. Generates Receiver Line Status interrupt.  '0' – No break condition in the current character |

| 5     | R      | Transmit FIFO is empty.  '1' – The transmitter FIFO is empty. Generates Transmitter Holding Register Empty interrupt. The bit is cleared in the following cases: The LSR has been read, the IIR has been read or data has been written to the transmitter FIFO.  '0' – Otherwise                                                                                                                                                                                                              |

| 6     | R      | Transmitter Empty indicator.  '1' – Both the transmitter FIFO and transmitter shift register are empty. The bit is cleared upon reading from the register or upon writing data to the transmit FIFO.                                                                                                                                                                                                                                                                                          |

| Bit # | Access | Description                                                        |

|-------|--------|--------------------------------------------------------------------|

|       |        | '0' – Otherwise                                                    |

| 7     | R      | '1' – At least one parity error, framing error or break            |

|       |        | indications have been received and are inside the FIFO. The bit is |

|       |        | cleared upon reading from the register.                            |

|       |        | '0' – Otherwise.                                                   |

#### 4.8 Modem Status Register (MSR)

The register displays the current state of the modem control lines. Also, four bits also provide an indication in the state of one of the modem status lines. These bits are set to '1' when a change in corresponding line has been detected and they are reset when the register is being read.

| Bit# | Access | Description                                                      |

|------|--------|------------------------------------------------------------------|

| 0    | R      | Delta Clear To Send (DCTS) indicator                             |

|      |        | '1' – The CTS line has changed its state.                        |

| 1    | R      | Delta Data Set Ready (DDSR) indicator                            |

|      |        | '1' – The DSR line has changed its state.                        |

| 2    | R      | Trailing Edge of Ring Indicator (TERI) detector. The RI line has |

|      |        | changed its state from low to high state.                        |

| 3    | R      | Delta Data Carrier Detect (DDCD) indicator                       |

|      |        | '1' – The DCD line has changed its state.                        |

| 4    | R      | Complement of the CTS input or equals to RTS in loopback mode.   |

| 5    | R      | Complement of the DSR input or equals to DTR in loopback mode.   |

| 6    | R      | Complement of the RI input or equals to Out1 in loopback mode.   |

| 7    | R      | Complement of the DCD input or equals to Out2 in loopback mode.  |

#### 4.9 Divisor Latches

The divisor latches can be accessed by setting the 7<sup>th</sup> bit of LCR to '1'. You should restore this bit to '0' after setting the divisor latches in order to restore access to the other registers that occupy the same addresses. The 4 bytes form one 32-bit register, which is internally accessed as a single number. You should therefore set all 4 bytes of the register to ensure normal operation. The register is set to the default value of 0 on reset, which disables all serial I/O operations in order to ensure explicit setup of the register in the software. The value set should be equal to (system clock speed) / (16 x desired baud rate).

11 of 14

# **Operation**

This UART core is very similar in operation to the standard 16550 UART chip with the main exception being that only the FIFO mode is supported. Additionally, it extends the Divisor Latch register to 32-bit from 16 bits in the 16550. The scratch register is removed, as it serves no purpose.

#### 5.1 Initialization

Upon reset the core performs the following tasks:

- The receiver and transmitter FIFOs are cleared.

- The receiver and transmitter shift registers are cleared

- The Divisor Latch register is set to 0.

- The Line Control Register is set to communication of 8 bits of data, no parity, 1 stop bit.

- All interrupts are disabled in the Interrupt Enable Register.

For proper operation, perform the following:

- Set the Line Control Register to the desired line control parameters. Set bit 7 to '1' to allow access to the Divisor Latches.

- Set the Divisor Latches.

- Set bit 7 of LCR to '0' to disable access to Divisor Latches. At this time the transmission engine starts working and data can be sent and received.

- Set the FIFO trigger level. Generally, higher trigger level values produce less interrupt to the system, so setting it to 14 bytes is recommended if the system responds fast enough.

- Enable desired interrupts by setting appropriate bits in the Interrupt Enable register.

Remember that (Input Clock Speed)/(Divisor Latch value) = 16 x the communication baud rate. Since the protocol is asynchronous and the sampling of the bits is performed in the perceived middle of the bit time, it is highly immune to small differences in the clocks of the sending and receiving sides, yet no such assumption should be made when calculating the Divisor Latch values.

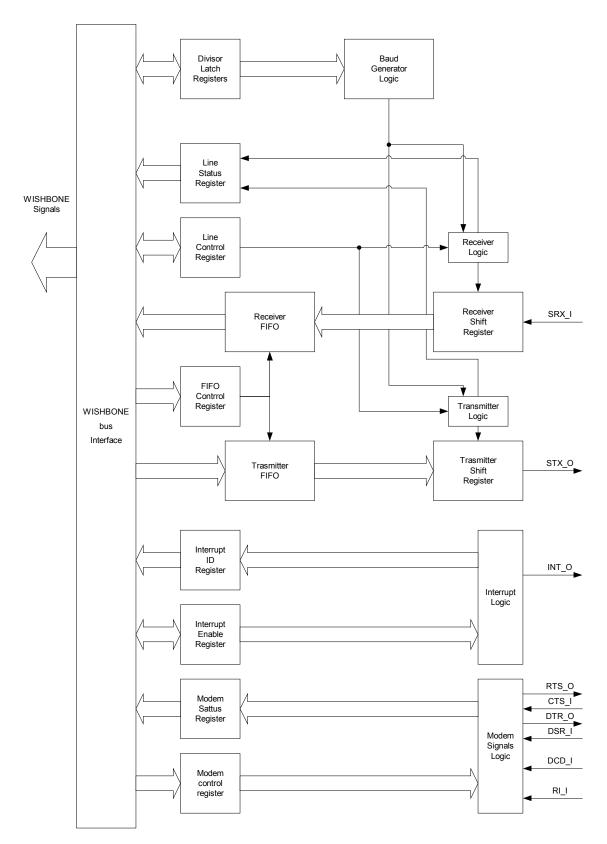

# **Architecture**

The core implements the WISNBONE SoC bus interface for communication with the system. It has an 8-bit data bus for compatibility reason. The core requires one interrupt. It requires 2 pads in the chip (serial in and serial out) and, optionally, another six modem control signals, which can otherwise be implemented using general purpose I/Os on the chip.

The block diagram of the core is on the following page.

Figure 1 - Block Diagram of the UART core