Fixed-point quadratic polynomial

Project maintainers

Details

Created: Feb 16, 2009

Updated: Jul 26, 2011

SVN Updated: Mar 10, 2009

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:VHDL

Development status:Stable

Additional info:FPGA proven

WishBone compliant: No

WishBone version: n/a

License: GPL

Description

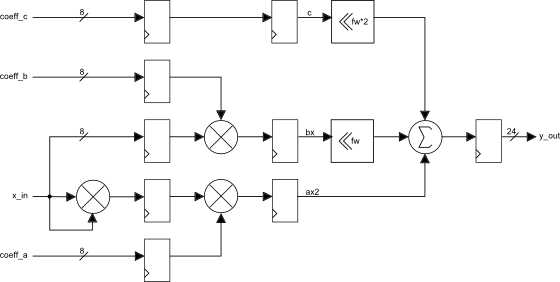

Quadratic_func is a fully pipelined quadratic polynomial that computes the relation y = ax^2 + bx + c. On each rising-edge of the clock (when en is high), the coefficients and input x term are sampled at the function inputs. The result has a latency of 3 clock cycles. All inputs to the function are 8-bit signed fractions, with the generic parameter 'fw' specifying the number of fraction bits. The output result is a 24-bit signed fraction. If integer arithmetic is preferred, then the parameter fw should be set to 0. For larger bit-widths, the design can easily be scaled up to suit the application.

Features

- Computes the relation y = ax^2 + bx + c

- Signed 8-bit fixed-point input

- Signed 8-bit fixed-point coefficients

- Signed 24-bit fixed-point output

- Configurable number of fraction bits

- Dynamic coefficients updated every clock cycle

- No internal loss of precision (no rounding or truncation)

- Fully pipelined architecture

- Result has a 3 clock-cycle latency

Status

- Fully tested and complete

- Future versions to support generic input data and coefficient widths as well as fraction width

Help and Support

Simon Doherty is a Senior Design Consultant at ZIPcores If you require further assistance regarding the implementation of this core, you may contact me directly via my Opencores email alias at sdoherty@opencores.org. Alternatively you may contact me through customer support at ZIPcores.