QUARK RISK

Project maintainers

Details

Name: quark

Created: Feb 22, 2016

Updated: Nov 27, 2017

SVN Updated: Dec 30, 2016

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Created: Feb 22, 2016

Updated: Nov 27, 2017

SVN Updated: Dec 30, 2016

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Star1you like it: star it!

Other project properties

Category:Processor

Language:Verilog & VHDL

Development status:Planning

Additional info:

WishBone compliant: Yes

WishBone version: n/a

License: LGPL

Language:Verilog & VHDL

Development status:Planning

Additional info:

WishBone compliant: Yes

WishBone version: n/a

License: LGPL

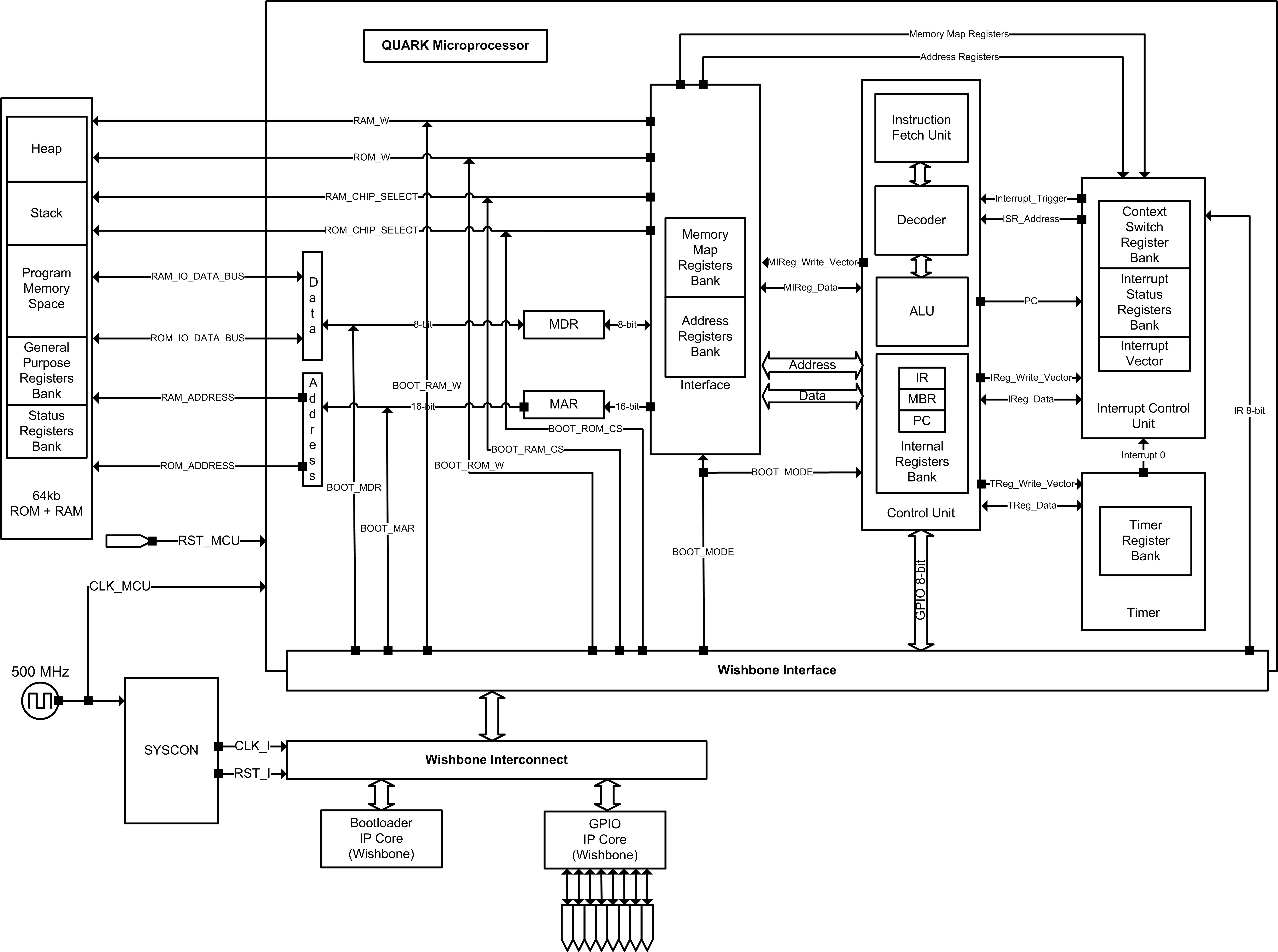

Description

8bit RISC microprocessor designed with features like wishbone interconnect to provide it as a tool for System-on-Chip or core (ASIC, CISC processor, etc) development decreasing the cost and effort when a bug is present on the design. This processor may be used as core (ASIC, SoC, CISC processor, etc) internal controller(s), so when a bug is present, engineering group shall modify only microcode and reprogram it instead of redesign the HDL modules.

Mechanization Drawing

License Info.

This project is under license LGPL 3.0

LGPL 3.0

References

© copyright 1999-2018 OpenCores.org, equivalent to Oliscience, all rights reserved. OpenCores®, registered trademark.