Scan Based Serial Communication

Project maintainers

Details

Name: scan_based_serial_communication

Created: Jul 19, 2010

Updated: Jul 22, 2010

SVN Updated: Apr 8, 2013

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Created: Jul 19, 2010

Updated: Jul 22, 2010

SVN Updated: Apr 8, 2013

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Star1you like it: star it!

Other project properties

Category:Communication controller

Language:Verilog

Development status:Stable

Additional info:

WishBone compliant: No

WishBone version: n/a

License: BSD

Language:Verilog

Development status:Stable

Additional info:

WishBone compliant: No

WishBone version: n/a

License: BSD

Description

Included is an on-chip synthesizble scan block and an off-chip testbench to interact with it.

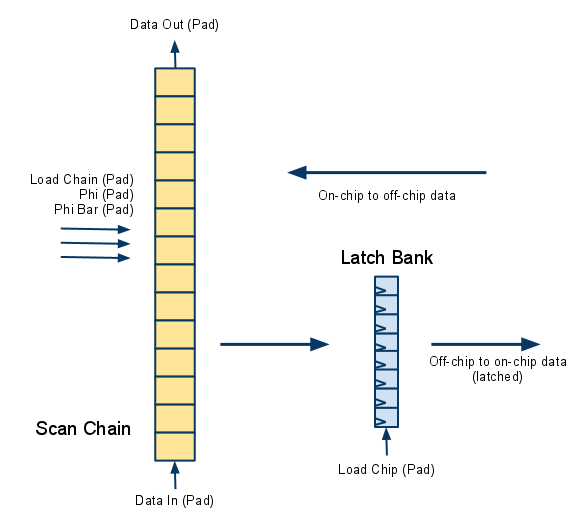

The on-chip scan block has six pad signals that go off-chip, and a configurable number of on-chip data input and output signals. Data signals from on-chip, going off-chip, can be latched into the scan chain and scanned out. Data signals going from off-chip to on-chip can be scanned into the chip, then stored into a latch that drives the output of the module. The buffering latch prevents data that is coming on-chip to not toggle randomly while the scan chain is active.

Due to the buffering latches, complex internal interfaces can be emulated using the scan chain. For instance, an SRAM could be connected to a clock, chip select, write enable, 64-bit data-in, and 64-bit data-out, all of which are connected to the scan chain. The scan chain would need to be used a few times for each "cycle" of the SRAM. For instance, each time the clock signal toggles the scan chain would need to be completely reloaded. Although this process is slow, it works reliably.

The scan chain is implemented with a simple Perl-based script called deperlify to make the scan chain easily reconfigurable (a copy is included). A single configuration file generates a synthesizble scan block (for on-chip) and a testbench to test it, which allows rapid changes with minimal errors. The testbench has a number of tasks to easily access the on-chip structures.

This code was originally developed by David Fick at the University of Michigan VLSI Design/Automation Lab.

© copyright 1999-2018 OpenCores.org, equivalent to Oliscience, all rights reserved. OpenCores®, registered trademark.