Theia: ray graphic processing unit

Project maintainers

Details

Created: Nov 23, 2009

Updated: Aug 16, 2011

SVN Updated: Nov 7, 2012

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 2 reported / 1 solved

Other project properties

Language:Verilog

Development status:Beta

Additional info:

WishBone compliant: Yes

WishBone version: n/a

License: GPL

Overview

Theia GPU Overview

Theia is a fully programmable Graphic Processing Unit written in structural Verilog

Theia features a multi-core architecture.

Theia uses a Ray-Cast approach to perform the RENDER. The Multi-core architectue benefits from

the parallel nature of Ray casting.

Each core has a pipe-lined SIMD ALU, capable of performing Fixed Point arithmetic on 3D vectors.

Theia's instruction set includes logic, arithmetic and flow control instructions.

Theia features a default code written into each core's ROM.

The default code allows a fully functional RENDER including texturing with bi-linear filtering.

The user can write his own Shader program for special effects,

or even overwrite the entire

default code with his own!

For more details, see the Examples section under SVN.

High level Architecture

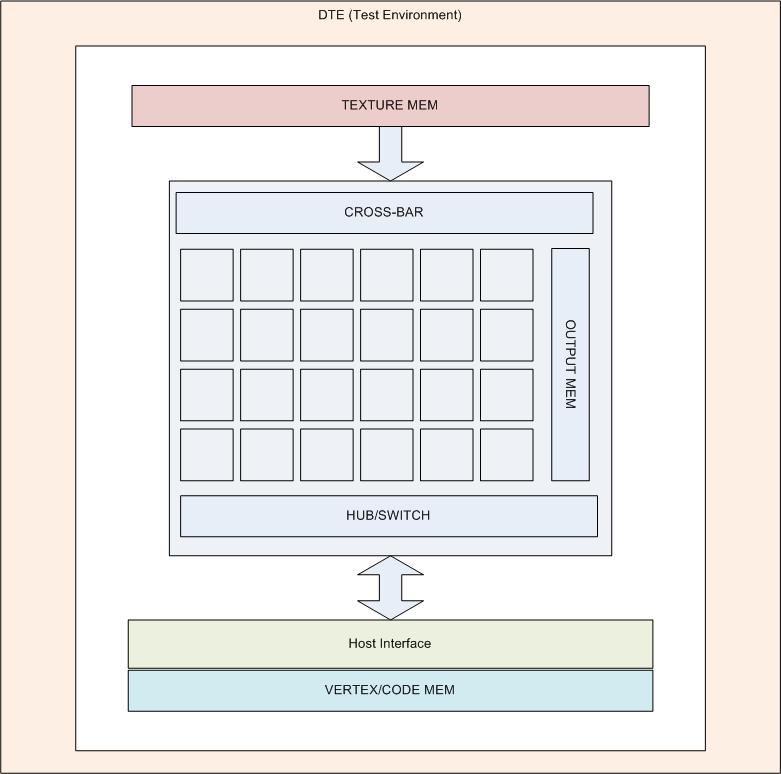

The Next diagram ilustrates the high level GPU architecure.

The

The GPU is has multiple cores.

The Cores communicate with the GPU Memory using the WishBone protocol.

The internal GPU memory is a combination of no-share with

a cross-bar and a HUB for geometry and textures

A Host module, is the interface between the 'outside world' (Desing Test Environment) and

internal GPU Blocks.

Note:Although the GPU has been written in such to synthetizable, THEIA only supports behavioral simulation at the moment.

Simulation Output

You can actually see an image as the output of the simulation

Please look at the Examples folder under the SVN trunk for more information

Here are some examples of simulation outputs:

Debug Capabilities

The simulation can be configured to generate verbose code dumps that allow you to see every instruction executed on each core

Here is a example of a piece of output log for Core0:

[CORE 0] IP: 142( 63068700ns ZERO 0080 [ 00000000 00020000 00000009 ][ 00000000 00020000 00000009 ] = [ 00000000 00000000 00000000 ])

[CORE 0] IP: 143( 63068720ns SETX 0049 [ 00020000 00000000 00000000 ][ 00020000 00003106 00001d6a ] = [ 00020000 00003106 00001d6a ])

[CORE 0] IP: 144( 63068740ns SETX 0047 [ 00000000 00000000 00000000 ][ 00000000 fffaccae 00000000 ] = [ 00000000 fffaccae 00000000 ])

[CORE 0] IP: 145( 63068760ns SUB 0064 [ fffb0000 00040000 00000000 ][ 00050000 00040000 00000000 ] = [ fff60000 00000000 00000000 ])

[CORE 0] IP: 146( 63068780ns SUB 0065 [ fffb0000 fffa0000 00000000 ][ 00050000 00040000 00000000 ] = [ fff60000 fff60000 00000000 ])

[CORE 0] IP: 147( 63068800ns SUB 0058 [ 00000000 00040000 00020000 ][ 00050000 00040000 00000000 ] = [ fffb0000 00000000 00020000 ])

[CORE 0] IP: 148( 63068840ns CROSS 0059 [ ffff2736 fffe3ac0 ffff9d79 ][ fff60000 fff60000 00000000 ] = [ fffe135d 0001eca3 fffb61b2 ])

[CORE 0] IP: 149( 63068880ns CROSS 005a [ fffb0000 00000000 00020000 ][ fff60000 00000000 00000000 ] = [ 00000000 fff60000 00000000 ])

[CORE 0] IP: 150( 63068930ns DOT 0069 [ 00000000 fff60000 00000000 ][ fff60000 fff60000 00000000 ] = [ 00320000 00320000 00320000 ])

[CORE 0] IP: 151( 63068980ns DOT 006a [ fffe135d 0001eca3 fffb61b2 ][ fffb0000 00000000 00020000 ] = [ 00003149 00003149 00003149 ])

[CORE 0] IP: 152( 63069030ns DOT 006b [ 00000000 fff60000 00000000 ][ ffff2736 fffe3ac0 ffff9d79 ] = [ 0008da40 0008da40 0008da40 ])

[CORE 0] IP: 153( 63069080ns DOT 0066 [ fffe135d 0001eca3 fffb61b2 ][ fff60000 00000000 00000000 ] = [ 00099f2f 00099f2f 00099f2f ])

[CORE 0] IP: 154( 63069800ns DIV 0063 [ 00320000 00320000 00320000 ][ 00099f2f 00099f2f 00099f2f ] = [ 000a649f 000a649f 000a649f ])

[CORE 0] IP: 155( 63070520ns DIV 0067 [ 00003149 00003149 00003149 ][ 00099f2f 00099f2f 00099f2f ] = [ 00000a3e 00000a3e 00000a3e ])

[CORE 0] IP: 156( 63071240ns DIV 0068 [ 0008da40 0008da40 0008da40 ][ 00099f2f 00099f2f 00099f2f ] = [ 0001d710 0001d710 0001d710 ])

[CORE 0] IP: 157( 63071260ns JGEX 009e [ 00000a3e 00000a3e 00000a3e ][ 00000000 fffaccae 00000000 ] = [ 00000000 00000000 00000000 ])

[CORE 0] IP: 159( 63071280ns JGEX 00a0 [ 0001d710 0001d710 0001d710 ][ 00000000 fffaccae 00000000 ] = [ 00000000 00000000 00000000 ])

[CORE 0] IP: 161( 63071300ns ADD 0048 [ 00000a3e 00000a3e 00000a3e ][ 0001d710 0001d710 0001d710 ] = [ 0001e14e 0001e14e 0001e14e ])

[CORE 0] IP: 162( 63071320ns JLEX 00a3 [ 0001e14e 0001e14e 0001e14e ][ 00020000 00003106 00001d6a ] = [ 00000000 00000000 00000000 ])

[CORE 0] IP: 164( 63071340ns JGEX 00ad [ 000a649f 000a649f 000a649f ][ 01f40000 000a6d67 000a6d67 ] = [ 00000000 00000000 00000000 ])

[CORE 0] IP: 165( 63071360ns COPY 005f [ 000a649f 000a649f 000a649f ][ 00000000 00020000 00000009 ] = [ 000a649f 000a649f 000a649f ])

Thanks for your interest in the project.

Please feel free to contact me any questions or help running the Simulation!.