Or1k SoC on Altera Embedded Dev Kit

Project maintainers

Details

Name: or1k_soc_on_altera_embedded_dev_kit

Created: Nov 16, 2009

Updated: May 29, 2012

SVN Updated: Sep 8, 2010

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 2 reported / 1 solved

Created: Nov 16, 2009

Updated: May 29, 2012

SVN Updated: Sep 8, 2010

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 2 reported / 1 solved

Star2you like it: star it!

Other project properties

Category:System on Chip

Language:Verilog

Development status:Mature

Additional info:

WishBone compliant: Yes

WishBone version: n/a

License: LGPL

Language:Verilog

Development status:Mature

Additional info:

WishBone compliant: Yes

WishBone version: n/a

License: LGPL

Description

This project is to implement a SoC of using OpenRISC 1200 and many open source IP cores from opencores.org on Nios II Embedded Evaluation Kit (Cyclone III Edition).

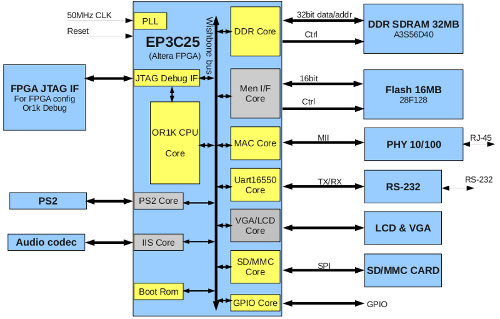

The system architecture is shown as below

Features

Hardware:

- 32-bit Openrisc 1200 with 8k cache and mmu enable (done)

- 16KB on-chip RAM for boot loader (done)

- Wishbone-to-Altera DDR/DDRII SDRAM core bridge (done)

- Advanced Debug System core. Debugging via Altera Virtual JTAG (done)

- Ethernet 10/100 MAC (done)

- UART 16550 core (done)

- SD/MMC core (done)

- GPIO core (done)

- VGA/LCD core + Touch screen (TBD)

- I2S core for audio codec (TBD)

- PS2 core for keyboard (TBD)

- MEM I/F core for FlashRAM and on-board SRAM (TBD)

- Linux 2.6.35 (successes boot up on this dev kit, but need to enhance)

- BusyBox 1.7.5 (boot passed with above kernel)

- SD card boot loader (done)

- Ethernet driver (done, web server up)

- GDB debugging supported (done)

- Block device driver for SD/MMC core (working)

- Framebuffer driver for VGA/LCD core (TBD)

- Touch screen driver (TBD)

- Sound card driver for I2S audio codec (TBD)

- PS2 keyboard driver for PS2 core (TBD)

© copyright 1999-2018 OpenCores.org, equivalent to Oliscience, all rights reserved. OpenCores®, registered trademark.