SPI-slave Wishbone-Master

Project maintainers

Details

Created: Jul 21, 2018

Updated: Apr 19, 2021

SVN Updated: Jul 22, 2018

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:VHDL

Development status:Mature

Additional info:

WishBone compliant: Yes

WishBone version: B.4

License: LGPL

Description

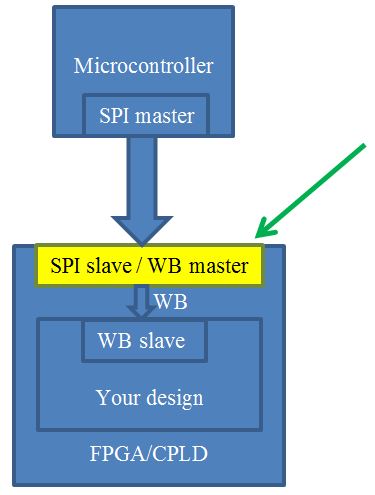

If a FPGA or CPLD needs to be coupled to a microcontroller often a fast interface is required. Many controllers do not provide an external address/data bus. Even if, this would require many wires and pins at both parts. Alternatively we can use one of the standard serial peripherals such as

Bus type

typical max. baud rate

needed pins

SPI

15..30 Mbit/s

4

I2C

often: 400 kbit/s

sometimes: 1 Mbit/s

seldom:3 Mbit/s

2

UART

5 Mbit/s

2

SD/MMC

12/25/48MHz @

1/4/8 datalines

3/6/10

The given core is a SPI slave which receives the SCLK, MOSI, MISO and SSEL signals from the SPI master (microcontroller). The master starts a transaction by sending a command followed by data. The command can be write, read, set, clear or toggle. It is decoded in the core and wishbone transactions on the master port are generated. Your design will be connected to this master port as wb slave(s) and now can be controlled by your controller.