# Generic AXI DMA

### joe68.chou@msa.hinet.net

#### **Revision History**

| Rev | Date       | Description  |  |  |  |  |  |

|-----|------------|--------------|--|--|--|--|--|

| 0.0 | 2017/05/27 | irst release |  |  |  |  |  |

|     |            |              |  |  |  |  |  |

|     |            |              |  |  |  |  |  |

|     |            |              |  |  |  |  |  |

|     |            |              |  |  |  |  |  |

|     |            |              |  |  |  |  |  |

### Description

An AXI DMA fits the peripheral (such as I2S, UART, SPI....) it needs DMA capability in SoC; the DMA will move data between the peripheral and system memory for efficient data transfer, also saving CPU computing power.

### Overview

- AXI compliant; 32-bit data width.

- Bi-directional; independent read/write channel, and also read/write channel can be executed in parallel.

- Byte addressable; DMA starting address and transfer length could not have to be a multiple of 4.

- Maximum burst length is 8 words, and burst access won't cross 8-word boundary.

- Outstanding transaction support.

- Response error/time-out support.

- APB interface for register programing

- Peripheral interface protocol: AXI stream

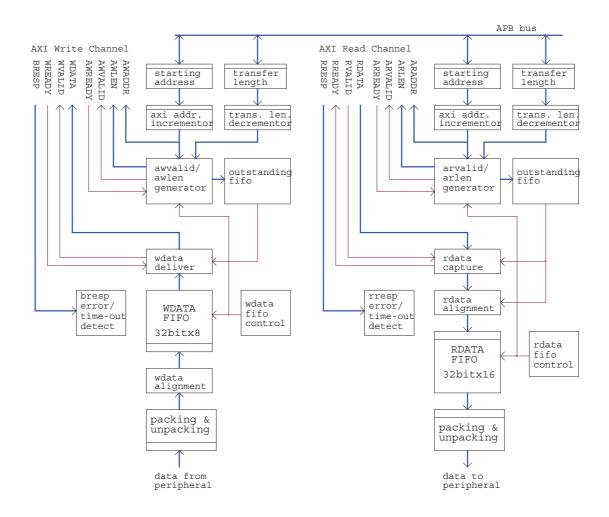

#### Block Diagram

Hardware Description

- HW will break DMA transfer length into several AXI burst accesses. The maximum burst length is 8 words, and also burst access address will not cross 8-word boundary, and this is good for DDR efficiency if target slave is DDR. Up to DMA address and remaining DMA length situation the burst length could be smaller in order not to cross 8-word boundary while DMA starting and ending addresses are not located at 8-word boundary.

- HW will look ahead on internal data FIFO situation for issuing access to AXI. For read it will make sure FIFO has enough room for receiving next bursting RDATA before issuing read access; and for write it will make sure FIFO has bursting WDATA ready before issuing write access. This prevents data pending or waiting on AXI bus, which may cause AXI bus low efficiency.

- For supporting of outstanding access a FIFO is used to keep issued AxADDR and AxLEN information to handle RDATA receiving or WDATA delivering.

IO Interface Definition

| General  |              |                                                  |

|----------|--------------|--------------------------------------------------|

| IO       | name         | description                                      |

| input    | clk          | Clock input to DMA.                              |

|          |              | The design is clocking by this clock only, and   |

|          |              | also only rising edge of the clock used.         |

| input    | rstn         | Reset input to DMA, low active.                  |

|          |              | The DMA used synchronous reset, the reset        |

|          |              | de-assertion needs to be synchronized with input |

|          |              | clock.                                           |

| output   | dma_itr      | DMA interrupt output; active high, level         |

|          |              | triggered. Registered output, glitch free. SW    |

|          |              | needs to clear the interrupt source within the   |

|          |              | design during ISR.                               |

| APB int  | erface       |                                                  |

| input    | pselect      | APB pselect input.                               |

| input    | penable      | APB penable input.                               |

| input    | pwrite       | APB pwrite input.                                |

| input    | paddr[7:0]   | APB address input                                |

| input    | pwdata[31:0] | APB write data input.                            |

| output   | prdata[31:0] | APB read data return.                            |

| AXI inte | erface       |                                                  |

| output   | arvalid      | AXI arvalid output                               |

| input    | arready      | AXI arready input                                |

| output   | araddr[31:0] | AXI araddr input                                 |

| output   | arlen[2:0]   | AXI arlen output.                                |

|          |              | The value could be from 3'b111 to 3'b000.        |

| output   | arsize[2:0]  | AXI arsize output. Fixed at 3'b010(32-bit)       |

| output   | arburst[1:0] | AXI arburst output. Fixed at 2'b01(INCR)         |

| input    | rvalid       | AXI rvalid input.                                |

| output   | rready       | AXI rready output                                |

| input    | rdata[31:0]  | AXI rdata input.                                 |

| input    | rresp[1:0]   | AXI rresp input                                  |

| input    | rlast        | AXI rlast input                                  |

| output   | awvalid      | AXI awvalid output                               |

| input    | awready      | AXI awready input                                |

| output   | awaddr[31:0] | AXI awaddr input                                 |

| output   | awlen[2:0]   | AXI awlen output.                                |

|          |                       | The value could be from 3'b111 to 3'b000.          |

|----------|-----------------------|----------------------------------------------------|

| output   | awsize[2:0]           | AXI awsize output. Fixed at 3'b010(32-bit)         |

| output   | awburst[1:0]          | AXI awburst output. Fixed at 2'b01(INCR)           |

| output   | wvalid                | AXI wvalid output                                  |

| input    | wready                | AXI wready input                                   |

| output   | wdata[31:0]           | AXI wdata output                                   |

| output   | wstrb[3:0]            | AXI wstrb output                                   |

| output   | wlast                 | AXI wlast output                                   |

| input    | bvalid                | AXI bvalid input                                   |

| output   | bready                | AXI bready output                                  |

| input    | bresp[1:0]            | AXI bresp input                                    |

| Peripher | al/RDMA interface (A) | XI stream protocol)                                |

| output   | rdma_tvalid           | To indicate data output from RDMA is valid to      |

|          |                       | peripheral.                                        |

| input    | rdma_tready           | Peripheral is ready to receive the tdata.          |

| output   | rdma_tdata[31:0]      | RDMA data output to peripheral.                    |

| output   | rdma_tstrb[3:0]       | tdata strobe indication; only combinations below.  |

|          |                       | tstrb[3:0]=4'b0001 indicate tdata[7:0] is valid.   |

|          |                       | tstrb[3:0]=4'b0011 indicate tdata[15:0] is valid.  |

|          |                       | tstrb[3:0]=4'b0111: indicate tdata[23:0] is valid. |

|          |                       | tstrb[3:0]=4'b1111: indicate tdata[31:0] is valid. |

| output   | rdma_tlast            | To indicate the last data to peripheral of a DMA.  |

| Peripher | al/WDMA interface (A) | XI stream protocol)                                |

| input    | wdma_tvalid           | To indicate data input to WDMA is valid from       |

|          |                       | peripheral.                                        |

| output   | wdma_tready           | WDMA is ready to receive the tdata.                |

| input    | wdma_tdata[31:0]      | WDMA data input from peripheral.                   |

| input    | wdma_tstrb[3:0]       | tdata strobe indication; only combinations below   |

|          |                       | allowed                                            |

|          |                       | tstrb[3:0]=4'b0001 indicate tdata[7:0] is valid.   |

|          |                       | tstrb[3:0]=4'b0011 indicate tdata[15:0] is valid.  |

|          |                       | tstrb[3:0]=4'b0111: indicate tdata[23:0] is valid. |

|          |                       | tstrb[3:0]=4'b1111: indicate tdata[31:0] is valid. |

|          |                       |                                                    |

## Register Definition

| Read DMA starting register / RDMA_SADR_REG | 0x00 |

|--------------------------------------------|------|

|--------------------------------------------|------|

| bit# | name     | type | reset | Description                                    |

|------|----------|------|-------|------------------------------------------------|

| 31:0 | Read DMA | R/W  | none  | Read DMA starting address.                     |

|      | Starting |      |       | To specify the source starting address for DMA |

|      | address  |      |       | transfer.                                      |

| Read I | OMA length r | egister | RDM   | A_LEN_REG                           | 0x04               |

|--------|--------------|---------|-------|-------------------------------------|--------------------|

| bit#   | name         | type    | reset | Description                         |                    |

| 19:0   | Read DMA     | R/W     | 0x0   | Read DMA transfer length, unit:     | byte.              |

|        | Transfer     |         |       | A non-zero value written to this r  | egister will       |

|        | length       |         |       | enable the read DMA transfer.       |                    |

|        |              |         |       | This register will be cleared to ze | ero by hardware    |

|        |              |         |       | while RDMA is started. Note: DM     | MA starting        |

|        |              |         |       | address register and DMA transfe    | er length register |

|        |              |         |       | are double-buffered, and user ma    | y prepare next     |

|        |              |         |       | DMA starting address and transfe    | er length while    |

|        |              |         |       | previous DMA start flag/interrup    | t has been set.    |

| 31:20  | Reserved     | R       | 0x0   | Always zero while reading           |                    |

| Read | DMA control | register | ·/ RDM | /A_CTL_REG 0x08     |  |

|------|-------------|----------|--------|---------------------|--|

| bit# | name        | type     | reset  | Description         |  |

| 0    | Read DMA    | R/W      | 0x0    | 0: mask             |  |

|      | start       |          |        | 1: enable interrupt |  |

|      | interrupt   |          |        |                     |  |

|      | enable      |          |        |                     |  |

| 1    | Read DMA    | R/W      | 0x0    | 0: mask             |  |

|      | finish      |          |        | 1: enable interrupt |  |

|      | interrupt   |          |        |                     |  |

|      | enable      |          |        |                     |  |

| 2    | Read DMA    | R/W      | 0x0    | 0: mask             |  |

|      | RRESP       |          |        | 1: enable interrupt |  |

|      | error       |          |        |                     |  |

|      | interrupt   |          |        |                     |  |

|      | enable      |          |        |                     |  |

| 3    | Read DMA    | R/W      | 0x0    | 0: mask             |  |

|      | RRESP       |          |        | 1: enable interrupt |  |

|      | time out    |          |        |                     |  |

|      | interrupt   |          |        |                     |  |

|      | enable      |          |        |                     |  |

| 4     | Read DMA  | R/W | 0x0 | 0: mask                                            |

|-------|-----------|-----|-----|----------------------------------------------------|

|       | RVALID    |     |     | 1: enable interrupt                                |

|       | error     |     |     |                                                    |

|       | interrupt |     |     |                                                    |

|       | enable    |     |     |                                                    |

| 7:5   | Reserved  | R   | 0x0 | Always zero while reading                          |

| 8     | Read DMA  | R/W | 0x0 | 0: play                                            |

|       | pause     |     |     | 1: pause; to disable DMA request to AXI bus.       |

| 9     | Read DMA  | R/W | 0x0 | To terminate on-going DMA operation.               |

|       | flush     |     |     | Set to 1 to terminate, and it will be auto-cleared |

|       |           |     |     | by hardware while on-going AXI transaction has     |

|       |           |     |     | been finished.                                     |

| 31:10 | Reserved  | R   | 0x0 | Always zero while reading                          |

| Write I | Write DMA starting register / WDMA_SADR_REG 0x10 |     |      |                                    |                 |

|---------|--------------------------------------------------|-----|------|------------------------------------|-----------------|

| bit#    | it# name type reset                              |     |      | Description                        |                 |

| 31:0    | Write DMA                                        | R/W | none | Write DMA starting address.        |                 |

|         | Starting                                         |     |      | To specify the source starting add | lress for write |

|         | address                                          |     |      | DMA transfer.                      |                 |

| Write I | OMA length r | egister | / WDM | IA_LEN_REG                          | 0x14               |

|---------|--------------|---------|-------|-------------------------------------|--------------------|

| bit#    | name         | type    | reset | Description                         |                    |

| 19:0    | Write DMA    | R/W     | 0x0   | Write DMA transfer length, unit:    | byte.              |

|         | Transfer     |         |       | A non-zero value written to this r  | egister will       |

|         | length       |         |       | enable the write DMA transfer.      |                    |

|         |              |         |       | This register will be cleared to ze | ero by hardware    |

|         |              |         |       | while WDMA is started. Note: D      | MA starting        |

|         |              |         |       | address register and DMA transfe    | er length register |

|         |              |         |       | are double-buffered, and user ma    | y prepare next     |

|         |              |         |       | DMA starting address and transfe    | er length while    |

|         |              |         |       | previous DMA start flag/interrup    | t has been set.    |

| 31:20   | Reserved     | R       | 0x0   | Always zero while reading           |                    |

| Write DMA control register / WDM |                      |     |     | IA_CTL_REG          | 0x18 |

|----------------------------------|----------------------|-----|-----|---------------------|------|

| bit#                             | bit# name type reset |     |     | Description         |      |

| 0                                | Write DMA            | R/W | 0x0 | 0: mask             |      |

|                                  | start                |     |     | 1: enable interrupt |      |

|       | interrupt |     |     |                                                    |

|-------|-----------|-----|-----|----------------------------------------------------|

|       | enable    |     |     |                                                    |

| 1     | Write DMA | R/W | 0x0 | 0: mask                                            |

|       | finish    |     |     | 1: enable interrupt                                |

|       | interrupt |     |     |                                                    |

|       | enable    |     |     |                                                    |

| 2     | Write DMA | R/W | 0x0 | 0: mask                                            |

|       | BRESP     |     |     | 1: enable interrupt                                |

|       | error     |     |     |                                                    |

|       | interrupt |     |     |                                                    |

|       | enable    |     |     |                                                    |

| 3     | Write DMA | R/W | 0x0 | 0: mask                                            |

|       | BRESP     |     |     | 1: enable interrupt                                |

|       | time out  |     |     |                                                    |

|       | interrupt |     |     |                                                    |

|       | enable    |     |     |                                                    |

| 4     | Write DMA | R/W | 0x0 | 0: mask                                            |

|       | BVALID    |     |     | 1: enable interrupt                                |

|       | error     |     |     |                                                    |

|       | interrupt |     |     |                                                    |

|       | enable    |     |     |                                                    |

| 7:5   | Reserved  | R   | 0x0 | Always zero while reading                          |

| 8     | Write DMA | R/W | 0x0 | 0: play                                            |

|       | pause     |     |     | 1: pause; to disable DMA request to AXI bus.       |

| 9     | Write DMA | R/W | 0x0 | To terminate on-going DMA operation.               |

|       | flush     |     |     | Set to 1 to terminate, and it will be auto-cleared |

|       |           |     |     | by hardware while on-going AXI transaction has     |

|       |           |     | ļ   | been finished.                                     |

| 31:10 | Reserved  | R   | 0x0 | Always zero while reading                          |

| DMA  | DMA Status register / DMA_STT_REG 0x20 |      |       |                                      |                |

|------|----------------------------------------|------|-------|--------------------------------------|----------------|

| bit# | name                                   | type | reset | Description                          |                |

| 0    | Read DMA                               | R/W  | 0x0   | Read DMA start interrupt flag. A     | n interrupt is |

|      | start                                  |      |       | generated while the DMA is start     | ted. Software  |

|      | interrupt                              |      |       | may clear it by writing 1 to this b  | oit.           |

|      | flag                                   |      |       | 0: no interrupt                      |                |

|      |                                        |      |       | 1: interrupt                         |                |

|      |                                        |      |       | Writing 1 to clear this bit, 0 no et | ffect.         |

|       | -         |     |     |                                                    |

|-------|-----------|-----|-----|----------------------------------------------------|

| 1     | Read DMA  | R/W | 0x0 | Read DMA finish interrupt flag. An interrupt is    |

|       | finish    |     |     | generated while DMA is finished. Software may      |

|       | interrupt |     |     | clear it by writing 1 to this bit.                 |

|       | flag      |     |     | 0: no interrupt                                    |

|       |           |     |     | 1: interrupt                                       |

|       |           |     |     | Writing 1 to clear this bit, 0 no effect.          |

| 2     | RRESP     | R/W | 0x0 | RRESP error received. Software may clear it by     |

|       | error     |     |     | writing 1 to this bit.                             |

|       | interrupt |     |     | 0: no interrupt                                    |

|       | flag      |     |     | 1: interrupt                                       |

|       |           |     |     | Writing 1 to clear this bit, 0 no effect           |

| 3     | RRESP     | R/W | 0x0 | RRESP didn't get back to RDMA within               |

|       | time out  |     |     | specified time. Software may clear it by writing 1 |

|       | interrupt |     |     | to this bit.                                       |

|       | flag      |     |     | 0: no interrupt                                    |

|       |           |     |     | 1: interrupt                                       |

|       |           |     |     | Writing 1 to clear this bit, 0 no effect           |

| 4     | RVALID    | R/W | 0x0 | Unexpected RVALID/RDATA received. Software         |

|       | error     |     |     | may clear it by writing 1 to this bit.             |

|       | interrupt |     |     | 0: no interrupt                                    |

|       | flag      |     |     | 1: interrupt                                       |

|       |           |     |     | Writing 1 to clear this bit, 0 no effect           |

| 7:5   | Reserved  | R   | 0x0 | Always zero while reading                          |

| 9:8   | RRESP     | R   | 0x0 | 00: OKAY                                           |

|       | error     |     |     | 01: EXOKAY                                         |

|       | message   |     |     | 10: SLVERR                                         |

|       |           |     |     | 11: DECERR                                         |

|       |           |     |     | See AXI spec for details.                          |

| 10    | Read DMA  | R   | 0x0 | To indicate Read DMA is operating                  |

|       | operating |     |     | 0: no                                              |

|       |           |     |     | 1: yes                                             |

| 15:11 | Reserved  | R   | 0x0 | Always zero while reading                          |

| 16    | Write DMA | R/W | 0x0 | Write DMA start interrupt flag. An interrupt is    |

|       | start     |     |     | generated while the DMA is started. Software       |

|       | interrupt |     |     | may clear it by writing 1 to this bit.             |

|       | flag      |     |     | 0: no interrupt                                    |

|       |           |     |     | 1: interrupt                                       |

|       |           |     |     | Writing 1 to clear this bit, 0 no effect.          |

|       |           |     |     |                                                    |

| 17    | Write DMA | R/W | 0x0 | Write DMA finish interrupt flag. An interrupt is   |

|-------|-----------|-----|-----|----------------------------------------------------|

| l     | finish    |     |     | generated while DMA is finished. Software may      |

| l     | interrupt |     |     | clear it by writing 1 to this bit.                 |

| l     | flag      |     |     | 0: no interrupt                                    |

| l     |           |     |     | 1: interrupt                                       |

| 1     |           |     |     | Writing 1 to clear this bit, 0 no effect.          |

| 18    | BRESP     | R/W | 0x0 | BRESP error received. Software may clear it by     |

| l     | error     |     |     | writing 1 to this bit.                             |

| l     | interrupt |     |     | 0: no interrupt                                    |

| l     | flag      |     |     | 1: interrupt                                       |

| 1     |           |     |     | Writing 1 to clear this bit, 0 no effect           |

| 19    | BRESP     | R/W | 0x0 | BRESP didn't get back to WDMA within               |

| l     | time out  |     |     | specified time. Software may clear it by writing 1 |

| l     | interrupt |     |     | to this bit.                                       |

| l     | flag      |     |     | 0: no interrupt                                    |

| 1     |           |     |     | 1: interrupt                                       |

| L     |           |     |     | Writing 1 to clear this bit, 0 no effect           |

| 20    | BVALID    | R/W | 0x0 | Unexpected BVALID/BRESP received. Software         |

| 1     | error     |     |     | may clear it by writing 1 to this bit.             |

| l     | interrupt |     |     | 0: no interrupt                                    |

| l     | flag      |     |     | 1: interrupt                                       |

| L     |           |     |     | Writing 1 to clear this bit, 0 no effect           |

| 23:21 | Reserved  | R   | 0x0 | Always zero while reading                          |

| 25:24 | BRESP     |     |     | 00: OKAY                                           |

| l     | error     |     |     | 01: EXOKAY                                         |

| l     | message   |     |     | 10: SLVERR                                         |

| 1     |           |     |     | 11: DECERR                                         |

| L     |           |     |     | See AXI spec for details.                          |

| 26    | Write DMA | R   | 0x0 | To indicate write DMA is operating.                |

| I     | operating |     |     | 0: no                                              |

| l     |           |     |     | 1: yes                                             |

|       |           |     |     |                                                    |

| Respor | Response Time-out period register / RSP_TOUT_REG 0x24 |      |       |                                 |                 |

|--------|-------------------------------------------------------|------|-------|---------------------------------|-----------------|

| bit#   | name                                                  | type | reset | Description                     |                 |

| 15:0   | Response                                              | R/W  | 0xFFF | To specify AXI BRESP or RRES    | P time out      |

|        | time out                                              |      | F     | period. If BRESP or RRESP didn  | 't get back to  |

|        | period                                                |      |       | DMA within specified time here, | then a time-out |

|       |          |   |     | interrupt will be generated.                       |

|-------|----------|---|-----|----------------------------------------------------|

|       |          |   |     | This is a down counter, will be reloaded by preset |

|       |          |   |     | value while access issued or BRESP/RRESP           |

|       |          |   |     | received but another outstanding access still      |

|       |          |   |     | on-going. The counter is clocking by DMA input     |

|       |          |   |     | clock, an interrupt is generated while count       |

|       |          |   |     | reaches zero value.                                |

|       |          |   |     | Value 0xFFFF is defined as a time-out counter      |

|       |          |   |     | disable state.                                     |

| 31:16 | Reserved | R | 0x0 | Always zero while reading                          |

Application Note

- The DMA operating is simple, SW user firstly may enable the interrupt wanted and set up DMA starting address, and then DMA transfer length. A non-zero value written to transfer length register will enable the DMA operation. After DMA is enabled, SW may wait for the interrupt for further operation.

- There are two interrupts from DMA operation; DMA start, and DMA finish. Note; DMA starting address and transfer length registers are double-buffered, while DMA is started, the software programmed DMA starting address and transfer length registers will be copied to internal, and also transfer length register will be cleared to zero, at this moment DMA starting address and transfer length registers are available for next DMA programming. While previous DMA is finished, HW will check DMA transfer length right away, if the content of transfer length register is not zero, then next DMA is started. Such mechanism will form a gapless transfer between two DMAs.

- SW user may select conventional way, wait for previous DMA finish, and then program DMA starting address and transfer length register to start next DMA.

- DMA pause function is to temporally disable DMA access to AXI.

- DMA flush function is to terminate on-going DMA as well as next DMA if it is already prepared in DMA transfer length register. The termination is executed after all outstanding transactions being finish to prevent AXI bus hang-up.