| 1 |

198 |

zero_gravi |

# The NEO430 Processor

|

| 2 |

|

|

|

| 3 |

|

|

[](https://travis-ci.com/stnolting/neo430)

|

| 4 |

|

|

[](https://github.com/stnolting/neo430/blob/master/LICENSE)

|

| 5 |

|

|

[](https://github.com/stnolting/neo430/releases)

|

| 6 |

|

|

[](https://raw.githubusercontent.com/stnolting/neo430/master/doc/NEO430.pdf)

|

| 7 |

|

|

|

| 8 |

|

|

[](https://github.com/stnolting/neo430/issues)

|

| 9 |

|

|

[](https://github.com/stnolting/neo430/pulls)

|

| 10 |

|

|

[](https://github.com/stnolting/neo430/commits/master)

|

| 11 |

|

|

|

| 12 |

|

|

## Table of Content

|

| 13 |

|

|

|

| 14 |

|

|

* [Introduction](#Introduction)

|

| 15 |

|

|

* [Processor Features](#Processor-Features)

|

| 16 |

|

|

* [Differences to the Original MSP430 Processors](#Differences-to-the-Original-MSP430-Processors)

|

| 17 |

|

|

* [Top Entity](#Top-Entity)

|

| 18 |

|

|

* [FPGA Implementation Results](#FPGA-Implementation-Results)

|

| 19 |

|

|

* [HW-SW Ecosystem](#HW-SW-Ecosystem)

|

| 20 |

|

|

* [Performance](#Performance)

|

| 21 |

|

|

* [**Quick Start**](#Quick-Start)

|

| 22 |

|

|

* [Change Log](#Change-Log)

|

| 23 |

|

|

* [Contact](#Contact)

|

| 24 |

|

|

* [Disclaimer, Proprietary and Legal Notice](#Disclaimer-Proprietary-and-Legal-Notice)

|

| 25 |

|

|

|

| 26 |

|

|

|

| 27 |

|

|

|

| 28 |

|

|

## Introduction

|

| 29 |

|

|

|

| 30 |

|

|

Welcome to __[The NEO430 Processor](https://github.com/stnolting/neo430)__ project!

|

| 31 |

|

|

|

| 32 |

|

|

You need a small but still powerful, customizable and microcontroller-like processor system for your next FPGA project?

|

| 33 |

|

|

Then the NEO430 is the right choice for you.

|

| 34 |

|

|

|

| 35 |

|

|

This processor is based on the Texas Instruments MSP430(TM) ISA and provides compatibility with the original

|

| 36 |

|

|

instruction set (see differences below). The NEO430 is not an exact MSP430 clone – it is more like a complete new implementation from the bottom up. The

|

| 37 |

|

|

processor features a very small outline, already implementing standard features like a timer, a watchdog, UART, TWI and SPI

|

| 38 |

|

|

serial interfaces, general purpose IO ports, an internal bootloader and of course internal memory for program code and data.

|

| 39 |

|

|

All of the implemented peripheral modules are optional – so if you do not need them, you can exclude them from synthesis to

|

| 40 |

|

|

reduce the size of the system. Any additional modules, which make a more customized system, can be connected via a

|

| 41 |

|

|

Wishbone-compatible bus interface or directly implemented within the processor. By this, you can built a system,

|

| 42 |

|

|

that perfectly fits your needs.

|

| 43 |

|

|

|

| 44 |

|

|

It is up to you to use the NEO430 as stand-alone, configurable and extensible microcontroller, or to use it as controller

|

| 45 |

|

|

within a more complex SoC design.

|

| 46 |

|

|

|

| 47 |

|

|

The high-level software development is based on the free TI msp430-gcc compiler tool chain. You can either use Windows

|

| 48 |

|

|

(PowerShell or Linux Subsystem) or Linux as build environment for your applications – the project supports both worlds.

|

| 49 |

|

|

|

| 50 |

|

|

This project is intended to work "out of the box". Just synthesize the test setup from this project, upload it to your

|

| 51 |

|

|

FPGA board of choice (the NEO430 uses a FPGA vendor-independent VHDL description) and start exploring the capabilities of

|

| 52 |

|

|

the NEO430 processor. Application program generation works by executing a single "make" command. Jump to the

|

| 53 |

|

|

"Let’s Get It Started" chapter in the NEO430 documentary, which provides a lot of guides and tutorials to make your first

|

| 54 |

|

|

NEO430 setup run: [ NEO430 Datasheet](https://raw.githubusercontent.com/stnolting/neo430/master/doc/NEO430.pdf "NEO430 Datasheet from GitHub")

|

| 55 |

|

|

|

| 56 |

|

|

|

| 57 |

|

|

|

| 58 |

|

|

## Processor Features

|

| 59 |

|

|

|

| 60 |

|

|

|

| 61 |

|

|

|

| 62 |

|

|

(optional modules are marked using dashed lines in the figure above)

|

| 63 |

|

|

|

| 64 |

|

|

|

| 65 |

|

|

- 16-bit open source soft-core microcontroller-like processor system

|

| 66 |

|

|

- Full support of the original [MSP430 instruction set architecture](https://raw.githubusercontent.com/stnolting/neo430/master/doc/instruction_set.pdf)

|

| 67 |

|

|

- Code-efficient CISC-like instruction capabilities

|

| 68 |

|

|

- Tool chain based on free [TI msp430-gcc compiler](http://software-dl.ti.com/msp430/msp430_public_sw/mcu/msp430/MSPGCC/latest/index_FDS.html "TI `msp430-gcc` compiler") (also available [here on github](https://github.com/stnolting/msp430-gcc))

|

| 69 |

|

|

- Application compilation scripts ([makefiles](https://github.com/stnolting/neo430/blob/master/sw/example/blink_led/Makefile)) for Windows Powershell / Windows Subsystem for Linux / native Linux

|

| 70 |

|

|

- Software requirements (regardless of platform):

|

| 71 |

|

|

- TI `msp430-gcc` compiler

|

| 72 |

|

|

- native `GCC` compiler

|

| 73 |

|

|

- `GNU Make`

|

| 74 |

|

|

- Completely described in behavioral, platform-independent VHDL (no macros, primitives, attributes, etc. used)

|

| 75 |

|

|

- Fully synchronous design, no latches, no gated clocks

|

| 76 |

|

|

- Very low resource requirements and high operating frequency

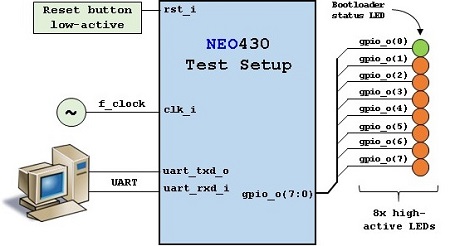

|

| 77 |

|

|

- Internal [DMEM](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_dmem.vhd) (RAM, for data) and [IMEM](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_imem.vhd) (RAM or ROM, for code), configurable sizes

|

| 78 |

|

|

- Customizable processor hardware configuration:

|

| 79 |

|

|

- Optional multiplier/divider unit ([MULDIV](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_muldiv.vhd))

|

| 80 |

|

|

- Optional high-precision timer ([TIMER](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_timer.vhd))

|

| 81 |

|

|

- Optional universal asynchronous receiver and transmitter ([UART](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_uart.vhd))

|

| 82 |

|

|

- Optional serial peripheral interface master ([SPI](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_spi.vhd)), 8 or 16 bit transfer data size, 6 dedicated chip-select lines

|

| 83 |

|

|

- Optional I2C-compatible two wire serial interface master ([TWI](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_twi.vhd)) supporting clock stretching

|

| 84 |

|

|

- Optional general purpose parallel IO port ([GPIO](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_gpio.vhd)), 16 inputs & 16 outputs, with pin-change interrupt and PWM option

|

| 85 |

|

|

- Optional 32-bit Wishbone bus master interface adapter ([WB32](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_wb_interface.vhd)) - including bridges to [Avalon (TM](https://github.com/stnolting/neo430/blob/master/rtl/top_templates/neo430_top_avm.vhd)) bus and [AXI4-Lite (TM](https://github.com/stnolting/neo430/blob/master/rtl/top_templates/neo430_top_axi4lite.vhd))

|

| 86 |

|

|

- Optional watchdog timer ([WDT](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_wdt.vhd))

|

| 87 |

|

|

- Optional cyclic redundancy check unit ([CRC16/32](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_crc.vhd))

|

| 88 |

|

|

- Optional custom functions unit ([CFU](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_cfu.vhd)) for processor-internal user-defined processor extensions

|

| 89 |

|

|

- Optional 4 channel PWM controller with 4 or 8 bit resolution ([PWM](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_pwm.vhd))

|

| 90 |

|

|

- Optional Galois Ring Oscillator (GARO) based true random number generator ([TRNG](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_trng.vhd)) with de-biasing and internal post-processing

|

| 91 |

|

|

- Optional external interrupts controller with 8 independent channels ([EXIRQ](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_exirq.vhd)), can also be used for software-triggered interrupts (traps, breakpoints, etc.)

|

| 92 |

|

|

- Optional NCO-based programmable frequency generator ([FREQ_GEN](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_freq_gen.vhd)) with 3 independent output channels

|

| 93 |

|

|

- Optional internal [bootloader](https://github.com/stnolting/neo430/blob/master/sw/bootloader/bootloader.c) (2kB ROM) with serial user console and automatic application boot from external SPI flash (like the FPGA configuration storage)

|

| 94 |

|

|

|

| 95 |

|

|

|

| 96 |

|

|

|

| 97 |

|

|

## Differences to the Original MSP430 Processors

|

| 98 |

|

|

|

| 99 |

|

|

- Completely different processor modules with different functionality

|

| 100 |

|

|

- Up to 48kB instruction memory and 12kB data memory

|

| 101 |

|

|

- NEO430 tool chain (makefiles, boot-code and linker script) required for application compilation

|

| 102 |

|

|

- Custom binary executable format

|

| 103 |

|

|

- No hardware debugging interface

|

| 104 |

|

|

- No analog components

|

| 105 |

|

|

- No support of TI's Code Composer Studio

|

| 106 |

|

|

- No support of CPU's DADD operation

|

| 107 |

|

|

- _Implicit_ software support of the NEO430 multiplier only via experimental ABI-override mode**

|

| 108 |

|

|

- Just 4 CPU interrupt channels (can be extended via the external IRQ controller)

|

| 109 |

|

|

- Single clock domain for complete processor

|

| 110 |

|

|

- Different numbers of instruction execution cycles

|

| 111 |

|

|

- Only one power-down (sleep) mode

|

| 112 |

|

|

|

| 113 |

|

|

**) A quite promising experimental mode to allow implicit multiplier usage (just write A*B in your code and the compiler

|

| 114 |

|

|

will automatically utilize the multiplier unit for this)

|

| 115 |

|

|

|

| 116 |

|

|

|

| 117 |

|

|

|

| 118 |

|

|

## Top Entity

|

| 119 |

|

|

|

| 120 |

|

|

The top entity of the processor is [**neo430_top.vhd**](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_top.vhd) (from the rtl\core folder).

|

| 121 |

|

|

Just instantiate this file in your project and you are ready to go! All signals of this top entity are of type *std_ulogic* or *std_ulogic_vector*, respectively.

|

| 122 |

|

|

If you need a top entity with resolved signals (*std_logic*), take a look at the [top_templates](https://github.com/stnolting/neo430/blob/master/rtl/top_templates) folder.

|

| 123 |

|

|

These alternative top entities also support AXI or Avalon connectivity.

|

| 124 |

|

|

|

| 125 |

|

|

|

| 126 |

|

|

### Generics

|

| 127 |

|

|

|

| 128 |

|

|

The main features and the actually implemented peripheral modules are configured via the top unit's generics.

|

| 129 |

|

|

|

| 130 |

|

|

| Generic Name | Type | Default Value | Function |

|

| 131 |

|

|

|:-------------|:-----------------------:|:-------------:|:---------------------------------------------------------|

|

| 132 |

|

|

| CLOCK_SPEED | natural | 100000000 | Clock speed of CPU clock input "clk_i" in Hz |

|

| 133 |

|

|

| IMEM_SIZE | natural | 4*1024 | Size of internal instruction memory in bytes (max 48 kB) |

|

| 134 |

|

|

| DMEM_SIZE | natural | 2*1024 | Size of internal data memory in bytes (max 12 kB) |

|

| 135 |

|

|

| USER_CODE | std_ulogic_vector(15:0) | x"0000" | 16-bit custom user code, can be read by user software |

|

| 136 |

|

|

| MULDIV_USE | boolean | true | Implement multiplier/divider unit (MULDIV) |

|

| 137 |

|

|

| WB32_USE | boolean | true | Implement Wishbone interface adapter (WB32) |

|

| 138 |

|

|

| WDT_USE | boolean | true | Implement watchdog timer (WDT) |

|

| 139 |

|

|

| GPIO_USE | boolean | true | Implement general purpose parallel in/out port (GPIO) |

|

| 140 |

|

|

| TIMER_USE | boolean | true | Implement high-precision timer (TIMER) |

|

| 141 |

|

|

| UART_USE | boolean | true | Implement UART serial communication unit (UART) |

|

| 142 |

|

|

| CRC_USE | boolean | true | Implement checksum computation unit (CRC16/32) |

|

| 143 |

|

|

| CFU_USE | boolean | false | Implement custom functions unit (CFU) |

|

| 144 |

|

|

| PWM_USE | boolean | true | Implement pulse width controller (PWM) |

|

| 145 |

|

|

| TWI_USE | boolean | true | Implement two wire serial interface unit (TWI) |

|

| 146 |

|

|

| SPI_USE | boolean | true | Implement serial peripheral interface unit (SPI) |

|

| 147 |

|

|

| TRNG_USE | boolean | false | Implement true random number generator (TRNG) |

|

| 148 |

|

|

| EXIRQ_USE | boolean | true | Implement external interrupts controller (EXIRQ) |

|

| 149 |

|

|

| FREQ_GEN_USE | boolean | true | Implement programmable frequency generator (FREQ_GEN) |

|

| 150 |

|

|

| BOOTLD_USE | boolean | true | Implement and auto-start internal bootloader |

|

| 151 |

|

|

| IMEM_AS_ROM | boolean | false | Implement internal instruction memory as read-only |

|

| 152 |

|

|

|

| 153 |

|

|

|

| 154 |

|

|

### Signals

|

| 155 |

|

|

|

| 156 |

|

|

Regarding unused unit's signals: Connect all unused inputs to low and leave all unused outputs 'open'.

|

| 157 |

|

|

Signal driections are seen from the processor.

|

| 158 |

|

|

|

| 159 |

|

|

| Signal Name | Width | Direction | HW Unit | Function |

|

| 160 |

|

|

|:-------------|:-----:|:---------:|:--------:|:---------------------------------------------------------|

|

| 161 |

|

|

| clk_i | 1 | In | - | Global clock line; all FFs triggering on rising edge |

|

| 162 |

|

|

| rst_i | 1 | In | - | Global reset, low-active |

|

| 163 |

|

|

| gpio_o | 16 | Out | GPIO | General purpose parallel output |

|

| 164 |

|

|

| gpio_i | 16 | In | GPIO | General purpose parallel input |

|

| 165 |

|

|

| pwm_o | 4 | Out | PWM | Pulse width modulation channels |

|

| 166 |

|

|

| timer_fg_o | 1 | Out | FREQ_GEN | Programmable frequency generator output |

|

| 167 |

|

|

| uart_txd_o | 1 | Out | UART | UART serial transmitter |

|

| 168 |

|

|

| uart_rxd_i | 1 | In | UART | UARt serial receiver |

|

| 169 |

|

|

| spi_sclk_o | 1 | Out | SPI | SPI master clock |

|

| 170 |

|

|

| spi_mosi_o | 1 | Out | SPI | SPI serial data output |

|

| 171 |

|

|

| spi_miso_i | 1 | In | SPI | SPI serial data input |

|

| 172 |

|

|

| spi_cs_o | 8 | Out | SPI | SPI chip select lines (active-low) |

|

| 173 |

|

|

| twi_sda_io | 1 | InOut | TWI | TWI master serial data line (external pull-up required) |

|

| 174 |

|

|

| twi_scl_io | 1 | InOut | TWI | TWI master serial clock line (external pull-up required) |

|

| 175 |

|

|

| wb_adr_o | 32 | Out | WB32 | Wishbone slave address |

|

| 176 |

|

|

| wb_dat_i | 32 | In | WB32 | Wishbone write data |

|

| 177 |

|

|

| wb_dat_o | 32 | Out | WB32 | Wishbone read data |

|

| 178 |

|

|

| wb_we_o | 1 | Out | WB32 | Wishbone write enable |

|

| 179 |

|

|

| wb_sel_o | 1 | Out | WB32 | Wishbone byte enable |

|

| 180 |

|

|

| wb_stb_o | 1 | Out | WB32 | Wishbone strobe |

|

| 181 |

|

|

| wb_cyc_o | 1 | Out | WB32 | Wishbone valid cycle |

|

| 182 |

|

|

| wb_ack_i | 1 | In | WB32 | Wishbone transfer acknowledge |

|

| 183 |

|

|

| ext_irq_i | 8 | In | EXIRQ | Interrupt request lines, high-active |

|

| 184 |

|

|

| ext_ack_o | 8 | Out | EXIRQ | Interrupt acknowledge, high-active, single-shot |

|

| 185 |

|

|

|

| 186 |

|

|

|

| 187 |

|

|

|

| 188 |

|

|

## FPGA Implementation Results

|

| 189 |

|

|

|

| 190 |

|

|

Mapping results generated for HW version 0x0406. The full (default) hardware configuration includes

|

| 191 |

|

|

all optional processor modules (excluding the CFU and the TRNG), an IMEM size of 4kB and a DMEM

|

| 192 |

|

|

size of 2kB. The minimal configuration only includes the CPU (including IMEM and DMEM) and the GPIO module.

|

| 193 |

|

|

Results generated with Xilinx Vivado 2019.2, Intel Quartus Prime Lite 17.1 and Lattice Radiant 1.1 (Synplify)

|

| 194 |

|

|

|

| 195 |

|

|

| __Xilinx Artix-7 (XC7A35TICSG324-1L)__ | LUTs | FFs | BRAMs | DSPs | f_max* |

|

| 196 |

|

|

|:---------------------------------------|:---------:|:------------:|:--------:|:------:|:-------:|

|

| 197 |

|

|

| Full (default) configuration: | 1036 (5%) | 1144 (2.75%) | 2.5 (5%) | 0 (0%) | 100 MHz |

|

| 198 |

|

|

| Minimal configuration (CPU + GPIO): | 576 (3%) | 266 (0.6%) | 1 (2%) | 0 (0%) | 100 MHz |

|

| 199 |

|

|

|

| 200 |

|

|

| __Intel Cyclone IV (EP4CE22F17C6)__ | LUTs | FFs | Memory bits | DSPs | f_max |

|

| 201 |

|

|

|:------------------------------------|:---------:|:---------:|:-----------:|:------:|:-------:|

|

| 202 |

|

|

| Full (default) configuration: | 1869 (8%) | 1137 (5%) | 65800 (11%) | 0 (0%) | 121 MHz |

|

| 203 |

|

|

| Minimal configuration (CPU + GPIO): | 590 (3%) | 230 (1%) | 49408 (8%) | 0 (0%) | 122 MHz |

|

| 204 |

|

|

|

| 205 |

|

|

| __Lattice iCE40 UltraPlus** (iCE40UP5K-SG48I)__ | LUTs | FFs | EBRs | DSPs | SPRAMs | f_max* |

|

| 206 |

|

|

|:-------------------------------------------------|:----------:|:----------:|:-------:|:------:|:-------:|:---------:|

|

| 207 |

|

|

| Full (default) configuration: | 3928 (74%) | 1923 (36%) | 9 (30%) | 0 (0%) | 2 (50%) | 20.25 MHz |

|

| 208 |

|

|

| Minimal configuration (CPU + GPIO + Bootloader): | 1812 (34%) | 755 (14%) | 4 (13%) | 0 (0%) | 2 (50%) | 20.25 MHz |

|

| 209 |

|

|

|

| 210 |

|

|

*) Constrained

|

| 211 |

|

|

|

| 212 |

|

|

**) Using optimized memory modules for IMEM (32kB) & DMEM (12kB) from the `rtl\fpga_specific\lattice_ice40up` folder

|

| 213 |

|

|

|

| 214 |

|

|

|

| 215 |

|

|

### Device Utilization by Entity

|

| 216 |

|

|

|

| 217 |

|

|

The following table shows the required resources for each module of the NEO430 processor system. Note that the provided

|

| 218 |

|

|

numbers only represent a coarse overview as logic elements might be merged and optimized beyond entity boundaries.

|

| 219 |

|

|

|

| 220 |

|

|

Mapping results generated for HW version 0x0406. The full (default) hardware configuration includes all optional

|

| 221 |

|

|

processor modules (excluding the CFU but including the TRNG), an IMEM size of 4kB and a DMEM size of

|

| 222 |

|

|

2kB. Results were generated using Intel Quartus Prime Lite 17.1.

|

| 223 |

|

|

|

| 224 |

|

|

| __Intel Cyclone IV (EP4CE22F17C6)__ | LUTs | FFs | Memory Bits | DSPs |

|

| 225 |

|

|

|:---------------------------------------|:----:|:---:|:-----------:|:----:|

|

| 226 |

|

|

| Bootloader Memory (Boot ROM, 2kB) | 2 | 1 | 16384 | 0 |

|

| 227 |

|

|

| Central Processing Unit (CPU) | 525 | 169 | 264 | 0 |

|

| 228 |

|

|

| Checksum Unit (CRC) | 111 | 94 | 0 | 0 |

|

| 229 |

|

|

| Custom Functions Unit (CFU)* | - | - | - | - |

|

| 230 |

|

|

| Data Memory (DMEM, 2kB) | 5 | 1 | 16384 | 0 |

|

| 231 |

|

|

| External Interrupts Controller (EXIRQ) | 70 | 55 | 0 | 0 |

|

| 232 |

|

|

| Frequency Generator (FREQ_GEN) | 140 | 130 | 0 | 0 |

|

| 233 |

|

|

| GPIO Port Unit (GPIO) | 50 | 45 | 0 | 0 |

|

| 234 |

|

|

| High-Precision Timer (TIMER) | 66 | 57 | 0 | 0 |

|

| 235 |

|

|

| Instruction Memory (IMEM, 4kB) | 5 | 1 | 32768 | 0 |

|

| 236 |

|

|

| Multiplier & Divider (MULDIV) | 209 | 134 | 0 | 0 |

|

| 237 |

|

|

| Pulse-Width Modulation Unit (PWM) | 96 | 66 | 0 | 0 |

|

| 238 |

|

|

| Serial Peripheral Interface (SPI) | 82 | 59 | 0 | 0 |

|

| 239 |

|

|

| System Info Memory (SYSCONFIG) | 12 | 11 | 0 | 0 |

|

| 240 |

|

|

| True Random Number Generator (TRNG) | 92 | 76 | 0 | 0 |

|

| 241 |

|

|

| Two Wire Interface (TWI) | 78 | 43 | 0 | 0 |

|

| 242 |

|

|

| Universal Asynchronous Rx/Tx (UART) | 130 | 91 | 0 | 0 |

|

| 243 |

|

|

| Watchdog Timer (WDT) | 53 | 37 | 0 | 0 |

|

| 244 |

|

|

| Wishbone Interface (WB32) | 129 | 117 | 0 | 0 |

|

| 245 |

|

|

|

| 246 |

|

|

*) Hardware requirements defined by user application

|

| 247 |

|

|

|

| 248 |

|

|

|

| 249 |

|

|

|

| 250 |

|

|

## HW-SW Ecosystem

|

| 251 |

|

|

|

| 252 |

|

|

The NEO430 Processor project provides driver libraries for the CPU itself and all included peripheral modules. These libraries

|

| 253 |

|

|

provide a certain level of hardware abstraction and allow an easy usage of the different hardware modules. Modules that cannot

|

| 254 |

|

|

be used "explicitly" (like CPU modules or the different memories) are not listed below.

|

| 255 |

|

|

|

| 256 |

|

|

| Hardware unit | VHDL source | C library source | C library header | SW example project |

|

| 257 |

|

|

|:---------------------------------------|:-----------:|:----------------:|:----------------:|:------------------:|

|

| 258 |

|

|

| Main CPU defines file | - | - | [neo430.h](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/include/neo430.h) | - |

|

| 259 |

|

|

| Central Processing Unit (CPU) | [neo430_cpu.vhd](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_cpu.vhd) | [neo430_cpu.c](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/source/neo430_cpu.c) | [neo430_cpu.h](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/include/neo430_cpu.h) |- |

|

| 260 |

|

|

| Custom Functions Unit (CFU) | [neo430_cfu.vhd](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_cfu.vhd) | provided by CFU designer | provided by CFU designer | [example](https://github.com/stnolting/neo430/tree/master/sw/example/cfu_test) |

|

| 261 |

|

|

| Checksum Unit (CRC16/32) | [neo430_crc.vhd](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_crc.vhd) | [neo430_crc.c](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/source/neo430_crc.c) | [neo430_crc.h](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/include/neo430_crc.h) | [example](https://github.com/stnolting/neo430/tree/master/sw/example/crc_test) |

|

| 262 |

|

|

| External Interrupts Controller (EXIRQ) | [neo430_exirq.vhd](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_exirq.vhd) | [neo430_exirq.c](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/source/neo430_exirq.c) | [neo430_exirq.h](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/include/neo430_exirq.h) | [example](https://github.com/stnolting/neo430/tree/master/sw/example/exirq_test) |

|

| 263 |

|

|

| Frequency Generator (FREQ_GEN) | [neo430_freq_gen.vhd](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_freq_gen.vhd) | [neo430_freq_gen.c](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/source/neo430_freq_gen.c) | [neo430_freq_gen.h](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/include/neo430_freq_gen.h) | [example](https://github.com/stnolting/neo430/tree/master/sw/example/freq_gen_demo) |

|

| 264 |

|

|

| IO Port Unit (GPIO) | [neo430_gpio.vhd](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_gpio.vhd) | [neo430_gpio.c](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/source/neo430_gpio.c) | [neo430_gpio.h](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/include/neo430_gpio.h) | [example](https://github.com/stnolting/neo430/tree/master/sw/example/blink_led) |

|

| 265 |

|

|

| Multiplier & Divider (MULDIV) | [neo430_muldiv.vhd](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_muldiv.vhd) | [neo430_muldiv.c](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/source/neo430_muldiv.c) | [neo430_muldiv.h](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/include/neo430_muldiv.h) | [example](https://github.com/stnolting/neo430/tree/master/sw/example/muldiv_test) |

|

| 266 |

|

|

| Pulse-Width Modulation Unit (PWM) | [neo430_pwm.vhd](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_pwm.vhd) | [neo430_pwm.c](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/source/neo430_pwm.c) | [neo430_pwm.h](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/include/neo430_pwm.h) | [example](https://github.com/stnolting/neo430/tree/master/sw/example/pwm_demo) |

|

| 267 |

|

|

| Serial Peripheral Interface (SPI) | [neo430_spi.vhd](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_spi.vhd) | [neo430_spi.c](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/source/neo430_spi.c) | [neo430_spi.h](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/include/neo430_spi.h) | [example](https://github.com/stnolting/neo430/tree/master/sw/bootloader) |

|

| 268 |

|

|

| High-Precision Timer (TIMER) | [neo430_timer.vhd](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_timer.vhd) | [neo430_timer.c](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/source/neo430_timer.c) | [neo430_timer.h](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/include/neo430_timer.h) | [example](https://github.com/stnolting/neo430/tree/master/sw/example/timer_simple) |

|

| 269 |

|

|

| True Random Number Generator (TRNG) | [neo430_trng.vhd](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_trng.vhd) | [neo430_trng.c](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/source/neo430_trng.c) | [neo430_trng.h](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/include/neo430_trng.h) | [example](https://github.com/stnolting/neo430/tree/master/sw/example/trng_test) |

|

| 270 |

|

|

| Two Wire Interface (TWI) | [neo430_twi.vhd](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_twi.vhd) | [neo430_twi.c](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/source/neo430_twi.c) | [neo430_twi.h](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/include/neo430_twi.h) | [example](https://github.com/stnolting/neo430/tree/master/sw/example/twi_test) |

|

| 271 |

|

|

| Universal Asynchronous Rx/Tx (UART) | [neo430_uart.vhd](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_uart.vhd) | [neo430_uart.c](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/source/neo430_uart.c) | [neo430_uart.h](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/include/neo430_uart.h) | [example](https://github.com/stnolting/neo430/tree/master/sw/example/uart_irq) |

|

| 272 |

|

|

| Watchdog Timer (WDT) | [neo430_wdt.vhd](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_wdt.vhd) | [neo430_wdt.c](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/source/neo430_wdt.c) | [neo430_wdt.h](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/include/neo430_wdt.h) | [example](https://github.com/stnolting/neo430/tree/master/sw/example/wdt_test) |

|

| 273 |

|

|

| Wishbone Interface (WB32) | [neo430_wb_interface.vhd](https://github.com/stnolting/neo430/blob/master/rtl/core/neo430_wb_interface.vhd) | [neo430_wishbone.c](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/source/neo430_wishbone.c) | [neo430_wishbone.h](https://github.com/stnolting/neo430/blob/master/sw/lib/neo430/include/neo430_wishbone.h) | [example](https://github.com/stnolting/neo430/tree/master/sw/example/wb_terminal) |

|

| 274 |

|

|

|

| 275 |

|

|

All software projects are compiled using an [application makefile](https://github.com/stnolting/neo430/blob/master/sw/example/blink_led/makefile).

|

| 276 |

|

|

|

| 277 |

|

|

|

| 278 |

|

|

## Performance

|

| 279 |

|

|

|

| 280 |

|

|

In contrast to most mainstream processors the NEO430 processor does not implement a "classic" pipelined instruction execution. Instead,

|

| 281 |

|

|

a **multi-cycle instruction execution scheme** is used: Each single instruction is executed in a series of micro instructions

|

| 282 |

|

|

requiring several clock cycles to complete. The main benefit of this execution style is the highly reduced logic overhead as no

|

| 283 |

|

|

complex pipeline hazard detection and resolving logic is required. This makes the NEO430 even smaller - at the cost of a reduced IPC

|

| 284 |

|

|

(*instructions per cycle*). Also, the MSP430 ISA is not really compatible to the classic (DLX/MIPS-like) pipeline scheme due to

|

| 285 |

|

|

its complex operand and adressing modes (e.g., ALU operations executing directly on memory data). However, this concept allows

|

| 286 |

|

|

the processor to use very **dense and powerfull CISC-like operations**.

|

| 287 |

|

|

|

| 288 |

|

|

Furthermore, the multi-cycle architecture features a **very short crtitical path** when compared to other (even 32-bit)

|

| 289 |

|

|

processors. Thus, the NEO430 can operate at very high frequencies even on low-cost (e.g., +120MHz on an Intel Cyclone IV)

|

| 290 |

|

|

and low-power FPGAs (e.g., +20MHz on a Lattice iCE40 UltraPlus) even without any area constraints.

|

| 291 |

|

|

|

| 292 |

|

|

Depending on the format / operand addressing mode of an instruction, the actual execution can take 3 to 10 clock cycles. If all possible instruction

|

| 293 |

|

|

types and formats are executed in an equally distributed manner (this is the worst case), the average CPI (clock cycles per instruction)

|

| 294 |

|

|

evaluates to **7.33 cycles/instruction resulting in 0.136 MIPS per MHz (again: worst case)**.

|

| 295 |

|

|

|

| 296 |

|

|

|

| 297 |

|

|

### CoreMark Benchmark

|

| 298 |

|

|

|

| 299 |

|

|

The [CoreMark CPU benchmark](https://www.eembc.org/coremark/) was executed on the NEO430 and is available in the

|

| 300 |

|

|

[sw/example/coremark](https://github.com/stnolting/neo430/blob/master/sw/example/coremark) project folder This benchmark

|

| 301 |

|

|

tests the capabilities of a CPU itself rather than the functions provided by the whole system / SoC.

|

| 302 |

|

|

|

| 303 |

|

|

~~~

|

| 304 |

|

|

Configuration

|

| 305 |

199 |

zero_gravi |

Hardware: 100 MHz, 32kB IMEM, 12kB DMEM, HW verison 0x0407, peripherals used: TIMER, UART, MULDIV

|

| 306 |

198 |

zero_gravi |

Software: msp430-gcc 8.3.0 for Linux, MEM_METHOD is MEM_STACK, 2000 CoreMark iterations

|

| 307 |

|

|

~~~

|

| 308 |

|

|

|

| 309 |

|

|

| __Optimization/Configuration__ | __Executable Size__ | __CoreMark Score__ | __Relative Score__ |

|

| 310 |

|

|

|:-------------------------------|:-------------------:|:------------------:|:-------------------:|

|

| 311 |

|

|

| -Os | 12150 bytes | 6.57 | 0.065 CoreMarks/MHz |

|

| 312 |

|

|

| -O2 | 14600 bytes | 7.16 | 0.072 CoreMarks/MHz |

|

| 313 |

|

|

| -Os + NEO430_MULDIV* | 12118 bytes | 14.43 | 0.144 CoreMarks/MHz |

|

| 314 |

|

|

| -O2 + NEO430_MULDIV* | 14562 bytes | 17.68 | 0.176 CoreMarks/MHz |

|

| 315 |

|

|

| -Os + NEO430_MULDIV* (DSP**) | 12060 bytes | 15.63 | 0.156 CoreMarks/MHz |

|

| 316 |

|

|

| -O2 + NEO430_MULDIV* (DSP**) | 14510 bytes | 19.42 | 0.194 CoreMarks/MHz |

|

| 317 |

|

|

|

| 318 |

|

|

*) These results were generated using the "NEO430_HWMUL_ABI_OVERRIDE" feature flag, which allows to map implicit multiplications

|

| 319 |

|

|

in the source code via compiler primitives directly to the multiplier core of the MULDIV unit. For more information see

|

| 320 |

|

|

chapter "Multiplier and Divider Unit (MULDIV)" of [NEO430.pdf](https://raw.githubusercontent.com/stnolting/neo430/master/doc/NEO430.pdf).

|

| 321 |

|

|

|

| 322 |

|

|

**) This setup uses the FPGA's embedded multipliers (DSP blocks) for the MULDIV's multiplier unit. The "NEO430_HWMUL_DSP" feature flag eliminates

|

| 323 |

|

|

the wait cycles usually required to wait for the result generated by the default serial MULDIV multiplier core.

|

| 324 |

|

|

|

| 325 |

|

|

Even though a score of 6.57 can outnumber certain architectures and configurations (see the score table on the CoreMark

|

| 326 |

|

|

homepage), the relative score of 0.065 coremarks per second might sound pretty low. True. But you have to keep in mind that benchmark

|

| 327 |

|

|

was executed using only the resources of the CPU itself. The CPU consists of only ~520 Intel Cyclone IV LUTs and does not

|

| 328 |

|

|

contain any sophisticated ALU operations like multiplication or barrel shifting. When including NEO430 MULDIV unit (using the

|

| 329 |

|

|

"NEO430_HWMUL_ABI_OVERRIDE" feature and using embedded DSP blocks ("NEO430_HWMUL_DSP")) the CoreMark score is increased to 19.42.

|

| 330 |

|

|

By explicitly using additional HW accelerators from the NEO430 ecosystem (e.g. the CRC unit) the performance can be further increased.

|

| 331 |

|

|

|

| 332 |

|

|

|

| 333 |

|

|

|

| 334 |

|

|

## Quick Start

|

| 335 |

|

|

|

| 336 |

|

|

* At first, get the most recent version the NEO430 Processor project from GitHub:

|

| 337 |

|

|

|

| 338 |

|

|

* Clone the NEO430 repository using `git` from the command line (suggested for easy project updates via `git pull`):

|

| 339 |

|

|

|

| 340 |

|

|

~~~

|

| 341 |

|

|

git clone https://github.com/stnolting/neo430.git

|

| 342 |

|

|

~~~

|

| 343 |

|

|

|

| 344 |

|

|

* Or download the current version of this project as ZIP file: [neo430-master.zip](https://github.com/stnolting/neo430/archive/master.zip)

|

| 345 |

|

|

|

| 346 |

|

|

* Next, install the free `MSP430-GCC` compiler toolchain from the TI homepage (select the "compiler only" package according to your system OS):

|

| 347 |

|

|

|

| 348 |

|

|

https://software-dl.ti.com/msp430/msp430_public_sw/mcu/msp430/MSPGCC/latest/index_FDS.html

|

| 349 |

|

|

|

| 350 |

|

|

* Alternatively, you can [directly download a copy](https://github.com/stnolting/msp430-gcc) of the msp430-gcc toolchain for Windows/Linux from github

|

| 351 |

|

|

|

| 352 |

|

|

* Make sure `GNU Make` and a native `GCC` compiler are installed (double check for the newest versions)

|

| 353 |

|

|

|

| 354 |

|

|

* Create a new HW project with your FPGA synthesis tool of choice. Add all files from the `rtl\core` folder to this project (and add them to a new library called "neo430").

|

| 355 |

|

|

|

| 356 |

|

|

* Follow the instructions from the "Let's Get It Started" section of the NEO430 documentary: [ NEO430 Datasheet](https://raw.githubusercontent.com/stnolting/neo430/master/doc/NEO430.pdf "NEO430 Datasheet from GitHub")

|

| 357 |

|

|

|

| 358 |

|

|

* This documentary will guide you to create a simple test setup, which serves as ["hello word" FPGA demo](https://github.com/stnolting/neo430/blob/master/rtl/top_templates/neo430_test.vhd):

|

| 359 |

|

|

|

| 360 |

|

|

|

| 361 |

|

|

|

| 362 |

|

|

* The NEO430 project also includes some example programs from which you can start your own application: [SW example projects](https://github.com/stnolting/neo430/tree/master/sw/example)

|

| 363 |

|

|

|

| 364 |

|

|

* Have fun! =)

|

| 365 |

|

|

|

| 366 |

|

|

|

| 367 |

|

|

|

| 368 |

|

|

## Change Log

|

| 369 |

|

|

|

| 370 |

|

|

The official change log of this project can be found at the end of the [ NEO430 Datasheet](https://raw.githubusercontent.com/stnolting/neo430/master/doc/NEO430.pdf "NEO430 Datasheet from GitHub").

|

| 371 |

|

|

|

| 372 |

|

|

|

| 373 |

|

|

|

| 374 |

|

|

## Contact

|

| 375 |

|

|

|

| 376 |

|

|

If you have any questions, bug reports, ideas or if you are facing problems with the NEO430 or want to give some kinf of feedback, open a

|

| 377 |

|

|

[new issue](https://github.com/stnolting/neo430/issues) or directly drop me a line:

|

| 378 |

|

|

|

| 379 |

|

|

stnolting@gmail.com

|

| 380 |

|

|

|

| 381 |

|

|

|

| 382 |

|

|

|

| 383 |

|

|

## Citation

|

| 384 |

|

|

|

| 385 |

|

|

If you are using the NEO430 Processor in some kind of publication, please cite it as follows:

|

| 386 |

|

|

|

| 387 |

|

|

> S. Nolting, "The NEO430 Processor", github.com/stnolting/neo430

|

| 388 |

|

|

|

| 389 |

|

|

|

| 390 |

|

|

|

| 391 |

|

|

## Disclaimer, Proprietary and Legal Notice

|

| 392 |

|

|

|

| 393 |

|

|

This is a hobby project released under the BSD 3-Clause license. No copyright infringement intended.

|

| 394 |

|

|

|

| 395 |

|

|

**BSD 3-Clause License**

|

| 396 |

|

|

|

| 397 |

|

|

Copyright (c) 2020, Stephan Nolting. All rights reserved.

|

| 398 |

|

|

|

| 399 |

|

|

Redistribution and use in source and binary forms, with or without modification, are

|

| 400 |

|

|

permitted provided that the following conditions are met:

|

| 401 |

|

|

|

| 402 |

|

|

1. Redistributions of source code must retain the above copyright notice, this list of

|

| 403 |

|

|

conditions and the following disclaimer.

|

| 404 |

|

|

2. Redistributions in binary form must reproduce the above copyright notice, this list of

|

| 405 |

|

|

conditions and the following disclaimer in the documentation and/or other materials

|

| 406 |

|

|

provided with the distribution.

|

| 407 |

|

|

3. Neither the name of the copyright holder nor the names of its contributors may be used to

|

| 408 |

|

|

endorse or promote products derived from this software without specific prior written

|

| 409 |

|

|

permission.

|

| 410 |

|

|

|

| 411 |

|

|

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS

|

| 412 |

|

|

OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF

|

| 413 |

|

|

MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE

|

| 414 |

|

|

COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL,

|

| 415 |

|

|

EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE

|

| 416 |

|

|

GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED

|

| 417 |

|

|

AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING

|

| 418 |

|

|

NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED

|

| 419 |

|

|

OF THE POSSIBILITY OF SUCH DAMAGE.

|

| 420 |

|

|

|

| 421 |

|

|

|

| 422 |

|

|

"MSP430" and "Code Composer Studio" are trademarks of Texas Instruments Corporation.

|

| 423 |

|

|

|

| 424 |

|

|

"Windows" is a trademark of Microsoft Corporation.

|

| 425 |

|

|

|

| 426 |

|

|

"Virtex", "Artix" and "Vivado" are trademarks of Xilinx Inc.

|

| 427 |

|

|

|

| 428 |

|

|

"Cyclone", "Quartus" and "Avalon Bus" are trademarks of Intel Corporation.

|

| 429 |

|

|

|

| 430 |

|

|

"iCE40 UltraPlus", "Lattice Radiant" and "Lattice Diamond" are trademarks of Lattice Semiconductor Corporation.

|

| 431 |

|

|

|

| 432 |

|

|

"AXI", "AXI4" and "AXI4-Lite" are trademarks of Arm Holdings plc.

|

| 433 |

|

|

|

| 434 |

|

|

|

| 435 |

|

|

[](https://travis-ci.com/stnolting/neo430)

|

| 436 |

|

|

|

| 437 |

|

|

Continous integration provided by [Travis CI](https://travis-ci.com/stnolting/neo430).

|

| 438 |

|

|

|

| 439 |

|

|

|

| 440 |

|

|

|

| 441 |

|

|

|

| 442 |

|

|

This project is not affiliated with or endorsed by the Open Source Initiative (https://www.oshwa.org / https://opensource.org).

|

| 443 |

|

|

|

| 444 |

|

|

|

| 445 |

|

|

Made with :beer: in Hannover, Germany.

|