# Point-to-point protocol exploration

Nayib Boukadida

June 29, 2018

Supervised by F. Schreuder<sup>1</sup>, A. Borga<sup>1</sup>, P. Jansweijer<sup>1</sup> and W.E. Dolman<sup>2</sup>

<sup>1</sup>Nikhef, <sup>2</sup>Amsterdam University of Applied Sciences

# **Version history**

| Version | Date          | Changes                                                                                                                      |

|---------|---------------|------------------------------------------------------------------------------------------------------------------------------|

| 1.0     | 16 Mar. 2018  | Finished first concept                                                                                                       |

| 1.1     | 27 Mar. 2018  | Changed lay-out, added clearer explanation of protocols removed code appendix and included the OSI model                     |

| 1.2     | 10 Apr. 2018  | Added a section dedicated to Interlaken, completely rewritten the hardware implementation and added a list of Figures/Tables |

| 1.3     | 23 Apr. 2018  | Added microsemi LiteFast, improved referencing                                                                               |

| 1.4     | 29 May. 2018  | Corrected grammar/spelling mistakes, added appendix of obtaining and configuring Core1990                                    |

| 1.5     | 29 June. 2018 | Expanded Core1990 appendix and added test results. Improved the implementation description                                   |

# **Contents**

| 1 | Intro           | oduction                                        | 9            |

|---|-----------------|-------------------------------------------------|--------------|

| 2 | <b>Stru</b> 2.1 | cture of communication protocols  The OSI model | <b>11</b> 11 |

|   | 2.2             | Data structure and framing                      | 12           |

|   | 2.3             | Error detection and correction                  | 13           |

|   | 2.4             | Encoding of data                                | 14           |

|   | 2.5             | Serialization and parallelization of data       | 15           |

|   | 2.6             | Protocol overview                               | 16           |

| 3 | Req             | uirements                                       | 17           |

|   | 3.1             | Line rate target                                | 17           |

|   | 3.2             | Range distance coverage                         | 17           |

|   | 3.3             | Forward Error Correction                        | 18           |

|   | 3.4             | Flow control                                    | 18           |

|   | 3.5             | Cyclic Redundancy Check                         | 18           |

|   | 3.6             | Channel bonding                                 | 19           |

| 4 | Line            | encoding and decoding                           | 20           |

|   | 4.1             | 8b/10b                                          | 20           |

|   | 4.2             | 64b/66b                                         | 20           |

|   | 4.3             | 128b/130b - PCle 3.0/4.0                        | 21           |

|   | 4.4             | 128b/132b - USB 3.1                             | 21           |

|   | 4.5             | 256b/257b - Fibrechannel                        | 22           |

|   | 4.6             | 64b/67b - Interlaken/SerialLite                 | 22           |

|   | 4.7             | Scramblers                                      | 23           |

| 5 | FPG             | SA vendor dependent protocols                   | 24           |

|   | 5.1             | Xilinx Aurora                                   | 24           |

|   | 5.2             | Altera/IntelFPGA Serial LITE                    | 25           |

|   | 5.3             | Microsemi LiteFast                              | 25           |

|   | 5.4             | Conclusion                                      | 26           |

| 6 | Ven             | dor independent protocols                       | 27           |

|   | 6.1             | The Interlaken Protocol                         | 27           |

|   | 6.2             | SATA protocol                                   | 28           |

|   | 6.3             | CPRI                                            | 29           |

|   | 6.4             | HyperTransport                                  | 30           |

|   | 6.5             | Fibre channel                                   | 31           |

|   | 6.6             | XAUI                                            | 31           |

|   | 6.7             | Conclusion                                      | 32           |

| 7 | The             | Interlaken Protocol                             | 33           |

|   | 7.1             | Overview                                        | 33           |

|   | 7.2             | Control Word Format                             | 34           |

|   | 7.3             | Bursts                                          | 36           |

|   | -               |                                                 | . •          |

|    | 7.4   | Meta Frame                                             | 88        |

|----|-------|--------------------------------------------------------|-----------|

|    |       | 7.4.1 Synchronization and Scrambler State              | 39        |

|    |       | 7.4.2 Skip Word                                        | 39        |

|    |       | 7.4.3 Diagnostic Word                                  | ŀO        |

|    | 7.5   | Flow Control                                           | ŀ1        |

|    |       | 7.5.1 Out-of-Band Flow Control                         | ŀ1        |

|    |       | 7.5.2 In-Band Flow Control                             | ŀ1        |

|    |       | 7.5.3 Full-Packet Flow Control                         | 12        |

|    | 7.6   | CRC generation                                         | ŀ3        |

|    |       | 7.6.1 CRC-4                                            | ŀ3        |

|    |       | 7.6.2 CRC-24                                           | ŀ3        |

|    |       | 7.6.3 CRC-32                                           | ŀ3        |

|    | 7.7   | Scrambler                                              | ŀ5        |

|    | 7.8   | Encoder                                                | ŀ6        |

| _  |       |                                                        | _         |

| 8  |       | lware implementation 4                                 | _         |

|    | 8.1   | Transmitter side                                       |           |

|    |       |                                                        | 18        |

|    |       |                                                        | 18        |

|    |       |                                                        | 19        |

|    |       | S .                                                    | 19        |

|    |       |                                                        | 0         |

|    | 8.2   |                                                        | 50<br>51  |

|    | 0.2   |                                                        | 51        |

|    |       |                                                        | ) 1<br>51 |

|    |       | 8                                                      | 52        |

|    |       | S .                                                    | 52        |

|    |       | 8                                                      | 52        |

|    |       |                                                        | 53        |

|    | 8.3   |                                                        | ,<br>3    |

|    | 8.4   | Flow control         5           Transceiver         5 |           |

|    | 8.5   | Complete interface                                     |           |

|    | 0.5   | complete interface                                     | , ,       |

| 9  | Test  | runs 5                                                 | 5         |

|    | 9.1   | Early testing                                          | 5         |

|    | 9.2   | Clock troubleshooting                                  | 6         |

|    | 9.3   | Communication between boards                           | 7         |

| 10 | Con   | clusion 5                                              | : n       |

| 10 | Conc  | Ciusion                                                | 9         |

| Re | feren | ces 6                                                  | 0         |

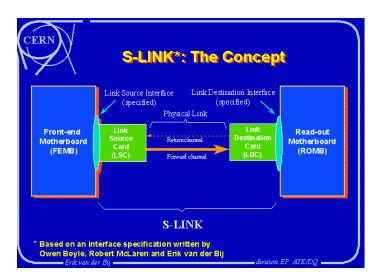

| Α  | Trad  | itional CERN protocols 6                               | 5         |

| -  |       | •                                                      | 55        |

|    |       |                                                        | 66        |

|    | A.3   |                                                        | 6         |

|    | A.4   |                                                        | 6         |

|    |       |                                                        |           |

# Point-to-point protocol exploration

| B Specifications of discussed protocols |      |                                  |    |

|-----------------------------------------|------|----------------------------------|----|

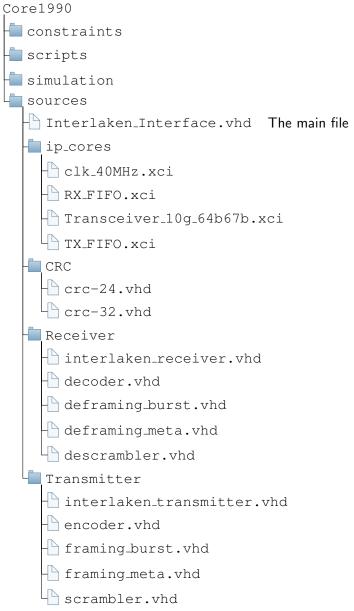

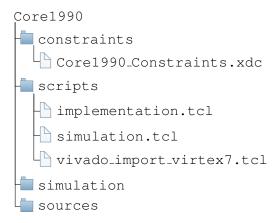

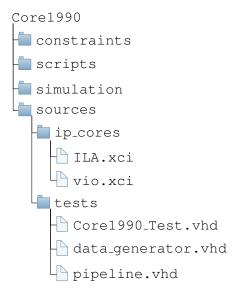

| C                                       | Core | ±1990                            | 68 |

|                                         | C.1  | Features                         | 68 |

|                                         | C.2  | Obtaining and building Core 1990 | 69 |

|                                         | C.3  | Transceiver IP Core              | 71 |

|                                         | C.4  | System Clock IP Core             | 73 |

|                                         | C.5  | FIFO IP Cores                    | 75 |

|                                         | C.6  | Simulating the core              | 75 |

|                                         | C.7  | Example design                   | 75 |

# **List of Figures**

| 1  | An overview of the OSI model                                       | 11 |

|----|--------------------------------------------------------------------|----|

| 2  | CRC division in case data appears flawless or corrupted            | 14 |

| 3  | SerDes gearboxes.                                                  | 15 |

| 4  | Protocol overview according to earlier subsections                 | 16 |

| 5  | The simple Stop and Wait implementation of flow control            | 18 |

| 6  | Transmitting data over different channels using bonding            | 19 |

| 7  | Headers used for 64b/66b encoding                                  | 21 |

| 8  | The header of a 256b/257b transmission containing data             | 22 |

| 9  | The header of a 256b/257b transmission with mixed blocks           | 22 |

| 10 | The Aurora block diagram.                                          | 24 |

| 11 | The SerialLite III block diagram (Simplex mode)                    | 25 |

| 12 | The LiteFast block diagram (Single Lane)                           | 26 |

| 13 | Word formats Interlaken makes use of                               | 27 |

| 14 | Overview of the SATA Express architecture                          | 28 |

| 15 | Overview of the CPRI architecture using FEC                        | 29 |

| 16 | HyperTransport versions and their specifications                   | 30 |

| 17 | Proposed architecture of 64GFC                                     | 31 |

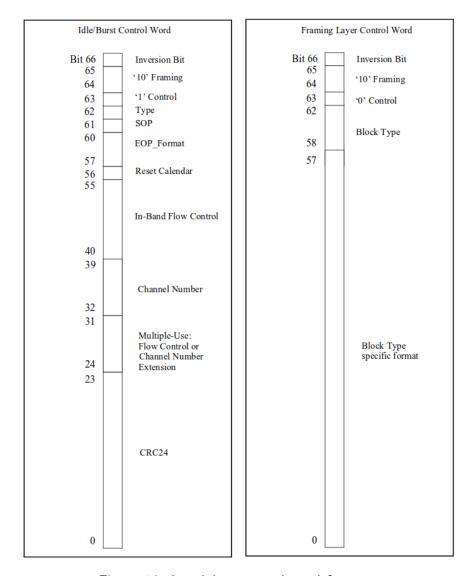

| 19 | Interlaken control word formats                                    | 34 |

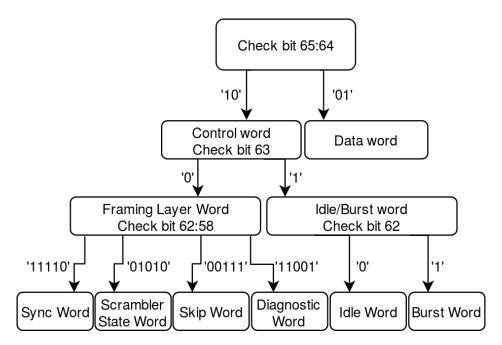

| 20 | A complete overview of word types and their structure              | 35 |

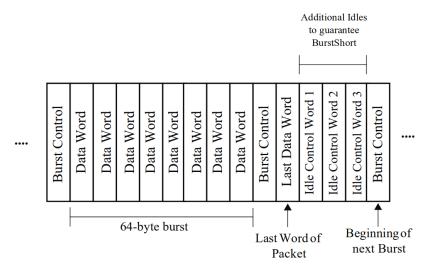

| 21 | An example of a short burst                                        | 36 |

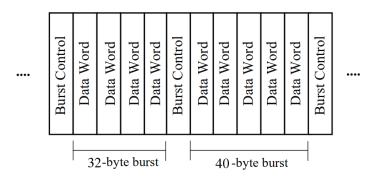

| 22 | An example of a burst without idles                                | 37 |

| 23 | Interlaken Meta Frame structure                                    | 38 |

| 24 | Interlaken framing layer block types                               | 38 |

| 25 | Interlaken lane alignment.                                         | 39 |

| 26 | Interlaken synchronization and scrambler state words               | 39 |

| 27 | Interlaken skip word                                               | 40 |

| 28 | Interlaken diagnostic word                                         | 40 |

| 29 | Interlaken Out-of-Band Flow Control timing diagram                 | 41 |

| 30 | Interlaken CRC-32 calculation                                      | 44 |

| 31 | Preamble of the $64b/67b$ encoding used in the Interlaken protocol | 46 |

| 32 | The Virtex-7 VC707 Board provided by Nikhef                        | 47 |

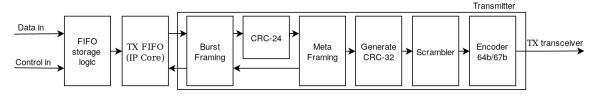

| 33 | Overview of the TX block diagram                                   | 48 |

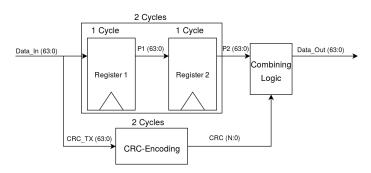

| 34 | Used method generating CRC                                         | 50 |

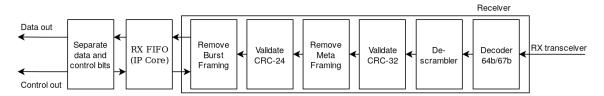

| 35 | Overview of the RX block diagram                                   | 51 |

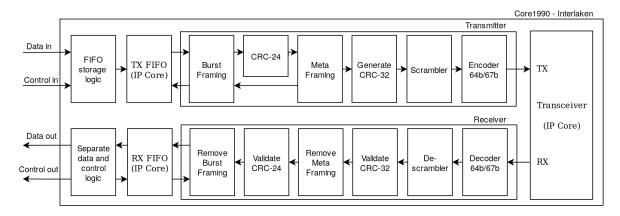

| 36 | Complete Core1990 architecture                                     | 54 |

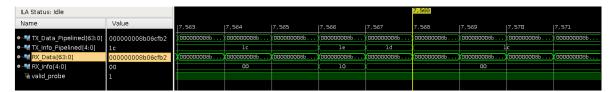

| 37 | The ILA during test                                                | 55 |

| 38 | The full sample range of the ILA during test                       | 55 |

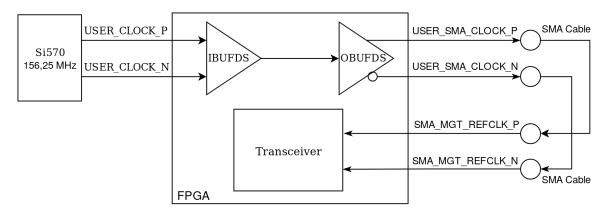

| 39 | Using the Si570 clock on the VC707                                 | 56 |

| 40 | Schematically viewed configuration of the Si570 clock on the VC707 | 57 |

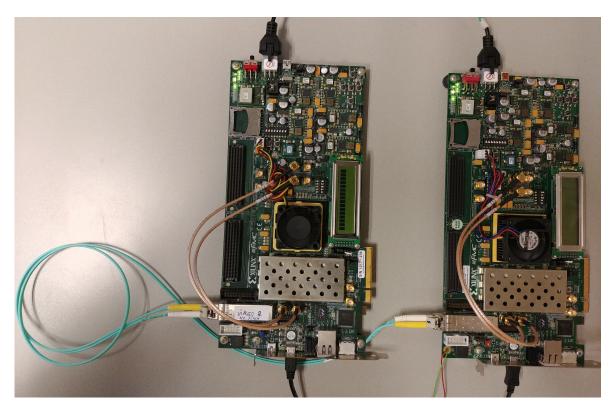

| 41 | Testing communication between two VC707 boards                     | 57 |

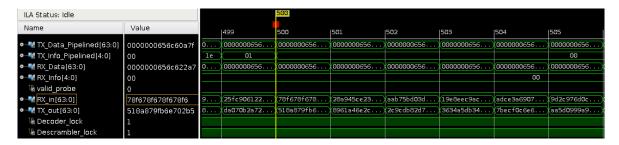

| 42 | Wave forms captured during the communication between VC707 boards  | 58 |

| 43 | S-Link overview.                                                   | 65 |

| 44 | Frame of the GBT procol                                            | 66 |

| 45 | Core1990 logo                                                      | 68 |

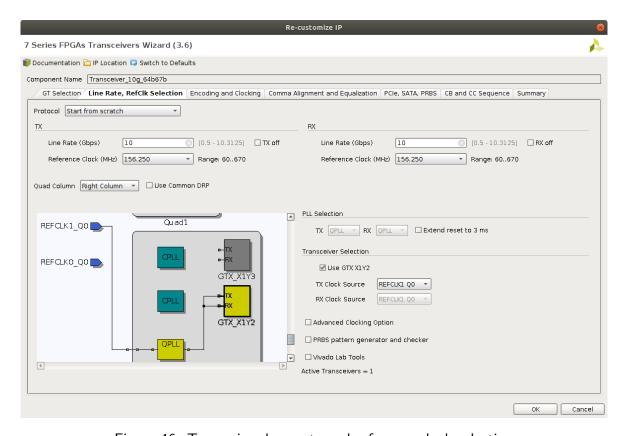

| 46 | Transceiver lane rate and reference clock selection                | 71 |

|    |                                                                    |    |

# Point-to-point protocol exploration

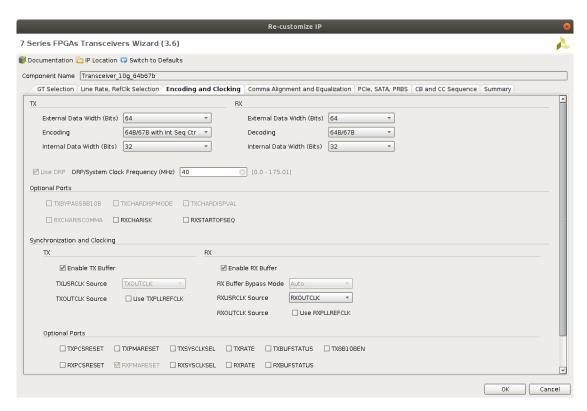

| 47   | Transceiver encoding and system clock selection |

|------|-------------------------------------------------|

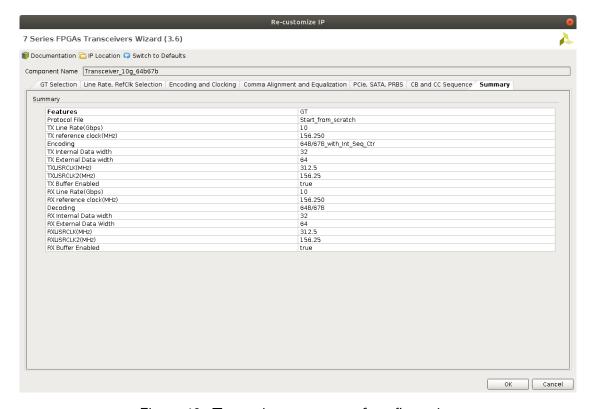

| 48   | Transceiver summary of configuration            |

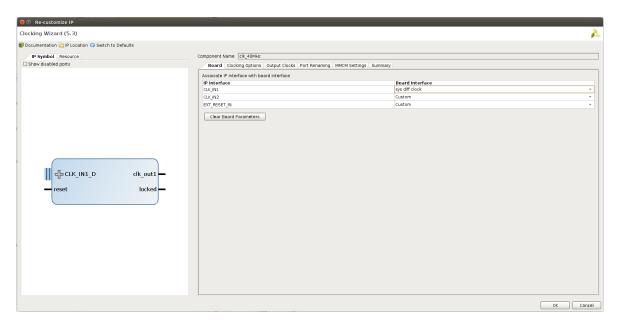

| 49   | System clock setting the board interface        |

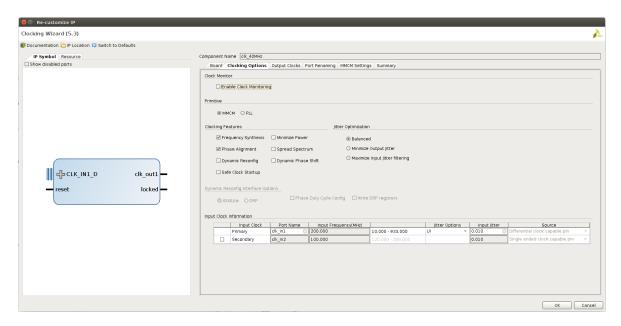

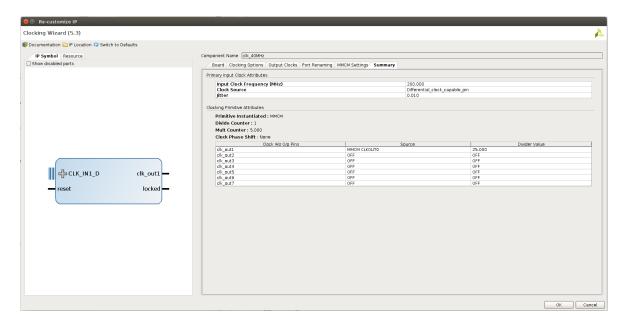

| 50   | System clock setting the options                |

| 51   | System clock configuring the output clock       |

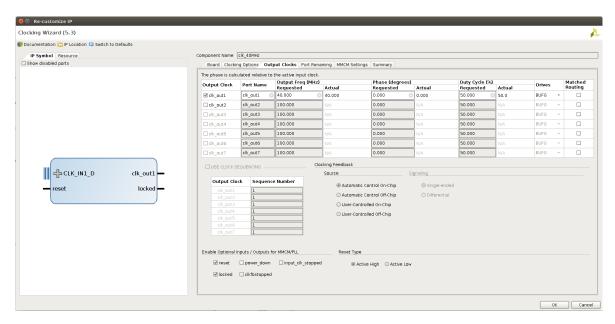

| 52   | System clock summary of configuration           |

|      |                                                 |

| List | of Tables                                       |

| 1    | Overview of the most suited protocols           |

### **Abbreviations**

CERN Conseil Européen pour la Recherche Nucléaire (European Council for Nuclear Research).

CRC Cyclic Redundancy Check (Variants will always be noted with a '-' between CRC and the length).

**EMI** ElectroMagnetic Interference.

FEC Forward Error Correction.

FIFO First In, First Out.

FPGA Field-Programmable Gate Array.

Gbps Gigabit per second.

**GT** Gigabit Transceiver.

**HT** HyperTransport.

ILA Integrated Logic Analizer.

IO Input/Output.

IP core Intellectual Property core.

LFSR Linear-Feedback Shift Register.

MMCM Mixed-Mode Clock Manager.

**NVMe** Non-Volatile Memory Express.

OSI Open Systems Interconnection.

PCIe Peripheral Component Interconnect Express.

PHY PHYsical layer of the OSI model.

**PLL** Phase Locked Loop.

SATA Serial Advanced Technology Attachment.

SerDes Serializer/Deserializer.

SFP Small form-factor pluggable.

SPI System Packet Interface.

VHDL VHSIC (Very High Speed Integrated Circuit) Hardware Description Language.

**VIO** Virtual Input/Output.

**XAUI** X(Ten) Attachment Unit Interface.

### 1 Introduction

This brief introduction covers the motivation to this work, providing a general overview on the assignment, and describing the structure of this report.

Virtually any sort of electronic communication system involving two or more peers requires the use of a protocol<sup>1</sup> to achieve proper information transfer. The nature of such protocol depends on the characteristics of the communication channel and the type of communication that one wants to pursue. A general overview of a communication protocol is given in Chapter 2. Since the protocol is targeting low level communication, a key element of it is the so called transmission encoding/decoding. Common techniques for such purpose are researched in Chapter 4.

Before exploring the commonly available and best suitable protocols, one should set a set of requirements that should be met. Such requirements are summarized in Chapter 3. An answer to the question if there is a suitable protocol available for the set requirements, should be clearly addressed. If none of the available protocols meets the requirements then the solution must be custom tailored and implemented. This last option is to be possibly avoided, as custom protocols are implementation time consuming, and harder to share and port to other designs.

This document is intended to summarize the findings of an assignment in which different point-to-point links are to be explored. At the time of writing several options considered to be "actual" have been found and analysed in Chapters 5 and 6.

No stranger to the concept of communication protocols, large particle detector facilities massively deploy electronics systems which always require a specific point-to-point connection at - for example - a certain stage of a Data AcQuisition (DAQ) chain. As a practical study case, this research uses CERN [2] facilities to explore some of its real-life examples. A list of sampled CERN proprietary protocols historically used is provided in Appendix A. CERN innovates in many fields of fundamental research, and technology, thus also on electrical engineering related matters: as the demand of data processing for large experimental facilities increases, and larger dataset are to be transported through existing point-to-point links, technology has to be scaled and adapted over time to meet the future challenges. At the time of writing this document (2018) there is a desire to upgrade certain sub-systems to a different protocol that could transport higher-throughput data and to more efficiently make use of the offered bandwidth.

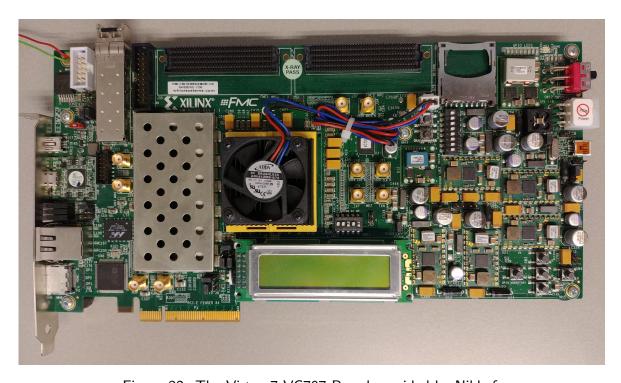

The complete proposed design is realized in hardware and the process is described in Chapter 8. The implementation targets vendor independence to maximize cross-platform portability; meaning that it should work on every FPGA with mid to high range specifications, and fast transceivers. This should be the only strong requirement in terms of the FPGA target device.

<sup>&</sup>lt;sup>1</sup>In telecommunication, a communication protocol is a system of rules that allow two or more entities of a communications system to transmit information via any kind of variation of a physical quantity. The protocol defines the rules syntax, semantics and synchronization of communication and possible error recovery methods. Protocols may be implemented by hardware, software, or a combination of both [1].

To summarize: the purpose of this assignment is to research and to implement the best protocol matching a set of clear requirements, and it should target an implementation using an FPGA. The specifications and implementation are published as Free and Open Source on code hosting platforms like OpenCores. Sharing is done with the aim of promoting the dissemination and broad adoption of the designed implementation.

# 2 Structure of communication protocols

Before getting into more details about the search and implementation of the surveyed protocols, the structure and functionality of communication protocols is described. This is for the sake of clarity to the readers and the author himself. Without a thorough understanding of a protocol structure and what to expect from it, the requirements could be misinterpreted, resulting in erroneously grounded research. This section is especially beneficial for new or less experienced readers on this subject.

#### 2.1 The OSI model

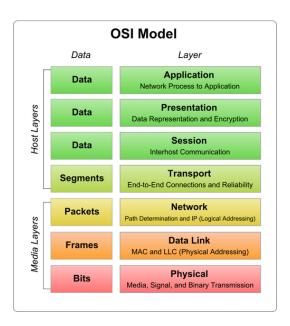

Communication functions of a computer system can be developed keeping the standardized Open Systems Interconnection (OSI) [3] model in mind. This model is designed to describe how data communication between two peers should take place. According to the OSI model communication systems consist of seven different layers which can be interpreted as groups with their own functions and responsibilities. In short, the model defines a stack of standards describing the way devices communicate and inform each other, when to send data, when to stop transmitting data, and so on. It also ensures devices use the correct data rate, guarantees the arrival of data at the receiver side, and in which way the physical connection is implemented. A general overview of the seven layers can be seen in Figure 1 [3]. The depicted structure goes bottom up with the lowest layer below.

Figure 1: An overview of the OSI model.

The first layer is the *physical layer* which is responsible for the communication signals passing through the connection between two points. Often the term *PHY* is used to refer to this layer. This concerns the physical connectors, cables, pin-outs and also the actual voltage (or the light) on the line, depending on the type of encoding the protocol makes use of. As shown in the figure above, the data from this layer can be seen as multiple "raw" bits. Further specifications the physical layer normally includes are the data rates, maximum transmission distances and low-level error correction. For example in the Ethernet standard

this layer contains multiple sub-layers which are the Physical Coding Sub-layer (PCS) delivering encoded data, Physical Medium Attachment Sub-layer (PMA) responsible for the attachment interface, Physical Medium Dependent Sub-layer (PMD) which defines the electrical transmit/receive characteristics and the Forward Error Correction Sub-layer (FEC) [4].

The second layer is called the *data link layer* and ensures error-free data transmission between two physical layers. This is done by arranging the stream of data in such way the receiver can easily understand. This is done by packing the data into so called frames, an explanation of which will follow in section 2.2. These frames will then be moved to the physical layer. This layer is also responsible for computing and adding data error correction, and including framing bits. The layer can also be divided in two sub-layers, the Logical Link Control (LLC) and the Media Access Control (MAC). The LLC is responsible for error checking, frame synchronization and flow control while the MAC is responsible for controlling how multi-peer network access is granted to the medium, and the permission to transmit data.

The third layer is the *network layer* which is primarily responsible for determining which physical path the data should take. It contains the function to route the data to it's recipient according to circumstances. This is where addresses will be added to the packets which is comparable with the well-known IP addressing from the Internet Protocol Suite [5]. Other functions handled by the data layer are packet switching and sequence control.

The fourth layer is called the *transport layer* and here the focus lies more on the delivery of messages between networked hosts. This is where the messages are fragmented and reassembled. This also contains higher-level error detection and recovery, flow control and guaranteed data delivery. Common protocols that function on this layer are TCP and UDP [5].

Since this document intends to target chip-to-chip communication, not all layers are important. In this case the Physical and Data Link layers are of most interest. Networking is also interesting in case data has to be transmitted over multiple channels. The transport layer can be of interest in case of multi-peer networked topologies, and that is the reason why it was still described. The other layers are of less interest.

# 2.2 Data structure and framing

OSI Layer 2

Transferring data is not just transmitting a bulk of data bytes to the other side. A certain amount of bytes will be accepted by the protocol which will package this data and prepare this for transmission. Depending on the protocol users can indicate when the data stream starts and when this ends. A whole lot of other indicators could be available to the user like choosing which bytes in the specific package are valid or the channel number to transmit on in the case of multiple data lines. The protocol will register this and pack them into so called frames. [6]

Not only do these frames contain for example the start and end of a package but they could also be used to transmit error correction and other crucial information. These frames are often categorized as control words. However the data itself is packed in a data word. These words always contain the same amount of bits. [7]

Of course the data can be transferred using a serial or parallel connection. This completely depends on what the designer of the protocol has implemented and at which speed the data is required to be transferred. Transmitting data in parallel requires more effort in comparison to a serial connection but delivers more data to the other side in the same time as expected. The data itself can be serially processed inside the electronics but it is also possible to process this in parallel using a specific package width.

### 2.3 Error detection and correction

OSI Layer 2/1

It is never certain whether the data received exactly matches the data that has been transmitted. During the data transmission all kinds of interference can be picked up by the communication line and can cause data bits to flip or be read as the wrong binary value. Without any indication whether these events overcame the data this bit flip will go unnoticed and corrupt data will be processed as if it were identical to the data sent by the transmitter.

To overcome these unnoticed forms of data corruption multiple ways of so called error correction have been researched and are nowadays nearly always implemented. The only downside of error correction is that additional information has to be transmitted between data packets but this sacrifice is in most cases worth the guarantee correct data will be processed by the receiver.

The easiest way of error detection is to add a checksum making use of a parity check. In this case the total number of high bits will represent a value according to their position in a specific byte. These values will be summed and the total will be divided by the amount of bytes again. This method offers easy detection of a single bit flip but if two bits are flipped at the same position in two different words, which represent the same value, the checksum won't change. For small amounts of data which are not that important it should suffice but when the received data is has a more important function, other methods of error detection are preferred.

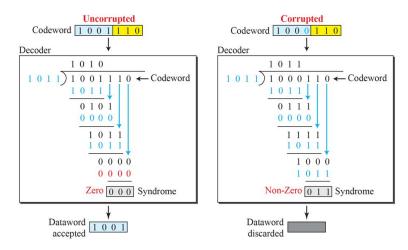

Another form is the Cyclic Redundancy Check (CRC) which has to be implemented before the encoding of data. In this case a so called polynomial is implemented which will be used as a divisor on the data. This pack of data will be divided by the polynomial starting at the most significant bit. After every division the result will be divided again but this time with the divisor shifted one position to the left. This can be interpreted as constantly using an XOR on the data bits. At the end of constant divisions, the complete data pack itself will be padded with zeros while the remainder should be the length of the divisor minus one bit. While dividing it is important to know that when the leftmost bit of the result data equals zero, the data will be divided by zeros instead of the divisor.

To validate the data this complete division will be repeated again but now using the generated remainder. This should result in is exactly zero for both the resulted data and remainder. [9] When the result is not equal to zero the received data is not identical to the data that was originally transmitted. An example of this check with a correctly arrived and corrupted package is depicted in Figure 2. [10] The most common CRC variants currently in use are CRC-8, CRC-16 and CRC-32.

Figure 2: CRC division in case data appears flawless or corrupted.

Forward Error Correction (FEC) is also an option which most of the times is used after encoding the data stream. Another term used for this way of error correction is channel coding. This technique is used to detect errors while communicating over unreliable or noisy channels. The big advantage of this technique is that it contains the ability to correct errors and when strategically placed between the encoder and transmission line, data entering the decoder will not contain errors caused during the physical transmission.

The so called Reed-Solomon error correction is an often implemented variant of FEC which contains the ability to detect and correct symbol errors. Another high-performance variant of FEC is called turbo code. This specific method of error correction makes use of two encoders, an inner and outer encoder with an additional interleaver. Multiple variants of these turbo codes are in use nowadays which are for example popular in deep space communication, 3G, 4G and different satellite networks. Optical forms of communication also make use of turbo code [11].

### 2.4 Encoding of data

# OSI Layer 1

Data has primarily always been transmitted using physical electrical conductive connections. While transmitting a lot of the same signs in a row over such a line, this causes the average line voltage to change in value and thus introduces a DC-component. This can cause the capacitance of line filters to be charged and the average voltage between ones and zeros can shift. This will eventually result in corrupt data and can even damage connected components. While the so called baseline wander is problematic, the short on transitions can additionally cause errors in the delineation of word boundaries, a form of constant EMI will be present and clock recovery<sup>2</sup> won't be possible since there will be no transitions to focus on.

A widely used solution to this problem is the addition of so called line encoding. The purpose of this technique is to encode the data in such way the receiver can still decipher it but long steams of the same binary value will be prevented. Encoders come in a lot of different variants.

<sup>&</sup>lt;sup>2</sup>The process of regenerating the clock signal at the receiving side with the absence of a separate clock signal. This can be done by using the timing information of the data stream.

The most simple and often used variant is 8b/10b encoding. This makes use of certain algorithms that will translate the bits to a specific pattern that will be transmitted. However as the name indicates for every eight bit transmitted two will be added as a header which results in about 20 percent of wasted bandwidth. The reason why they are still used a lot is because of their excellent DC-balance and they are easy to implement.

Through time more advanced encoders have developed like the 64B/66B encoder. The caused reason to innovate was primarily because of the overhead included with 8b/10b encoding. Since data rates nowadays grow rapidly, as less bandwidth as possible should be wasted. These moderner encoders also don't use a lookup table but make use of a so called scrambler which uses an algorithm to randomize the bit orders. Multiple variants have again tried to improve on the 64b/66b like the 64b/67b which offers better DC-balance. More details on this subject will be explained in section 4 which will be dedicated to the currently existing ways of encoding and decoding.

### 2.5 Serialization and parallelization of data OSI Layer 1

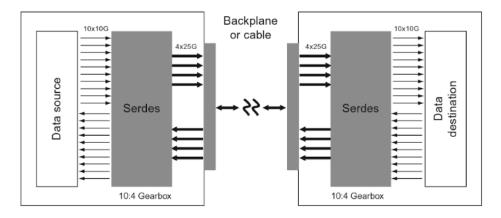

Serial and parallel data streams have been discussed in short earlier. When high speed transmissions are required it is preferred to gain a speed high as possible over a single transmission line. This doesn't mean all data processing operations inside the chips have to happen in serial order. Most of the times data is processed in parallel using FPGA's or dedicated chips suited for data transfer. Serially processing the data steam inside the chips would be too slow and bottleneck the line speed.

The parallel data bus will be translated into one or multiple serial data steams at the transmitter side and the receiver has to revert this transformation. Of course the speed of these lanes will also be altered according to the speed the parallel bus was transferring data on. The component that is responsible for this task is called a "Gearbox". When for example four 2,5 Gbps lanes are translated into a single 10 Gbps line, this would be mentioned as a 4:1 gearbox. The same can be said when this process is reversed with a 1:4 gearbox. Often this conversion block is also called a SerDes (SerializerDeserializer) and this is the last step before transmitting data. In Figure 3 an example of two gearboxes with a transmission line in between is shown. [12]

Figure 3: SerDes gearboxes.

#### 2.6 Protocol overview

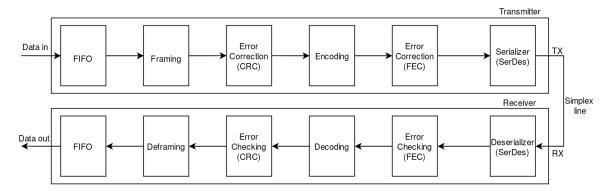

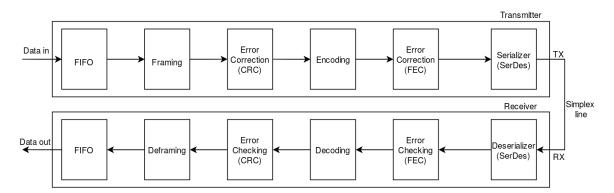

After this research it should be clearer what to expect of a communication protocol and what fundamental components it consists of. A simple depiction can be made to summarize this section which can be seen in Figure 4. Transmitted and received data will both be stored in separate FIFO's which act as a buffer for adding and removing frames in between the data packets. In case independent clock FIFO's are implemented, the protocol can be assigned different clock speeds than other section on the chip which can be seen as an advantage.

Figure 4: Protocol overview according to earlier subsections.

The framing, encoding and error checking are also present. In this example a simplex line has been displayed. Data is only transmitted in one direction from TX to RX. Both the transmitting and receiving side should have a TX and RX pin. Additional information and status updates on the receiver can then be transmitted in the other direction. This way data transmission could be for example slowed down or completely stopped in case an error occurs at the receiver side. still feels a bit empty and check paragraph title

# 3 Requirements

Before the search for suitable protocols starts, it is important to know what kind of protocol would suffice and what specification should at least be required. This will drastically increase the process of narrowing the search to a handful available protocols. For example in case the line rate is not sufficient, it is immediately clear the protocol is not suited for the application it has to fulfill.

This section contains these requirements with their description and explanation in case this has not been discussed in the previous section. There is a minimum line rate that should be possible to reach. At that rate a certain line range should be covered and flow control has to be included. Error detections and corrections like the Cyclic Redundancy Check and Forward Error Correction are a very important addition to the protocol and their priority will be discussed.

In addition to these requirements it is the purpose to look for a protocol that transfers data in a serial way and not in parallel. Of course bonding could be implemented but this should only apply in case a single line could at least transmit the minimum amount of data required.

### 3.1 Line rate target

OSI Layer 1

Line rate is the physical speed at which the device communicates with the equipment directly. For this project it has been specified the line rate has to be about 10 Gbps. This results is a rate of 1.25 GB/s when converted to bytes.

However while the line rate is the physical speed, this doesn't mean the actual data (payload) will also be transported at this rate. There is also overhead that has to be taken into account which adds additional information transmitted. The encoding and framing of data to be transmitted have a big impact on the amount of overhead. Error correction will also play a determining factor because this often adds redundant data. In this case the payload the data contains has to be more than 70%. This means that a maximum of 30% overhead is allowed, which still is quite a large percentage.

# 3.2 Range distance coverage

OSI Layer 1

This is the effective distance that can be covered by the signal that is carrying the data. In this project it has been specified the data stream should cover short to medium distances that vary between around 10 and 200 m, which corresponds to normal distances covered by cables in data centers.

The range largely depends on the transmission medium, the encoding used by the protocol and how many parallel transmission lines are used. Also the EMI induced on the line by other operating devices or transmission lines can cause the range to decrease. This can be solved by implementing FEC as explained in section 2.3. Each protocol has it's own effective range distance coverage which makes some protocols very suitable to use in this case while others can quickly be skipped.

#### 3.3 Forward Error Correction

### **OSI** Layer 1

Forward Error Correction is an optional feature but as explained the addition could prove very useful. Especially in noisy environments this could prevent a lot of possible errors. Especially since it provides the ability to also correct these. It is certainly a feature to keep in mind and it would be great if a protocol provides at least the must have and also has implemented FEC.

#### 3.4 Flow control

### OSI Layer 2

Implementing flow control is a must have so it's absolutely necessary that the chosen or designed protocol includes this feature. Flow control is the ability to manage the data rate of the transmission process between two devices. While the transmitter cant send data at the maximum speed the transceiver and protocol are allowing, this doesn't mean the receiver can always process all this data at the same rate. For example the receiver could have other tasks or the FIFO is read out at a slower rate and has the tendency to overflow, this could cause data loss because the receiver is simply overwhelmed by the amount of data and has no place to store it. The consequences could be disastrous. Picture of an atomic bomb

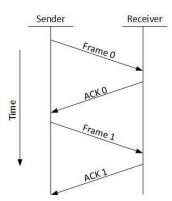

By implementing flow control the receiver will be added the ability to make it's processing speed clear to the transmitter. There are multiple variants to implement this but now the transmitter has an indication at which rate it can send data. The most simple way is Stop and Wait which is depicted in Figure 5 [13]. The disadvantage of this way is the waiting time before the ACK arrives at the transmitter and this wastes resources. A different approach is the Sliding Window in which multiple frames are transmitted and while transmitting the ACK's will arrive. This boosts the efficiency considerably.

Figure 5: The simple Stop and Wait implementation of flow control.

# 3.5 Cyclic Redundancy Check

### OSI Layer 2

The Cyclic Redundancy Check is an optional way of error detection which is used to detect corruption in the received frames. This is not a must have but it would be very useful if a protocol meeting the minimum requirements would also offer this feature. It would cause frame errors to be detected and prevent using corrupt data as if it were identical to the transmitted data.

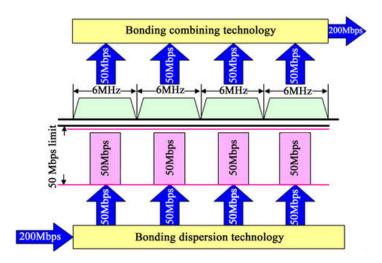

### 3.6 Channel bonding

### **OSI Layer 3**

This is a technique where two or more links are combined to increase throughput or to add redundancy. Differently formulated this will lead to an increase in the total amount of bandwidth available. For example this technique can often be found in wireless Internet connections like 4G and WiFi. Figure 6 shows a visualization of the bonding technology [14].

Especially in the case of using FPGA's this technique comes in very useful since it offers the possibility to bond multiple transceivers and can handle the high speeds at which data flows. Xilinx and Altera for example both offer their own specific high speed transceivers which individually can reach high line rates but they can be bonded for even higher rates. Bonding is a completely optional feature to add but as explained this could cause a huge increase in the maximum amount of data that could be transported. This would also make the protocol better suitable for more use in the future.

Figure 6: Transmitting data over different channels using bonding.

Not only does bonding provide higher bandwidth, the distance that can be reached while using wires also extends. The data packets will be fragmented and transmitted containing additional headers [15]. This will cause the receiver to be able to reconstruct the complete package using the headers containing crucial information.

Of course implementing this technique requires a lot more effort. All lines will have to be in constant synchronization, otherwise reconstructing packets will be very difficult and the chance is fairly high a lot of data will be lost.

# 4 Line encoding and decoding

Line encoders and decoders are essential components in the Physical OSI layer, which has also been described in section 2.4. Multiple ways of line encoding have been introduced over time and all have their own characteristics. Since many variants are still widely in use, this separate chapter has been written to provide more information on how important these techniques are. The process of encoding and decoding itself will be described in more detail but also other additions that play a role while encoding will be discussed.

Each line encoding and decoding technique has it's own benefits while the drawbacks should also provide important knowledge. The presence of scramblers in modern ways of encoding will also be discussed. In short they are responsible for the prevention of DC offset by randomizing the data. Modern encoders are responsible for the addition of synchronization headers.

### 4.1 8b/10b

A fairly simple form of encoding which was developed by IBM in 1983. Each incoming byte will be translated into a constrained 10-bit binary.

The encoder actually consists of two components, a 5b/6b and a 3b/4b encoder. The last five bits of the incoming byte will be picked and placed at the start of the encoded byte. After these bits, an extra bit will be added. The remaining three first bits the incoming byte contained will follow with an extra bit added again.

Those so called extra bits are known as running disparity. These are variable bits to ensure the balance between ones and zeros is maintained. Otherwise DC unbalance can cause malfunctions in the system like explained in section 2.4 [16].

The 5b/6b and 3b/4b encoders make use of separate tables to translate the original data bits to the accompanying encoded bits. This way of coding also provides the ability to transmit control symbols and characters to the receiver over the line.

8b/10b encoding is still widely in use despite multiple attempts have been made to develop better encoders. The reliability that comes with the encoder is why many protocols still use 8b/10b encoding. Also the absence of DC-imbalance is a huge advantage. This is possible because the used algorithm always balances the amount of ones and zeros. However the 20% overhead that comes with it and increasing demands in transfer speeds cause protocols to slowly look for different variants of encoding.

Technologies using this way of encoding are among others DVI, HDMI, Gigabit Ethernet (SGMII), SATA, SAS, USB 3.0 and XAUI.

# 4.2 64b/66b

At the time of writing 8b/10b encoding is still widely used but the 20% overhead is quickly becoming a bottleneck while transmitting data a high rates. Different and more efficient ways of encoding have been introduced and 64b/66b is one of them. It is immediately clear that this way up to eight bytes can be transmitted in one package while using a two-bit preamble. This way of encoding provides a better approach to prevent the earlier discussed quite large overhead, which in size went from 20% to a decreased percentage of little over 3%. Less bandwidth is wasted using this approach and more data can be transferred in

the same time. Before transmitting, the data will be scrambled using a self synchronous scrambler with a 58-bit polynomial and eventually the receiver will unscramble the data [18].

#

Figure 7: Headers used for 64b/66b encoding.

In Figure 7 two different data blocks are visible [19]. The upper one is just a block containing the eight bytes of data. The lower block contains the control commands. It consists of seven bytes and a two bit type indication. This structure could vary depending on the protocol but it gives a general overview of what the two types of encoded vectors/blocks look like.

Technologies who adopted this way of encoding are for example 10/100 Gigabit Ethernet, InfiniBand and Thunderbolt.

# 4.3 128b/130b - PCIe 3.0/4.0

This builds further on the 64b/66b encoding but now with twice the payload. It doesn't make use of self-synchronous scrambler and uses a different scrambling polynomial. The two preamble bits still have the same functionality as the case with 64b/66b encoding. The encoding results in less overhead and more bandwidth can be used to transmit data bytes.

This way of encoding is for example used in PCI Express 3.0 and 4.0 which can reach line rates up to respectively 8 and 16 Gbps [20].

# 4.4 128b/132b - USB 3.1

Very alike with the earlier discussed 128b/130b encoding but with four preamble bits instead of two. This way of encoding is primarily used by the USB 3.1 protocol. The preamble is still used to indicate whether the transmitted information is a block containing data or a block that contains control commands. The first two bits or the preamble are set to indicate a control block and the last two are used to indicate a block containing data.

The two extra bits in the preamble have been added to decrease the error-rate compared to earlier USB versions. The protocol will stay running if a single bit flips and can correct that flip. When two or more bits flip, the protocol will go to into recovery. Same would be the case with a single bit when the two preamble bits were used [21].

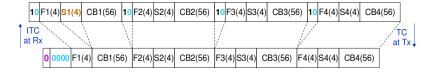

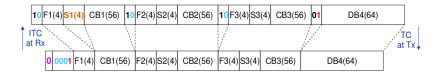

### 4.5 256b/257b - Fibrechannel

This a way of encoding results in a very big packet of data to be transmitted. Four incoming 66 bit blocks are converted into a single 257 bit block. This is done by a of course removing some of the bits but without influencing the actual data and control commands. In Figure 8 a transmission packet containing exclusively data is visualized [22].

Figure 8: The header of a 256b/257b transmission containing data.

When four eight data byte blocks in a row have to be transmitted, it is fairly simple to put these in a single 257b block by removing all the preambles and putting a single preamble bit in front of the transmitted block. A one indicates that only data blocks are being transmitted and a zero indicated control block or a mix of data and control. Figure 9 shows a transmission packet containing data and control blocks [22].

Figure 9: The header of a 256b/257b transmission with mixed blocks.

When only control blocks or both variants are sent in a single block. The first bit will be zero and the following four bits will indicate which bytes are data or control commands. The first nibble of a command block will be removed to make room for the four additional bits. This way the block can be transmitted with less than 2% overhead.

This way of encoding is used by FibreChannel in the 32G and 128G variants [23].

# 4.6 64b/67b - Interlaken/SerialLite

This is nearly identical to the structure used in 64b/66b encoding. The only difference is the addition of an extra bit to the preamble. While 64b/66b encoding completely depends on the scrambler to prevent DC base wandering, this way of encoding also has the ability to invert the data that will be transmitted. If this data has the tendency to excessively increase or decrease the line voltage, the data pack excluding the preamble can be inverted. This inversion is indicated using the additional bit which is referred to as the inversion bit. This makes the decoder clear whether the data is has been inverted and the data will always leave the decoder with it's original polarity.

Analysis has shown that the scrambler 64b/66b encoding trusts so much on, is not perfect and can still cause DC base wandering over time. This is why the 64b/67b encoding has been developed. The only protocols using this way of encoding at the moment of writing are the Interlaken protocol [7] and Altera/IntelFPGA SerialLite [8].

### 4.7 Scramblers

It should be taken in account that long streams of ones and zeros create a constant voltage. This could be a harmful phenomenon while synchronizing a communication system because there is a short on transition states. Several ways of encoding were developed to overcome this problem but nonetheless without success since they actually didn't solve the problem but provided workarounds. One of the workarounds was to limit the maximum length of a possible string only containing ones or zeros. Of course this wasn't a direct solution to the existing problem but it was the easiest way to get the transmission suited for long-distance communication.

A more appropriate solution was the so called scrambler. A scrambler randomizes the data input sequence in such way that it is nearly guaranteed there will be no long streams which only contain ones or zeros. After this scrambling the data is still recoverable with a descrambler that will be placed at the receiving side.

Unfortunately the scrambler cannot completely guarantee the prevention of such a long stream of ones and zeros but it will minimize the probability.

Implementing a scrambler provides even more benefits. Beside the prevention of a DC component it provides good error detection, good synchronization capability, eases clock recovery performance and offers the possibility to send data over long distances [17].

A physical scrambler is realized by implementing a parallel register and several XOR gates.

# 5 FPGA vendor dependent protocols

The first protocols to look at, are these delivered by the FPGA vendors. Unfortunately this introduces some complications because the protocol has to function on every FPGA, whatever vendor these are from. Vendors often offer IP-Cores which are only compatible with their specific FPGA's. This could have several reasons like optimization of the hardware structure for certain models, which only the manufacturer knows of course, and which specific parts are included as a hardcore instead of a softcore. Also lots of effort and man hours went into the development of these IP-cores which makes it understandable they are vendor dependent. Nonetheless we will look at these protocols because it is important and interesting to know what the vendors have to offer.

#### 5.1 Xilinx Aurora

Xilinx Aurora is an existing communication protocol which is as indicated developed by Xilinx and only applicable for Xilinx FPGA's [24]. Aurora is designed to ease the implementation of multi-gigabit transceivers in a project and besides that provides a light-weight user interface on top of which designers have the possibility to build a serial link. It is very useful in situations where serial point-to-point connectivity is required like chip-to-chip links. The protocol comes in multiple variants, one of them makes use of the older 8b/10b encoding [25] and the other makes use of 64b/66b encoding. This section will be primarily focused on the 64b/66b variant from which a complete IP Product Guide is available [26].

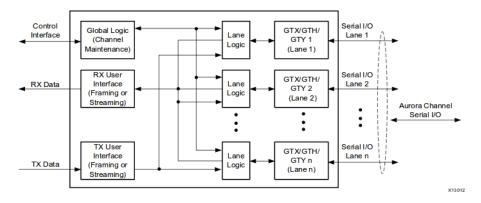

The Aurora protocol has a very high throughput that can vary from 0,5 Gbps to over 400 Gbps depending on the amount of available transceivers and their maximum speed. Data can be transferred in simplex or full-duplex mode. Figure 10 shows a block diagram of the protocol [26].

Figure 10: The Aurora block diagram.

Every lane contains a separate logic lane where encoding, decoding and error detection happens. The global logic monitors all lane logic modules and is responsible for channel bonding. Aurora is also capable of CRC encoding/decoding and flow control.

The CRC32 will be calculated for each individual lane on the valid bytes to be transmitted. There are different variants of flow control to choose from. User flow control (UFC) for example allows the applications to send high-priority messages to each other while native flow control (NFC) allows receivers to regulate the speed at which data will be received.

Immediate mode makes it possible to insert idle codes within data frames while completion modes inserts idle codes between complete data frames.

### 5.2 Altera/IntelFPGA Serial LITE

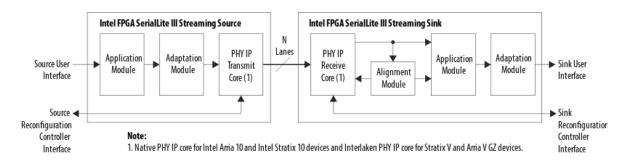

Altera/IntelFPGA has it's own serial streaming protocol [8] SerialLite is meant for high bandwidth chip-to-chip, board-to-board and backplane communications. The protocol comes in two variants. The older SerialLite II and the newer SerialLite III. This section will focus on the newer variant of the protocol.

SerialLite can be run in two modes. The continuous and burst mode which both are useful for different applications. In the first mode data will be continuously transmitted without gasps. This is useful when a simple high bandwidth interface is required. The second mode will transmit the data is bursts across the interface. Very useful for applications which send a lot of data at certain moments. Like for example raw digital video content where lines of the display raster can be sent in bursts.

The protocol can be used in simplex and duplex mode which is very useful when needed. Speeds up to 28 Gbps can be reached which is of course very dependent on the transceivers connected to the specific FPGA. Channel bonding with up to 24 lanes is supported which results in possible bandwidth to over 300 Gbps. Transmitted data will be encoded by 64b/67b. All data will also contain CRC-32 error correction.

Figure 11: The SerialLite III block diagram (Simplex mode).

In Figure 11 the block diagram of the protocol in simplex mode is shown [27]. The documentation also advertises with low overhead and point-to-point transfer latency. To save soft logic resources it is possible to make use of the hardened Native or Interlaken PHY IP core depending on the model used. The mentioned Interlaken protocol will be discussed in the next section.

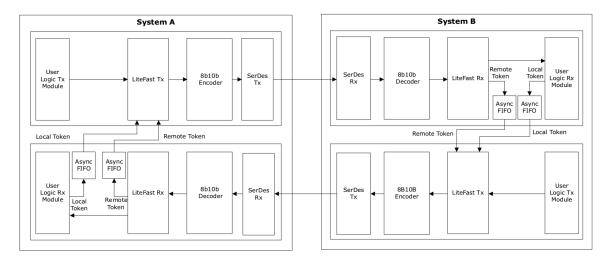

#### 5.3 Microsemi LiteFast

Microsemi has also developed it's own serial point-to-point link. It is intended as a low-cost, scalable, light weight and high-speed solution. It also provides built-in flow control and in case no data is transmitted link activity will be maintained.

The protocol includes data framing and in case no data is available idle frames will be transmitted. The data payload will be covered by a CRC-32 packet included at the data frame end. Channel bonding is added as an optional feature and the user can choose between 1, 2 or 4 lanes per SerDes. This supports speeds varying from 4 up to 10 Gbps in case 4 lanes are used. In case multiple lanes are used, the ability to align these is

included. Unfortunately the protocol still uses 8b/10b encoding which offers quite the overhead compared to the newer ways of encoding. A quick overview of the interface can be seen in Figure 12 [28].

Figure 12: The LiteFast block diagram (Single Lane).

#### 5.4 Conclusion

Include Microsemi? To conclude this section, a bullet point overview of the protocols is added. This will mention the features of both vendor dependent protocols and compare them with each other.

- Both protocols offer line rates which will push the transceivers to their limits. Aurora mentions about 26 Gbps and Serial Lite III about 28 Gbps per transceiver

- Aurora features flow control while Serial Lite III is not clear on this. (In contrast Serial Lite II does support flow control)

- Both offer CRC-32 error correction, FEC is not mentioned in the documentations

- Aurora uses 64b/66b encoding while Serial Lite III implements 64b/67b line encoding

- Both offer excellent channel bonding up to 16 (Aurora) or 24 (Serial Lite) channels which results in speeds to over 300 Gbps

# 6 Vendor independent protocols

This section contains a survey on frequently used protocols which offer high bandwidth and reliability. It will be described how the protocols function and how their specifications compare to the requirements mentioned earlier. This section will conclude with a short summary on the discussed protocols and which of them will be the most suitable according to their specifications.

#### 6.1 The Interlaken Protocol

The Interlaken protocol is a narrow, high speed channelized chip-to-chip interface [7]. Interlaken consists of two fundamental structures. These are the data transmission format and the Meta Frame.

The data transmission format relies on the concepts of SPI (System Packet Interface) 4.2 which is a protocol used for data transfer between a link layer and a physical layer [29]. Multiple bursts will contain the data, thus this will not be sent in a single pack. These will be subsets of the original packet data and will be sent sequentially. Before and after each burst, a control word is placed. These words contain important instructions, for example error detection or just an indication of the start or end of a packet. The segmentation of data also allows interleaving of data transmissions from different channels. This can be implemented for low-latency operation.

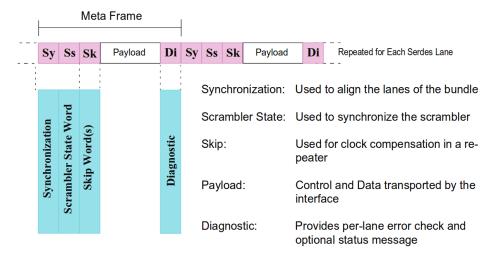

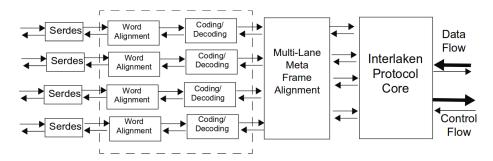

To transmit the data over a SerDes infrastructure, the Meta Frame is defined. This contains four unique control words to provide lane alignment, clock compensation, scrambler initialization and diagnostic functions. These frames run in-band with the data transmissions, using formatting to distinguish it from the data. In Figure 13 the word type structures are depicted [7].

Figure 13: Word formats Interlaken makes use of.

The Interlaken protocol provides a handful of important features: [7]

- Support for 256 communications channels, or up to 64K with channel extension

- A simple control word structure to delineate packets, similar in function to SPI4.2 [29]

- A continuous Meta Frame of programmable frequency to guarantee lane alignment, synchronize the scrambler, perform clock compensation, and indicate lane health

- Protocol independence from the number of SerDes lanes and SerDes rates

- Both out-of-band and in-band per-channel flow control options, with a simple Xon/Xoff semantic

- 64b/67b data encoding/decoding and scrambling/unscrambling

- Performance that scales with the number of lanes

Interlaken also features error correction in the form of a 24-bit CRC. Instead of the 64b/66b encoding 64b/67b has been chosen to prevent DC balance or baseline wandering. This adds a little overhead but prevents possible bit-errors and complications in the circuitry the receiver contains.

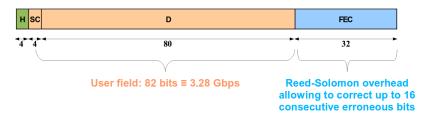

Forward Error Correction has later been added as an extension and offers Reed-Solomon (544,514) encoding. The protocol definition also mentioned the additional overhead. Line coding itself adds about 4,7% overhead and the RS FEC extension will add an additional about 2,7% to this which results in 7,5% overhead [30].

Both Xilinx [31] and Altera/IntelFPGA [32] developed IP-Cores based on the Interlaken protocol which are capable of achieving huge speeds, 150 Gbps and 300 Gbps respectively. This applies when channel bonding is used. Both vendors claim that a single lane can provide 12,5 or even around 25 Gbps. These speeds would be sufficient according to the requirements and even offer more speed when needed. According to the documentation these cores have recently been updated so they are still maintained which is a good indication.

### 6.2 SATA protocol

Serial-ATA is a communication protocol that evolved from Parallel-SATA [33]. Nowadays the technology is often used to for the connection of hard drives [34].

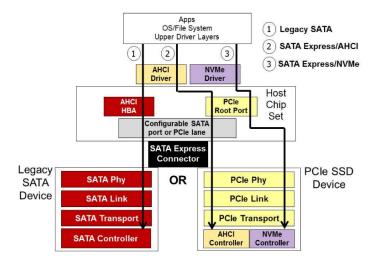

Unfortunately the speed of SATA 2 is limited to 3 Gbps and SATA 3 can reach speeds up to 6 Gbps. The maximum speed of SATA 3 is around 0.6 GB/s, the speed current SATA SSD's also reach their maximum read/write speeds. SATA-Express is a newer variant of the SATA standard but didn't change much. It is part of the SATA 3.2 standard and actually is just a connector to combine SATA and PCle [35]. An overview of the SATA Express architecture is depicted in Figure 14 [36].

Thanks to the PCIe support, SATA Express has the ability to use the newer NVMe driver [36]. Unfortunately this is a whole different protocol and actually has nothing to do with the SATA protocol itself, which doesn't reach the required speed and is unsuited for this application.

Figure 14: Overview of the SATA Express architecture.

#### **6.3 CPRI**

Common Public Radio Interface is an initiative protocol which was meant to define a publicly available specification [37]. This would standardize the protocol interface between the radio equipment control (REC) and radio equipment (RE) in wireless base-stations. It is designed with an optical or copper transmission line in mind.

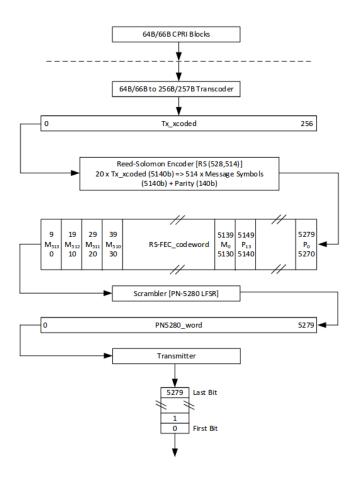

CPRI offers high lane rates up to 24,330 Gbps while using a serial connection. The two most common ways of encoding are used, 8b/10b and 64b/66b are supported. 8b/10b maxes out at 9,8 Gbps and from there on 64b/66b starts to increase the line rate up to te earlier mentioned 24 Gpbs. Speeds of 10,1 and 12,2 Gbps are also possible.

According to the documentation the physical layer is designed in such way that bit errors are very uncommon. This is why error detection is not directly included in the framing or encoding but is more an optional feature. Detection of sync header violation is used to detect link failures in case this occurs.

Unlike CRC which is not mentioned, Forward Error Correction is an optional feature in this protocol.

Figure 15: Overview of the CPRI architecture using FEC.

In Figure 15 the architecture of CPRI uses is visualized [37]. It is clearly visible that the data is packed into 66b blocks thanks to the 64b/66b encoder. But these CPRI packets are put into a block of 257b. This is like the earlier explained 256b/257b encoder. These are encoded again by the RS(528,514) FEC, scrambled and transmitted.

There are two different protocols available for the Control and Management (C&M) information exchange. The slow High level Data Link Control (HDLC) and the faster Ethernet variant. Unfortunately flow control is only available to use for the slow C&M channel. Selecting HDLC or Ethernet is purely optional. The specifications recommend to support at least one non-zero C&M channel bit rate on a link [37].

Altera and Xilinx both developed their IP Cores for the CPRI protocol.

So in short CPRI offers the required speed and delivers line rates up to 24,330 Gbps. It doesn't mention CRC but offers the addition of FEC. Flow control is support but only when using HDLC. Channel bonding is not mentioned and the range depends on the cabling.

### 6.4 HyperTransport

This is a frequently used packet-based, high-bandwidth, scalable, low-latency point-to-point interconnect technology [38]. The purpose of this technology was to increase the communication speed between integrated circuits in for example computers, servers and embedded systems. Hereby the number of buses is a system can be kept at a minimum, which can reduce the occurrence of possible system bottlenecks. HyperTransport is an open standard which is royalty-free managed. Before implementing HyperTransport a license is required which can be provided by the developers. Figure 16 [39] shows the current versions of HyperTransport and their specifications.

| Special Features                                                                                                     | HT 1.x                                              | HT 2.0        | HT 3.0       | HT 3.1    |  |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------|--------------|-----------|--|

| Max Clock Speed                                                                                                      | 800 MHz                                             | 1.4 GHz       | 2.6 GHz      | 3.2 GHz   |  |

| Max Aggregate Bandwidth (32-bit links)                                                                               | 12.8 GB/s                                           | 22.4 GB/s     | 41.6 GB/s    | 51.2 GB/s |  |

| AC Operation – Capacitive Coupling<br>(optional) with AC/DC Autosensing,<br>Autoconfiguration                        | No                                                  | No            | Yes          | Yes       |  |

| Link Splitting (un-ganging)<br>Each HT Link Split into 2x Half-Width Links                                           | No                                                  | No            | Yes          | Yes       |  |

| Hot-Plugging                                                                                                         | No                                                  | No            | Yes          | Yes       |  |

| Dynamic Link Clock/Width Adjustment                                                                                  | No                                                  | No            | Yes          | Yes       |  |

| DirectPackets™ Data Streaming -<br>+16 Virtual Channels (22 total), Peer-to-<br>Peer Support, Native Packet Handling | HT 1.1<br>only                                      | Yes           | Yes          | Yes       |  |

| PCI Express Mapping                                                                                                  | No                                                  | Yes           | Yes          | Yes       |  |

| Comm                                                                                                                 | on Features                                         | 5             |              |           |  |

| 2 x Unidirectional, Low-Voltage                                                                                      | -Differential-S                                     | ignaling Link | s per HT Bus |           |  |

| Scalable Link \                                                                                                      | Width (2-bit to                                     | 32-bit)       |              |           |  |

| Asymetric Link Sup                                                                                                   | Asymetric Link Support (different link widths)      |               |              |           |  |

| Asynchronous Link Operation                                                                                          |                                                     |               |              |           |  |

| Clock Forwarding (no SerDes latency penalty)                                                                         |                                                     |               |              |           |  |

| DC Operation (direct signal coupling)                                                                                |                                                     |               |              |           |  |

| PCI, PCI-X Mapping                                                                                                   |                                                     |               |              |           |  |

| Priority Request Inter                                                                                               | Priority Request Interleaving™ (lowest I/O latency) |               |              |           |  |

| Virtual Channels Support (6)                                                                                         |                                                     |               |              |           |  |

| Error Retry                                                                                                          |                                                     |               |              |           |  |

Figure 16: HyperTransport versions and their specifications.

The bandwidth of this protocol is very high but it should be taken in account that this is the case for a 32-bit link. It is possible to make use of the HT point-to-point link using a PCI bus. Unfortunately HT has it's own connectors. An open-source HyperTransport IP-core has been developed which offers a bandwidth of 1,4GB/s which results in 11,2Gbps [40]. Xilinx used to have it's own IP-Core for HT but unfortunately this has been discontinued. Altera

also abandoned it's HT Core and does not recommend use of this IP in new designs. Another paper has been written on a HT3 Physical Layer Interface for FPGA's but unfortunately this reaches proven speeds up to 1600Mbps. The authors claim possible link speeds up to 12,8GB/s but not proven [41].

#### 6.5 Fibre channel

Fibre channel as the name indicates is a communication protocol with optical data transmission kept in mind. The Fibre Channel Industry Association claim it to be a reliable, cost-effective and capable of high speed data transmission [42]. The recent release variant named 64GFC should reach a throughput of 12,8 GB/s which is sufficient according to the requirements. 128GFC offers a throughput of 25,6 GB/s but is just four parallel 32GFC lanes.

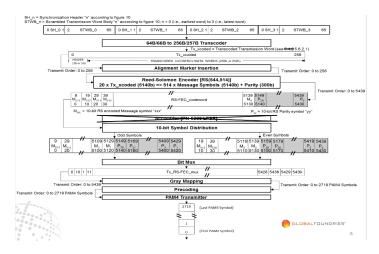

One of the notable things about Fibre Channel is that it makes use of 256b/257b encoding. It packs four control/data words in a single package and adds a header that can be the size of one or five bits. After that a Reed-Solomon Encoder, RS(544,514), is added so it contains FEC. It distributes the symbols and eventually transmits the data using PAM4 technology [43].

Figure 17: Proposed architecture of 64GFC.

Figure 17 [43] shows a proposed architecture but it's not 100% certain that this is exactly the same as how it functioned since the official release. However the chance is fairly high it is and slides have been updated through time. Of course this architecture has been well thought through since the source is Global Foundries.

There is not much documentation to be found on the protocol so unfortunately a clear description has not been stumbled upon. Xilinx had an IP-Core developed in 2010 for Fibre Channel but unfortunately this IP has been discontinued [44]. A newer variant has been released in 2016 but is only available on request and contains an encrypted RTL [45].

#### **6.6 XAUI**

XAUI is a modern chip interface that came along with the innovations of the 10 Gigabit Ethernet Task Force. The name came into existence by merging AUI from Ethernet At-

tachment Unit Interface and X (10 in roman numbers) which represents 10 Gigabit. It is designed to extend the XGMII (10 Gigabit Media Independent Interface).

The serial bus used for this interface has a low pin count and is self-clocked. It provides 2,5 times the speed of usual Gigabit Ethernet. The purpose of this protocol is to combine four of these lanes to a single 10 Gbps line [46].

This unfortunately concludes that it is not possible to use a single lane to transfer around 10 Gbps of data. In addition there is still a 8b/10b encoder which can be substituted by a 64b/66b encoder. This could prevent the rather big overhead that comes with 8b/10b encoding. One of the biggest downsides is that the protocol lacks flow control which is an absolute must have [47].

Altera/IntelFPGA, Xilinx and Lattice have developed IP cores to implement XAUI in a simple way on your FPGA. Broadcom released HiGig which is used to enhance the XAUI PHY. It makes use of different headers and increases the speed to 6,375 Gbps per lane [48].

#### 6.7 Conclusion

This section will conclude which of the earlier described protocols is more suitable and whether or not it meets the requirements. Table 1 provides a quick overview of their specifications. In case a yes is noted, this means support is available but the exact specifications have not been described clear enough. When there is a '-' noted, there is no support or documentation has not been clear enough to provide the required information.

|                 | Interlaken      | SATA   | CPRI            | Fibre channel   |

|-----------------|-----------------|--------|-----------------|-----------------|

| Lane rate       | 25,3 Gbps       | 6 Gbps | 24,33 Gbps      | 12,8 Gbps       |

| Encoding        | 64b/67b         | 8b/10b | 64b/66b         | 256b/257b       |

| Flow control    | Yes             | Yes    | -               | -               |

| Range distance  | Cable dependent | Short  | Cable dependent | Cable dependent |

| CRC             | CRC-24/32       | CRC-32 | -               | Yes             |

| FEC             | RS(544,514)-Ext | -      | RS(528,514)     | RS(544,514)     |

| Channel bonding | Upto 400 Gbps   | -      | -               | -               |

Table 1: Overview of the most suited protocols.

SATA is an interesting protocol but the line rate is not sufficient. HyperTransport is great for huge bandwidths but implements a parallel bus while serial transmission is required in this case. Fibre channel looks like an interesting alternative. Unfortunately the lack of documentation and not being open will bring a lot of risks with it.

CPRI is another very interesting option offering a high line rate and a good way of encoding. Unfortunately the unclear documentation on CRC and flow control plus the lack of channel bonding cause this option to be a less suited option. Nevertheless a protocol to keep in mind.

The Interlaken Protocol looks like the best solution. While having excellent documentation, the protocol also meets all the requirements. This even includes the optional/ nice to have specifications. The protocol is open to use and is even promoted to use by Cortina Systems and Cisco Systems.

### 7 The Interlaken Protocol

After the survey of available protocols and their specifications, the Interlaken protocol appeared as the one meeting nearly all requirements in contrast to the other surveyed protocols [49]. Not only the specifications looked propitious for the current situation but the documentation also offered lots of information which made it a lot clearer how the protocol functions and how to possibly realize this in hardware.

Until now the Interlaken Protocol has been described in short but this section will be dedicated to a more extended description of the Interlaken protocol. As described earlier the protocol can be divided into different components which belong in their specific OSI layer. A complete Interlaken frame is formed in the first two OSI layers. The frame itself containing the data and control words is formed in the second layer while the first layer adds the three bit preamble that comes with the encoding.

#### 7.1 Overview

This section will present a complete overview to clear up how the protocol is structured and in what order the functions will be discussed. The earlier presented Figure 4 can be used as reference in this case. The Interlaken also functions is this order but the blocks get somewhat complexer.

Figure 4: Protocol overview. (repeated from page 16)

Interlaken uses two ways of framing which both add control words. First bursts will be formed by adding framing words and these will be covered by the first CRC and after this the meta frame will be formed which will be covered by another CRC. This can be interpreted as the framing and error correction blocks repeating once. Because of this the control word itself will be explained first and after this the two ways of framing will be discussed in more detail. Flow control and it's supported variants will also be described. This will be followed by the CRC variants Interlaken makes use of since all components containing CRC have been described.

The encoding will consist of a scrambler and the 64b/67b encoder itself which will be described respectively. FEC is available as an extension and will not be described yet since it is not included in the standard protocol description.

#### 7.2 Control Word Format

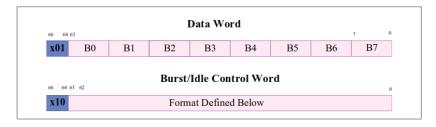

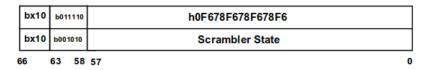

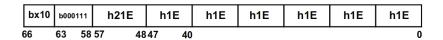

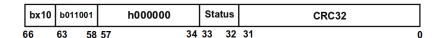

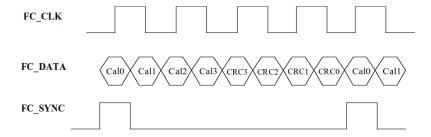

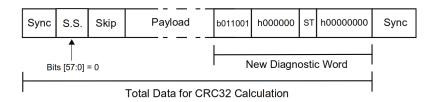

It is essential to know how the control word is structured to understand how Interlaken handles data transmission. There are two different types of control words used depending on the control bit status. In case this is a one it concerns an idle/burst control word and in case this is a zero it concerns a framing layer control word. Figure 19 depicts the word formats [7].

Figure 19: Interlaken control word formats.

As seen the two idle/burst control words contain a type bit which indicates whether the word is an idle or burst word. It includes Start and End Of Packet (SOP and EOP) indicators which will be explained later. Flow control and CRC are also present in this word and there is space for the specific channel number in the case of bonding.

The framing word has a less complex structure and contains a block type field which functions as an identification. After this the specific format according to the block type itself will follow. The structure of this last data block differs for each type and this will be explained further in section 7.4.