Eli Billauer elib@flextronics.co.il

November 11, 2003

This guide applies to version 0.2 (beta) of PERLILOG.

Copyright © 2003, Eli Billauer.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in Appendix A.

# **Contents**

| 1 | Intro | duction 10                                   |

|---|-------|----------------------------------------------|

|   | 1.1   | PERLILOG in a nutshell                       |

|   |       | 1.1.1 What is PERLILOG?                      |

|   |       | 1.1.2 Bye bye Verilog?                       |

|   |       | 1.1.3 Status of the project                  |

|   |       | 1.1.4 Other usability                        |

|   | 1.2   | What's PERLILOG? A broader look              |

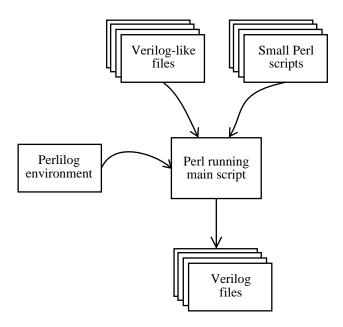

|   | 1.3   | How PERLILOG is used                         |

|   | 1.4   | The key features of PERLILOG                 |

|   | 1.5   | About the project                            |

|   | 1.6   | About the author                             |

|   | 1.7   | Acknowledgements                             |

|   | 1.8   | This guide's outline                         |

|   |       |                                              |

| 2 | A ju  | mp into the water 17                         |

|   | 2.1   | A jump into what?                            |

|   | 2.2   | Installing and running PERLILOG              |

|   |       | 2.2.1 Automatic installation                 |

|   |       | 2.2.2 Manual installation                    |

|   | 2.3   | First example: A simple connection           |

|   |       | 2.3.1 The template files                     |

|   |       | 2.3.2 The Perl script                        |

|   |       | 2.3.3 The output Verilog files               |

|   |       | 2.3.4 Ports and interface                    |

|   |       | 2.3.5 "via" wires                            |

|   |       | 2.3.6 The Silos project file output          |

|   |       | 2.3.7 Two files instead of three             |

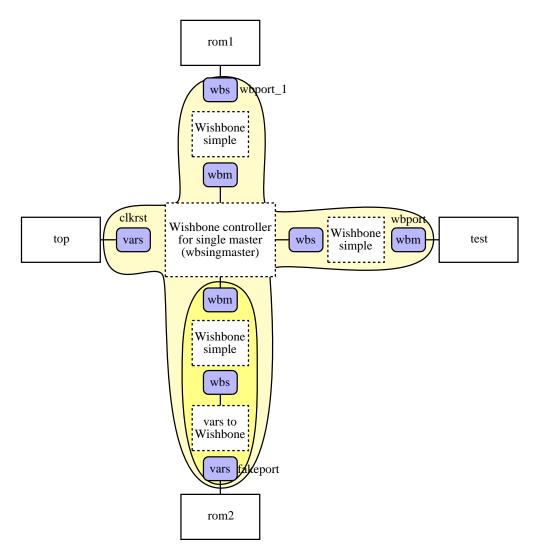

|   | 2.4   | Other examples: Wishbone connections         |

|   |       | 2.4.1 Purpose                                |

|   |       | 2.4.2 A simple master-slave connection       |

|   |       | 2.4.3 Connecting three Wishbone ports        |

|   |       | 2.4.4 Mapping a non-Wishbone port to the bus |

|   |       | 2.4.5 Non-Wishbone port: A nicer example     |

|   | 2.5   | Last example: Embedded Perl code             |

|   |       | 2.5.1 The main script                        |

|   |       | 2.5.2 The template file                      |

| _ | _     |                                              |

| 3 |       | plate objects 42                             |

|   | 3.1   | About this section                           |

|   | 3.2   | How it works                                 |

|   | 3.3   | What to expect from template objects         |

|   | 3.4   | A template object as an object               |

|   | 3.5   | Variable declarations                        |

|   |       | 3.5.1 Same syntax, different meaning         |

|   |         | 3.5.2 Undeclared bit range [:]           |            |

|---|---------|------------------------------------------|------------|

|   |         | 3.5.3 Verilog input and output           | 45         |

|   |         | 3.5.4 wire and iwire                     | 46         |

|   |         | 3.5.5 Variable rules summary             | 46         |

|   |         | 3.5.6 simple_rom.pt revisited            |            |

|   | 3.6     | Declaring ports                          |            |

|   | 3.7     | Embedded Perl                            |            |

|   |         | 3.7.1 How it works                       |            |

|   |         | 3.7.2 perl or perlonload?                |            |

|   |         | 3.7.3 Rules for writing embedded scripts |            |

|   | 3.8     | Importing prewritten modules             |            |

|   | 5.0     | 3.8.1 Verilog compatability              |            |

|   |         |                                          |            |

|   |         | 5                                        |            |

|   |         | 3.8.3 Unhandled Verilog variables        |            |

|   |         | 3.8.4 Verilog task and function          |            |

|   |         | 3.8.5 Comments in Verilog                | 2          |

| 4 | \A/+:4: | ing main carinta                         | 53         |

| 4 |         | •                                        |            |

|   |         | Introduction                             |            |

|   |         | The init() call                          |            |

|   | 4.3     | The object dumper                        | <b>5</b> 4 |

| 5 | DED     | LILOG objects                            | 55         |

| 5 |         | Background                               |            |

|   |         | An example                               |            |

|   |         |                                          |            |

|   | 5.3     | Properties                               |            |

|   |         | 5.3.1 The basics                         |            |

|   |         | 5.3.2 Property names                     |            |

|   |         | 5.3.3 Undefs and empty lists             |            |

|   |         | 5.3.4 More about constant properties     |            |

|   |         | 5.3.5 "Magic" callbacks                  |            |

|   |         | 5.3.6 The property path                  |            |

|   |         | 5.3.7 Methods for lists                  |            |

|   | 5.4     | Creating and using objects               | 31         |

|   |         | 5.4.1 The formalilties                   | 31         |

|   |         | 5.4.2 An example                         | 31         |

|   |         | 5.4.3 Property paths in new              | 32         |

|   |         | 5.4.4 Common object types                | 32         |

|   |         | 5.4.5 The global object                  |            |

|   |         | ,                                        |            |

| 6 | Crea    | 9 9                                      | 64         |

|   | 6.1     | How this section is organized            | 34         |

|   | 6.2     | Overview                                 | 35         |

|   |         |                                          |            |

|   |         | 6.2.1 What's a code generating class? 6  | ວວ         |

|   |         |                                          |            |

|   |         | <del>_</del>                             | 35         |

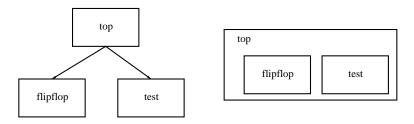

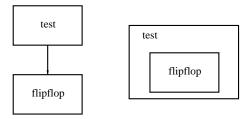

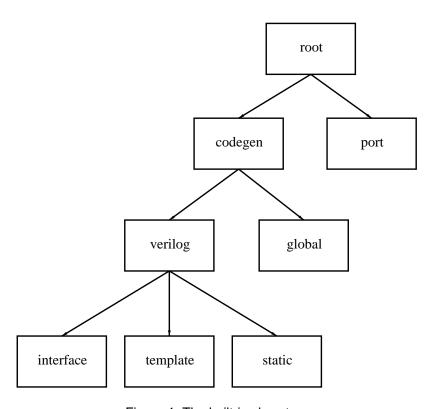

|   |      |          | Instantiation and the object tree       |    |

|---|------|----------|-----------------------------------------|----|

|   | 6.3  | An exa   | ample                                   | 66 |

|   | 6.4  | Classe   | es and inheritance                      | 70 |

|   |      | 6.4.1    | Source files and classes                | 70 |

|   |      | 6.4.2    | The phases of the object system         | 71 |

|   |      | 6.4.3    | Class definition                        | 72 |

|   |      | 6.4.4    | "Normal" methods                        | 73 |

|   |      | 6.4.5    | Methods overriding new                  | 74 |

|   |      | 6.4.6    | The autoloading mechanism               | 75 |

|   |      | 6.4.7    |                                         | 75 |

|   |      | 6.4.8    |                                         | 76 |

|   | 6.5  | The ex   | , , , , , , , , , , , , , , , , , , , , | 77 |

|   |      | 6.5.1    |                                         | 77 |

|   |      | 6.5.2    | ·                                       | 78 |

|   | 6.6  | Useful   |                                         | 79 |

|   | 6.7  |          |                                         | 80 |

|   |      | 6.7.1    | Introduction                            |    |

|   |      | 6.7.2    | Identifying a variable in PERLILOG      |    |

|   |      | 6.7.3    | Variable drive and connection           |    |

|   |      | 6.7.4    | Connecting variables with attach()      |    |

|   |      | 6.7.5    |                                         | 83 |

|   |      | 6.7.6    |                                         | 85 |

|   |      | 6.7.7    |                                         | 85 |

|   | 6.8  |          | •                                       | 86 |

|   | 0.0  | 6.8.1    |                                         | 86 |

|   |      | 6.8.2    | •                                       | 86 |

|   | 6.9  |          |                                         | 87 |

|   | 0.0  | 6.9.1    |                                         | 87 |

|   |      | 6.9.2    |                                         | 87 |

|   |      | 6.9.3    | Variables of static objects             |    |

|   |      | 6.9.4    | Example of using a static object        |    |

|   |      | 6.9.5    |                                         | 90 |

|   | 6 10 |          |                                         | 90 |

|   | 0.10 |          |                                         | 90 |

|   |      |          | ' '                                     | 91 |

|   |      |          |                                         | 92 |

|   | 6 11 |          | ary: How to write classes properly      |    |

|   | 0.11 | Cullilli | ary. Flow to write diasses properly     | J2 |

| 7 | Port | s and o  | creating interface classes              | 94 |

|   |      |          | <del>-</del>                            | 94 |

|   |      | 7.1.1    | •                                       | 94 |

|   |      | 7.1.2    | ·                                       | 95 |

|   |      | 7.1.3    | · •                                     | 95 |

|   |      | 7.1.4    | 1 1 7                                   | 96 |

|   | 7.2  |          | ·                                       | 97 |

|   |      | 7.2.1    |                                         | 97 |

|   |      |          |                                         | ٠, |

|     | 7.2.2  | Approaching interface objects                     | . 97  |

|-----|--------|---------------------------------------------------|-------|

|     | 7.2.3  | Assumptions to start with                         | . 97  |

|     | 7.2.4  | The Perl snippets presented                       |       |

| 7.3 | The va | ars2vars class in detail ........................ |       |

|     | 7.3.1  | Example revisited                                 | . 98  |

|     | 7.3.2  | The attempt() method                              | . 99  |

|     | 7.3.3  | The nick property                                 |       |

|     | 7.3.4  | The generate method                               | . 100 |

|     | 7.3.5  | The labelID() method                              | . 100 |

|     | 7.3.6  | Doing the actual work                             | . 101 |

| 7.4 | The wh | bsimple class                                     | . 102 |

| 7.5 | The va | ars2wbm <b>class</b>                              | . 103 |

|     | 7.5.1  | A more complex attempt()                          | . 103 |

|     | 7.5.2  | A call to intobjects()                            | . 104 |

|     | 7.5.3  | Whose port is this anyway?                        | . 106 |

|     | 7.5.4  | The whereto() method                              | . 107 |

|     | 7.5.5  | Creating new variables                            | . 107 |

|     | 7.5.6  | Setting up the labels property                    | . 108 |

|     | 7.5.7  | The rest of the class                             | . 108 |

|     | 7.5.8  | The IDvar() method                                | . 109 |

|     | 7.5.9  | The copyvar() method                              | . 109 |

|     | 7.5.10 | codetargets() and whereto()                       | . 110 |

| 7.6 | Two ex | xamples revisited                                 | . 111 |

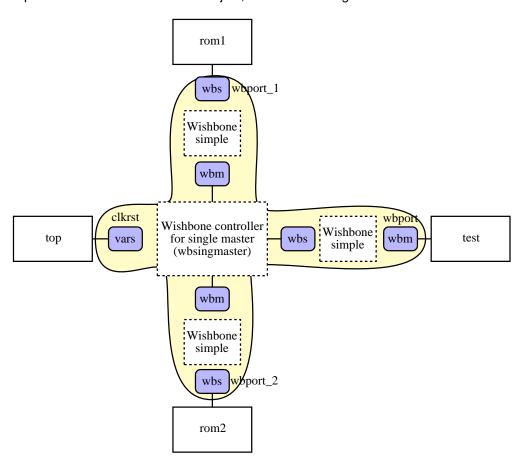

| 7.7 | The wh | bsingmaster <b>class</b>                          |       |

|     | 7.7.1  | The attempt() method                              | . 114 |

|     | 7.7.2  | The generate() method                             |       |

|     | 7.7.3  | Setting up the slave port                         | . 117 |

|     | 7.7.4  | Retrieving bit range                              |       |

|     | 7.7.5  | Some initializations                              |       |

|     | 7.7.6  | The main loop                                     |       |

|     | 7.7.7  | The mates property                                |       |

|     | 7.7.8  | Creating the slave selector                       |       |

|     | 7.7.9  | · · · · · · · · · · · · · · · · · · ·             |       |

|     | 7.7.10 | Slave-specific Verilog code                       | . 122 |

|     | 7.7.11 | Setting up labels                                 | . 123 |

|     |        | ! Grand finale                                    |       |

|     |        | What we didn't have in this class                 |       |

| 7.8 | The el | lements of an interface class                     |       |

|     | 7.8.1  | The common methods                                |       |

|     | 7.8.2  | The elements of the attempt() method              |       |

|     | 7.8.3  | The elements of the generate() method             |       |

| 7.9 |        | PERLILOG uses interface classes                   |       |

|     | 7.9.1  | Registration of interface classes                 |       |

|     | 7.9.2  | Quering order of interface classes                |       |

|     | 7.9.3  | <pre>interface() VS. intobjects()</pre>           |       |

|     | 7.9.4  | intobjects() and recursive calls                  | . 127 |

|   | 7.10 Transi | ent objects                              | . 128 |

|---|-------------|------------------------------------------|-------|

|   | 7.10.1      | Why transient objects                    | . 128 |

|   |             | ! How it works                           |       |

|   |             | Guidelines for correct code              |       |

|   | 7.10.4      | The sustain() method                     | . 130 |

|   | 7.11 Advan  | nced issues                              | . 131 |

|   |             | Dispatch classes                         |       |

|   |             | Static objects in interface objects      |       |

|   |             | Objects that don't generate files        |       |

| 8 | PERLILOG    | main script API                          | 135   |

| • |             | ted subroutines                          |       |

|   | 8.1.1       | The exported subroutine init()           |       |

|   | 8.1.2       | The exported subroutine inherit()        |       |

|   | 8.1.3       | The exported subroutine inheritdir()     |       |

|   | 8.1.4       | The exported subroutine override()       |       |

|   | 8.1.5       | The exported subroutine underride()      |       |

|   | 8.1.6       | The exported subroutine definedclass()   |       |

|   | 8.1.7       | The exported subroutine globalobj()      |       |

|   | 8.1.8       | The exported subroutine execute()        |       |

|   | 8.1.9       | The exported subroutine interfaceclass() |       |

|   |             | lobal variables                          |       |

|   | 8.2.1       | The variable \$VERSION                   |       |

|   | 8.2.2       | The variable \$globalobject              |       |

|   | 8.2.3       | The variable %classes                    |       |

|   | 8.2.4       | The variable %objects                    |       |

|   | 8.2.5       | The variable @VARS                       |       |

|   | 8.2.6       | The variable @EQVARS                     |       |

|   | 8.2.7       | The variable @interface_classes          |       |

|   | 8.2.8       | The variable \$interface_rec             |       |

| 9 | The root cl | ass ADI                                  | 144   |

| 3 |             | ids                                      |       |

|   | 9.1.1       | The method new()                         |       |

|   | 9.1.2       | The method set()                         |       |

|   | 9.1.3       | The method get()                         |       |

|   | 9.1.4       | The method const()                       |       |

|   | 9.1.5       | The method globalobj()                   |       |

|   | 9.1.6       | The method who()                         | 140   |

|   | 9.1.7       | The method safewho()                     |       |

|   | 9.1.8       | The method isobject()                    |       |

|   | 9.1.9       | The method objbyname()                   |       |

|   |             | The method objdump()                     |       |

|   |             | The method suggestname()                 |       |

|   |             | ! The method addmagic()                  |       |

|   |             | The method addinagre()                   |       |

|   | 5.1.15      |                                          |       |

|    |        |                | The method            |                         |       |     |      |      |      |   |      |   |                    |

|----|--------|----------------|-----------------------|-------------------------|-------|-----|------|------|------|---|------|---|--------------------|

|    | 9      | .1.15          | The method            | pshift()                |       |     |      | <br> | <br> |   | <br> |   | <br>158            |

|    | 9      | .1.16          | The method            | ppop()                  |       |     |      | <br> | <br> |   | <br> |   | <br>159            |

|    | 9      | .1.17          | The method            | punshift()              | )     |     |      | <br> | <br> |   | <br> |   | <br>159            |

|    | 9      | .1.18          | The method            | ppush().                |       |     |      | <br> | <br> |   | <br> |   | <br>160            |

|    | 9      | .1.19          | The method            | addchild()              | )     |     |      | <br> | <br> |   | <br> |   | <br>161            |

|    | 9      | .1.20          | The method            | prettyval               | () .  |     |      | <br> | <br> |   | <br> |   | <br>161            |

|    | 9      | .1.21          | The method            | linebreak               | () .  |     |      | <br> | <br> |   | <br> |   | <br>162            |

|    |        |                | The method            |                         |       |     |      |      |      |   |      |   |                    |

|    | 9.2 F  | roper          | ties                  |                         |       |     |      | <br> | <br> |   | <br> |   | <br>163            |

|    | 9      | .2.1           | The property          | /name                   |       |     |      | <br> | <br> |   | <br> |   | <br>163            |

|    | 9      | .2.2           | The property          | parent                  |       |     |      | <br> | <br> |   | <br> |   | <br>163            |

|    | 9      | .2.3           | The property          | / children              |       |     |      | <br> | <br> |   | <br> |   | <br>164            |

|    | 9      | .2.4           | The property          | /nick                   |       |     |      | <br> | <br> |   | <br> |   | <br>164            |

|    | 9      | .2.5           | The property          | / perlilog-             | -tran | sie | nt . | <br> | <br> |   | <br> |   | <br>165            |

|    | 9      | .2.6           | The property          | treepath                |       |     |      | <br> | <br> |   | <br> |   | <br>165            |

|    |        |                |                       | _                       |       |     |      |      |      |   |      |   |                    |

| 10 |        |                | enerating cl          |                         |       |     |      |      |      |   |      |   | 167                |

|    |        |                | ds                    |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | The method            |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | The method            |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | The method            |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | The method            |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | The method            |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | The method            |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | The method            |                         |       |     |      |      |      |   |      |   |                    |

|    | 1      | 0.1.8          | The method            | whereto()               |       |     |      | <br> | <br> | - | <br> |   | <br>171            |

| 44 | The W  | مواامه         | , alaaa ADI           |                         |       |     |      |      |      |   |      |   | 172                |

| 11 |        |                | class API             |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | ds                    |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | The method The method |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | The method            |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | The method            |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                |                       |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | The method The method |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | The method            |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | The method            |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | ties                  |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | The property          |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | The property          |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                |                       |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | The property          |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                |                       |                         |       |     |      |      |      |   |      |   |                    |

|    |        |                | The property          |                         |       |     |      |      |      |   |      |   |                    |

|    | 1      | 1.2.5          | The property          | / insname .             |       |     |      | <br> | <br> |   | <br> |   | <br>179            |

|    | 1<br>1 | 1.2.5<br>1.2.6 |                       | y insname .<br>y static |       |     |      | <br> | <br> |   | <br> | : | <br><br>179<br>180 |

|    |      | 11.2.8 The property perlilog-no-file                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 180 |

|----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 12 |      | Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|    | 12.2 | 12.1.1 The method execute()                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|    | 12.2 | Properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|    |      | · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|    |      | 12.2.2 The property great are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|    |      | 12.2.3 The property system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|    |      | 12.2.4 The property man_initial not_ittle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 102 |

| 13 |      | the state of the s | 83  |

|    | 13.1 | Port object properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|    |      | 13.1.1 The property labels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|    |      | 13.1.2 The property mates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|    | 13.2 | ! Interface object properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|    |      | 13.2.1 The property perlilog-ports-to-connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 183 |

| Α  | GNU  | J FDL license                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 84  |

|    |      | PREAMBLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|    | A.1  | APPLICABILITY AND DEFINITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 184 |

|    | A.2  | VERBATIM COPYING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 186 |

|    | A.3  | COPYING IN QUANTITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 186 |

|    | A.4  | MODIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 187 |

|    | A.5  | COMBINING DOCUMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 189 |

|    |      | COLLECTIONS OF DOCUMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|    |      | AGGREGATION WITH INDEPENDENT WORKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|    |      | TRANSLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|    |      | TERMINATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|    | A.10 | ) FUTURE REVISIONS OF THIS LICENSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 191 |