# A Pipelined RISC CPU

# Aquarius

(SuperH-2 ISA Compatible CPU Core)

# **Thorn Aitch**

Rev 1.1 July 21, 2003

### Copyright

Aquarius RTL codes and related documents are copyrighted by the author, but placed into the public domain.

Designs can be altered while keeping list of modifications "the same as in GNU" No money can be earned by selling the designs themselves, but anyone can get money by selling the implementation of the design, such as ICs based on some cores, boards based on some schematics or Layouts, and even GUI interfaces to text mode drivers. "The same as GPL SW" Any update to the design should be documented and returned to the design. Any derivative work based on the IP should be free under OpenIP License. Derivative work means any update, change or improvement on the design. Any work based on the design can be either made free under OpenIP license or protected by any other license. Work based on the design means any work uses the OpenIP Licensed core as a building black without changing anything on it with any other blocks to produce larger design. There is NO WARRANTY on the functionality or performance of the design on the real hardware implementation.

On the other hand, the SuperH-2 ISA (Instruction Set Architecture) executed by Aquarius is rigidly the property of Renesas Technology Corp., which has established on April 1st, 2003 by merging semiconductor groups of Hitachi and Mitsubishi. Then you have responsibility to judge if there are not any infringements to Renesas's rights regarding your Aquarius adoption into your design. By adopting Aquarius, the user assumes all responsibility for its use.

#### Trademark

Aquarius is a name of 5-stages pipelined RISC CPU core that can execute SuperH-2 ISA. Aquarius is not registered trademark. If you officially use the name of Aquarius to external world, you have responsibility to care the legal issues.

#### **Royalty Release**

I will not request you any royalties or other financial obligation for your Aquarius adoption to your design and production. But you have responsibility to judge the usage of SuperH-2 ISA, legally. I strongly recommend you should ask Renesas Technology Corp. when you

decide to adopt Aquarius into your products.

#### **Patent Notice**

I have not cared that the information contained in this document and Aquarius deliverables cause infringement on the patent, copyright, trademark or trade secret rights of others. You have all responsibilities for determining if your design and products infringe on the intellectual property rights of others.

#### **Disclaimers**

Aquarius deliverables including this document are not guaranteed. They may cause any damages to many things, for example, loss of properties, data, money, profits, life, or business. By adopting Aquarius, the user assumes all responsibility for its use.

Aquarius deliverables are permanently preliminary, and is subject to change.

#### **Contact to Author**

After release of Aquarius onto the OpenCores Organization site, you will be able to contact me via the organization's site. The email address is thorn\_aitch@opencores.org.

If you find any bugs and strange descriptions, please feel free to inform me.

#### Trademark

SuperH™ is a trademark of Renesas Technology Corp.

Virtex<sup>™</sup> is a trademark of Xilinx, Inc.

Stratix<sup>TM</sup> is a trademark of Altera, Corp.

Each another proper noun might be a trademark of each rights holders.

# **Revision History**

Rev 0.1: May 1, 2003 by Thorn Aitch Draft

Drafting out a tentative document

Rev 1.0: July 12, 2003 by Thorn Aitch Release Version

A First Release Version

Rev 1.1: July 21, 2003 by Thorn Aitch Addition of an application A Program for calculation of Circular Constant (Pi) is added.

# Index

| PART1. | USING AQUARIUS                               | 8  |

|--------|----------------------------------------------|----|

| 1. IN  | TRODUCTION                                   | 9  |

| 1.1.   | What is Aquarius                             | 9  |

| 1.2.   | PURPOSE OF THIS PROJECT                      | 10 |

| 1.3.   | STRUCTURE OF CHAPTERS IN THIS DOCUMENT       | 11 |

| 2. SP  | ECIFICATION OVERVIEW                         | 12 |

| 2.1.   | AQUARIUS INSTRUCTION SET ARCHITECTURE        | 12 |

| 2.2.   | INTERRUPTS AND EXCEPTIONS                    | 12 |

| 2.3.   | DIFFERENCES BETWEEN AQUARIUS AND SUPERH-2    | 13 |

| 2.4.   | AQUARIUS BLOCK DIAGRAM                       | 14 |

| 2.5.   | EXAMPLES OF AQUARIUS BASED SoC               | 16 |

| 3. PR  | EPARATION                                    | 18 |

| 3.1.   | PC ENVIRONMENT.                              | 18 |

| 3.2.   | CYGWIN                                       | 18 |

| 3.3.   | ICARUS VERILOG                               | 18 |

| 3.4.   | GNU ASSEMBLER AND C COMPILER FOR SUPERH-2    | 18 |

| 3.5.   | FPGA DEVELOPMENT TOOL                        | 20 |

| 3.6.   | FPGA Board                                   | 20 |

| 4. DE  | LIVERABLES                                   | 21 |

| 4.1.   | DOCUMENT                                     | 21 |

| 4.2.   | RTL RESOURCES                                | 21 |

| 4.3.   | VERIFICATION RESOURCES                       | 23 |

| 4.4.   | FPGA RELATED RESOURCES                       | 24 |

| 5. AQ  | UARIUS CPU INTERFA CE SPECIFICATION: "CPU.V" | 26 |

| 5.1.   | AQUARIUS CPU IN/OUT SIGNALS                  | 26 |

| 5.2.   | SYSTEM SIGNALS                               | 26 |

| 5.3.   | "WISHBONE" COMPLIANT BUS SIGNALS             | 27 |

| 5.4.   | HARDWARE EVENT SIGNALS (INTERRUPT)           | 30 |

| 5.5.         | SLEEP SIGNAL FOR LOW POWER MODE         | 32 |

|--------------|-----------------------------------------|----|

| 6. SI        | MULATION TEST BENCH                     | 34 |

| 6.1.         | Top Layer: "top.v"                      | 34 |

| 6.2.         | SIMULATION TEST BENCH: "TEST.V"         | 34 |

| 6.3.         | PARALLEL I/O PORT (PIO): "PIO.V"        | 34 |

| 6.4.         | SERIAL I/O (UART): "UART.V"             | 37 |

| 6.5.         | System Controller (SYS): "sys.v"        | 39 |

| 6.6.         | On Chip Memory: "memory.v"              | 42 |

| 6.7.         | SIMULATION TOOLS AND FLOWS              | 43 |

| 7. FP        | PGA IMPLEMENTATION                      | 45 |

| 7.1.         | FPGA System                             | 45 |

| 7.2.         | CIRCUIT OF FPGA BOARD                   | 46 |

| 7.3.         | CIRCUIT OF INTERFACE BOARD              | 46 |

| 7.4.         | FPGA CONFIGURATION                      | 49 |

| 7.5.         | RESULTS OF FPGA CONFIGURATION           | 49 |

| 7.6.         | APPLICATION PROGRAMS ON THE FPGA SYSTEM | 51 |

| PART2        | 2. INSIDE AQUARIUS CPU                  | 56 |

| 8. AG        | QUARIUS CPU OVERVIEW                    | 57 |

| 8.1.         | AQUARIUS BLOCK DIAGRAM                  | 57 |

| 8.2.         | AQUARIUS CPU IN/OUT SIGNALS             | 59 |

| 9. O\        | VERVIEW OF PIPELINE CONTROL             | 60 |

| 9.1.         | PIPELINE AND STAGE                      | 60 |

| 9.2.         | PIPELINE OF EACH INSTRUCTION            | 61 |

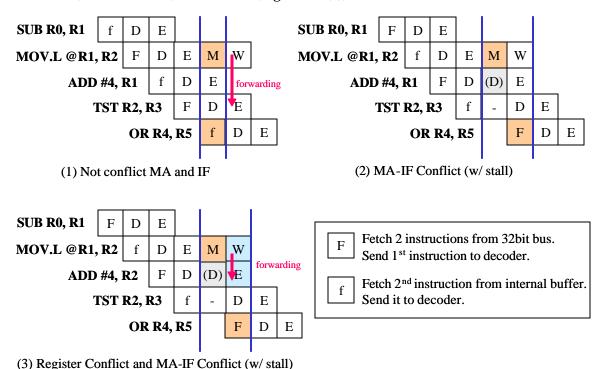

| 9.3.         | REGISTER CONFLICT                       | 64 |

| 9.4.         | MEMORY ACCESS CONFLICT                  | 64 |

| 9.5.         | Who issues IF? Who issues ID?           | 65 |

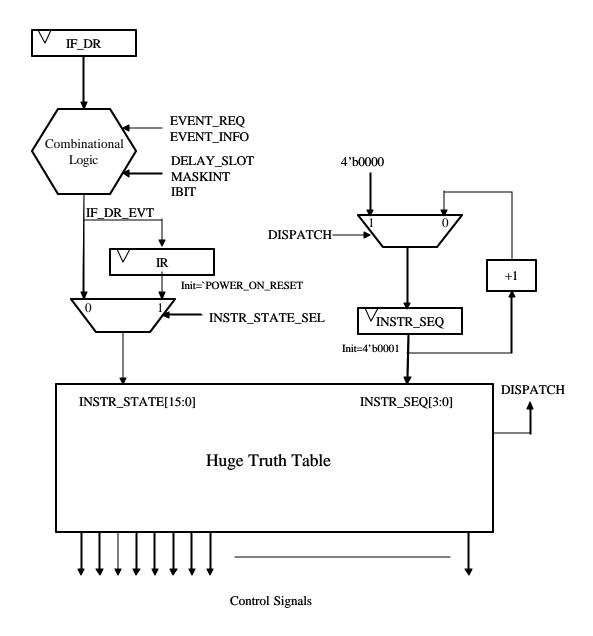

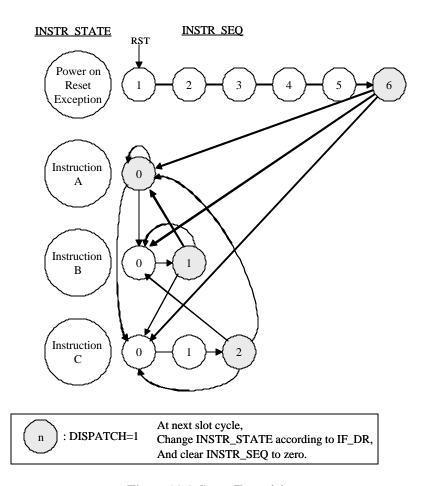

| <b>10.</b> ] | DECODER UNIT                            | 66 |

| 10.1         | . IN/OUT SIGNALS                        | 66 |

| 10.2.  | STRUCTURE OF DECODER UNIT                       | 68  |

|--------|-------------------------------------------------|-----|

| 10.3.  | SHIFTING CONTROL SIGNALS                        | 72  |

| 10.4.  | PIPELINE STALL                                  | 74  |

| 10.5.  | REGISTER FORWARDING                             | 77  |

| 10.6.  | Examples of Pipeline Control                    | 77  |

| 10.7.  | CONTROL OF PROGRAM COUNTER                      | 77  |

| 11. M  | EMORY ACCESS CONTROL UNIT                       | 82  |

| 11.1.  | IN/OUT SIGNALS                                  | 82  |

| 11.2.  | WISHBONE'S ACK AND AQUARIUS' SLOT               | 82  |

| 11.3.  | Instruction Fetch Cycle                         | 83  |

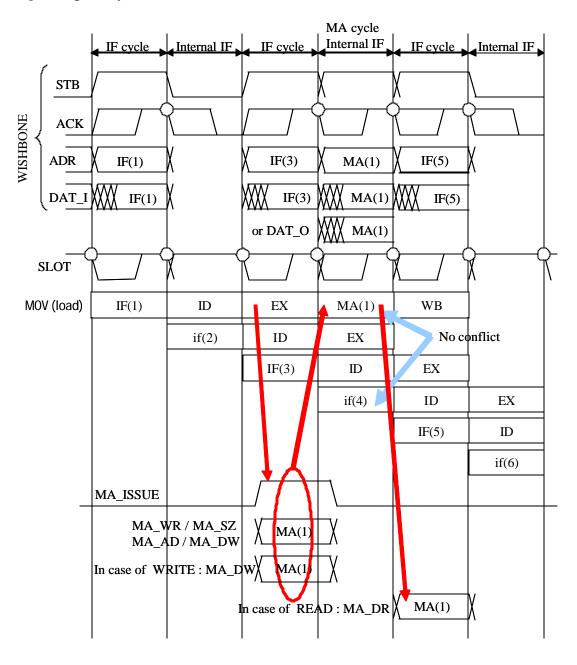

| 11.4.  | MEMORY ACCESS CYCLE                             | 84  |

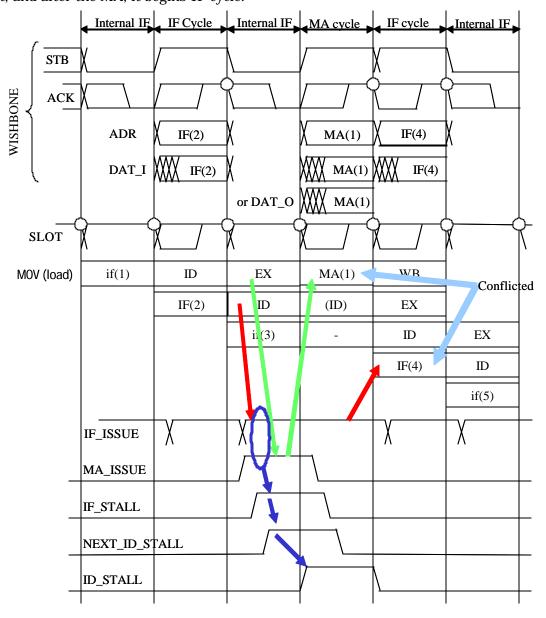

| 11.5.  | IF-MA CONFLICT                                  | 86  |

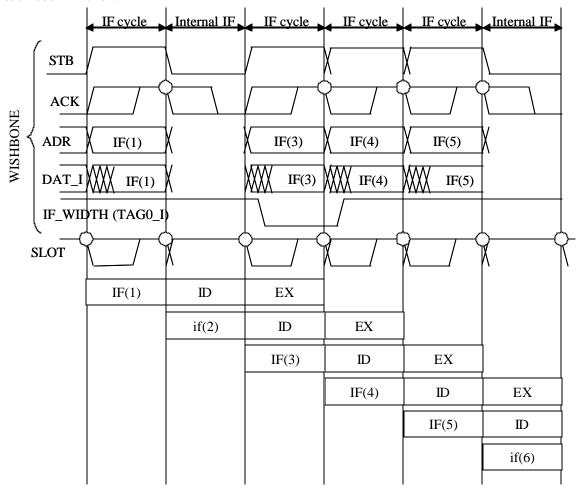

| 11.6.  | BUS WIDTH OF INSTRUCTION FETCH CYCLE (IF_WIDTH) | 87  |

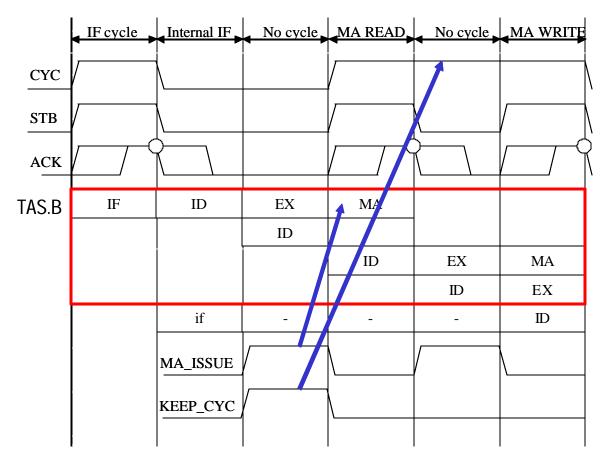

| 11.7.  | READ MODIFY WRITE CYCLE (FOR INSTRUCTION TAS.B) | 87  |

| 11.8.  | STATE MACHINE OF MEMORY ACCESS CONTROL UNIT     | 88  |

| 12. DA | ATA PATH UNIT                                   | 90  |

| 12.1.  | IN/OUT SIGNAL TABLE                             | 90  |

| 12.2.  | STRUCTURE OF DATA PATH                          | 92  |

| 13. M  | ULTIPLIER UNIT                                  | 95  |

| 13.1.  | IN/OUT SIGNAL TABLE                             | 95  |

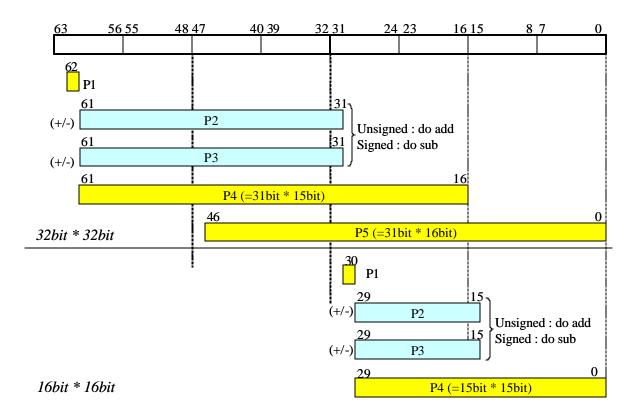

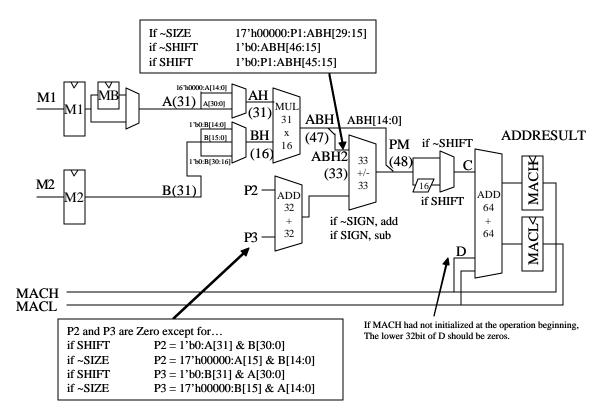

| 13.2.  | ALGORITHM OF MULTIPLICATION                     | 95  |

| 13.3.  | STRUCTURE OF MULTIPLIER UNIT                    | 98  |

| 13.4.  | CONTROL OF MULTIPLICATION UNIT                  | 99  |

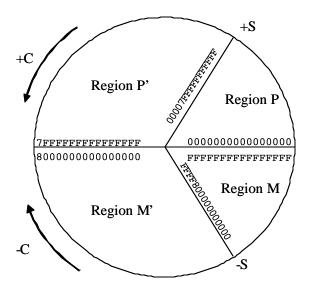

| 13.5.  | HOW TO IMPLEMENT SATURATING ACCUMULATION        | 100 |

| 14. AI | PPENDIX: AQUARIUS INSTRUCTION CODES             | 105 |

# Part1. Using Aquarius

# 1. Introduction

# 1.1. What is Aquarius

Aquarius is a Core IP (Intellectual Property) of pipelined RISC CPU and can execute SuperH-2 instructions. Aquarius and related information are released to OpenCores Organization web site (<a href="www.opencores.org">www.opencores.org</a>). You can freely download all necessary resources and latest updates from the site.

The reasons why I selected SuperH-2 ISA (Instruction Set Architecture) are as follows.

- (1) SuperH is a very popular CPU core. The software development environments such as C compiler have been well prepared. The GNU C compiler for SuperH is very famous and easy to get. The SuperH had been developed by Hitachi, Ltd. Now, semiconductor group of Hitachi has merged with same group of Mitsubish and new semiconductor company "Renesas Technology Corp." has established in April, 2003.

- (2) SuperH-2 is a CPU for MCU (Micro Controller Unit). Then the CPU need not handle complex exception recovering such as memory fault exception from MMU (Memory Managing Unit). This means SuperH-2 has simple structure, easiness to design, and it does not consume many logic gates and power.

- (3) All SuperH-2 instructions have 16bit length. It also makes the hardware very simple. And most important aspect from 16bit fixed length of instructions is that the object code size compiled from C source programs becomes very small.

- (4) And, I love SuperH.

Aquarius is a free and completed soft IP. So I believe that Aquarius can increase SuperH-2 ISA familiars.

Aquarius consists of RTL descriptions. The language is Verilog-HDL. You can implement Aquarius not only in your System LSI but also in your FPGA system. The Aquarius bus interface follows WISHBONE specification maintained by the OpenCores Organization (<a href="https://www.opencores.org">www.opencores.org</a>), so you can easily connect Aquarius to many IPs registered in OpenCores web site.

During my Aquarius design, I only referred public SuperH document from Renesas such as SH-2 Programming Manual. Of course I could not reach Renesas' internal design information, so the Aquarius may NOT have completely same functionality as real SuperH-2 CPU core, however, Aquarius can execute all public instructions of SuperH-2.

The functionality of Aquarius has been verified by both methods of functional vector simulation and long run tests on FPGA board using program codes from GNU C Compiler and Assembler.

I have designed Aquarius without consuming money except for FPGA hardware. I have used free simulation tools and free FPGA configuration tool. You also do not need to buy expensive EDA tools.

I am not an expert designer of CPU core, so the current Aquarius may not have the best performance. I think efficiency of the design such as area consumption and operation frequency can be improved much more. If you find some improvements, please feel free to suggest your ideas to me.

Please enjoy the exciting deep IP design world. You can modify Aquarius to make your original system. I hope Aquarius will help system designers, university students and electronics hobbyists.

#### 1.2. Purpose of this Project

The main purpose of Aquarius Project is to provide everyone a pipelined RISC CPU core as one of the IPs for System LSI and FPGA system. You can get information about how to design actual useful RISC CPU.

The Aquarius has SuperH-2 compatible ISA, so I hope that SuperH familiarized people will increase more and more. Many embedded system, for example Robots, Industrial Systems, Measurement Instruments, and many kind of digital information systems controlled by embedded micro controllers, can be realized by SuperH-2 architecture.

I provide Aquarius without any license fee and royalty. You can freely get the latest

Aquarius IP codes from OpenCores Organization on the internet whenever you like. And I will introduce you the cheapest but excellent design environments via this document. You will able to modify Aquarius and establish your original IP.

# 1.3. Structure of Chapters in this document

This document consists of 2 parts. The first part describes how to use Aquarius, for example, explanation of interface signals, test bench and FPGA implementation. All readers should read first part. The second part shows inside Aquarius which is way of thought for designing a pipelined RISC CPU. If you want to understand the apparatus of pipelined RISC CPU and want to design your original CPU core, you should read second part, too.

# 2. Specification Overview

# 2.1. Aquarius Instruction Set Architecture

Aquarius is based on SuperH-2 Instruction Set Architecture (ISA). The SuperH-2 CPU has RISC-type instruction sets and 16 32bit-general-registers (R0-R15). All instructions have 16bits fixed length. The SuperH-2 is based on 5 stages pipelined architecture, so basic instructions are executed in one clock cycle pitch, which dramatically improves instruction execution speed. The CPU also has an internal 32-bit architecture for enhanced data processing ability such as multiply and accumulation like DSP functionality.

The detail document of SuperH-2 CPU architecture can be found in Renesas web site.

#### http://www.renesas.com/

Please reach to the SuperH product page and find the SH-2 related product documents. Then search document type of "Programming Manual" and find the "SuperH RISC Engine SH-1/SH-2/SH-DSP Programming Manual". This manual includes explanations among SH-1, SH2 and SH2-DSP Instruction set. Please check up only SH-2 portions from this manual. But it does not describe about exception and interrupt. For that information, pick up product manual such as "SH7040 series Hardware Manual" and refer to chapters regarding Exception and Interrupt Controller.

#### 2.2. Interrupts and Exceptions

Like SuperH-2 CPU, Aquarius can handle interrupt requests, such as NMI (non maskable interrupt) and IRQ (interrupt request). The interrupt priority level can be set from 0 to 16. The interrupt request whose priority level is higher than I bit (I3-I0) in SR (Status Register) will accepted by CPU. The priority of NMI is 16, so it is always accepted. The priority level and the vector number of IRQ can be informed from external circuit such as interrupt controller or system controller. If the priority level is zero, such interrupt will not be accepted. Once the interrupt is accepted, the interrupt exception will start. It copies the interrupt request level to I bit (I3-I0) in SR ,push SR and PC onto stack, fetch the vector address and branch to targeting interrupt service routine. To return from interrupt service routine, use RTE, which pops PC and SR and starts from the address of popped PC.

By the 4 bit priority control scheme, the interrupt can be nested.

The other exceptions such as CPU address error, DMA address error, TRAP Instruction, Illegal Instruction, Slot Illegal Instruction, Manual Reset and Power on Reset are fully supported by Aquarius.

## 2.3. Differences between Aquarius and SuperH-2

Aquarius can execute all public SuperH-2 instructions. But there are some functional differences between Aquarius and real SuperH-2 CPU.

#### (1) Improvement of Multiplication Cycle

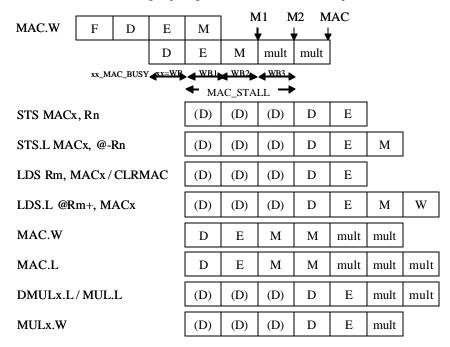

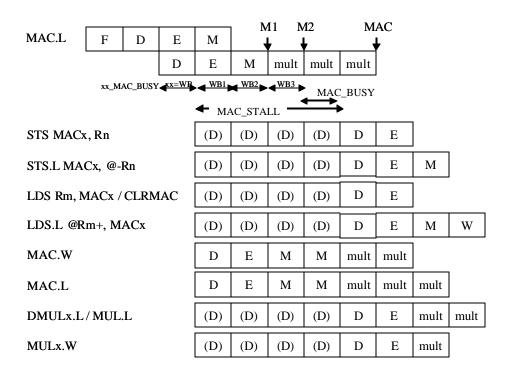

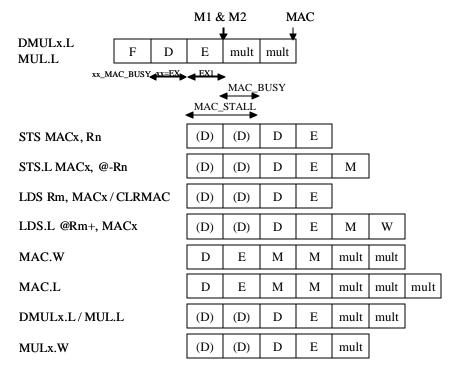

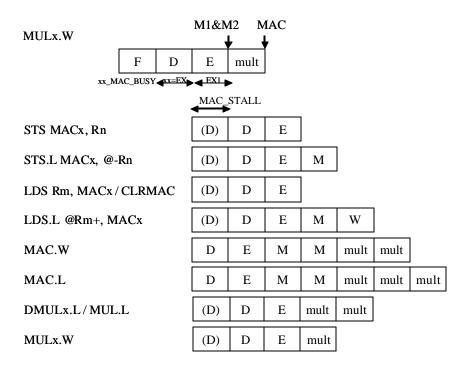

Table 2.1 shows that the execution cycle of the multiplication related instructions of Aquarius are slightly different from SuperH-2's because I guess the structure of connection between CPU and Multiplier is changed from real SuperH-2. You can find some performance is improved. Especially, the pitch cycle reduction of MAC.L will improve performance of many real time applications. The details of pipeline control will be shown in later chapter.

| Instruction      | Aquarius              | SuperH-2              | Notes |

|------------------|-----------------------|-----------------------|-------|

| MAC.W @Rm+, @Rn+ | C=2, P=2, L=3         | C=2, P=2, L=2         |       |

| MAC.L @Rm+, @Rn+ | C=2, <b>P=2</b> , L=4 | C=2, <b>P=4</b> , L=4 |       |

| MULS/U.W Rm, Rn  | C=1, <b>P=1</b> , L=2 | C=1, <b>P=2</b> , L=2 |       |

| DMULS/U.L Rm, Rn | C=1, <b>P=3, L=2</b>  | C=1, <b>P=4, L=4</b>  |       |

| MUL.L Rm, Rn     | C=1, <b>P=3, L=2</b>  | C=1, <b>P=4, L=4</b>  |       |

$<sup>\</sup>boldsymbol{C}$  (Cycle): Instruction Execution Cycle if there is no contention. This is minimum cycle.

Table 2.1. Differences of Instruction Execution Cycles between Aquarius and SuperH-2

#### (2) Detection of Illegal Instruction

The real SuperH-2 decodes all illegal instructions. But in Aquarius, only the FF-line instructions (0xFFxx) are recognized as illegal instructions that bring up "Illegal Instruction Exception". Other "should-be illegal instructions" are not fully decoded, so these operations are seemed as "Undefined". Actually, the operation of undefined instructions will be just same as similar code's instruction. By this shortcut, the usage of area is reduced. Of course, the Slot Illegal Exception (in the case that a branch instruction placed at the

P (Pitch): Instruction Execution Pitch cycle if same instructions are repeated.

L (Latency): Latency cycle until STS, which is located just after me, and stores MACH/MACL to Rn.

delay slot of delayed branch) is completely detected.

Even **f** you want Aquarius to detect all illegal instructions, you can easily modify the decode unit's RTL code.

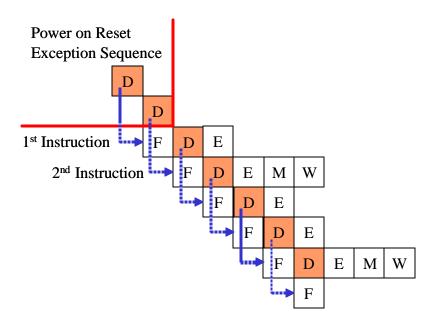

#### (3) Instruction Codes for Exception

Some instructions in F-line (0xFxxx) are used for launching exceptions. These are shown in Tabel2.2, which are not defined in actual SuperH ISA. In the CPU decoder, the hardware event, for example interrupt, exchanges a fetched instruction to another code (in Table1.2) which launches exception, and then changes the control sequence from normal instruction's one to the exception's. If these instructions exist in program code, corresponding exception will start, but will not have correct operation, such as interrupt priority control. I recommend you not to write the Exception Launch Instructions in program code.

| Instruction | Correct Code | Exception Sequence | Notes                            |

|-------------|--------------|--------------------|----------------------------------|

| 0xF7xx      | 0xF700       | Power On Rest      | Lower 8bit is used as vector No. |

| 0xF6xx      | 0xF602       | Manual Reset       | Lower 8bit is used as vector No. |

| 0xF3xx      | 0xF30A       | DMA Address Error  | Lower 8bit is used as vector No. |

| 0xF2xx      | 0xF209       | CPU Address Error  | Lower 8bit is used as vector No. |

| 0xF1xx      | 0xF10B       | NMI                | Lower 8bit is used as vector No. |

| 0xF0xx      | 0xF0xx       | IRQ                | Lower 8bit is used as vector No. |

| 0xFF04      | 0xFF04       | General Illegal    | Lower 8bit is used as vector No. |

| 0xFE06      | 0xFE06       | SLOT Illegal       | Lower 8bit is used as vector No. |

**Table2.2 Exception Launch Instruction**

#### (4) ICE Support Instructions

Although the actual SuperH-2 may have dedicated instructions to support the ICE (in circuit emulator), Aquarius do not have, because those instructions are not released generally. In the test bench of Aquarius, I have implemented the "break" function by NMI (non maskable interrupt).

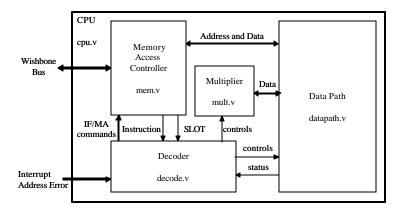

#### 2.4. Aquarius Block Diagram

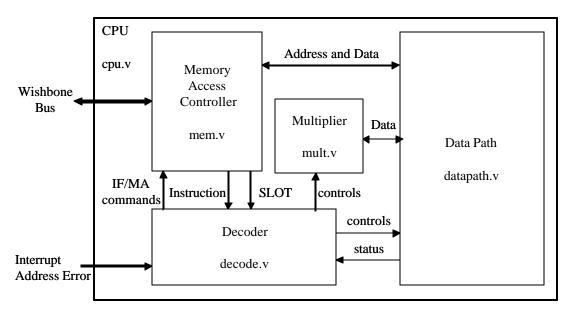

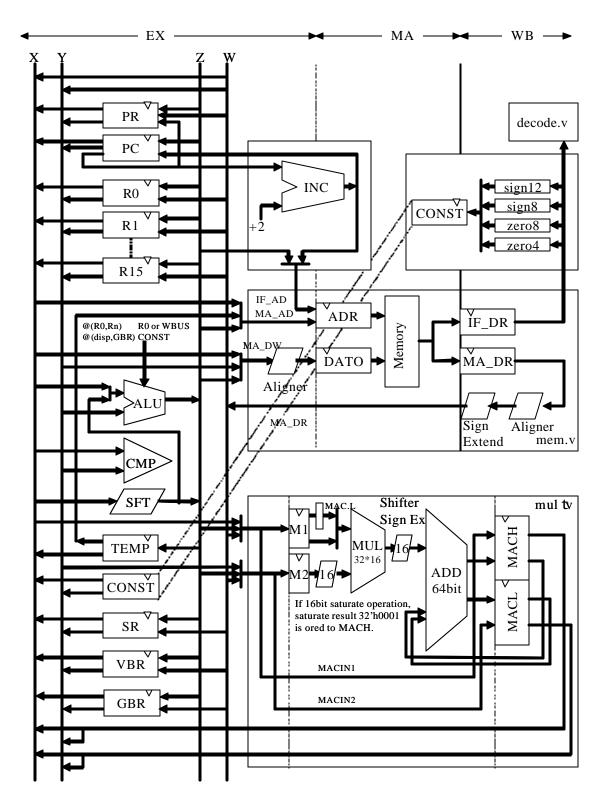

Figure 2.1 shows the block diagram of Aquarius CPU core.

Figure 2.1. Block Diagram of Aquarius

Top layer of Aquarius is "CPU" which has WISHBONE compliant bus signals and accepts interruption related signals. The most important system signals such as clock and reset are not shown in this figure.

The Memory Access Controller handles instruction fetch and data read/write access. The operations of Memory Access Controller are fully controlled by Decoder unit. Memory Access Controller sends fetched instruction bit fields to the Decoder unit, and interchanges read/write data and its address with Data Path unit. Aquarius assumes the Wishbone bus is a Non-Harvard bus, then the simultaneous instruction fetch and R/W data access makes bus contention. Memory Access Controller handles such contention smoothly and informs the pipeline stall caused by the bus contention to Decoder unit. Also, the Memory Access Controller can sense each boundary of bus cycles (with wait state) from WISHBONE ACK signal. In Aquarius architecture (may be in SuperH-2 architecture as well), such bus cycle boundary corresponds to the pipeline's slot edge. So the Memory Access Controller produces the most important pipeline control signal "SLOT" indicating pipeline slot edge.

The Data Path unit has registers you can see in programmer's model in SuperH-2 manual such as General Registers (R0 to R15), Status Register (SR), Global Base Register (GBR), Vector Base Register (VBR), Procedure Register (PR) and Program Counter (PC). The Multiplication and Accumulate Registers (MACH/MACL) are found in Multiplication unit. The Data Path unit also has necessity operation resources such as ALU (Arithmetic and Logical operation Unit), Shifter, Divider, Comparator, temporary registers, many selectors,

interfaces to/from Memory Access Controller and Multiply unit, and several buses to connect each resource. The Data Path is fully controlled by control signals from Decoder unit.

Multiply unit has a 32bit x 16bit multiplier and its control circuits. A 16bit x 16bit multiply operation is executed in one clock cycle. A 32 bit x 32bit multiply operation is done in two clock cycles. Multiply unit also has the Multiplier and Accumulate Registers (MACH/MACL). The MACH/MACL are not only the final result registers of multiply or multiply-and-accumulation but also the temporary registers to hold the 48bit partial multiply result from 32bit x 16bit multiplier for 32bit x 32bit operation. The multiply instruction, for example MULS.L, clears the contents of MACH/MACL in early stage of the instruction operation. However the multiply and accumulate instruction, for example MAC.L, does not clear MACH/MACL before the operation. The MAC.L accumulates its own partial multiply result to initial MACH/MACL and then finalize the operation result. The major difference between multiply (MULS.L) and "multiply and accumulate" (MAC.L) is whether to clear or not to clear the MACH/MACL before the operation. And also, for MAC.L and MAC.W instruction, the accumulation adder in this unit has saturating function.

The Decoder unit is the fundamental CPU controller. It orders Memory Access Controller fetch instructions and then receives the instruction. The Decoder Unit decodes the instruction bit fields and judges the followed operations. Basically, the Decoder unit plays the role only for the instruction ID stage. But it throws many control signals for following EX, MA and WB stages toward Data Path unit, Multiplication unit, and Memory Access Controller. These control signals are kept and shifted with its pipeline flow at each slot edge until reaching to the target stage of the instruction. The Decoder unit detects every conditions of pipeline stalling, and makes each unit of CPU be controlled properly. Also, it controls not only simple 1 cycle instructions but also multi cycle instructions and exception's sequences such as interrupt and address error.

Detailed design description of each unit is found in Part 2.

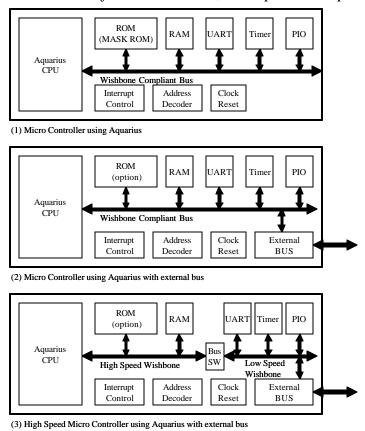

## 2.5. Examples of Aquarius based SoC

Figure 2.2 shows some examples of SoC using Aquarius.

- (1) It is a simple micro controller that has CPU, ROM, RAM and some peripherals. Each module is connected by a common Wishbone bus.

- (2) It is same as (1) except it has external bus interface. If the external bus interface is designed properly, it can be connected any memories such as ROM, Burst ROM, SRAM, SDRAM and, if you desire, DDR may be possible.

- (3) If the bus operation frequency is high (for example, over 100MHz), one common Wishbone bus will not catch up with the frequency because of heavy load. In such case, I recommend you to divide the internal bus into as least two, one is the fast speed bus with only CPU and internal fast memories, and the other one is slow speed bus with many slow peripheral modules and external memory interface.

I provide Aquarius deliverables not only as CPU core but also as MCU like (1), which has ROM, RAM, UART, PORT and System Controller (interrupt and exception controller) etc.

Figure 2.2. Examples of System LSI using Aquarius

# 3. Preparation

This chapter describes my recommendations regarding necessary preparations before starting development. You do not need any expenses except PC environment and FPGA board.

#### 3.1. PC environment

This is the most important tool. Any Windows machines are OK. I still use SONY VAIO Notebook PCG-R505FR/D with Mobile PentiumIII 800MHz, 256MB RAM, and Microsoft Windows XP. Even such machine has enough power to design Aquarius. Of course, you need broadband internet connection such as xDSL to download many required resources.

The reason why I use Windows machine instead of Linux machine is that the most "free" FPGA development tools from FPGA vendors such as Xilinx and Altera run on only Windows environment.

# 3.2. Cygwin

The simulator of Verilog-HDL codes and the compiler/assembler of SuperH-2 run on the UNIX environment. In order all tools to live together in Windows environment, the Cygwin is a good selection. Download the latest Cygwin system from <a href="http://www.cygwin.com">http://www.cygwin.com</a>, and full-install to your PC according to its instructions. After the Cygwin installation, many UNIX/Linux applications and all Windows applications simultaneously run on your PC without circumstances.

# 3.3. Icarus Verilog

I think the most excellent free Verilog simulator is Icarus Verilog. Download Icarus from <a href="http://www.icarus.com/eda/verilog/index.html">http://www.icarus.com/eda/verilog/index.html</a> and install it from Cygwin console window according to Icarus's installation document. If you have installed Cygwin with full packages, you will not encounter any problems.

# 3.4. GNU Assembler and C Compiler for SuperH-2

To make verification program and to develop application program, the SuperH-2 assembler and compiler are necessary for you. Install them as follows.

(1) Download following files from <a href="ftp://ftp.gnu.org/pub/gnu/">ftp://ftp.gnu.org/pub/gnu/</a>

```

binutils-2.13.1.tar.gz

gcc-2.95.3.tar.gz

gdb-5.2.1.tar.gz

```

(2) Download following file from <a href="http://sources.redhat.com/newlib/">http://sources.redhat.com/newlib/</a>

```

newlib-1.10.0.tar.gz

```

- (3) Place these 4 files under /usr/local/src.

- (4) Install GNU binutils.

```

cd /usr/local/src

gzip -dc binutils-2.13.1.tar.gz | tar xvf -

cd binutils-2.13.1

mkdir work

cd work

../configure --prefix=/usr/local --target=sh-elf

make

make install

```

(5) Install GNU gcc and newlib.

```

cd /usr/local/src

gzip -dc newlib-1.10.0.tar.gz | tar xvf -

gzip -dc gcc-2.95.3.tar.gz | tar xvf -

cd gcc-2.95.3

ln -s ../newlib-1.10.0/newlib .

mkdir work

cd work

../configure --prefix=/usr/local --target=sh-elf --with-gnu-as

--with-gnu-ld --with-dwarf2 --disable-multilib --enable-languages=c

--with-newlib

make

make install

```

(6) Install GNU gdb.

```

cd /usr/local/src

gzip -dc gdb-5.2.1.tar.gz | tar xvf -

```

```

cd gdb-5.2.1

mkdir work

cd work

../configure --prefix=/usr/local --target=sh-elf

make

make install

```

#### 3.5. FPGA development tool

To implement your design to FPGA, you need FPGA development tool. The FPGA vendors release excellent free development tool which has editor, logic synthesizer, static timing analyzer, placer & router and configuration binary generator. In Aquarius project, I have been using Xilinx free ISE Webpack 5.x. Download it from following URL site and install it on your Windows environment. It has a nice Verilog syntax editor, so I have mainly used the editor in "Project Navigator" of ISE during Aquarius development.

http://www.xilinx.com/xlnx/xil prodcat landingpage.jsp?title=ISE+WebPack

#### 3.6. FPGA Board

To verify the logic design, implementing it to FPGA device is very good method. The FPGA plays a role as a hardware logic emulator, so the verification speed is much faster than vector logic simulation. And the CPU in FPGA can execute very large and long program quickly, so the verification quality will be improved.

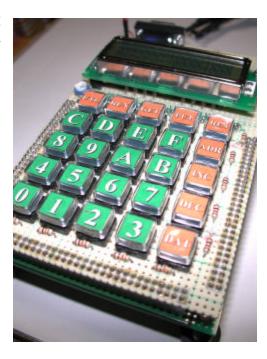

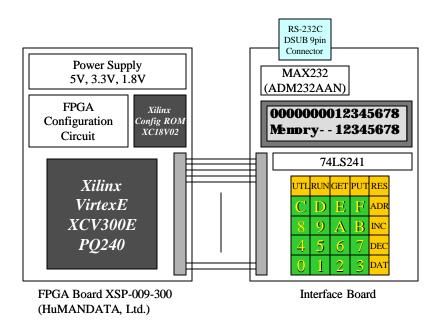

I bought a board which has Xilinx VirtexE-300 (XCV300E). In my case, the board vendor name is HuMANDATA Ltd, and the product name is XSP-009-300. The site is <a href="http://www.hdl.co.jp/">http://www.hdl.co.jp/</a> which unfortunately has only Japanese description. But this company opens their technical documents regarding the products on their site, freely.

I think you can find another good FPGA boards from many vendors around you. Or if you can get FPGA device, making a board by "DIY" is a good choice.

I added some external circuit such as LCD display, Hex Key board and I/F to RS232C to above board to make the verification be smooth. The detail circuit is described later.

# 4. Deliverables

This chapter shows the all deliverables of Aquarius project.

#### 4.1. Document

Aquarius.pdf : this document (Adobe Acrobat Reader)

Aquarius.doc : this document (Microsoft Word)

#### 4.2. RTL Resources

Verilog –HDL (RTL) of Aquarius CPU and its test bench

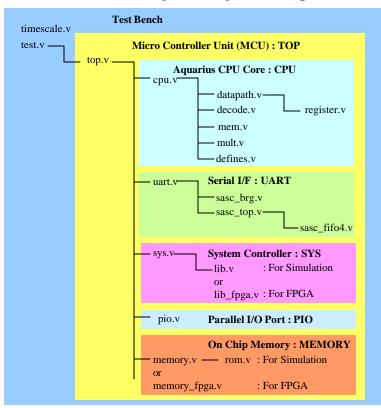

The set of RTL codes of Aquarius includes not only CPU RTL but also Simple MCU RTL that comprises CPU, ROM, RAM, PIO, UART and System Controller. The RTL codes except CPU are used as test bench of CPU. Of course, you can implement all RTL codes into your FPGA, and verify it much more efficiently like as I did. Figure 3.1 shows RTL structure of Aquarius MCU.

#### <u>Test Bench comprises...</u>

```

timescale.v Timescale definition. All files include me.

```

test.v Test Bench

top.v Top layer of MCU

#### MCUcomprises...

top.v Top layer of MCU

pio.v Parallel IN/OUT Interface

memory.v ROM(8KB) and RAM(8KB) for Verilog simulation.

ROM can be initialized from S-format binary code.

rom.v ROM description created by a converter from S-format.

memory\_fpga.v "memory.v" for Xilinx FPGA's configuration (BlockRAM)

All area (16KB) can be initialized by INIT constraints.

uart.v UART (Universal Asynchronous Receiver/Transmitter)

sasc\_brg.v Baud Rate Generator

sasc\_top.v UART Body

sasc\_fifo4.v 4 step FIFO for UART Buffer

```

System Controller that handles interrupts and exceptions

lib.v A clock stop gate (SLEEP instruction) for Verilog sim.

lib_fpga.v "lib.v" for Xilinx FPGA configration

cpu.v Top layer of CPU (Aquarius)

```

# Aquarius CPU comprises...

```

cpu.v Top layer of CPU (Aquarius)

datapath.v Data Path

register.v General Registers R0-R15

decode.v Instruction Decoder

mem.v Memory Access Controller

mult.v Multiplier

defines.v Constant Parameters referred from CPU

```

The UART is based on the "Simple Asynchronous Serial Communication Device created by Rudolf Usselmann" downloaded from <a href="http://www.opencores.org/cores/sasc/">http://www.opencores.org/cores/sasc/</a>.

**Figure 3.1 RTL Structure**

#### 4.3. Verification Resources

I also provide simple but useful resources for logic verification and program development.

#### (1) Assembler Source Programs for Verilog simulation

I provide some example programs for Verilog simulation. You can find them under the directory "sha\_testsource".

#### (2) Converter from S-format object to Verilog ROM description "rom.v"

The assembler can make S-format object. But it should be linked to Aquarius Verilog test bench. I made a simple binary converter from S-format to Verilog ROM description "rom.v". This converter is "genrom.c" which is C source program. Compile it on your Cygwin console. Simply, do this.

```

$ gcc -o genrom.exe genrom.c

```

The usage is very simple. If your S-format binary name is "test.obj", you can convert it to Verilog ROM description by typing as follows.

```

$ ./genrom test.obj

```

This operation creates "rom.v", which is an 8Kbyte ROM.

Note that the "genrom" supports the S-Format which has only S0 (comment), S3 (4byte address) and S7 (end of record).

#### (3) Script to launch Assembler

The script named "asm" launches the GNU assembler, creates object code as an S-format file, and converts the S-Format object to a Verilog ROM description "rom.v". The "asm" is very short script as follows.

#!/bin/bash

sh-elf-as -a \$1 > lis

sh-elf-as -o a.out \$1

sh-elf-objcopy -O srec --srec-forceS3 a.out obj

./genrom obj

The usage is also simple. If you have assemble source program named "test.src", simply

type as follows.

```

$ ./asm test.src

```

This operation creates Verilog ROM description "rom.v" corresponding to "test.src".

#### (4) Script to launch Verilog Simulation

After creating "rom.v", now you can simulate Aquarius. First of all, prepare a text file "test.txt" that lists up all Verilog source files.

The script named "sim" launches the Icarus Verilog Simulator. The "sim" is very short script as follows.

```

#!/bin/bash

iverilog -o test -c test.txt

vvp -v test

```

By the Aquarius test bench "test.v", the simulation results is created as "test\_result.txt" which is a trace list of bus cycle and important register contents.

#### 4.4. FPGA related Resources

To implement Aquarius into Xilinx VirtexE, I have prepared some resources.

#### (1) Converter from S-format object to Xilinx BlockRAM INIT Constraints

In case of FPGA implementation, ROM should be configured by BlockRAM instead of "rom.v", which is described by continuous "case" statements, to reduce the consumption of logic cells. The BlockRAM can be initialized by INIT statement in user constraints file (.ucf). So I made a converter from S-format object to INIT statement.

The converter is "genram.c", which is also a C program, then compile it on your Cygwin console.

```

$ qcc -o genram.exe genram.c

```

The usage is very simple. If your S-format binary name is "test.obj", you can convert it to INIT description by typing as follows.

```

$ ./genram test.obj

```

This operation creates "ram.dat", which is 16Kbyte BlockRAM initialization.

The content of "ram.dat" is as follows.

```

INST "MEMORY_Mram_RAMOHH_inst_ramb_0" INIT_00 = 00000000000000000...;

INST "MEMORY_Mram_RAMOHH_inst_ramb_0" INIT_01 = 0000000000000000...;

INST "MEMORY_Mram_RAMOHH_inst_ramb_0" INIT_02 = 2121212121212121...;

INST "MEMORY_Mram_RAMOHH_inst_ramb_0" INIT_03 = 6765636100D02F2F...;

```

After creating "ram.dat", add this content after the tail of your user constraints file (.ucf), or change all old INST statement. Then, configure your FPGA.

(2) An example of User Constraints File (.ucf)

I provide an example of user constraints file (top.ucf) which corresponds to my FPGA system described later.

#### (3) Some Applications for FPGA System

Following application programs are provided.

Monitor Program shc\_monitor\_release\_v1/

LCD Test shc\_lcdtest/

Interrupt! Clock shc\_clock/

Calculation of Pi shc\_pi/

Details are described later (FPGA Implementation)

# 5. Aquarius CPU Interface Specification: "cpu.v"

# 5.1. Aquarius CPU IN/OUT Signals

The Aquarius CPU ("cpu.v")'s IN/OUT signals are shown in Table5.1. In Aquarius CPU logic circuit, all signals are positive logic level and the changing timing is always at positive edge of CLK.

| Class       | Signal Name                   | Direction | Meaning            | Notes |

|-------------|-------------------------------|-----------|--------------------|-------|

| System      | CLK                           | Input     | System clock       |       |

| Signals     | RST                           | Input     | Power On Reset     |       |

| Wishbone    | CYC_O                         | Output    | Cycle Output       |       |

| Bus         | STB_O                         | Output    | Strobe Output      |       |

| Signals     | ACK_I                         | Input     | Device Acknowledge |       |

|             | ADR_0[31:0]                   | Output    | Address Output     |       |

|             | DAT_I[31:0]                   | Input     | Read Data          |       |

|             | DAT_0[31:0]                   | Output    | Write Data         |       |

|             | WE_O                          | Output    | Write Enable       |       |

|             | SEL_O[3:0]                    | Output    | Byte Lane Select   |       |

|             | TAGO_I (IF_WIDTH)             | Input     | Fetch Width        |       |

| Hardware    | EVENT_REQ_I[2:0]              | Input     | Event Request      |       |

| Event       | <pre>EVENT_INFO_I[11:0]</pre> | Input     | Event Information  |       |

| (interrupt) | EVENT_ACK_O                   | Output    | Event Acknowledge  |       |

| SLEEP       | SLP                           | Output    | Sleep Pulse        |       |

**Table5.1 Aquarius CPU IN/OUT Signals**

### **5.2. System Signals**

#### (1) CLK

The clock input [CLK] coordinates all activities for the internal logic within the WISHBONE interconnect. All output signals are registered at the rising edge of [CLK]. All input signals are stable before the rising edge of [CLK].

#### (2) RST

The reset input [RST] forces the WISHBONE interface to restart. Furthermore, all internal

state machines are forced into an initial state.

When system power-on (cold start), [RST] should be asserted at least for 1 cycle. The Aquarius CPU senses [RST] asynchronously, so any glitch pulse should not be overlaid on [RST] signal. Aquarius Flip Flops are written as follows.

```

always @(posedge CLK or posedge RST)

{

if (RST)

{

}

else

{

}

}

```

If your in-house design rule inhibits asynchronous reset at Flip Flops, you can rewrite RTL codes of Aquarius as follows. Aquarius CPU can operate in synchronous reset manner.

```

always @(posedge CLK)

{

if (RST)

{

}

else

{

}

}

```

# 5.3. "WISHBONE" Compliant Bus Signals

The bus specification of Aquarius CPU is based on WISHBONE classic bus. It follows "Specification for the WISHBONE System-on-Chip (SoC) Interconnection Architecture for Portable IP Cores Revision: B.3, Released: September 7, 2002". The detail specification document is found in the OpenCores site.

#### (1) CYC\_O

The cycle output [CYC\_O], when asserted, indicates that a valid bus cycle is in progress.

The signal is asserted for the duration of all bus cycles. For example, during a Read Modify Write cycle caused by TAS.B (test and set instruction for semaphore protocol), there are two data transfers. The [CYC\_O] signal is asserted during the first data read, and remains its assertion until the last data write. The [CYC\_O] signal is useful for bus arbiter to prevent exchanging the current bus master to another device such as DMA controller during the TAS.B read modify write cycle.

#### (2) STB\_O

The strobe output [STB\_O] indicates a valid data transfer cycle. It is used to qualify various other signals on the interface such as [SEL\_O]. The SLAVE module asserts either the [ACK\_I] signals in response to every assertion of the [STB\_O] signal.

#### (3) ACK\_I

The acknowledge input [ACK\_I], when asserted, indicates the normal termination of a bus cycle. The [ACK\_I] creates CPU internal signal "SLOT" to indicate the edge of pipeline slot.

#### (4) ADR\_O[31:0]

The address output array [ADR\_O] is used to pass a binary address.

#### (5) DAT\_I[31:0]

The data input array [DAT\_I] is used to read binary data from external devices such as ROM, RAM and peripheral modules.

#### (6) DAT\_O[31:0]

The data output array [DAT\_O] is used to write binary data to external devices such as RAM and peripheral modules.

#### (7) WE\_O

The write enable output [WE\_O] indicates whether the current local bus cycle is a READ or WRITE cycle. The signal is negated during READ cycles, and is asserted during WRITE cycles.

#### (8) SEL\_O[3:0]

The select output array [SEL\_O] indicates where valid data is expected on the [DAT\_I] signal array during READ cycles, and where it is placed on the [DAT\_O] signal array during WRITE cycles. The minimum data granularity size is BYTE, so each SEL\_O corresponds to each byte lane. The data alignment position is described in detail later.

#### (9) TAGO\_I (IF\_WIDTH)

All SuperH-2 instruction has 16bit length. The memory such as ROM and RAM connected to Aquarius CPU has 32bit data width. So, when CPU fetches its instruction from 32bit width memory, CPU can get 2 instructions. But if the device data width is 16bit, only one instruction can be sent to CPU at once fetch cycle. Latter case may happen when CPU fetches its instruction from 16bit width external bus, for example.

Therefore, WISHBONE glue logic must inform CPU the instruction fetch space's width.

If the address space is 32bit width, WISHBONE should return IF\_WDTH=1, else should return IF\_WIDTH=0 before ACK\_I signal is asserted.

If CPU fetches instruction from address 0x2, 0x6, 0xa, 0xe, CPU can get only 1 instruction by the fetch cycle. But CPU knows such status, so WISHBONE need not check such case. The WISHBONE glue logic should care only the instruction sending band width that is the data width of accessing address space.

In other words, in case of instruction fetch, IF\_WIDTH has its meaning only when lower 2bit of address is 2b00. The IF\_WIDTH informs CPU how many instructions should be fetched. But if the lower 2bit of address is 2b10, CPU can get only one instruction regardless IF\_WIDTH. In latter case, CPU ignores the IF\_WIDTH.

[CAUTION] Aquarius CPU assumes that the internal bus width is always 32bit. If you connect the internal WISHBONE to 16bit/8bit external bus or peripheral modules, some glue bus control logic should be created to convert internal 32bit data to/from 8bit/6bit data with proper wait timing controls.

#### (10) Data Alignment Position

Aquarius CPU is big-endian. The data width is 32 bit, memory data access granularity is byte, and instruction fetch granularity is 16 bit.

Table 5.2 shows the data alignment position on WISHBONE data bus for each access.

In WISHBONE specification data sheet, 32bit operand size is called as "DWORD", but in

SuperH and Aquarius world, 32bit is called as "Long" or "Long Word".

Note that in case of write operation, the unselected lanes have same write data as valid lane's one. For example, in WORD writing to address 2(2'b10), the valid lane is bit15-0, but bit31-16 of DAT\_O has same data as bit15-0.

| Access Type      |         | Lane     | Lane     | Lane     | Lane    | Notes |

|------------------|---------|----------|----------|----------|---------|-------|

| Size             | Address | [31:24]  | [23:16]  | [15:8]   | [7:0]   |       |

|                  | Lower   | SEL [3]  | SEL[2]   | SEL[1]   | SEL[0]  |       |

|                  | 2bit    |          |          |          |         |       |

| Data Read Long   | 2'b00   | D[31:24] | D[23:16] | D[15:8]  | D[7:0]  |       |

| Data Read Word   | 2'b00   | D[15:8]  | D[7:0]   | ignored  | ignored |       |

|                  | 2'b10   | Ignored  | ignored  | D[15:8]  | D[7:0]  |       |

| Data Read Byte   | 2'b00   | D[7:0]   | ignored  | ignored  | ignored | DAT_I |

|                  | 2'b01   | Ignored  | D[7:0]   | ignored  | ignored |       |

|                  | 2'b10   | Ignored  | ignored  | D[7:0]   | ignored |       |

|                  | 2'b11   | Ignored  | ignored  | ignored  | D[7:0]  |       |

| Data Write Long  | 2'b00   | D[31:24] | D[23:16] | D[15:8]  | D[7:0]  |       |

| Data Write Word  | 2'b00   | D[15:8]  | D[7:0]   | D[15:8]  | D[7:0]  |       |

|                  | 2'b10   | D[15:8]  | D[7:0]   | D[15:8]  | D[7:0]  |       |

| Data Write Byte  | 2'b00   | D[7:0]   | D[7:0]   | D[7:0]   | D[7:0]  | DAT_O |

|                  | 2'b01   | D[7:0]   | D[7:0]   | D[7:0]   | D[7:0]  |       |

|                  | 2'b10   | D[7:0]   | D[7:0]   | D[7:0]   | D[7:0]  |       |

|                  | 2'b11   | D[7:0]   | D[7:0]   | D[7:0]   | D[7:0]  |       |

| Fetch IF_WIDTH=1 | 2'b00   | I0[15:8] | I0[7:0]  | I1[15:8] | I1[7:0] |       |

| Fetch IF_WIDTH=0 | 2'b00   | I[15:8]  | I[7:0]   | ignored  | Ignored | DAT_I |

| Fetch IF_WIDTH=* | 2'b10   | ignored  | ignored  | I[15:8]  | I[7:0]  |       |

: Corresponding SEL\_O[n] is asserted.

**Table5.2 Data Alignment Position**

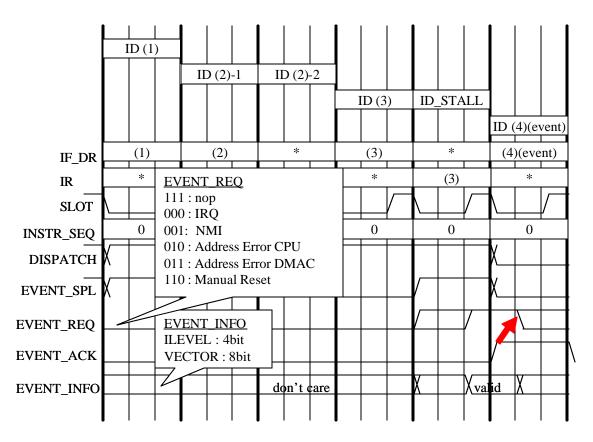

# 5.4. Hardware Event Signals (Interrupt)

CPU should accept some requests from hardware events such as interrupt, address error and manual reset. These requests are informed to CPU by EVENT\_REQ[2:0] associated

with EVENT\_INFO[11:0]. The EVENT\_REQ[2:0] shows the kind of event request. The meanings are shown in Table5.3. In case of IRQ request, EVENT\_INFO[11:0] should also be valid. The upper 4bit of EVENT\_INFO shows the priority level of the requesting IRQ, and the lower 8bit of EVENT\_INFO shows its vector No. The vector address of IRQ equals to EVENT\_INFO[7:0] \* 4. Also see Table5.4.

The EVENT\_REQ and EVENT\_INFO should be asserted and be valid at same timing. CPU samples them at same timing (at the decode stage of pipeline). If the EVENT\_REQ do not show IRQ request, CPU ignores the EVENT\_INFO. After CPU samples the EVENT\_REQ (and EVENT\_INFO), CPU asserts EVENT\_ACK, which shows that the CPU accepts the hardware event request that is valid just at when EVENT\_ACK is being asserted. The EVENT\_REQ should be negated or should be change to next request just after EVENT\_ACK is asserted.

If the event can not be accepted by CPU; that happens in case of lower priority IRQ than I-bit in SR, interrupt request just after the instruction that masks interrupt (for example LDC/LDC.L), or all hardware exception events just after delayed branch instruction; the EVENT\_ACK is not asserted until the request signals can be accepted by CPU. Of course, if the event request is negated before CPU's sampling, the event request can not be accepted by CPU. The hardware event request timing is shown in Figure 5.1 with internal pipeline controls.

| Hardware Event    | EVENT_REQ[2:0] | Notes                     |

|-------------------|----------------|---------------------------|

| NOP               | 3'b111         |                           |

| IRQ               | 3'b000         | Also use EVENT_INFO[11:0] |

| NMI               | 3'b001         |                           |

| CPU Address Error | 3'b010         |                           |

| DMA Address Error | 3'b011         |                           |

| Manual Reset      | 3'b110         |                           |

Table 5.3 Hardware Event Request Signal: EVENT\_REQ[2:0]

| Hardware Event Information | Meaning                                 | Notes |

|----------------------------|-----------------------------------------|-------|

| EVENT_INFO[11:8]           | Priority level of requesting IRQ (4bit) |       |

| EVENT_INFO[7:0]            | Vector No. of requesting IRQ (8bit)     |       |

Table 5.4 Hardware Event Information: EVENT\_INFO[11:0]

The priority among hardware exceptions should be determined by external circuits, which generates EVENT\_REQ and EVENT\_INFO. In SuperH-2 products, the priority order of exceptions is as follows.

1st: Power On Reset (Triggered by RST signal.)

2<sup>nd</sup>: Manual Reset

3rd: CPU/DMA Address Error

4th: NMI

5th: IRQ

The exceptions caused by instruction (Illegal, Slot-Illegal and Trap) have the lowest priority, but the external circuits need not to care, because the decoder unit in CPU detects them.

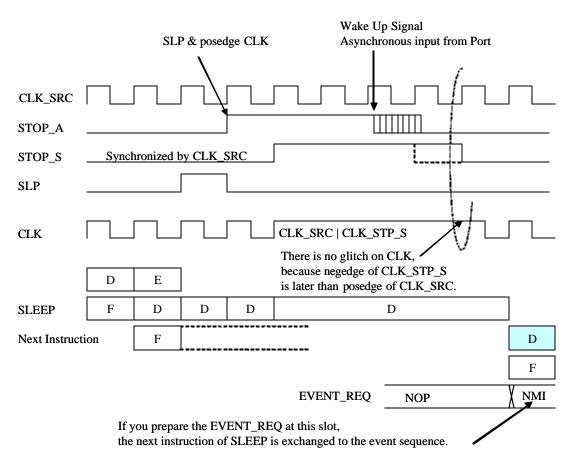

**Figure 5.1 Hardware Event Request and Sampling Timing**

#### **5.5. SLEEP signal for Low Power Mode**

The SLP output is asserted by SLEEP instruction. The chip can stop its clock by SLP signal and can go to low power mode, if you desire.

The SLEEP timing is shown is Figure 5.2. The CLK\_SRC is an original clock generated by, for example, XTAL oscillator. The CLK is made from CLK\_SRC by a gating logic and the CLK stops during SLEEP state. Of course you can stop CLK\_SRC by similar method (But, to wake up CLK\_SRC, you may need some delay timer to wait for the stable XTAL oscillation.) And by some wakeup signal such as NMI, the CLK is waked up. At the wakeup timing, if CPU finds a hardware event request, corresponding exception starts. Or, if there is no hardware event, the program starts from next instruction of SLEEP.

The actual low power mode should be implemented by whole chip designer. The Aquarius test bench includes very simple low power control logic, for your reference.

If not, the next instruction of SLEEP continues its operation, after the CLK wakes up. Even in latter case, if you place the opcode for NMI-emulation as the next instruction, you can get desired exception sequence only by the wake-up operation.

**Figure 5.2 SLEEP and Low Power Timing**

# 6. Simulation Test Bench

This chapter describes the Aquarius test bench structure for the verification by the method of vector logic simulation.

# 6.1. Top Layer: "top.v"

As shown in Figure 3.1, "top.v" is the top layer of Aquarius MCU. It combines among CPU, UART, System Controller, Parallel Port, and on chip memories.

In this chapter, "memory.v" and "lib.v" are assumed to be used, instead of "memory\_fpga.v" and "lib\_fpga.v".

The system address map is shown in Table 6.1. The "memory.v" has 8KB ROM ("rom.v") and 8KB RAM. All CPU instruction should be verified in various memory access cycle and instruction fetch size. So, the memory access cycle and instruction fetch width are determined by its address; i.e. WISHBONE ACK and  $TAGO_I(IF_WIDTH)$  are generated in "top.v".

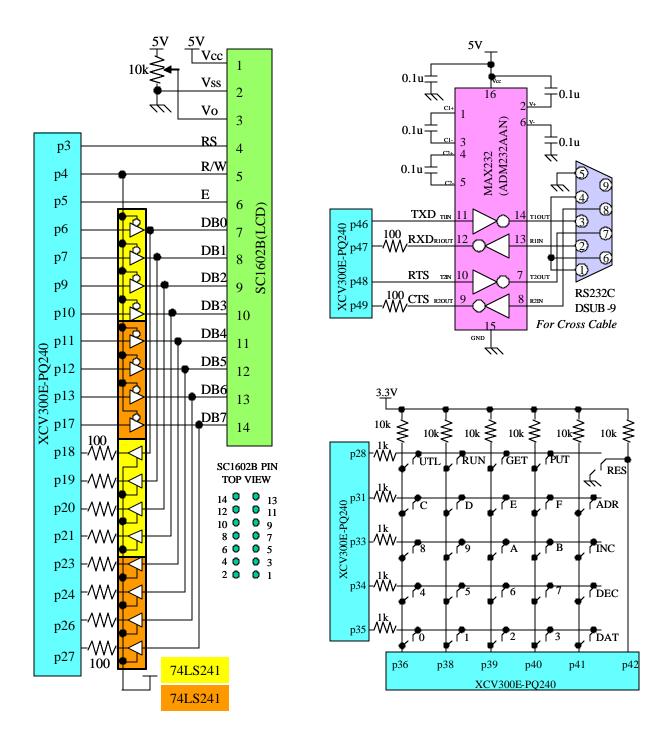

The peripheral devices such as PIO, UART and SYS are located in 0xABCDxxxx area. The top layer's IN/OUT signals are shown in Table6.2. These signals correspond with author's FPGA configuration. There are several LCD and KEY control signals from PIO module, and UART signals. See later chapter for detail FPGA board circuit.

#### 6.2. Simulation Test Bench: "test.v"

The "test.v" is a test bench for Verilog simulation. It creates clock and some input signals (stimuli). Also it generate trace list file as a simulation result named "test\_result.txt". For your own simulation, please modify "test.v". When you simulate instructions of CPU by Verilog logic simulator, you need not care the operations of LCD, KEY and UART interfaces. You should care only bus transaction, register contents and signal levels and timings, etc. in case that your viewpoint of simulation is in Aquarius CPU operation.

#### 6.3. Parallel I/O Port (PIO): "pio.v"

Parallel I/O Port (PIO) "pio.v" IN/OUT signals are shown in Table6.3. PIO has 2 32bit registers to control Port Pins. Parallel I/O Port (PIO) Registers are shown in Figure6.1. There are 4 byte-size registers for PORT Output and 4 byte-size registers for PORT Input.

Both registers for PORT Input and PORT Output have same address. If you read each register, you can access PORT Input, and if you write to each register, you can access PORT Output.

Each register is located in side-by-side address, so they can be accessed by byte, word or long operand size. PORT Output registers are reset to 0x00 when power on reset.

| Address               | Device                                         | Size   | Access       | IF Width | Notes       |

|-----------------------|------------------------------------------------|--------|--------------|----------|-------------|

| 0x00000000-0x00001FFF | ROM                                            | 8KB    | 1cyc         | 32bit    | A           |

| 0x00002000-0x00003FFF | RAM                                            | 8KB    | 1cyc         | 32bit    | В           |

| 0x00004000-0x0000FFFF | Shadow of                                      | f 0x00 | 000000-0x000 | 03FFF    |             |

| 0x00010000-0x00011FFF | ROM                                            | 8KB    | 4cyc         | 32bit    | Shadow of A |

| 0x00012000-0x00013FFF | RAM                                            | 8KB    | 4cyc         | 32bit    | Shadow of B |

| 0x00014000-0x0001FFFF | Shadow of                                      | f 0x00 | 010000-0x000 | 13FFF    |             |

| 0x00020000-0x00021FFF | ROM                                            | 8KB    | 1cyc         | 16bit    | Shadow of A |

| 0x00022000-0x00023FFF | RAM                                            | 8KB    | 1cyc         | 16bit    | Shadow of B |

| 0x00024000-0x0002FFFF | Shadow of                                      | f 0x00 | 020000-0x000 | 23FFF    |             |

| 0x00030000-0x00031FFF | ROM                                            | 8KB    | 4cyc         | 16bit    | Shadow of A |

| 0x00032000-0x00033FFF | RAM                                            | 8KB    | 4cyc         | 16bit    | Shadow of B |

| 0x00034000-0x0003FFFF | Shadow of                                      | f 0x00 | 030000-0x000 | 33FFF    |             |

| 0x00040000-0xABCCFFFF | Shadow of 0x0000000-0x0003FFFF                 |        |              |          |             |

| 0xABCD0000-0xABCD00FF | PIO                                            | 256B   | 4cyc         | 32bit    |             |

| 0xABCD0100-0xABCD01FF | UART                                           | 256B   | 4cyc         | 32bit    |             |

| 0xABCD0200-0xABCD02FF | SYS                                            | 256B   | 4cyc         | 32bit    |             |

| 0xABCD0300-0xFFFFFFFF | 0300-0xFFFFFFFF Shadow of 0x0000000-0x0003FFFF |        |              |          |             |

**Table6.1 Address Map of the Test Bench**

| Class    | Signal Name | Direction | Meaning              | Notes     |

|----------|-------------|-----------|----------------------|-----------|

| System   | CLK_SRC     | Input     | System clock         |           |

| Signals  | RST_n       | Input     | Power On Reset       | Negated   |

| Parallel | LCDRS       | Output    | LCD Register Select  | PO[8]     |

| I/O Port | LCDRW       | Output    | LCD Read/Write       | PO[9]     |

|          | LCDE        | Output    | LCD Enable Signal    | PO[10]    |

|          | LCDDB0[7:0] | Output    | LCD Data Bus Output  | PO[7:0]   |

|          | LCDDBI[7:0] | Input     | LCD Data Bus Input   | PI[7:0]   |

|          | KEYYO[4:0]  | Output    | KEY Matrix Y Output  | PO[20:16] |

|          | KEYXI[4:0]  | Input     | KEY Matrix X Input   | PI[20:16] |

| UART     | RXD         | Input     | Receive Serial Data  |           |

|          | TXD         | Output    | Transmit Serial Data |           |

|          | CTS         | Input     | Clear To Send        |           |

|          | RTS         | Output    | Request To Send      |           |

**Table6.2 Top Layer IN/OUT Signals**

| Class    | Signal Name | Direction | Meaning                     | Notes |

|----------|-------------|-----------|-----------------------------|-------|

| System   | CLK         | Input     | System clock                |       |

| Signals  | RST         | Input     | Power On Reset              |       |

| Wishbone | CE          | Input     | Chip Select (Module Select) | STB   |

| Bus      | WE          | Input     | Write Enable                |       |

| Signals  | SEL[3:0]    | Input     | Byte Lane Select            |       |

|          | DATI[31:0]  | Input     | Data Input (Write Data)     |       |

|          | DATO[31:0]  | Output    | Data Output (Read Data)     |       |

| PORT     | PI[31:0]    | Input     | Port Input                  |       |

|          | PO[31:0]    | Output    | Port Output                 |       |

**Table6.3 Parallel I/O Port (PIO) Module IN/OUT Signals**

| [PORT Ou                                                   | tput] Addre                                                 | ss=0xABCD                                                       | 0000 W                                                | only reser                                                  | ved                                             |                                    |                                   |

|------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------|------------------------------------|-----------------------------------|

| 31(7)                                                      | 30(6)                                                       | 29(5)                                                           | 28(4)                                                 | 27(3)                                                       | 26(2)                                           | 25(1)                              | 24(0)                             |

| reserved                                                   | reserved                                                    | reserved                                                        | reserved                                              | reserved                                                    | reserved                                        | reserved                           | reserved                          |

| [PORT Ou                                                   | tput] Addre                                                 | ss=0xABCD                                                       | 0001 W                                                | only KEY                                                    | YO (KEY M                                       | atrix Y-axis                       | Output)                           |

| 23(7)                                                      | 22(6)                                                       | 21(5)                                                           | 20(4)                                                 | 19(3)                                                       | 18(2)                                           | 17(1)                              | 16(0)                             |

| reserved                                                   | reserved                                                    | reserved                                                        | KY4                                                   | KY3                                                         | KY2                                             | KY1                                | KY0                               |

| [PORT Ou                                                   | tput] Addre                                                 | ss=0xABCD                                                       | 00002 W                                               | only LCD                                                    | CON (LCD                                        | Control Out                        | put)                              |

| 15(7)                                                      | 14(6)                                                       | 13(5)                                                           | 12(4)                                                 | 11(3)                                                       | 10(2)                                           | 9(1)                               | 8(0)                              |

| reserved                                                   | reserved                                                    | reserved                                                        | reserved                                              | reserved                                                    | E                                               | R/W                                | RS                                |

| [PORT Ou                                                   | tput] Addre                                                 | ss=0xABCD                                                       | 00003 W                                               | only LCD                                                    | OUT (LCD V                                      | Write Data                         | Output)                           |

| 7(7)                                                       | 6(6)                                                        | 5(5)                                                            | 4(4)                                                  | 3(3)                                                        | 2(2)                                            | 1(1)                               | 0(0)                              |

| DW7                                                        | DW6                                                         | DW5                                                             | DW4                                                   | DW3                                                         | DW2                                             | DW1                                | DW0                               |

| [PORT Inp                                                  | [PORT Input] Address=0xABCD0000 R only reserved             |                                                                 |                                                       |                                                             |                                                 |                                    |                                   |

|                                                            |                                                             | -UXADCDU                                                        | ooo k                                                 | omy reser                                                   | veu                                             |                                    |                                   |

| 31(7)                                                      | 30(6)                                                       | 29(5)                                                           | 28(4)                                                 | 27(3)                                                       | 26(2)                                           | 25(1)                              | 24(0)                             |

| 31(7)                                                      | _                                                           |                                                                 |                                                       | J                                                           |                                                 | 25(1)                              | 24(0)                             |

| reserved                                                   | 30(6)                                                       | 29(5)                                                           | 28(4)                                                 | 27(3)                                                       | 26(2)                                           | reserved                           | reserved                          |

| reserved                                                   | 30(6)                                                       | 29(5)                                                           | 28(4)                                                 | 27(3)                                                       | 26(2)                                           | reserved                           | reserved                          |

| reserved [PORT In]                                         | 30(6) reserved out] Address                                 | 29(5) reserved s=0xABCD0                                        | 28(4) reserved 001 R                                  | 27(3) reserved only KEY                                     | 26(2)<br>reserved<br>XI (KEY Ma                 | reserved                           | reserved Input)                   |

| reserved [PORT Inp 23(7) reserved                          | 30(6) reserved out] Address 22(6) reserved                  | 29(5) reserved s=0xABCD0 21(5)                                  | 28(4) reserved  001 R 20(4) KX4                       | 27(3) reserved only KEY 19(3)                               | 26(2)<br>reserved<br>XI (KEY Ma<br>18(2)<br>KX2 | reserved  Atrix X-axis  17(1)      | reserved Input) 16(0)             |

| reserved [PORT Inp 23(7) reserved                          | 30(6) reserved out] Address 22(6) reserved                  | 29(5) reserved s=0xABCD0 21(5) reserved                         | 28(4) reserved  001 R 20(4) KX4                       | 27(3) reserved only KEY 19(3) KX3                           | 26(2)<br>reserved<br>XI (KEY Ma<br>18(2)<br>KX2 | reserved  Atrix X-axis  17(1)      | reserved Input) 16(0)             |

| reserved [PORT Inp 23(7) reserved [PORT Inp                | 30(6) reserved out] Address 22(6) reserved out] Address     | 29(5) reserved s=0xABCD0 21(5) reserved s=0xABCD0               | 28(4) reserved 001 R 20(4) KX4 002 R                  | 27(3) reserved only KEY 19(3) KX3 only reser                | 26(2) reserved XI (KEY Ma 18(2) KX2             | reserved  atrix X-axis  17(1)  KX1 | reserved Input) 16(0) KX0         |

| reserved [PORT In] 23(7) reserved [PORT In] 15(7) reserved | 30(6) reserved  22(6) reserved  out] Address 14(6) reserved | 29(5) reserved s=0xABCD0 21(5) reserved s=0xABCD0 13(5)         | 28(4) reserved  001 R 20(4) KX4  002 R 12(4) reserved | 27(3) reserved only KEY 19(3) KX3 only reser 11(3) reserved | 26(2) reserved XI (KEY Ma 18(2) KX2 ved 10(2)   | reserved 17(1) KX1 9(1) R/W        | reserved Input) 16(0) KX0 8(0) RS |

| reserved [PORT In] 23(7) reserved [PORT In] 15(7) reserved | 30(6) reserved  22(6) reserved  out] Address 14(6) reserved | reserved 29(5) reserved 21(5) reserved 5=0xABCD0 13(5) reserved | 28(4) reserved  001 R 20(4) KX4  002 R 12(4) reserved | 27(3) reserved only KEY 19(3) KX3 only reser 11(3) reserved | 26(2) reserved XI (KEY Ma 18(2) KX2 ved 10(2) E | reserved 17(1) KX1 9(1) R/W        | reserved Input) 16(0) KX0 8(0) RS |

Figure 6.1 Parallel I/O Port (PIO) Registers

# 6.4. Serial I/O (UART): "uart.v"

The top layer has Serial I/O device (UART) "uart.v", which is SASC (Simple Asynchronous Serial Communication Device) from the opencores.org IP. The SASC is not WISHBONE compliant IP, so some registers are added to connect SASC to WISHBONE bus. UART IN/OUT signals are shown in Table 6.4, and its registers are shown in Figure 6.2.

Each register is located in side-by-side address, so they can be accessed by byte, word or long operand size, but the UARTCON and UARTRXD/TXD should be accessed only by byte operand size.

| Class    | Signal Name | Direction | Meaning                     | Notes |

|----------|-------------|-----------|-----------------------------|-------|

| System   | CLK         | Input     | System clock                |       |

| Signals  | RST         | Input     | Power On Reset              |       |

| Wishbone | CE          | Input     | Chip Select (Module Select) | STB   |

| Bus      | WE          | Input     | Write Enable                |       |

| Signals  | SEL[3:0]    | Input     | Byte Lane Select            |       |

|          | DATI[31:0]  | Input     | Data Input (Write Data)     |       |

|          | DATO[31:0]  | Output    | Data Output (Read Data)     |       |

| UART     | RXD         | Input     | Receive Serial Data         |       |

|          | TXD         | Output    | Transmit Serial Data        |       |

|          | CTS         | Input     | Clear To Send               |       |

|          | RTS         | Output    | Request To Send             |       |

Table 6.4 Serial I/O (UART) IN/OUT Signals

| [UART] Ad | ddress=0xA | BCD0100  | R/W U      | <b>UARTBG0 (Baud rate Generator Div0)</b> |             |             | 7 <b>0</b> )  |

|-----------|------------|----------|------------|-------------------------------------------|-------------|-------------|---------------|

| 31(7)     | 30(6)      | 29(5)    | 28(4)      | 27(3)                                     | 26(2)       | 25(1)       | 24(0)         |

| B07       | B06        | B05      | B04        | B03                                       | B02         | B01         | B00           |

| [UART] Ad | ddress=0xA | BCD0101  | R/W U      | JARTBG1 (B                                | aud rate Ge | nerator Div | <b>/1)</b>    |

| 23(7)     | 22(6)      | 21(5)    | 20(4)      | 19(3)                                     | 18(2)       | 17(1)       | 16(0)         |

| B17       | B16        | B15      | B14        | B13                                       | B12         | B11         | B10           |

| [UART] Ad | ddress=0xA | BCD0102  | R only U   | JARTCON (1                                | TXF=full_o, | RXE=empty   | y_ <b>o</b> ) |

| 15(7)     | 14(6)      | 13(5)    | 12(4)      | 11(3)                                     | 10(2)       | 9(1)        | 8(0)          |

| reserved  | reserved   | Reserved | reserved   | reserved                                  | reserved    | TXF         | RXF           |

| [UART] A  | ddress=0xA | BCD0103  | R only / U | ARTRXD, W                                 | only / UAR  | TTXD        |               |

| 7(7)      | 6(6)       | 5(5)     | 4(4)       | 3(3)                                      | 2(2)        | 1(1)        | 0(0)          |

| TR7       | TR6        | TR5      | TR4        | TR3                                       | TR2         | TR1         | TR0           |

Figure 6.2 Serial I/O (UART) Registers

The UARTBG0 and UARTBG1 are the registers to determine the serial baud rate. The

UARTBG0 and UARTBG1 are reset to 0x00 when power on reset. The expression to calculate the baud rate is shown below.

$$BaudRate = \frac{f(CLK)}{4} \times \frac{1}{(BG0+2)\times(BG1+1)} [bps]$$

Table 6.5 shows some examples of baud rate setting.

| Baud Rate | f (CLK) | UARTBG0   | UARTBG1    | Notes |

|-----------|---------|-----------|------------|-------|

| [bps]     | [MHz]   |           |            |       |

| 1200      | 20      | 0x12 (18) | 0xCF (207) |       |

| 2400      | 20      | 0x12 (18) | 0x67 (103) |       |

| 4800      | 20      | 0x12 (18) | 0x33 (51)  |       |

| 9600      | 20      | 0x12 (18) | 0x19 (25)  |       |

**Table6.5 Examples of Baud Rate Settings**

The UARTCON has 2 flags; TXF and RXE. The TXF is 1 when transmit buffer is full. If TXF=0, you can write next transmit data. The RXE is 1 when receive buffer is empty. If TXE=0, you can read receive data. The TXF and RXE correspond to full\_o and empty\_o of SASC, respectively. Note that SASC has 4 byte depth FIFOs for both transmit buffer and receive buffer. In case of this top layer, TXF and RXE are not connected as interrupt signals, so you should poll these flags in your program. Generally, such flags should be treated as interrupt requests. You can easily modify the Aquarius RTL codes like this.

The UARTRXD and UARTTXD are the receive buffer and transmit buffer registers, which have same address. Read operation accesses to UARTRXD, and Write operation accesses to UARTTXD.

# 6.5. System Controller (SYS): "sys.v"

The System Controller (SYS) "sys.v" has following functions.

- (1) Generate Exception of Hardware Event.

- NMI (by Address Break)

- IRQ (by Interval Timer)

- CPU Address Error (by watching WISHBONE bus transaction)

- (2) Emulate Exception of Hardware Event.

- NMI

- IRQ

- CPU Address Error

- DMA Address Error

- Manual Reset

- (3) Control priority level among the requests of hardware exception.

- (4) Set IRQ priority level and vector number.

- (5) 12it Interval Timer to generate IRQ.

- (6) Bus Address Break Function for debugging capability (NMI).

- (7) Detect CPU Address Error by watching WISHBONE bus signals.

- (8) SLEEP and Low Power Control, according to Figure 5.2 manner.

The IN/OUT Signals of SYS are shown in Table 6.6.

The SYS has 2 32bit length registers; INTCTL and BRKADR. These are shown in Figure 6.3. Both registers should be accessed only by long word operand size. The INTCTL is reset to 0x000000FFF, and the BRKADR is reset to 0x00000000 when power on reset.

| Class    | Signal Name                 | Direction | Meaning                      | Notes |

|----------|-----------------------------|-----------|------------------------------|-------|

| System   | CLK_SRC                     | Input     | System clock Source          |       |

| Signals  | CLK                         | Output    | CLK , which stops at SLEEP   |       |

|          | SLP                         | Input     | SLEEP request from CPU       |       |

|          | WAKEUP                      | Input     | Wakeup Request               |       |

|          | RST                         | Input     | Power On Reset               |       |

| Wishbone | CE                          | Input     | Chip Select (Module Select)  | STB   |

| Bus      | WE                          | Input     | Write Enable                 |       |

| Signals  | SEL[3:0]                    | Input     | Byte Lane Select             |       |

|          | ACK                         | Input     | Bus Acknowledge              |       |

|          | DATI[31:0]                  | Input     | Data Input (Write Data)      |       |

|          | DATO[31:0]                  | Output    | Data Output (Read Data)      |       |

|          | STB                         | Input     | Strobe (Bus monitor to BRK)  |       |

|          | ADR[31:0]                   | Input     | Address (Bus monitor to BRK) |       |

| Hardware | EVENT_REQ[2:0]              | Output    | Event Request                |       |

| Events   | <pre>EVENT_INFO[11:0]</pre> | Output    | Event Information (IRQ)      |       |

|          | EVENT_ACK                   | Input     | Event Acknowledge from CPU   |       |

Table 6.6 System Controller (SYS) IN/OUT Signals

| [SYS] Add                  | ress=0xAB(                       | CD0200                           | R/W I                            | NTCON (Int        | errupt Cont                | rol)                       |                           |

|----------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------|----------------------------|----------------------------|---------------------------|

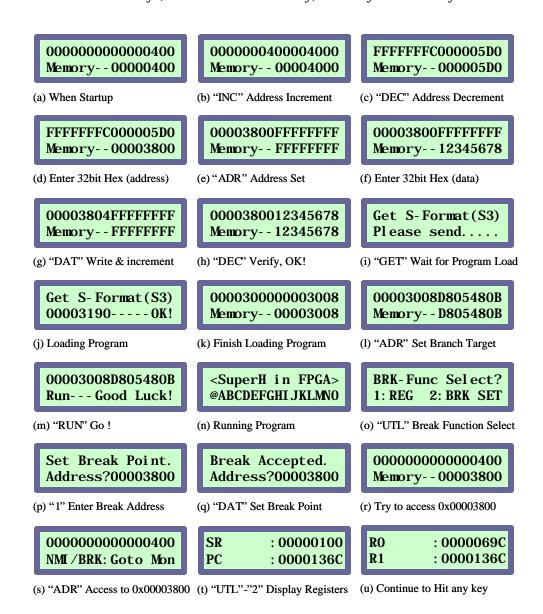

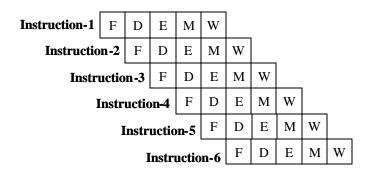

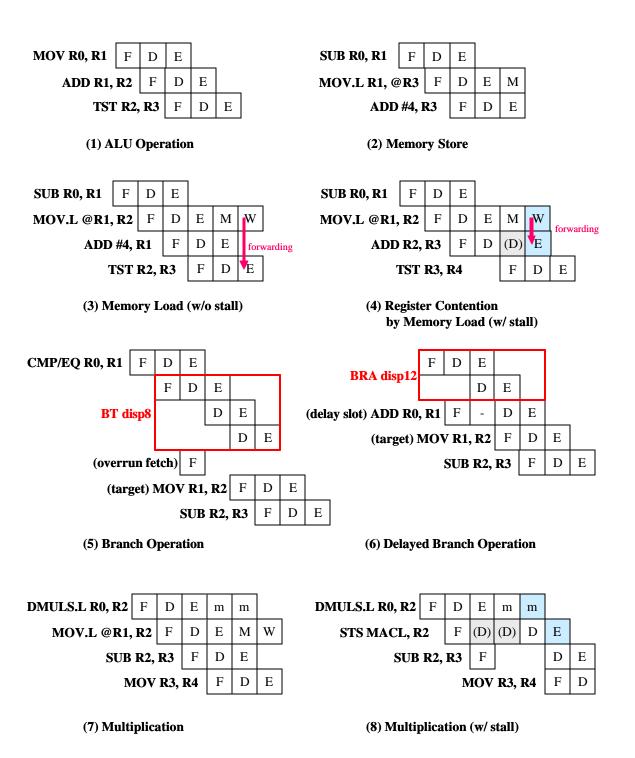

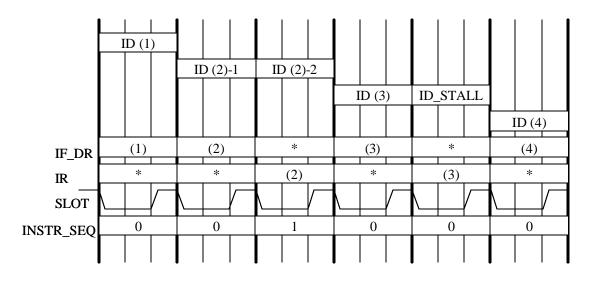

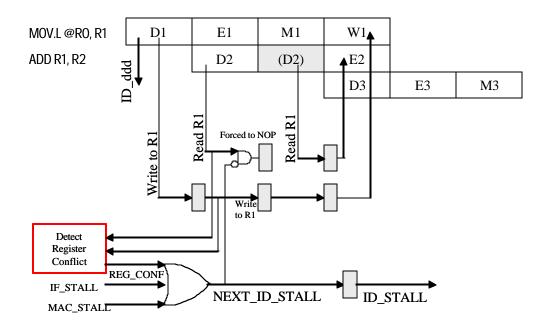

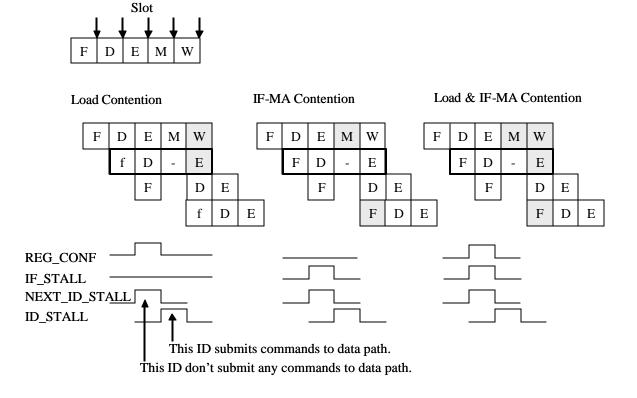

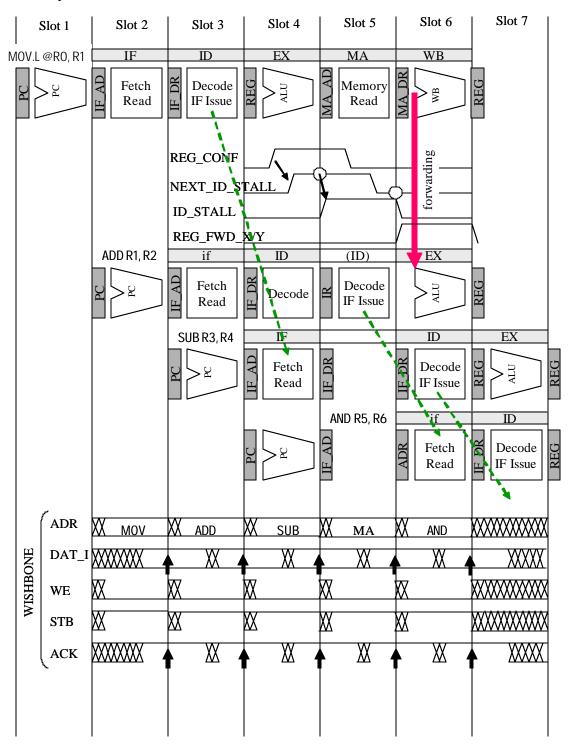

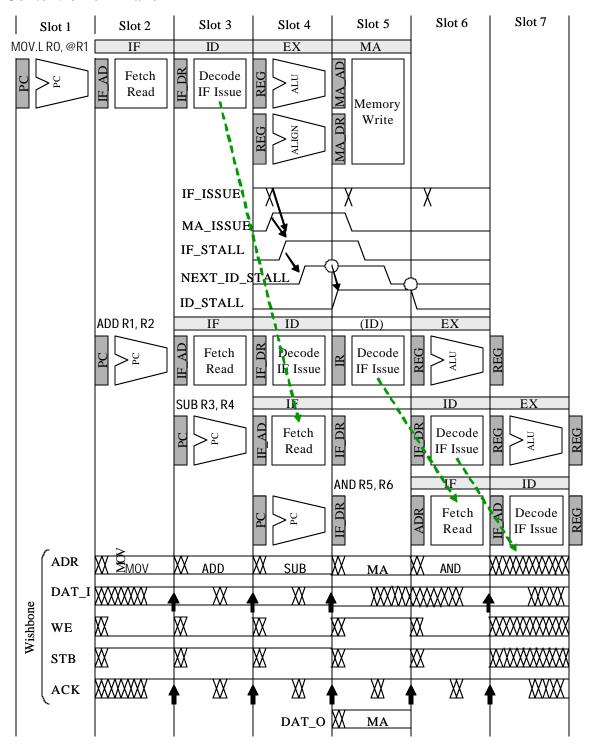

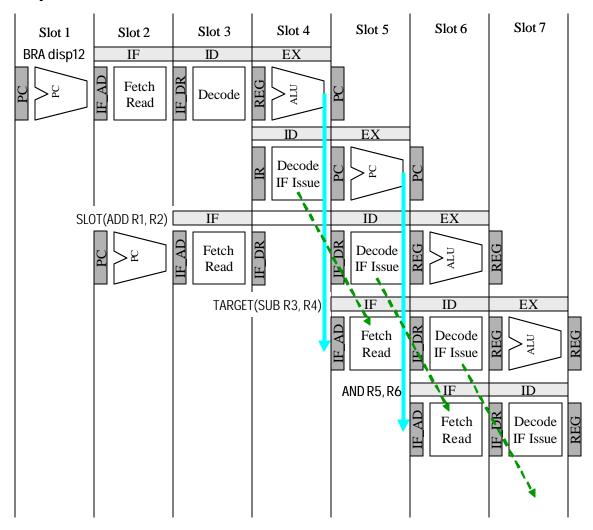

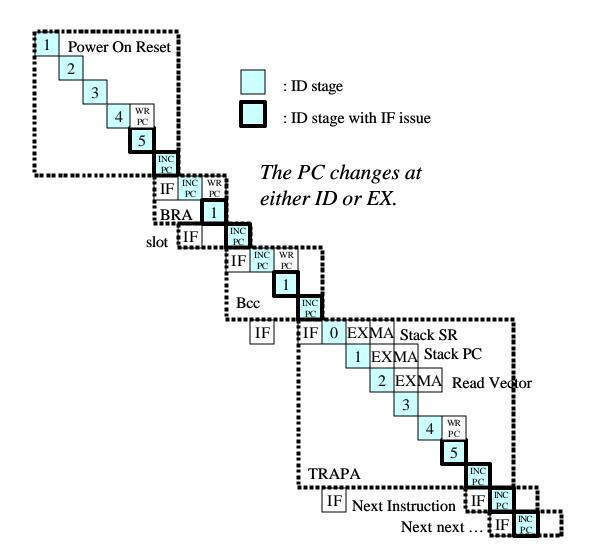

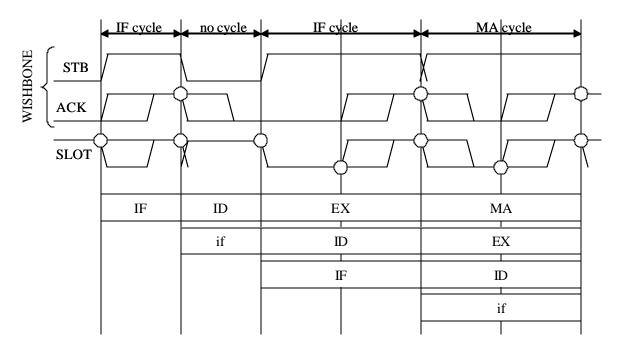

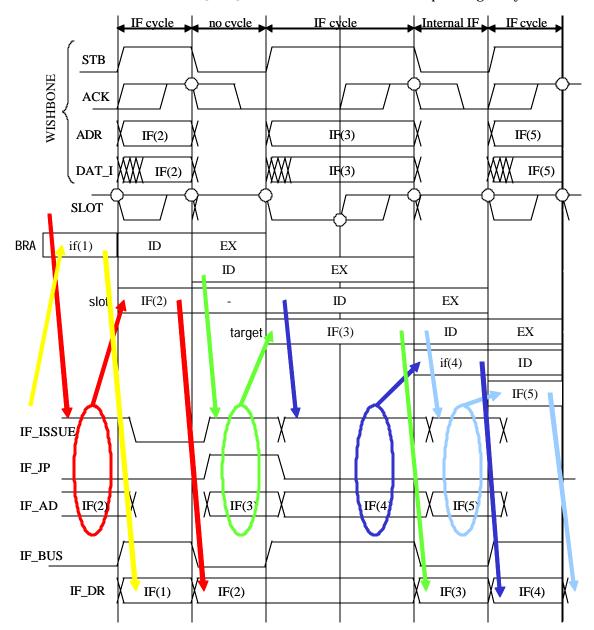

| 31                         | 30                               | 29                               | 28                               | 27                | 26                         | 25                         | 24                        |