# Xilinx Internal JTAG

### (Test Access Port)

Author: Nathan Yawn nathan.yawn@opencores.org

Rev. 1.0

May 16, 2009

Copyright (C) 2008-2009 Nathan Yawn

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license should be included with this document. If not, the license may be obtained from www.gnu.org, or by writing to the Free Software Foundation.

This document is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE.

### History

| Rev. | Date       | Author      | Description              |

|------|------------|-------------|--------------------------|

| 1.0  | 18/07/2008 | Nathan Yawn | First Draft              |

| 1.1  | 16/05/2009 | NY          | Edit for initial release |

### Contents

| 1 INTRODUCTION                  | 5 |

|---------------------------------|---|

| 2 OPERATION                     | 6 |

| 2.1 XILINX BSCAN_* MACRO BLOCKS |   |

| 2.3 Non-standard Behavior       |   |

| 3 IO PORTS                      | 8 |

| 3.1 Debug Ports                 |   |

| 4 REGISTERS                     | 9 |

| 5 INTEGRATED SYSTEM             |   |

### 1 Introduction

The Xilinx Internal JTAG core is used for development purposes (hardware and software debugging). It uses a Xilinx BSCAN\_SPARTAN or BSCAN\_VIRTEX IP library function macro to allow debugging of an OpenRisc-based System-on-Chip (SoC) using the same JTAG interface IO pins used to upload the bitstream to the FPGA. This core can only be used in Xilinx FPGAs which support a BSCAN\_\* macro. Before continuing with this document, it is recommended that you familiarize yourself with the IEEE 1149.1 specification (JTAG and Boundary Scan), and also that you read the section of the Xilinx Unified Libraries manual which deals with the BSCAN\_\* macros.

The xilinx\_internal\_jtag core is designed to replace the "jtag" TAP core in a Xilinx-based system. It is designed to provide an interface between the FPGA's JTAG pins and the SoC debug core. In particular, the xilinx\_internal\_jtag core is designed to interface with the Advanced Debug Interface (adv\_dbg\_if core). Other debug cores may require modification in order to work with this one. Note that this core provides only a single device enable output (for the debug core); adding other JTAG scan chains may be done by hand, if multiple USER instructions are supported by the BSCAN\_\* block in your particular FPGA.

## 2 Operation

This section describes the operation of the xilinx\_internal\_jtag core. The core relies heavily on the BSCAN\_\* macro blocks for its operation. In fact, the core is primarily a wrapper for the BSCAN macro, with some additional logic to make the signals more compatible with standard JTAG signaling.

#### 2.1 Xilinx BSCAN\_\* Macro Blocks

These macro blocks are designed to allow a user-defined JTAG scan chain to be accessed through the same pins used to upload a configuration bitstream to the FPGA. In particular, the BSCAN macro allows a user to attach programmable FPGA logic to the hard-wired JTAG TAP. The FPGA logic is connected to the TAP as a Data Register (DR), which is selected when one of the USERn instructions is active in the TAP IR.

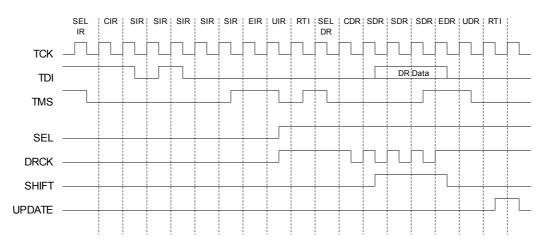

The BSCAN\_\* blocks provide different signals, depending on what type of Xilinx device is used. All provide SHIFT\_DR and UPDATE\_DR outputs, as well as a SELECT output. Many provide a CAPTURE\_DR output, and this signal can be implied from other signals in devices that do not provide the signal. Clocking is of particular interest; with the exception of one device (BSCAN\_SPARTAN3), the BSCAN\_\* macros do not provide a regular TCK JTAG clock. Instead, they provide a clock named DRCK. The DRCK clock first goes high when USERn is made active in the TAP's IR. The clock does not change state until the TAP reaches the CAPTURE\_DR state. While the TAP is in the CAPTURE\_DR or SHIFT\_DR states, DRCK follows the TCK input clock. Once the TAP leaves the SHIFT\_DR state, DRCK returns to a constant high level. This means that no transitions on the DRCK line occur while the UPDATE\_DR output signal is active, which is incompatible with many JTAG devices. See Figure 1 for an example of the output waveform of a BSCAN\_\* device. (Where possible, the xilinx\_internal\_jtag core compensates for this, see section 2.3.)

Figure 1: JTAG signals and their corresponding BSCAN \* outputs

#### **2.2 Instructions**

The xilinx\_internal\_jtag core instantiates a BSCAN\_\* macro associated with the USER1 instruction. To make the debug core active, the USER1 instruction must be shifted into the FPGA's IR. The value (and IR length) may change depending on which FPGA is used, check the chip's documentation or JTAG BSDL file for details.

The debug interface core is connected as the Data Register (DR) of the JTAG TAP when the USER1 instruction is active in the IR. Data from the xilinx\_internal\_jtag core to the debug core is assumed to be latched on the rising edge of the TCK ouput clock. Data from the debug core to the internal jtag core is latched on the falling edge of TCK.

#### 2.3 Non-standard Behavior

Because of the behavior of the DRCK line, logic has been added to the xilinx\_internal\_jtag core in order to make it more compatible with standard behavior. The tck\_o clock output from the xilinx\_internal\_jtag core is AND'ed with the inverse of the UPDATE\_DR output line of the BSCAN\_\* macro. This forces the clock low during the UPDATE\_DR TAP state. By latching the UPDATE\_DR line from the BSCAN\_\* macro, the update\_dr\_o output is held high when the UPDATE\_DR line is de-asserted, causing a low-to-high transition on the tck\_o output clock, which should allow connected devices to register the UPDATE\_DR state.

The update\_dr\_o output remains high until the TAP's CAPTURE\_DR state is entered, or the SELECT output of the BSCAN\_\* macro is de-asserted (there are no DRCK events during this period). This means that zero clock events will occur on tck\_o between the UPDATE\_DR and CAPTURE\_DR states. Some devices, such as the adv\_dbg\_if core, require at least one clock during this period in order to maintain their internal state machine. In this case, a tck\_o event must be generated by shifting a different instruction into the TAP IR (BYPASS is recommended), then re-activating USER1. The tck\_o line will be forced low while USER1 is not selected. Driver software on the PC must be modified to perform this operation if necessary.

None of the BSCAN\_\* macros provide PAUSE\_DR or RUN\_TEST\_IDLE outputs. While these ports are present in the xilinx\_intenal\_jtag interface (as pause\_dr\_o and run\_test\_idle\_o, respectively), they are only for port compatibility with other JTAG TAP cores. The value of these signals is a constant '0'.

## 3 IO Ports

This section describes the top-level ports of the xilinx\_internal\_jtag core. Because all of the JTAG signals come through the BSCAN\_\* macro, the only ports from the core are used to interface to the debug interface.

#### 3.1 Debug Ports

| Port               | Width | Direction | Description                                                                                    |

|--------------------|-------|-----------|------------------------------------------------------------------------------------------------|

| tck_o              | 1     | output    | JTAG clock signal                                                                              |

| test_logic_reset_o | 1     | output    | TAP controller state "Test Logic Reset", acts as reset signal to sub-modules (debug unit etc.) |

| rup tost idlo o    | 1     | output    | TAP controller state "Run Test / Idle"                                                         |

| run_test_idle_o    | I     |           | Constant '0' value.                                                                            |

| shift_dr_o         | 1     | output    | TAP controller state "Shift DR"                                                                |

| nauso dr. o        | 1     | output    | TAP controller state "Pause DR"                                                                |

| pause_dr_o         |       |           | Constant '0' value.                                                                            |

| capture_dr_o       | 1     | output    | TAP controller state "Capture DR"                                                              |

| update_dr_o        | 1     | output    | TAP controller state "Update DR"                                                               |

| debug_select_o     | 1     | output    | Debug select, true when DEBUG instruction active in the virtual IR                             |

| tdo_o              | 1     | output    | TDO signal, connects to all TDI signals of sub-<br>modules (i.e. debug module)                 |

| debug_tdi_i        | 1     | input     | TDI signal from debug module                                                                   |

Table 1: Debug Ports

## 4 Registers

There are no registers in the Xilinx Internal JTAG core. While the instantiated BSCAN\_\* macro does include a JTAG Instruction Register, which must be loaded with the USER1 instruction to enable this core, the length of the register and the value of the USER1 instruction vary depending on which Xilinx FPGA is used. Consult the documentation for your particular FPGA (or its JTAG BSDL file) to determine these value.

### 5

### **Integrated System**

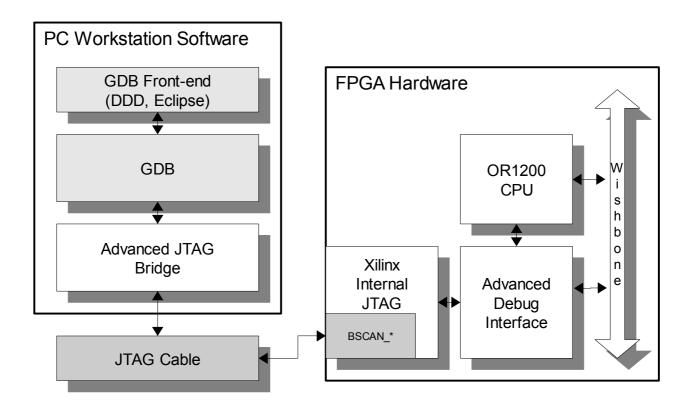

The Xilinx Internal JTAG core is just one part of the complete debugging system. To be useful, the system-on-chip must also include a compatible debug core (i.e. the adv\_dbg\_if core), a WishBone bus, and an OR1200 CPU (or a CPU with a compatible debug interface). Externally, the debugging system must include a JTAG cable, GDB (the GNU Debugger program), a GDB-to-JTAG bridge program (i.e. adv\_jtag\_bridge), and an optional graphical front-end to GDB, such as DDD or Eclipse. A block diagram of this system is shown in Figure 2.

Figure 2: Complete Debug System Block Diagram