## 1. DESCRIPTION OF LPM MODULES

This section describes in detail the functionality and semantics of each module in LPM.

### **1.1 MODULE CATEGORIES**

The LPM modules fall into five major categories:

| CATEGORY                          | DESCRIPTION                              |

|-----------------------------------|------------------------------------------|

| GATES                             |                                          |

| LPM_CONSTANT                      | Constant value                           |

| LPM_INV, LPM_AND, LPM_OR, LPM_XOR | Basic combinatorial gates                |

| LPM_BUSTRI                        | Tri-State buffer                         |

| LPM_MUX                           | Multiplexer                              |

| LPM_DECODE                        | Decoder                                  |

| LPM_CLSHIFT                       | Combinatorial shifter                    |

| ARITHMETIC COMPONENTS             |                                          |

| LPM_COUNTER                       | Counter                                  |

| LPM_ADD_SUB                       | Adder/Subtracter                         |

| LPM_COMPARE                       | Comparator                               |

| LPM_MULT                          | Multiplier                               |

| LPM_ABS                           | Absolute Value                           |

| LPM_DIVIDE                        | Divider                                  |

| STORAGE COMPONENTS                |                                          |

| LPM_ROM                           | Read Only Memory                         |

| LPM_LATCH                         | Transparent latch                        |

| LPM_FF                            | D-type or T-type flip-flop               |

| LPM_SHIFTREG                      | Shift Register                           |

| LPM_RAM_DQLPM_RAM_IO,             | Random Access Memory                     |

| LPM_RAM_DP                        | Dual-Port Ramdom Access Memory           |

| LPM_FIFO                          | Single colock First-In-First-Out Memory  |

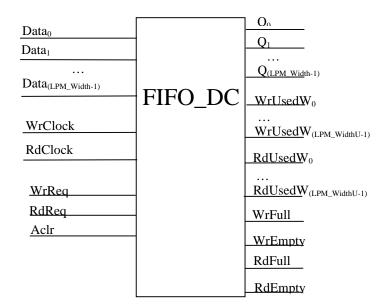

| LPM_FIFO_DC                       | Double colocks First-In-First-Out Memory |

| TABLE PRIMITIVES                  |                                          |

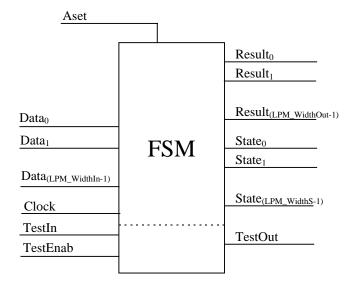

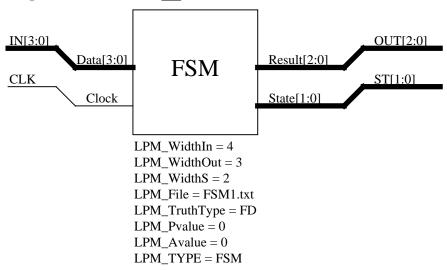

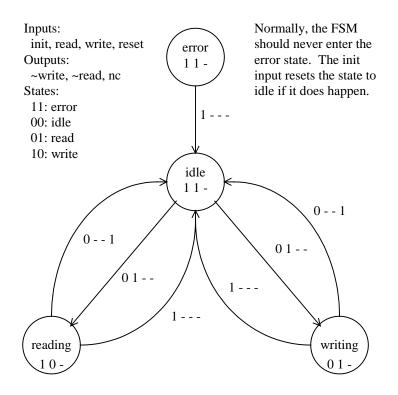

| LPM_FSM                           | Finite state machine                     |

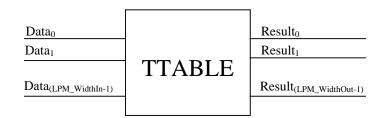

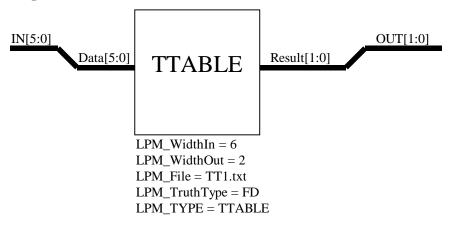

| LPM_TTABLE                        | Truth table                              |

| PAD PRIMITIVES                    |                                          |

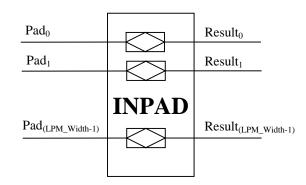

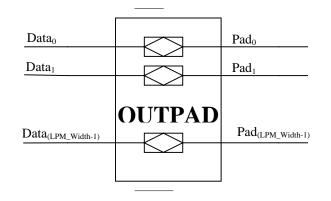

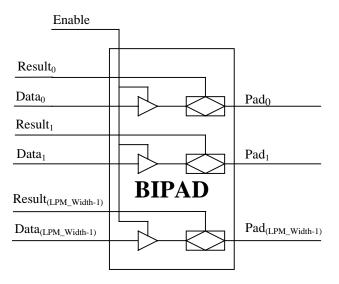

| LPM_INPAD, LPM_OUTPAD, LPM_BIPAD  | Input/Output/Bidrectional pads           |

Note that truth table, finite state machine, RAM and ROM modules require more information than can be contained in the LPM netlist to define their function. These modules use supporting files to describe their function. These supporting files use the standard Intel HEX, Berkeley PLA and KISS formats.

#### **1.1.1 Logic Conventions**

Where logic equations or logic models are used, the following symbols are used for both single bit operations and bit-wise vector operations:

| AND                  | &  |                                   |

|----------------------|----|-----------------------------------|

| OR                   |    |                                   |

| XOR                  | ^  |                                   |

| NOT or INVERT        | ~  | on vectors this is 1's complement |

| NAND                 | ~& |                                   |

| NOR                  | ~  |                                   |

| XNOR                 | ~^ |                                   |

| LEFT SHIFT           | << | vector only                       |

| RIGHT SHIFT          | >> | vector only                       |

| Two's Complement     | +  |                                   |

| or Unsigned Add      |    |                                   |

| Two's Complement     | _  |                                   |

| or Unsigned Subtract |    |                                   |

| Two's Complement     | ×  |                                   |

| or Unsigned Multiply |    |                                   |

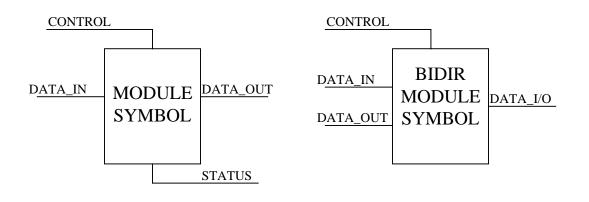

#### **1.1.2 Drawing Conventions**

The drawings of all modules in this document use the following conventions (shown in the figure below):

| Data Inputs    | Are shown going into the left of the module symbol.                                                                                                             |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Data Outputs   | Are shown coming out of the right side of the module symbol except<br>on bidir module symbols that have bi-directional port where they are<br>on the left side. |  |

| Control Inputs | Are shown going into the top of the module symbol.                                                                                                              |  |

| Status Outputs | Are shown coming out of the bottom of the module symbol.                                                                                                        |  |

| Data I/Os      | Are shown on the right side of the bidir module symbol.                                                                                                         |  |

| Width & Size   | Width refers to LPM_Width and Size refers to LPM_Size                                                                                                           |  |

#### **1.1.3 Scan Test Conventions**

All of the modules that have scan-test ports (LPM\_COUNTER, LPM\_LATCH, LPM\_FF, LPM\_TFF, LPM\_FSM) use the same convention. The **TestOut** port always has the same value as the most significant bit of the output (**Q** or **State**). When **TestEnab** is high, the data on **TestIn** is shifted into the least significant bit of the associated register as the contents of the register are shifted towards the most significant bit.

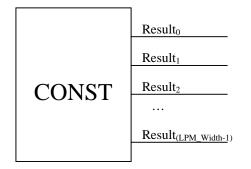

### 1.2 GATES 1.2.1 LPM\_CONSTANT

### **1.2.1.1** Ports

| ĺ | Port Name | Туре | Usage | Description | Comments                                                                                      |

|---|-----------|------|-------|-------------|-----------------------------------------------------------------------------------------------|

|   | Result    | 0    | -     | CValue      | Output vector LPM_Width wide<br>LPM_Cvalue is truncated or sign<br>extended to LPM_Width bits |

### 1.2.1.2 Properties

| Property     | Usage    | Value         | Comments                                                 |

|--------------|----------|---------------|----------------------------------------------------------|

| LPM_Width    | Required | LPM Value > 0 | Width of output vector                                   |

| LPM_CValue   | Required | LPM Value     | Value of constant                                        |

| LPM_Strength | Optional | WEAK          | If present, this indicates a pullup or pulldown strength |

### 1.2.1.3 Function

### Result = LPM\_Cvalue

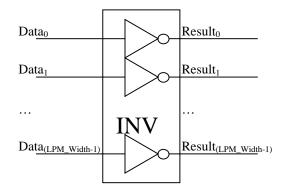

### 1.2.2 LPM\_INV

### 1.2.2.1 Ports

| Port Name | Туре | Usage    | Description     | Comments               |

|-----------|------|----------|-----------------|------------------------|

| Data      | Ι    | Required | Data input      | Vector, LPM_Width wide |

| Result    | 0    | Required | Inverted Result | Vector, LPM_Width wide |

### 1.2.2.2 Properties

| Property  | Usage    | Value         | Comments                          |

|-----------|----------|---------------|-----------------------------------|

| LPM_Width | Required | LPM Value > 0 | Width of input and output vectors |

### 1.2.2.3 Function

### Result = ~ Data

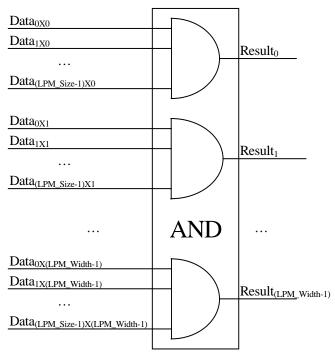

#### 1.2.3 LPM\_AND

#### 1.2.3.1 Ports

| Port Name | Туре | Usage    | Description             | Comments                              |

|-----------|------|----------|-------------------------|---------------------------------------|

| Data      | Ι    | Required | 1                       | Vector, LPM_Size times LPM_Width wide |

| Result    | 0    | Required | Result of AND operators | Vector, LPM_Width wide                |

#### 1.2.3.2 Properties

| Property  | Usage    | Value           | Comments                           |

|-----------|----------|-----------------|------------------------------------|

| LPM_Width | Required | LPM Value $> 0$ | Width of output vector.            |

|           |          |                 | Number of AND gates.               |

| LPM_Size  | Required | LPM Value $> 0$ | Number of inputs to each AND gate. |

|           |          |                 | Number of input buses.             |

#### 1.2.3.3 Function

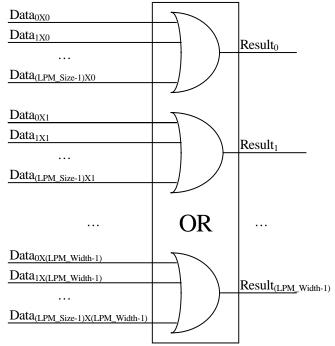

$Result_0 = Data_{0X0} \& Data_{1X0} \& Data_{2X0} \& \dots \& Data_{LPM\_Size-1X0}$

$Result_1 = Data_{0X1} \& Data_{1X1} \& Data_{2X1} \& \dots \& Data_{LPM\_Size-1X1}$

$Result_2 = Data_{0X2} \& Data_{1X2} \& Data_{2X2} \& \dots \& Data_{LPM\_Size-1X2}$

Result<sub>i</sub> = Data<sub>0Xi</sub> & Data<sub>1Xi</sub> & Data<sub>2Xi</sub> & ... & Data<sub>LPM\_Size-1Xi</sub>

Where i goes from 0 to (LPM\_Width - 1).

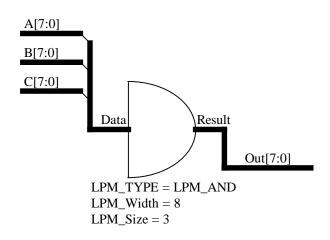

#### 1.2.3.4 Example

Suppose the designers have three 8-bit buses and they want to AND the corresponding bits of the three buses. This is done using an LPM\_AND with an LPM\_Width = 8 and an LPM\_Size = 3. The LPM\_Width of eight indicates that there are eight AND gates, and the LPM\_Size of three indicates that each AND gate has three inputs.

This diagram is for illustrative purposes only and is not intended to specify any implementation details.

The function performed by the LPM\_AND gate in this case is:

$Out[0] = Result_0 = Data_{0X0} \& Data_{1X0} \& Data_{2X0} = C[0] \& B[0] \& A[0]$

$Out[1] = Result_1 = Data_{0X1} \& Data_{1X1} \& Data_{2X1} = C[1] \& B[1] \& A[1]$

$Out[2] = Result_2 = Data_{0X2} \& Data_{1X2} \& Data_{2X2} = C[2] \& B[2] \& A[2]$

$Out[3] = Result_3 = Data_{0X3} \& Data_{1X3} \& Data_{2X3} = C[3] \& B[3] \& A[3]$

$Out[4] = Result_4 = Data_{0X4} \& Data_{1X4} \& Data_{2X4} = C[4] \& B[4] \& A[4]$

$Out[5] = Result_5 = Data_{0X5} \& Data_{1X5} \& Data_{2X5} = C[5] \& B[5] \& A[5]$

$Out[6] = Result_6 = Data_{0X6} \& Data_{1X6} \& Data_{2X6} = C[6] \& B[6] \& A[6]$

$Out[7] = Result_7 = Data_{0X7} \& Data_{1X7} \& Data_{2X7} = C[7] \& B[7] \& A[7]$

### 1.2.4 LPM\_OR

### 1.2.4.1 Ports

| Port Name | Туре | Usage    | Description            | Comments                              |

|-----------|------|----------|------------------------|---------------------------------------|

| Data      | Ι    | Required | 1                      | Vector, LPM_Size times LPM_Width wide |

| Result    | 0    | Required | Result of OR operators | Vector, LPM_Width wide                |

#### 1.2.4.2 Properties

| Property  | Usage    | Value           | Comments                          |

|-----------|----------|-----------------|-----------------------------------|

| LPM_Width | Required | LPM Value > 0   | Width of output vector.           |

|           |          |                 | Number of OR gates.               |

| LPM_Size  | Required | LPM Value $> 0$ | Number of inputs to each OR gate. |

|           |          |                 | Number of input buses.            |

#### 1.2.4.3 Function

$Result_i = Data_{0Xi} \mid Data_{1Xi} \mid Data_{2Xi} \mid \dots \mid Data_{LPM\_Size-1Xi}$

Where **i** goes from 0 to (LPM\_Width - 1).

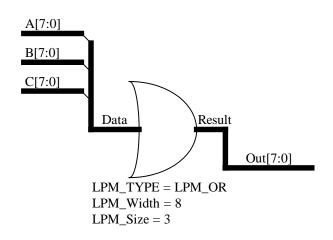

#### 1.2.4.4 Example

Suppose the designers have three 8-bit buses and they want to OR the corresponding bits of the three buses. This is done using an LPM\_OR with an LPM\_Width of 8 and an LPM\_Size of three. The LPM\_Width of eight indicates that there are eight OR gates, and the LPM\_Size of three indicates that each OR gate has three inputs.

This diagram is for illustrative purposes only and is not intended to specify any implementation details.

The function performed by the LPM\_OR gate in this case is:

$Out[0] = Result_0 = Data_{2X0} | Data_{1X0} | Data_{0X0} = A[0] | B[0] | C[0]$

$Out[1] = Result_1 = Data_{2X1} | Data_{1X1} | Data_{0X1} = A[1] | B[1] | C[1]$

$Out[2] = Result_2 = Data_{2X2} | Data_{1X2} | Data_{0X2} = A[2] | B[2] | C[2]$

$Out[3] = Result_3 = Data_{2X3} | Data_{1X3} | Data_{0X3} = A[3] | B[3] | C[3]$

$Out[4] = Result_4 = Data_{2X4} | Data_{1X4} | Data_{0X4} = A[4] | B[4] | C[4]$

$Out[5] = Result_5 = Data_{2X5} | Data_{1X5} | Data_{0X5} = A[5] | B[5] | C[5]$

$Out[6] = Result_6 = Data_{2X6} | Data_{1X6} | Data_{0X6} = A[6] | B[6] | C[6]$

$Out[7] = Result_7 = Data_{2X7} | Data_{1X7} | Data_{0X7} = A[7] | B[7] | C[7]$

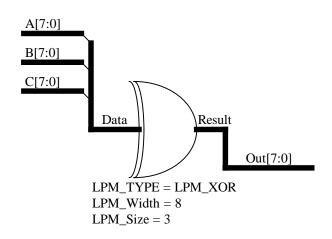

# 1.2.5 LPM\_XOR

### 1.2.5.1 Ports

| Port Name | Туре | Usage    | Description             | Comments                              |

|-----------|------|----------|-------------------------|---------------------------------------|

| Data      | Ι    | Required | 1                       | Vector, LPM_Size times LPM_Width wide |

| Result    | 0    | Required | Result of XOR operators | Vector, LPM_Width wide                |

### 1.2.5.2 Properties

| Property  | Usage    | Value           | Comments                           |

|-----------|----------|-----------------|------------------------------------|

| LPM_Width | Required | LPM Value > 0   | Width of output vector.            |

|           |          |                 | Number of XOR gates.               |

| LPM_Size  | Required | LPM Value $> 0$ | Number of inputs to each XOR gate. |

|           |          |                 | Number of input buses.             |

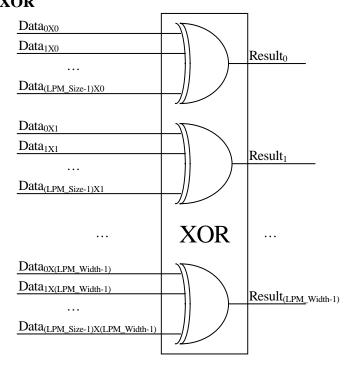

#### 1.2.5.3 Function

$Result_i = Data_{0Xi} \wedge Data_{1Xi} \wedge Data_{2Xi} \wedge \dots \wedge Data_{LPM_Size-1Xi}$

Where **i** goes from 0 to (LPM\_Width - 1).

#### 1.2.5.4 Example

Suppose the designers have three 8-bit buses and they want to XOR the corresponding bits of the three buses. This is done using an LPM\_XOR with an LPM\_Width of 8 and an LPM\_Size of three. The LPM\_Width of eight indicates that there are eight XOR gates, and the LPM\_Size of three indicates that each XOR gate has three inputs.

This diagram is for illustrative purposes only and is not intended to specify any implementation details.

The function performed by the LPM\_XOR gate in this case is:

$\begin{aligned} & Out[0] = Result_0 = Data_{2X0} \land Data_{1X0} \land Data_{0X0} = A[0] \land B[0] \land C[0] \\ & Out[1] = Result_1 = Data_{2X1} \land Data_{1X1} \land Data_{0X1} = A[1] \land B[1] \land C[1] \\ & Out[2] = Result_2 = Data_{2X2} \land Data_{1X2} \land Data_{0X2} = A[2] \land B[2] \land C[2] \\ & Out[3] = Result_3 = Data_{2X3} \land Data_{1X3} \land Data_{0X3} = A[3] \land B[3] \land C[3] \\ & Out[4] = Result_4 = Data_{2X4} \land Data_{1X4} \land Data_{0X4} = A[4] \land B[4] \land C[4] \\ & Out[5] = Result_5 = Data_{2X5} \land Data_{1X5} \land Data_{0X5} = A[5] \land B[5] \land C[5] \\ & Out[6] = Result_6 = Data_{2X6} \land Data_{1X6} \land Data_{0X6} = A[6] \land B[6] \land C[6] \\ & Out[7] = Result_7 = Data_{2X7} \land Data_{1X7} \land Data_{0X7} = A[7] \land B[7] \land C[7] \end{aligned}$

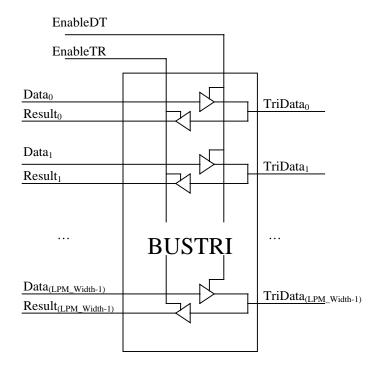

### 1.2.6 LPM\_BUSTRI

Connection to a Tri-State Bus.

#### 1.2.6.1 Ports

| Port Name | Туре | Usage    | Description               | Comments                                                                  |

|-----------|------|----------|---------------------------|---------------------------------------------------------------------------|

| TriData   | ΙΟ   | Required | Bi-directional bus signal | Vector, LPM_Width wide                                                    |

| Data      | Ι    | Note 1   | 1                         | Vector, LPM_Width wide. One of <b>Data</b> or <b>Result</b> must be used. |

| EnableDT  | Ι    | 1        |                           | Default value is Low. Required if <b>Data</b> is used.                    |

| Result    | 0    | Note 1   | 1                         | Vector, LPM_Width wide. One of <b>Data</b> or <b>Result</b> must be used. |

| EnableTR  | Ι    | 1        |                           | Default value is Low. Required if <b>Result</b> is used                   |

Note 1: Either the **Result** or **Data** port is required. Both may be used.

#### **1.2.6.2** Properties

| Property  | Usage    | Value         | Comments                          |

|-----------|----------|---------------|-----------------------------------|

| LPM_Width | Required | LPM Value > 0 | Width of input and output vectors |

### 1.2.6.3 Functions

| EnableDT | EnableTR | Data  | Result                 | TriData             |

|----------|----------|-------|------------------------|---------------------|

| L        | L        | Х     | Hi-Z                   | Hi-Z Note 1         |

| L        | Н        | Х     | VALUE                  | VALUE               |

|          |          |       | (From <b>TriData</b> ) |                     |

| Н        | L        | VALUE | Hi-Z                   | VALUE               |

|          |          |       |                        | (From <b>Data</b> ) |

| Н        | Н        | VALUE | VALUE                  | VALUE               |

|          |          |       | (From <b>Data</b> )    | (From <b>Data</b> ) |

Note 1: When both control ports (EnableDT and EnableTR) are inactive (LOW) the Result port is high impedance, and the TriData port will take its value from the attached net (i.e. it is not driven by the LPM\_Bustri).

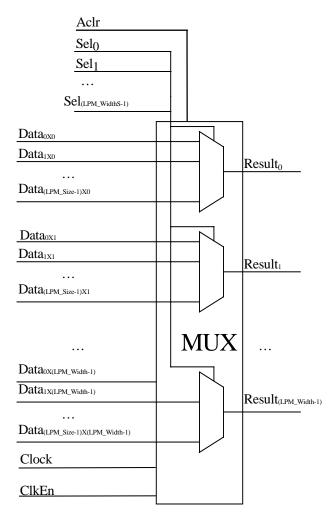

#### **1.2.7 LPM\_MUX**

#### 1.2.7.1 Ports

| Port Name | Туре | Usage    | Description Comments                         |                                       |

|-----------|------|----------|----------------------------------------------|---------------------------------------|

| Data      | Ι    | Required | <b>Data</b> input                            | Vector, LPM_Size times LPM_Width wide |

| Result    | 0    | Required | Selected input vector Vector, LPM_Width wide |                                       |

| Sel       | Ι    | Required | Selects one of the input                     | Vector, LPM_WidthS wide               |

|           |      |          | vectors                                      |                                       |

| Clock     | Ι    | Optional | Clock for pipelined usage Note 1             |                                       |

| ClkEn     | Ι    | Optional | Clock enable for pipelined                   | Note 2                                |

| Aclr      | Ι    | Optional | Asynchronous Clear                           | Note 3                                |

Note 1: The **Clock** port provides for pipelined operation of the LPM\_MUX. If a lpm\_pipeline other than 0 (default value) is specified, then the clock port must be connected.

Note 2: The ClkEn port provides a clock enable for pipelined operation.

Note 3: The pipeline initializes to undefined. The **Aclr** port may be used at any time to reset the pipeline to all 0's asynchronously to the clock.

|              | leb      |                    |                                                                                                                            |

|--------------|----------|--------------------|----------------------------------------------------------------------------------------------------------------------------|

| Property     | Usage    | Value              | Comments                                                                                                                   |

| LPM_Width    | Required | LPM Value > 0      | Width of output vector. Number of Multiplexers.                                                                            |

| LPM_Size     | Required | LPM Value > 0      | Number of inputs to each Multiplexer.<br>Number of input buses.                                                            |

| LPM_WidthS   | Required | LPM Value >0       | WidthS should be the next integer greater than or equal to $log_2(LPM\_Size)$ or there will be unselectable input vectors. |

| LPM_Pipeline | Optional | LPM Value $\geq 0$ | Default is 0 - non-pipelined                                                                                               |

### 1.2.7.2 Properties

### **1.2.7.3 Functions**

| Sel vector | Sel Value  | Result                                     |

|------------|------------|--------------------------------------------|

| 0000000    | 0          | Data <sub>0_[LPM_Width-1:0]</sub>          |

| 0000001    | 1          | Data <sub>1_[LPM_Width-1:0]</sub>          |

| 0000010    | 2          | Data <sub>2_[LPM_Width-1:0]</sub>          |

|            | •••        |                                            |

| 1111110    | LPM_Size-2 | Data <sub>LPM_Size-2_[LPM_Width-1:0]</sub> |

| 1111111    | LPM_Size-1 | Data <sub>LPM_Size-1_[LPM_Width-1:0]</sub> |

This table assumes that LPM\_Size is a power of two, but that is not required. If there is no **Data** vector that corresponds to the 'Sel Value'; that is, if  $Data_{Sel_Value}$  is not connected or is greater than LPM\_Size, the selection of 'Sel Value' will produce an undefined **Result**.

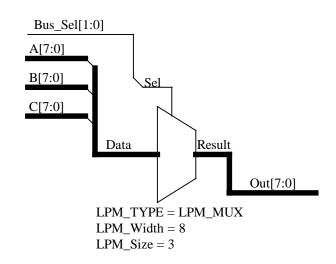

#### 1.2.7.4 Example

Suppose the designers have three 8-bit buses and they want to select one of the three buses. This is done using an LPM\_MUX with an LPM\_Width of 8 and an LPM\_Size of three. The LPM\_Width of eight indicates that there are eight multiplexers, and the LPM\_Size of three indicates that each multiplexer has three inputs.

This diagram is for illustrative purposes only and is not intended to specify any implementation details.

Supposing that bus A becomes  $Data_{2Xi}$ , bus B becomes  $Data_{1Xi}$ , and bus C becomes  $Data_{0Xi}$ , the function performed by the LPM\_MUX gate in this case is:

$\begin{aligned} &\text{Out}[0] = \text{Result}_0 = \text{Data}_{\text{SelX0}} = (\text{UNDEFINED if Sel} = 3, \text{ A}[0] \text{ if Sel} = 2, \text{ B}[0] \text{ if Sel} = 1, \text{ C}[0] \text{ if Sel} = 0 ) \\ &\text{Out}[1] = \text{Result}_1 = \text{Data}_{\text{SelX1}} = (\text{UNDEFINED if Sel} = 3, \text{ A}[1] \text{ if Sel} = 2, \text{ B}[1] \text{ if Sel} = 1, \text{ C}[1] \text{ if Sel} = 0 ) \\ &\text{Out}[2] = \text{Result}_2 = \text{Data}_{\text{SelX2}} = (\text{UNDEFINED if Sel} = 3, \text{ A}[2] \text{ if Sel} = 2, \text{ B}[2] \text{ if Sel} = 1, \text{ C}[2] \text{ if Sel} = 0 ) \\ &\text{Out}[3] = \text{Result}_3 = \text{Data}_{\text{SelX3}} = (\text{UNDEFINED if Sel} = 3, \text{ A}[3] \text{ if Sel} = 2, \text{ B}[3] \text{ if Sel} = 1, \text{ C}[3] \text{ if Sel} = 0 ) \\ &\text{Out}[4] = \text{Result}_4 = \text{Data}_{\text{SelX4}} = (\text{UNDEFINED if Sel} = 3, \text{ A}[4] \text{ if Sel} = 2, \text{ B}[4] \text{ if Sel} = 1, \text{ C}[4] \text{ if Sel} = 0 ) \\ &\text{Out}[5] = \text{Result}_5 = \text{Data}_{\text{SelX5}} = (\text{UNDEFINED if Sel} = 3, \text{ A}[5] \text{ if Sel} = 2, \text{ B}[5] \text{ if Sel} = 1, \text{ C}[5] \text{ if Sel} = 0 ) \\ &\text{Out}[6] = \text{Result}_6 = \text{Data}_{\text{SelX6}} = (\text{UNDEFINED if Sel} = 3, \text{ A}[6] \text{ if Sel} = 2, \text{ B}[6] \text{ if Sel} = 1, \text{ C}[6] \text{ if Sel} = 0 ) \\ &\text{Out}[7] = \text{Result}_7 = \text{Data}_{\text{SelX6}} = (\text{UNDEFINED if Sel} = 3, \text{ A}[7] \text{ if Sel} = 2, \text{ B}[7] \text{ if Sel} = 1, \text{ C}[6] \text{ if Sel} = 0 ) \end{aligned}$

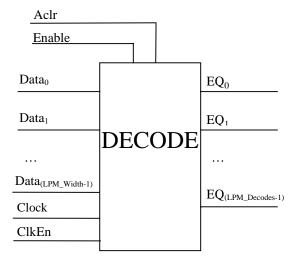

#### 1.2.8 LPM\_DECODE

#### 1.2.8.1 Ports

| Port Name | Туре | Usage    | Description                                    | Comments                                   |

|-----------|------|----------|------------------------------------------------|--------------------------------------------|

| Data      | Ι    |          | Data input. Treated as unsigned binary number. | Vector, LPM_Width wide                     |

| Enable    | Ι    |          | Enable. All outputs low when not active        | Default value is Active (High) if absent.  |

| EQ        | 0    | -        | For $i = 0$ to                                 | Vector, LPM_Decodes wide.                  |

|           |      |          | LPM_Decodes                                    | If <b>Data</b> $\geq$ LPM_Decodes then all |

|           |      |          | if $(i = \mathbf{Data}) Eq_i = 1$              | Eq <sub>i</sub> are 0                      |

|           |      |          | else $Eq_i = 0$                                |                                            |

| Clock     | Ι    | Optional | Clock for pipelined usage                      | Note 1                                     |

| ClkEn     | Ι    | Optional | Clock enable for pipelined                     | Note 2                                     |

| Aclr      | Ι    | Optional | Asynchronous Clear                             | Note 3                                     |

Note 1: The **Clock** port provides for pipelined operation of the LPM\_DECODE. If a lpm\_pipeline other than 0 (default value) is specified, then the clock port must be connected.

Note 2: The **ClkEn** port provides a clock enable for pipelined operation.

Note 3: The pipelined initializes to undefined. The **Aclr** port may be used at any time to reset the pipeline to all 0's asynchronously to the clock.

| Property     | Usage    | Value                             | Comments                     |

|--------------|----------|-----------------------------------|------------------------------|

| LPM_Width    | Required | LPM Value > 0                     | Width of input vector        |

| LPM_Decodes  | Required | $0 < LPM Value \le 2^{LPM_Width}$ | Number of explicit decodes   |

| LPM_Pipeline | Optional | LPM Value $\geq 0$                | Default is 0 - non-pipelined |

#### 1.2.8.2 Properties

| 1.2.0.3 Г | unctions                 |                                  |

|-----------|--------------------------|----------------------------------|

| Enable    | Data vector              | Eq <sub>i</sub> that is 1 (high) |

|           |                          | all other $Eq_i = 0$ (low)       |

| L         | Х                        | NONE                             |

| Н         | 0000000                  | $Eq_0$                           |

| Н         | 0000001                  | Eq <sub>1</sub>                  |

|           |                          |                                  |

| Н         | 0000101                  | Eq <sub>5</sub>                  |

|           |                          |                                  |

| Н         | $Data = LPM\_Decodes -1$ | $Eq_{(LPM\_Decodes-1)}$          |

| Н         | Data = LPM_Decodes       | NONE                             |

| Н         | Data > LPM_Decodes       | NONE                             |

### 1.2.8.3 Functions

Note 1: If Data = i and  $Eq_i$  is not connected or does not appear in the symbol then all outputs will be low.

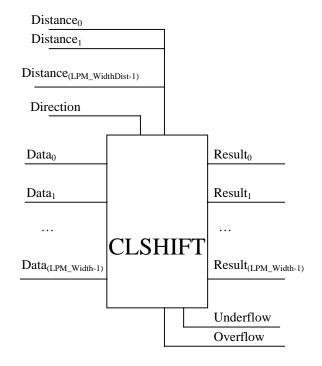

### 1.2.9 LPM\_CLSHIFT

Combinatorial Logic shifter. Barrel Shifter.

#### 1.2.9.1 Ports

| Port Name | Туре | Usage    | Description                                                                 | Comments                                            |

|-----------|------|----------|-----------------------------------------------------------------------------|-----------------------------------------------------|

| Data      | Ι    | Required | Data to be shifted.                                                         | Vector, LPM_Width wide                              |

| Distance  | Ι    | -        | Number of positions to shift <b>Data</b> .                                  | Vector, LPM_WidthDist wide                          |

| Direction | Ι    | 1        | Direction of shift.<br>Low = Left (toward MSB)<br>High = Right (toward LSB) | Default value is 0 (Low) =<br>Left (toward the MSB) |

| Result    | 0    | Required | Shifted <b>Data</b>                                                         | Vector, LPM_Width wide                              |

| Overflow  | 0    | Optional | Logical or Arithmetic Overflow                                              | Note 1                                              |

| Underflow | 0    | Optional | Logical or Arithmetic Underflow                                             | Note 1                                              |

Note 1: If the LPM\_ShiftType is **ROTATE** and Overflow or Underflow are connected, the output of those ports will be undefined.

#### 1.2.9.2 Properties

| Property      | Usage    | Value            | Comments                   |

|---------------|----------|------------------|----------------------------|

| Toperty       | Usage    | Value            | Comments                   |

| LPM_Width     | Required | LPM Value > 0    | Width of input vector      |

| LPM_WidthDist | Optional | LPM Value > 0    | Width of the Distance Port |

|               |          |                  | Note 1                     |

| LPM_ShiftType | Optional | LOGICAL   ROTATE | Default is LOGICAL         |

|               |          | ARITHMETIC       | Note 2                     |

Note 1: LPM\_WidthDist specifies the width of the Distance port. The values on the Distance port would normally range from 0 which would mean "no shift" to (LPM\_Width-1) which would be the maximum meaningful shift. The typical value assigned to LPM\_WidthDist would be "the smallest integer not less than log<sub>2</sub>(LPM\_Width)" or [log<sub>2</sub>LPM\_Width]. Any value on the Distance port greater than LPM\_Width-1 results in an UNDEFINED output.

Note 2: The sign bit is extended for ARITHMETIC. For a LOGICAL right shift 0's are always shifted into the MSB.

#### 1.2.9.3 Functions

The LPM\_CLSHIFT module acts like a barrel-shifter. It is entirely combinational logic.

Overflow occurs when the shifted result exceeds the precision of the **Result** bus. For LOGICAL values, overflow occurs when all ones have been shifted out. For ARITHMETIC value, overflow occurs a significant digit is shifted into or past the sign bit.

| LPM_ShiftType | Direction | Function                                                                                                                      |

|---------------|-----------|-------------------------------------------------------------------------------------------------------------------------------|

| LOGICAL       | 0 = Left  | Result = Data << Distance                                                                                                     |

| LOGICAL       | 1 = Right | Result = Data >> Distance                                                                                                     |

| ROTATE        | 0 = Left  | $\begin{aligned} Result_i &= Data_x \text{ where } x \text{ is } ((Distance + i ) \text{ mod} \\ LPM\_Width) \end{aligned}$   |

| ROTATE        | 1 = Right | $\begin{aligned} Result_i &= Data_x \text{ where } x \text{ is } ((Distance - i \ ) \text{ mod} \\ LPM\_Width) \end{aligned}$ |

| ARITHMETIC    | 0 = Left  | Result = DATA * $2^{\text{LPM}_{\text{WidthDist}}}$                                                                           |

| ARITHMETIC    | 1 = Right | Result = DATA $\div 2^{\text{LPM}_{\text{WidthDist}}}$ (integer divide)                                                       |

Underflow occurs when the shifted result contains no significant digits.

Values larger than (LPM\_Width - 1) result in an UNDEFINED output.

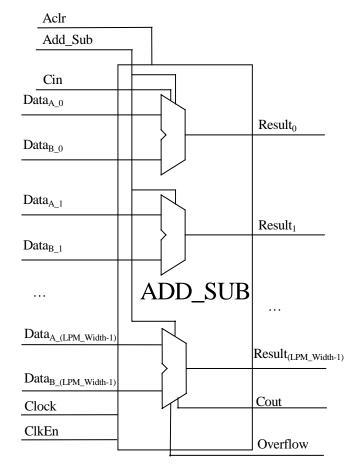

### **1.3 ARITHMETIC COMPONENTS 1.3.1 LPM\_ADD\_SUB**

#### 1.3.1.1 Ports

| Port Name | Туре | Usage    | Description                                                                        | Comments                                                                                         |  |  |  |  |

|-----------|------|----------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| DataA     | Ι    | Required | Augend/Minuend                                                                     | Vector, LPM_Width wide                                                                           |  |  |  |  |

| DataB     | Ι    | Required | Addend/Subtrahend                                                                  | Vector, LPM_Width wide                                                                           |  |  |  |  |

| Cin       | Ι    |          | Carry in to the low order bit<br>OP=ADD Low= 0 High= +1<br>OP=SUB Low = -1 High= 0 | If not connected, default value is LOW.                                                          |  |  |  |  |

| Add_Sub   | Ι    |          | performed                                                                          | Cannot be used it LPM_Direction<br>property is used. If not connected,<br>defaults value is ADD. |  |  |  |  |

| Result    | 0    | Required | $DataA \pm DataB \pm Cin$                                                          | Vector, LPM_Width wide                                                                           |  |  |  |  |

| Cout      | 0    |          | Carry-out (~Borrow-in) of<br>Most Significant Bit (MSB)                            | Note 1                                                                                           |  |  |  |  |

| Overflow | 0 | -        | Result exceeds available precision. | Note 2 |

|----------|---|----------|-------------------------------------|--------|

| Clock    | Ι | Optional | Clock for pipelined usage           | Note 3 |

| Clken    | Ι | Optional | Clock enable for pipelined          | Note 4 |

| Aclr     | Ι | Optional | Asynchronous Clear                  | Note 5 |

Note 1: **Cout** has a physical interpretation as the carry-out (~borrow-in) of the most significant bit. Cout is most meaningful for detecting overflow in **unsigned** numbers. See Table 1 for the arithmetic interpretation of **Cout** = 1.

- Note 2: **Overflow** has a physical interpretation as the XOR (exclusive or) of the carry into the MSB with the carry out of the MSB. Overflow is only meaningful when the LPM\_Representation is **signed**. It indicates that the **Result** has exceeded the available precision. See Table 2 for the arithmetic interpretation of **Overflow** = 1.

- Note 3: The **Clock** port provides for pipelined operation of the LPM\_ADD\_SUB. If a lpm\_pipeline other than 0 (default value) is specified, then the clock port must be connected.

- Note 4: The **ClkEn** port provides a clock enable for pipelined operation.

- Note 5: The pipelined initializes to undefined. The **Aclr** port may be used at any time to reset the pipeline to all 0's asynchronously to the clock

|          | OP = ADD                                                                      | OP = SUB                                                                                       |

|----------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Unsigned | $(\mathbf{DataA} + \mathbf{DataB} + \mathbf{Cin}) > 2^{\text{LPM}_Width} - 1$ | Normal Subtract. However, if $Cout = 0$ ,<br>then (DataA - DataB - Cin) < 0                    |

| Signed   | Normal result of adding two negative numbers, or possible overflow.           | Normal result when subtracting a positive number from a negative number, or possible overflow. |

Table 1: Arithmetic interpretation of Cout = 1

Table 2: Arithmetic interpretation of Overflow = 1

|          | OP=ADD                                        | OP=SUB                                        |  |  |

|----------|-----------------------------------------------|-----------------------------------------------|--|--|

| Unsigned | Not meaningful                                | Not meaningful                                |  |  |

| Signed   | $(DataA + DataB + Cin) > 2^{LPM_Width-1} - 1$ | $(DataA - DataB - Cin) > 2^{LPM_Width-1} - 1$ |  |  |

|          | or                                            | or                                            |  |  |

|          | $(DataA + DataB + Cin) < -2^{LPM_Width-1}$    | $(DataA - DataB - Cin) < -2^{LPM_Width-1}$    |  |  |

#### **1.3.1.2** Properties

| Property           | Usage    | Value                 | Comments                                                                      |

|--------------------|----------|-----------------------|-------------------------------------------------------------------------------|

| LPM_Width          | Required | LPM Value > 0         | Width of DataA, DataB and Result                                              |

| LPM_Direction      | Optional | ADD   SUB             | Default is ADD. <b>Add_Sub</b> port may not be used if this property is used. |

| LPM_Representation | Optional | UNSIGNED or<br>SIGNED | Default is SIGNED                                                             |

| LPM_Pipeline       | Optional | LPM Value $\geq 0$    | Default is 0 - non-pipelined                                                  |

### 1.3.1.3 Functions

$Result_i = DataA_i \land DataB_i \land Cin_i \land (\sim Add\_Sub)$

**Cout** = carry out of the MSB

**Overflow** = the XOR of the carry into the MSB and **Cout**

When **Cout** is prepended to the **Result**, the result is a vector that always has sufficient precision to represent the result of the operation.

$\{Cout, Result\} = DataA + Cin \pm DataB$

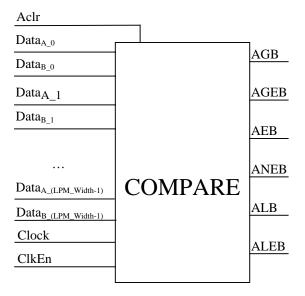

#### **1.3.2 LPM\_COMPARE**

#### 1.3.2.1 Ports

| 1.3.4.1 10 | 1 65 |          |                                     |                        |

|------------|------|----------|-------------------------------------|------------------------|

| Port Name  | Туре | Usage    | Description                         | Comments               |

| DataA      | Ι    | Required | <b>DataB</b> is compared to this.   | Vector, LPM_Width wide |

| DataB      | Ι    | Required | This is compared to <b>DataA</b>    | Vector, LPM_Width wide |

| AGB        | 0    | Note 1   | High (1) if <b>DataA &gt; DataB</b> |                        |

| AGEB       | 0    | Note 1   | $High (1) if DataA \ge DataB$       |                        |

| AEB        | 0    | Note 1   | High (1) if DataA = DataB           |                        |

| ANEB       | 0    | Note 1   | High (1) if <b>DataA ≠ DataB</b>    |                        |

| ALB        | 0    | Note 1   | High (1) if <b>DataA &lt; DataB</b> |                        |

| ALEB       | 0    | Note 1   | $High (1) if DataA \leq DataB$      |                        |

| Clock      | Ι    | Optional | Clock for pipelined usage           | Note 2                 |

| ClkEn      | Ι    | Optional | Clock enable for pipelined          | Note 3                 |

| Aclr       | Ι    | Optional | Asynchronous Clear                  | Note 4                 |

Note 1: At least one of the 6 output ports must be connected.

- Note 2: The **Clock** port provides for pipelined operation of the LPM\_COMPARE. If a lpm\_pipeline other than 0 (default value) is specified, then the **Clock** port must be connected.

- Note 3: The **ClkEn** port provides a clock enable for pipelined operation.

- Note 4: The pipelined initializes to undefined. The **Aclr** port may be used at any time to reset the pipeline to all 0's asynchronously to the clock.

### 1.3.2.2 Properties

| Property          | Usage    | Value                 | Comments                               |

|-------------------|----------|-----------------------|----------------------------------------|

| LPM_Width         | Required | LPM Value > 0         | Width of <b>DataA</b> and <b>DataB</b> |

| LPM_Representatio | Optional | UNSIGNED or<br>SIGNED | Default is UNSIGNED.                   |

| LPM_Pipeline      | Optional | LPM Value ≥0          | Default is 0 - non-pipelined           |

### 1.3.2.3 Functions

Signed or unsigned comparison of the value represented by **DataA** versus the value represented by **DataB**. Note that:

$AEB = \sim ANEB$   $ALB = \sim AGEB$   $AGB = \sim ALEB$

#### 1.3.3 LPM\_MULT

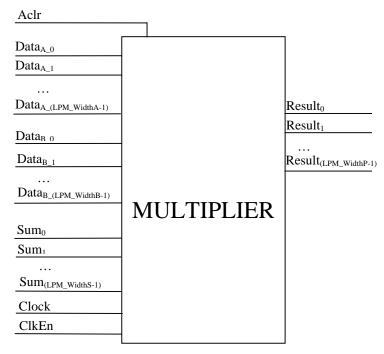

#### 1.3.3.1 Ports

| Port Name | Туре | Usage    | Description                | Comments                        |

|-----------|------|----------|----------------------------|---------------------------------|

| DataA     | Ι    | Required | Multiplicand               | Vector, LPM_WidthA wide         |

| DataB     | Ι    | Required | Multiplier                 | Vector, LPM_WidthB wide         |

| Sum       | Ι    | Optional | Partial Sum                | Vector, LPM_WidthS wide. Note 1 |

| Result    | 0    | Required | Product                    | Vector, LPM_WidthP wide. Note 2 |

| Clock     | Ι    | Optional | Clock for pipelined usage  | Note 3                          |

| ClkEn     | Ι    | Optional | Clock enable for pipelined | Note 4                          |

| Aclr      | Ι    | Optional | Asynchronous Clear         | Note 5                          |

- Note 1: An extra bit should be reserved in the LPM\_WidthS if a carry out is expected from addition of the Product and the Partial Sum. LPM\_WidthS should be larger than LPM\_WidthA plus LPM\_WidthB to guarantee that the carry out will be represented in Result.

- Note 2: The product is a vector, LPM\_WidthP bits wide. If LPM\_WidthP is less than the maximum of either LPM\_WidthA plus LPM\_WidthB or LPM\_WidthS, then only the LPM\_WidthP most significant bits are present. See 1.3.3.3.

- Note 3: The **Clock** port provides for pipelined operation of the LPM\_MULT. If a lpm\_pipeline other then 0 (default value) is specified, then the clock port must be connected.

- Note 4: The ClkEn port provides a clock enable for pipelined operation.

- Note 5: The pipelined initializes to undefined. The **Aclr** port may be used at any time to reset the pipeline to all 0's asynchronously to the clock.

| Property          | Usage    | Value                 | Comments                                                                      |

|-------------------|----------|-----------------------|-------------------------------------------------------------------------------|

| LPM_WidthA        | Required | LPM Value > 0         | Width of <b>DataA</b>                                                         |

| LPM_WidthB        | Required | LPM Value > 0         | Width of <b>DataB</b>                                                         |

| LPM_WidthS        | Optional | LPM Value > 0         | Width of <b>Sum.</b> Required if the <b>Sum</b> port is used.                 |

| LPM_WidthP        | Required | LPM Value > 0         | Width of <b>Result.</b> This represents the LPM_WidthP most significant bits. |

| LPM_Representatio | Optional | UNSIGNED or<br>SIGNED | Default is UNSIGNED.                                                          |

| LPM_Pipeline      | Optional | LPM Value $\geq 0$    | Default is 0 - non-pipelined                                                  |

### 1.3.3.2 Properties

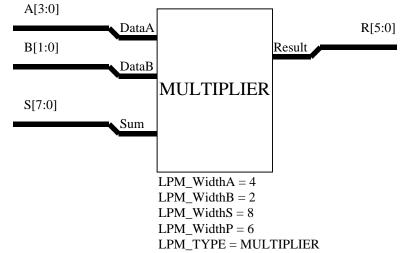

### **1.3.3.3 Function**

### **Result** = (**DataA** \* **DataB**) + **Sum**

The LSB of the product of **DataA** and **DataB** is aligned with the LSB of **Sum.**

### 1.3.3.4 Example

This diagram is for illustrative purposes only and is not intended to specify any implementation details.

|   |            |            |    |            | A3         | A2 | A1         | A0         |

|---|------------|------------|----|------------|------------|----|------------|------------|

|   |            |            |    |            |            | ×  | B1         | <b>B</b> 0 |

|   |            | =          | P5 | P4         | P3         | P2 | P1         | P0         |

| + | <b>S</b> 7 | <b>S</b> 6 | S5 | <b>S</b> 4 | <b>S</b> 3 | S2 | <b>S</b> 1 | <u>S0</u>  |

| = | X7         | X6         | X5 | X4         | X3         | X2 | X1         | X0         |

| = | R5         | R4         | R3 | R2         | R1         | R0 |            |            |

The partial product is represented by P, and the full product by X. Both are internal only.

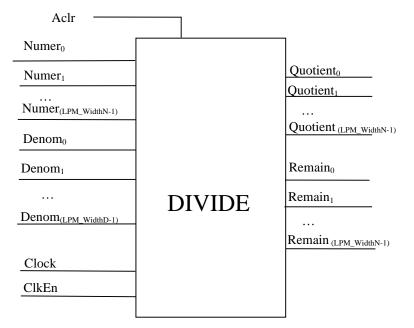

#### 1.3.4 LPM\_DIVDE

#### 1.3.4.1 Ports

| Port Name | Туре | Usage    | Description                | Comments                           |

|-----------|------|----------|----------------------------|------------------------------------|

| Numer     | Ι    | Required | Numerator                  | Vector, LPM_WidthN wide            |

| Denom     | Ι    | Required | Denominator                | Vector, LPM_WidthD wide.<br>Note 1 |

| Clock     | Ι    | Optional | Clock for pipelined usage  | Note 2                             |

| ClkEn     | Ι    | Optional | Clock enable for pipelined | Note 3                             |

| Aclr      | Ι    | Optional | Asynchronous Clear         | Note 4                             |

| Quotient  | 0    | Note 5   | Quotient                   | Vector, LPM_WidthN wide            |

| Remain    | 0    | Note 5   | Remainder                  | Vector, LPM_WidthD wide            |

Note 1: The Quotient and Remain will be UNDEFINED if Denom value is 0.

- Note 2: The **Clock** port provides for pipelined operation of the LPM\_DIVIDE. If a lpm\_pipeline other than 0 (default value) is specified, then the clock port must be connected.

- Note 3: The ClkEn port provides a clock enable for pipelined operation.

- Note 4: The pipeline initializes to undefined. The **Aclr** port may be used at any time to reset the pipeline to all 0's asynchronously to the clock.

Note 5: At lease one of **Quotient** and **Remain** ports must be used.

### 1.3.4.2 Properties

| Property            | Usage    | Value                 | Comments                     |

|---------------------|----------|-----------------------|------------------------------|

| LPM_WidthN          | Required | LPM Value $> 0$       | Width of <b>Numer</b>        |

| LPM_WidthD          | Required | LPM Value > 0         | Width of <b>Denom</b>        |

| LPM_NRepresentation | Optional | UNSIGNED or<br>SIGNED | Default is UNSIGNED.         |

| LPM_DRepresentation | Optional | UNSIGNED or<br>SIGNED | Default is UNSIGNED.         |

| LPM_Pipeline        | Optional | LPM Value $\geq 0$    | Default is 0 - non-pipelined |

### 1.3.4.3 Function

### **Quotient = Numerator / Denominator**

### Numerator = Quotient \* Denominator + Remainder

#### 1.3.4.4 Examples:

| Numerator | Denominator | Quotient | Remainder |

|-----------|-------------|----------|-----------|

| +7        | +3          | +2       | +1        |

| -1        | +3          | -1       | +2        |

| -4        | +3          | -2       | +2        |

| -7        | +3          | -3       | +2        |

| +7        | -3          | -2       | +1        |

| +4        | -3          | -1       | +1        |

| -4        | -3          | +2       | +2        |

| -7        | -3          | +3       | +2        |

In all cases, Remainder is always positive, while Quotient can be negative.

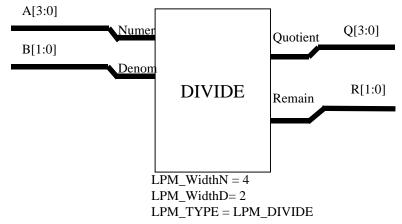

### 1.3.4.5 Example

This diagram is for illustrative purposes only and is not intended to specify any implementation details.

|       |                                             | A3         | A2     | A1 | A0 |

|-------|---------------------------------------------|------------|--------|----|----|

|       |                                             |            | /      | B1 | B0 |

|       | =                                           | Q3         | Q2     | Q1 | Q0 |

|       |                                             |            |        | R1 | R0 |

| ronro | souted by $\mathbf{O}$ and the remainder is | roprosonto | d hy D |    |    |

The quotient is represented by Q, and the remainder is represented by R.

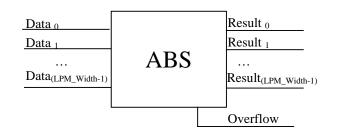

### 1.3.5 LPM\_ABS

### 1.3.5.1 Ports

| Port Name | Туре | Usage    | Description                           | Comments                |

|-----------|------|----------|---------------------------------------|-------------------------|

| Data      | Ι    | Required | Vector represents SIGNED number       | Vector, LPM_Width wide  |

| Result    |      | -        |                                       | Vector, LPM_Width wide. |

| Overflow  | 0    | Optional | High (1) if $Data = -2^{LPM_Width-1}$ | Note 1                  |

Note 1: Two's complement allows one more negative number than positive. The overflow port detects that singular instance and goes high to indicate that no positive equivalent exists.

### **1.3.5.2** Properties

| Property  | Usage    | Value         | Comments                          |

|-----------|----------|---------------|-----------------------------------|

| LPM_Width | Required | LPM Value > 1 | Width of input and output vectors |

#### 1.3.5.3 Function

# if Data = $-2^{\text{LPM}_{\text{Width}-1}}$ , then Overflow = 1, Result = UNDEFINED

### else if Data < 0, then Result = (0 - Data)

#### else Result = Data

**Data** must always represent a SIGNED number and may be positive or negative. **Result** will always be positive.

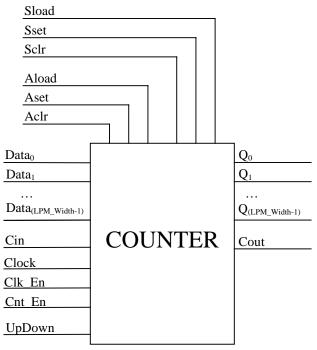

### 1.3.6 LPM\_COUNTER

#### 1.3.6.1 Ports

| 1.5.0.1 10 | 1 65 |             |                                                                              |                         |

|------------|------|-------------|------------------------------------------------------------------------------|-------------------------|

| Port Name  | Туре | Usage       | Description                                                                  | Comments                |

| Data       | Ι    | Optional    | Parallel Data load for the counter                                           | Vector, LPM_Width wide  |

|            |      | -           |                                                                              | Uses Aload and/or Sload |

| Clock      | Ι    | Required    | Positive Edge Triggered                                                      |                         |

| Clk_En     | Ι    | Optional    | Enable all synchronous activities                                            | Default is enabled (1)  |

| Cnt_En     | Ι    | Optional    | Disables count when low (0)                                                  | Default is enabled (1)  |

|            |      |             | (without affecting Sload, Sset,<br>Sclr)                                     |                         |

| Cin        | Ι    | Optional    | Carry in                                                                     |                         |

| UpDown     | Ι    | Note 1      | Controls direction of count                                                  | Default is Up (1)       |

|            |      |             | High = 1 = count up                                                          |                         |

|            |      |             | Low = 0 = count down                                                         |                         |

| Cout       | 0    | Optional    | Carry out port                                                               | Note 3                  |

| Q          | 0    | Note 2      | Count output.                                                                | Vector, LPM_Width wide  |

| Sload      | Ι    | 1           | Load the counter with Data on the next clock.                                | Note 4                  |

| Sset       | Ι    | -           | Set counter value to all 1's or to<br>the value of LPM_Svalue, if<br>present | Note 5, Note 6          |

| Sclr       | Ι    |             | Clear the counter (set to all 0's)                                           | Note 6                  |

| Aload      | I    | 1           | Load the counter with Data.                                                  | Note 4                  |

|            | -    | - Prioritai |                                                                              |                         |

| Port Name | Туре | Usage    | Description                                                             | Comments       |

|-----------|------|----------|-------------------------------------------------------------------------|----------------|

| Aset      | Ι    | 1        | Set counter value to all 1's or to the value of LPM_Avalue, if present. | Note 5, Note 6 |

| Aclr      | Ι    | Optional | Clear the counter (set to all 0's)                                      | Note 6         |

Note 1: If the LPM\_Direction property is used, then the **UpDown** port cannot be connected. If the LPM\_Direction property is not used, then the **UpDown** port is optional.

Note 2: Either **Q** or **Cout** ports must be connected.

- Note 3: Since the counter goes through C counts where  $0 \le C < Modulus$ . Modulus is either the value specified by LPM\_Modulus if present, or  $2^{LPM_Width}$ . The **Cout** ports are optional and generally will be LPM\_Modulus-1 which is the terminal count.

- Note 4: If Aload and/or Sload are used, then the Data port must be connected.

- Note 5: **Sset** and **Aset** will set the count to the value of LPM\_Svalue or LPM\_Avalue respectively, if those values are present. If no LPM\_Svalue is specified, then **Sset** will set the count to all ones, likewise **Aset**.

- Note 6: For outputs such as **Q** and **Cout** on the LPM\_COUNTER, Aset, Aclr, Sset and Sclr affect the output **before** polarity is applied.

| Property      | Usage    | Value           | Comments                                                                                                                   |

|---------------|----------|-----------------|----------------------------------------------------------------------------------------------------------------------------|

| LPM_Width     | Required | LPM Value > 0   | Width of input and output vectors. If<br>no output vectors are specified, then<br>this is the number of bits in the count. |

| LPM_Modulus   | Optional | LPM Value $> 0$ | The maximum count. plus one                                                                                                |

| LPM_Direction | Optional | UP   DOWN       | Note 1                                                                                                                     |

| LPM_Avalue    | Optional | LPM Value       | Loaded when Aset is active (1) Note 2                                                                                      |

| LPM_Svalue    | Optional | LPM Value       | Loaded when Sset is active (1) Note 2                                                                                      |

| LPM_Pvalue    | Optional | LPM Value       | Loaded at power on. Note 2                                                                                                 |

#### **1.3.6.2** Properties

Note 1: If the LPM\_Direction property is used, then the **UpDown** port cannot be connected. This property allows implementation of a Down counter as the default when the **UpDown** port is not connected.

Note 2: If the value specified is larger than the Modulus, then the behavior of the counter is UNDEFINED. The Modulus is the LPM\_Modulus, if present, or else  $2^{\text{LPM}_{Width}}$ .

The LPM\_Counter defaults to an unsigned binary counter. The LPM\_Hint property can be used to suggest an implementation style other than unsigned binary.

It is suggested, but not required, that all of the following styles be supported in the fitting tool and in simulation.

| Unsigned binary    | Signed Binary | BCD  |

|--------------------|---------------|------|

| standard Gray Code | Johnson       | LFSR |

| 1.5.0.5 | Funcue | 0115       |        |        |      |                     |

|---------|--------|------------|--------|--------|------|---------------------|

| Aclr    | Sclr   | Clock      | Cnt_En | Clk_En | Up-  | Output              |

| Aset    | Sset   |            |        |        | Down |                     |

| Aload   | Sload  |            |        |        |      |                     |

| Н       | L      | X          | X      | Х      | Х    | Asynchronous value. |

|         |        |            |        |        |      | Note 1              |

| L       | Н      | $\uparrow$ | Х      | Н      | Х    | Synchronous value   |

|         |        |            |        |        |      | Note 2              |

| L       | Н      | $\uparrow$ | Х      | L      | Х    | No change           |

| Н       | Н      | Х          | Х      | Х      | Х    | UNDEFINED           |

| L       | L      | $\uparrow$ | Н      | L      | Х    | No change           |

| L       | L      | $\uparrow$ | Н      | Н      | Η    | Previous output + 1 |

| L       | L      | $\uparrow$ | Н      | Н      | L    | Previous output – 1 |

| L       | L      | $\uparrow$ | Н      | Н      | U    | Note 3              |

#### 1.3.6.3 Functions

Note 1: The asynchronous value is determined by which asynchronous port is high: Aclr, Aset or Aload. If Aclr and Aset are both high, then the output is UNDEFINED. Aclr or Aset takes priority over Aload. Asynchronous controls have priority over synchronous controls. If the LPM\_Avalue property is defined, then the Aset port, when active, will set the count to the value of the LPM\_Avalue..

- Note 2: The synchronous value is determined by which synchronous port is high: Sclr, Sset or Sload. If more then one synchronous port is high, then Sclr takes priority over Sset which takes priority over Sload. Asynchronous controls have priority over synchronous controls. If the LPM\_Svalue property is defined, then the Sset port, when active, will set the count to the value of the LPM\_Svalue..

- Note 3: If the **UpDown** port is not connected, then the LPM\_Direction property, if present, will determine the direction of the count. The LPM\_Direction property defaults to UP. The **UpDown** and the LPM\_Direction property are mutually exclusive; if one is used, then using the other is an ERROR.

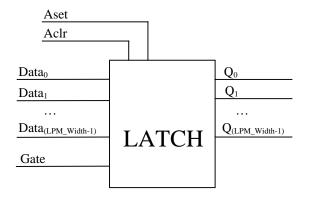

## 1.4 STORAGE COMPONENTS 1.4.1 LPM\_LATCH

D-Type Latch.

#### 1.4.1.1 Ports

| Port Name | Туре | Usage    | Description                                                           | Comments                         |

|-----------|------|----------|-----------------------------------------------------------------------|----------------------------------|

| Data      | Ι    | Optional | Data Input to D-Type Latches                                          | Vector, LPM_Width wide<br>Note 1 |

| Gate      | Ι    | Required | Latch enable input<br>High (1) = flow through<br>Low (0) = latch      |                                  |

| Q         | 0    | Required | Data output from D-type latches                                       | Vector, LPM_Width wide           |

| Aset      | Ι    | -        | Set latch value to all 1's or to the value of LPM_Avalue, if present. | Note 2, Note 3                   |

| Aclr      | Ι    | Optional | Clear the latch (set to all 0's)                                      | Note 3                           |

Note 1: If the **Data** input is not used, then either **Aset** or **Aclr** must be used.

Note 2: Aset will set the count to the value of LPM\_Avalue, if that value is present. If no LPM\_Avalue is specified, then Aset will set the count to all ones.

Note 3: Aset and Aclr affect the output  $(Q_i)$  values before the application of polarity to the ports.

| 1.4.1.2 | Properties |

|---------|------------|

|         |            |

| Property       | Usage    | Value         | Comments                          |

|----------------|----------|---------------|-----------------------------------|

| LPM_Width      | Required | LPM Value > 0 | Width of input and output vectors |

| LPM_Avalu<br>e | Optional | LPM Value     | Value loaded by Aset              |

| LPM_Pvalue     | Optional | LPM Value     | Value loaded at power-on          |

## 1.4.1.3 Functions

| Aclr<br>Aset | Gate | Output                              |

|--------------|------|-------------------------------------|

| Н            | Х    | Asynchronous value.<br>Note 1       |

|              |      | Note 1                              |

| L            | L    | Latch holds current value (latched) |

| L            | Н    | Latch is transparent (flow-through) |

Note 1: The asynchronous value is determined by which asynchronous port is high: Aclr or Aset. If both asynchronous ports are high, then the output is UNDEFINED. If the LPM\_Avalue property is defined, then the Aset port, when active, will set the count to the value of the LPM\_Avalue.

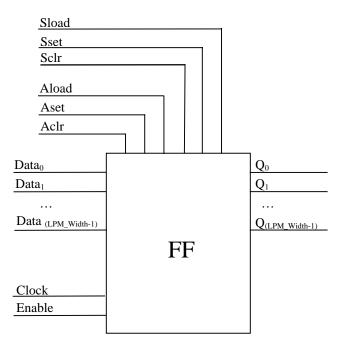

## 1.4.2 LPM\_FF

Flip-flop: D type or Toggle

## 1.4.2.1 Ports

| 1.4.4.1 10 |      |          |                                                                                       | 1                      |  |  |

|------------|------|----------|---------------------------------------------------------------------------------------|------------------------|--|--|

| Port Name  | Туре | Usage    | Description                                                                           | Comments               |  |  |

| Data       | Ι    | Required | TFF: Toggle enable                                                                    | Vector, LPM_Width wide |  |  |

|            |      |          | DFF: Data input                                                                       |                        |  |  |

|            |      |          | Data input during <b>Aload</b> or <b>Sload</b>                                        |                        |  |  |

| Clock      | Ι    | Required | Positive Edge Triggered                                                               |                        |  |  |

| Enable     | Ι    | Optional | Enable all synchronous activities                                                     | Default is enabled (1) |  |  |

| Q          | 0    | Required | Output of Flip-flops                                                                  | Vector, LPM_Width wide |  |  |

| Sload      | Ι    |          | TFF only: Load the Flip-flops with                                                    | Note 2, Note 4         |  |  |

|            |      |          | <b>Data</b> on the next clock.                                                        |                        |  |  |

| Sset       | Ι    |          | Set Flip-flops to all 1's or to the value of LPM_Svalue, if present                   | Note 3, Note 4         |  |  |

| Sclr       | Ι    | Optional | Clear the Flip-flops (set to all 0's)                                                 | Note 4                 |  |  |

| Aload      | Ι    | Note 1   | TFF only: Load the Flip-flops with                                                    | Note 4                 |  |  |

|            |      |          | Data.                                                                                 |                        |  |  |

| Aset       | Ι    | 1        | Set Flip-flops to all 1's or to the<br>value of LPM_Avalue, if present.Note 3, Note 4 |                        |  |  |

| Aclr       | Ι    | Optional | Clear the Flip-flops (set to all 0's) Note 4                                          |                        |  |  |

Note 1: Aload and Sload are only applicable when LPM \_FFType is TFF. If the LPM\_FFType is DFF and these ports are connected, it is an ERROR.

Note 2: Synchronous load of LPM\_TFF. For load operation **Sload** must be high (1) and **Enable** (the clock enable) must be High or unconnected.

- Note 3: **Sset** and **Aset** will set the Flip-flops to the value of LPM\_Svalue or LPM\_Avalue repectively, if those values are present. If no LPM\_Svalue is specified, then **Sset** will set the Flip-flops to all ones, likewise **Aset**.

- Note 4: For outputs such as Q<sub>i</sub> on the LPM\_FF, Aload, Aset, Aclr, Sload, Sset and Sclr affect the output before polarity is applied.

| Property   | Usage    | Value         | Comments                          |

|------------|----------|---------------|-----------------------------------|

| LPM_Width  | Required | LPM Value > 0 | Width of input and output vectors |

| LPM_Avalue | Optional | LPM Value     | Value loaded by Aset              |

| LPM_Svalue | Optional | LPM Value     | Value loaded by <b>Sset</b>       |

| LPM_Pvalue | Optional | LPM Value     | Value loaded at power-on          |

| LPM_FFType | Optional | DFF   TFF     | Default is DFF                    |

#### 1.4.2.2 Properties

#### 1.4.2.3 Functions

| Aclr  | Sclr  | Clock      | Enable | Output                                                                   |

|-------|-------|------------|--------|--------------------------------------------------------------------------|

| Aset  | Sset  |            |        |                                                                          |

| Aload | Sload |            |        |                                                                          |

| Н     | Х     | Х          | Х      | Asynchronous value.                                                      |

|       |       |            |        | Note 1                                                                   |

| L     | Н     | $\uparrow$ | Н      | Synchronous value                                                        |

|       |       |            |        | Note 2                                                                   |

| L     | Н     | $\uparrow$ | L      | No change                                                                |

| L     | L     | $\uparrow$ | L      | No change (clock not enabled)                                            |

| L     | L     | $\uparrow$ | Н      | TFF: FF <sub>i</sub> is toggled if <b>Data</b> <sub>i</sub> is high (1). |

|       |       |            |        | DFF: Data is loaded into the register                                    |

- Note 1: The asynchronous value is determined by which asynchronous port is high: Aclr, Aset or Aload. If Aclr and Aset are both high, then the output is UNDEFINED. Aclr or Aset takes priority over Aload. Asynchronous controls have priority over synchronous controls. If the LPM\_Avalue property is defined, then the Aset port, when active, will set the FFs to the value of the LPM\_Avalue. Aload is not permitted when the LPM FFType is DFF.

- Note 2: The synchronous value is determined by which synchronous port is high: Sclr, Sset or Sload. If more then one synchronous port is high, then Sclr takes priority over Sset which takes priority over Sload. Asynchronous controls have priority over synchronous controls. If the LPM\_Svalue property is defined, then the Sset port, when active, will set the FFs to the value of the LPM\_Svalue. Sload is not permitted when the LPM\_FFType is DFF.

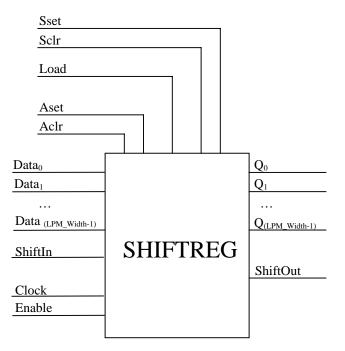

Universal Shift Register

## 1.4.3.1 Ports

| Port Name | Туре | Usage    | Description                                                              | Comments                   |

|-----------|------|----------|--------------------------------------------------------------------------|----------------------------|

| Data      | Ι    |          | Data for parallel load of shift register                                 | Vector, LPM_Width wide     |

| Clock     | Ι    | Required | Clock, positive edge triggered                                           |                            |

| Enable    | Ι    | Optional | Clock enable input                                                       | Default is enabled (High)  |

| ShiftIn   | Ι    | Note 1   | Input for serial data during shift                                       |                            |

| Load      | Ι    | Optional | High (1): Load operation                                                 | Default is low (0) - shift |

|           |      |          | Low (0): Shift operation                                                 | operation. Note 2.         |

| Q         | 0    | Note 3   | Output for parallel data                                                 | Vector, LPM_Width wide     |

| ShiftOut  | 0    | Note 3   | Output for serial data during shift                                      |                            |

| Aset      | Ι    |          | Set register value to all 1's or to the value of LPM_Avalue, if present. | Note 4, Note 5             |

| Aclr      | Ι    | Note 1   | Clear the register (set to all 0's)                                      | Note 5                     |

| Sset      | Ι    |          | Set register value to all 1's or to the value of LPM_Svalue, if present  | Note 4, Note 5             |

| Sclr      | Ι    | Note 1   | Clear the register (set to all 0's)                                      | Note 5                     |

- Note 1: At least one of **Data**, Aset, Aclr, Sset, Sclr and/or ShiftIn must be used.

- Note 2: Synchronous parallel load. For parallel load operation **Load** must be high (1) and **Enable** (the clock enable) must be High or unconnected.

- Note 3: Either **ShiftOut** or **Q** or both must be used.

- Note 4: **Sset** and **Aset** will set the count to the value of LPM\_Svalue or LPM\_Avalue respectively, if those values are present. If no LPM\_Svalue is specified, then **Sset** will set the count to all ones, likewise **Aset**.

- Note 5: Sset, Sclr, Aset and Aclr affect the output  $(Q_i)$  values before the application of polarity to the ports.

| 1.4.3.2 | <b>Properties</b> |

|---------|-------------------|

|---------|-------------------|

| Property      | Usage    | Value         | Comments                          |

|---------------|----------|---------------|-----------------------------------|

| LPM_Width     | Required | LPM Value > 0 | Width of input and output vectors |

| LPM_Avalue    | Optional | LPM Value     | Value loaded by Aset              |

| LPM_Svalue    | Optional | LPM Value     | Value loaded by <b>Sset</b>       |

| LPM_Pvalue    | Optional | LPM Value     | Value loaded at power-on          |

| LPM_Direction | Optional | LEFT RIGHT    | Default is LEFT. Note 1.          |

Note 1: A left shift implies that the data is being shifted into the LSB and out the MSB. The LSB gets the value on the **ShiftIn** port. The **ShiftOut** port is always equal to  $Q_{LPM_Width-1}$ .

| Aclr | Sclr | Clock      | Enable | Load | Output                                |

|------|------|------------|--------|------|---------------------------------------|

| Aset | Sset |            |        |      |                                       |

| Н    | Х    | Х          | Х      | Х    | Asynchronous value.                   |

|      |      |            |        |      | Note 1                                |

| L    | Н    | $\uparrow$ | Н      | Х    | Synchronous value                     |

|      |      |            |        |      | Note 2                                |

| L    | Н    | $\uparrow$ | L      | Х    | No change (clock not enabled)         |

| L    | L    | $\uparrow$ | L      | Х    | No change (clock not enabled)         |

| L    | L    | $\uparrow$ | Н      | L    | Parallel load Register from Data      |

| L    | L    | $\uparrow$ | Н      | Н    | $Q_i$ is shifted into $Q_{i+1}$       |

|      |      |            |        |      | ShiftIn is loaded into Q <sub>0</sub> |

- Note 1: The asynchronous value is determined by which asynchronous port is high: Aclr or Aset. If Aclr and Aset are both high, then the output is UNDEFINED. Asynchronous controls have priority over synchronous controls. If the LPM\_Avalue property is defined, then the Aset port, when active, will set the FFs to the value of the LPM\_Avalue.

- Note 2: The synchronous value is determined by which synchronous port is high: Sclr or Sset. If more then one synchronous port is high, then Sclr takes priority over Sset. Asynchronous controls have priority over synchronous controls. If the LPM\_Svalue property is defined, then the Sset port, when active, will set the Q to the value of the LPM\_Svalue.

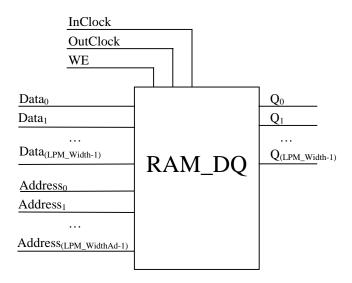

## 1.4.4 LPM\_RAM\_DQ

Memory with separate input and output ports.

#### 1.4.4.1 Ports

| 1         |      |          |                                                                        |                          |

|-----------|------|----------|------------------------------------------------------------------------|--------------------------|

| Port Name | Туре | Usage    | Description                                                            | Comments                 |

| Data      | Ι    | Required | Data input to memory                                                   | Vector, LPM_Width wide   |

| Address   | Ι    | Required | Address of memory location                                             | Vector, LPM_WidthAd wide |

| Q         | 0    | Required | Output of memory                                                       | Vector, LPM_Width wide   |

| InClock   | Ι    | Optional | Clock for read operation                                               | Note 1                   |

| OutClock  | Ι    | Optional | Clock for write operation                                              | Note 2                   |

| WE        | Ι    |          | Write enable control. Enables<br>write to the memory when high<br>(1). | Note 3                   |

- Note 1: If the **InClock** port is used, then the **WE** port acts as an enable for write operations synchronized to the positive going edge of the signal on the **InClock** port. If the **InClock** ports is not used, then the **WE** port acts as an enable for write operations asynchronously.

- Note 2: The addressed memory content  $\rightarrow \mathbf{Q}$  response is synchronous when the **OutClock** port is connected. and asynchronous when it is not connected.

- Note 3: If only **WE** is used, the data on the **Address** port should not change while **WE** is active (high, 1). If the data on the **Address** port changes while **WE** is high (1), then all memory locations that are addressed are over-written with **Data**.

| Property            | Usage    | Value                        | Comments                                                                              |

|---------------------|----------|------------------------------|---------------------------------------------------------------------------------------|

| LPM_Width           | Required | LPM Value > 0                | Width of input and output vectors.                                                    |

| LPM_WidthAd         | Required | LPM Value > 0                | Width of Address Port. Note 1.                                                        |

| LPM_NumWords        | Optional | LPM Value > 0                | Number of words stored in Memory.<br>Note 2.                                          |

| LPM_InData          | Optional | REGISTERED  <br>UNREGISTERED | Indicates if <b>Data</b> port is registered.<br>Default is REGISTERED                 |

| LPM_Address_Control | Optional | REGISTERED  <br>UNREGISTERED | Indicates if <b>Address</b> and <b>WE</b> ports are registered. Default is REGISTERED |

| LPM_OutData         | Optional | REGISTERED  <br>UNREGISTERED | Indicates if <b>Q</b> port is registered.<br>Default is REGISTERED                    |

| LPM_File            | Optional | File Name                    | File for RAM initialization.                                                          |

#### 1.4.4.2 Properties

Note 1: The LPM\_WidthAd should be (but is not required to be) equal to:

$\lceil \log_2(LPM\_NumWords) \rceil$ . If LPM\_WidthAd is too small, some memory locations will not be addressable. If it is too big, then the addresses that are too high will return UNDEFINED.

Note 2: If LPM\_NumWords is not used, then it defaults to  $2^{\text{LPM}_WidthAd}$ . In general, this value should be (but is not required to be):  $2^{\text{LPM}_WidthAd-1} < \text{LPM}_NumWords \le 2^{\text{LPM}_WidthAd}$ .

## 1.4.4.3 Functions

Random Access Memory. This module can represent asynchronous memory or memory with synchronous inputs and/or outputs.

| Synchro<br>nous<br>Write to<br>memoryI<br>nClock | WE | Memory Contents                                                                                            |

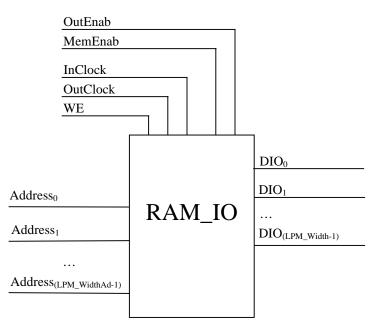

|--------------------------------------------------|----|------------------------------------------------------------------------------------------------------------|