# DESIGN AND VERIFICATION OF WISHBONE BUS INTERFACE FOR SOC INTEGRATION

A thesis submitted in partial fulfilment of the requirements for the degree of

Master of Technology (Research)

in

Electronics & Communication Engineering

Ву

Ayas Kanta Swain

Roll No: 60609001

Under the supervision of

Dr. KamalaKanta Mahapatra Professor

Department of Electronics & Communication Engineering

National Institute of Technology, Rourkela, Orissa

January 2010

# Dedicated to my family

# Department of Electronics & Communication Engineering NATIONAL INSTITUTE OF TECHNOLOGY, ROURKELA ORISSA, INDIA – 769 008

#### CERTIFICATE

This is to certify that the thesis titled "**Design and Verification of WISHBONE Bus Interface for SOC Integration**" submitted to the National Institute of Technology, Rourkela by **Ayas Kanta Swain**, Roll No. **60609001** for the award of the degree of **Master of Technology (Research)** in Electronics & Communication Engineering, is a bonafide record of research work carried out by him under my supervision and guidance.

The candidate has fulfilled all the prescribed requirements.

The thesis, which is based on candidate's own work, has not been submitted elsewhere for a degree/diploma.

In my opinion, the thesis is of standard required for the award of a Master of Technology (Research) degree in Electronics & Communication Engineering.

To the best of my knowledge, he bears a good moral character and decent behaviour.

> Prof. K. K. Mahapatra Professor

Department of Electronics & Communication Engineering

NATIONAL INSTITUTE OF TECHNOLOGY

Rourkela-769 008 (INDIA) Email: kkm@nitrkl.ac.in

#### **ACKNOWLEDGEMENT**

I would like to take this opportunity to extend my deepest gratitude to my teacher and supervisor, Prof. K. K. Mahapatra, for his continuous encouragement and active guidance. I am indebted to him for the valuable time he has spared for me during this work. He is always there to meet and talk about my ideas and he is great moral support behind me in carrying out my research work.

I am very much thankful to Prof. S. K. Patra, HOD, ECE Department for his continuous encouragement. I am grateful to Prof. G.S.Rath, Prof.S.Meher, Prof.T.K.Dan and Dr.D.P.Acharya, Prof. S.K.Behera, Prof. Ajit Sahoo and Prof.B.D.Sahoo for valuable suggestions and comments during this research period.

In addition, I am grateful to Prof. A. Routray and Prof. B.S. Das, IIT Kharagpur for giving me an opportunity to work with them; this introduced me to the area of research and development.

I am grateful to www.opencores.org for their technical support during the complete project period.

I need to thank my friends especially Saroj, who stands with me in all my endeavours. And also I am thankful to him for making my thesis more representable.

In addition, let me thank all my friends Jitendra sir, Sushant, Sudeendra, Trillochan, Sanatan, Devi, Prasanta, Karuppanan, Deepak, Arun, Tom, Soumya, Jagannath and Peter for their great support and encouragement during the research period. Also, I am thankful to all the non-teaching staffs of ECE Department for their kind cooperation.

I would like to thank Department of Information Technology, Govt. of India, for supporting me under SMDP-VLSI project.

Last but not the least; I would like to thank my parents, brother and sister for their unconditional support and encouragement to carry out research. I am also thankful to my sister for helping me in typing the part of my thesis.

Ayas Kanta Swain

#### **BIO-DATA**

Name of the Candidate : Ayas Kanta Swain

Father's Name : Kulamani Swain

Permanent Address : S/o. Kulamani Swain

F-17, Sector-7

Rourkela-3

Date of Birth : 26<sup>th</sup> August 1979

Email ID : swain.ayas@gmail.com

#### ACADEMIC QUALIFICATION

• Continuing M. Tech (Research) in Dept. of Electronics and Communication Engineering, National Institute of Technology Rourkela, Orissa (INDIA).

• B. E. (Hons.) (Electrical Engineering), IGIT, Sarang, Utkal University, Orissa

#### **EXPERIENCE**

- Working as a Contractual Faculty, in Project "Special Man Power Development Project for VLSI Design and its Related Software" funded by DIT under MCIT, Delhi.

- Worked as a Research Engineer in DST Sponsored Project in Dept. of AG&FE. & Dept. of Electrical Engg., IIT Kharagpur

- Worked as a Guest Faculty at Dept. Elect. Engg.,IGIT Sarang, Dhenkanal, Orissa.

#### **PUBLICATIONS:**

Published 01 paper in International Conferences;

#### **ABSTRACT**

The rapid development in the field of mobile communication, digital signal processing (DSP) motivated the design engineer to integrate complex systems of multimillion transistors in a single chip. The integration of the transistor in a single chip greatly increases the performance of the system while reduction in system size. Recently, there is a considerable increase in the application front in several areas of engineering and technology. Moore's law states that integration density gets doubled every two years, so the complexity of the integrated circuits also increases by keeping the used chip area constant. In order to keep pace with the levels of integration available, design engineers have developed new methodologies and techniques to manage the increased complexity in these large chips.

System-on-Chip (SOC) design is proposed as an extended methodology to this problem where pre-designed and pre-verified IP cores of embedded processors, memory blocks, interface blocks, and analog blocks are combined on a single chip targeting a specific application. These chips may have one or more processors on chip, a large amount of memory, bus-base architectures, peripherals, co processors, and I/O channels. These chips integrates systems far more similar to the boards designed ten years ago that to the chips of even a few years ago. The primary drivers for this are the reduction of power, smaller form factor, and lower overall cost. SOC offers many benefits such as smaller space requirements with higher performance. Design reuse- the use of predesigned and pre-verified cores – is now the cornerstone of SOC design. It uses reusable IP blocks that supports plug and play integration and in turn allows huge chips to be designed at an acceptable cost, and quality.

The benefits SOC design methodology also come with challenges such as: larger design space, higher design and prototype costs. Apart from these challenges, the design again needs an expertise in both hardware and software levels for proper hardware and software co-design. Another important aspect of SOC integration is the development of a proper test methodology for post manufacturing test. All these integration issues makes the design time consuming and also expensive.

To deal with this inherent integration problems and reduction in design cycle time, platform based SoC design was proposed where new designs could be quickly created from the original platform over many design derivatives. More specifically a platform is an abstraction level that covers a number of refinements to a lower level resulting in improvement of the design productivity. In other side, a new concept that is gaining interest is the Open Core SoC design methodology which is based on publishing all necessary information about the hardware. Open Core group has provided many pre-synthesized and pre-verified hardware core for the designer under GPL/LGPL license.

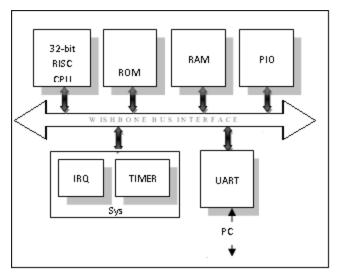

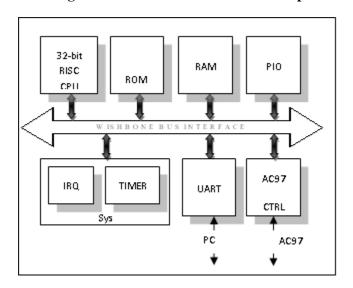

This thesis investigates the Open core based SOC design platform. Open Core uses a standard bus WISHBONE to alleviate System-on-Chip problem. The various issues related to Open Core WISHBONE bus interfaces are presented in this thesis. These include WISHBONE specification, types of interconnections, WISHBONE Bus cycles.etc. A comparison of three bus protocol has been discussed. The issues related to design of a WISHBONE compatible IP core, Point-to-Point interconnection, shared bus interconnection is also presented in this investigation. All the designs are validated by XILINX ISE simulation results and real time debugging signals though ChipScope Pro. A SOC design methodology has been presented for a proposed SOC architecture. Afterwards a SOC architecture of 32-bit RISC CPU, memory, System Controller, UART and PIO has been proposed and the design methodology used to implement the SOC in FPGA has been discussed. The functionality of CPU operation in SOC architecture is verified by simulation results and corresponding steps for FPGA implementation of the SOC architecture with synthesis results have been presented. Finally, application software ha been developed in C and the object file is ported to FPGA system for validation of the SOC functionality of the SOC architecture.

### **Table of Contents:**

|     | List o | of Figures                            | i  |

|-----|--------|---------------------------------------|----|

|     | List o | of Tables                             | v  |

|     | List o | of Abbreviations                      | vi |

| 1.  | Syste  | em on Chip: An Overview               | 1  |

| 1.1 | -      | ept of System-on-Chip                 | 2  |

| 1.2 | Histo  | ry of SOC                             | 4  |

| 1.3 | Desig  | gn Reuse Concept                      | 4  |

|     | 1.3.1  | Design for reuse                      | 5  |

| 1.4 | The s  | ystem on chip design flow and process | 6  |

|     | 1.4.1  | A canonical SOC design                | 6  |

|     | 1.4.2  | System Design Flow                    | 7  |

|     | I.     | Waterfall vs. Spiral                  | 7  |

|     | II.    | Top-down Vs. Bottom up                | 9  |

|     | 1.4.3  | The System Design Process             | 11 |

| 1.5 | Syste  | m level Design Issues                 | 14 |

|     | 1.5.1  | Different Types of IP Cores           | 14 |

|     | I.     | Digital IP                            | 14 |

|     | II.    | AMS IP                                | 15 |

|     | 1.5.2  | System Interconnect and On Chip-Buses | 15 |

|     | 1.5.3  | SOC Test Methodologies                | 15 |

|     | I.     | IP core level test                    | 16 |

|      | II. SOC level test                     | 19 |

|------|----------------------------------------|----|

|      | 1.5.4 SOC Verification                 | 19 |

| 1.6  | Motivation                             | 20 |

| 1.7  | Work Presented in the Thesis           | 21 |

| 1.8  | Thesis Outline                         | 21 |

| 1.8  | Conclusions                            | 22 |

| 2.   | Open Core Based SOC Design Methodology | 23 |

| 2.1  | Platform Based SOC Design              | 24 |

| 2.2  | Open Core Based SOC Design Platform    | 26 |

| 2.3  | The Objective behind WISHBONE          | 26 |

| 2.4  | WISHBONE Basics                        | 27 |

| 2.5  | WISHBONE Interface Specification       | 28 |

|      | 2.5.1 Documentation for IP Cores       | 28 |

|      | 2.5.1 WISHBONE Interface Signal        | 29 |

| 2.6. | Wishbone Interconnections              | 32 |

|      | 2.6.1 Point-to-Point Interconnection   | 32 |

|      | 2.6.2 Data Flow Interconnection        | 33 |

|      | 2.6.3 Share Bus Interconnection        | 33 |

|      | 2.6.4 Cross Bar Switch Interconnection | 34 |

| 2.7  | WISHBONE Bus Cycle                     | 34 |

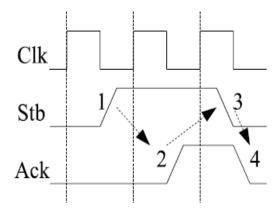

|      | 2.7.1 Handshaking Protocol             | 34 |

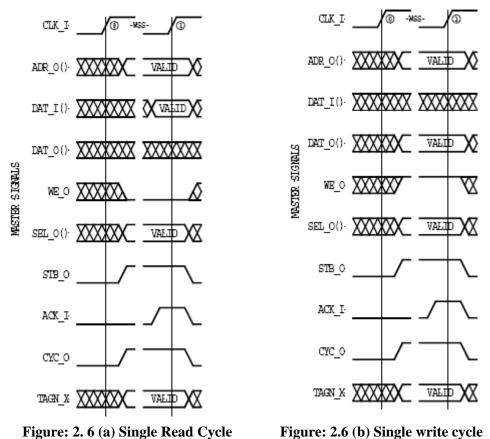

|      | 2.7.2 Single Read/ Write Cycle         | 35 |

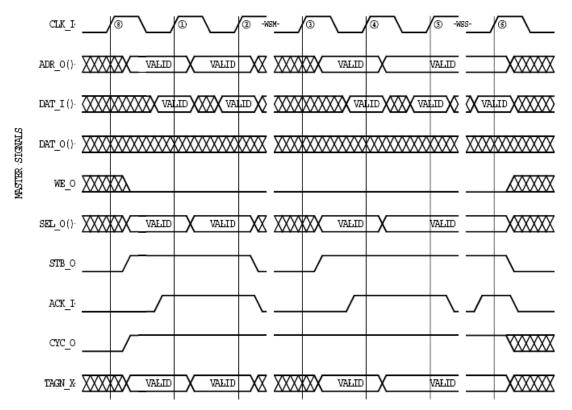

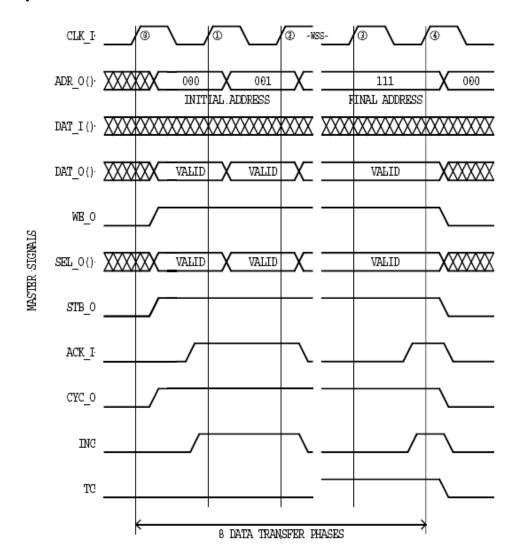

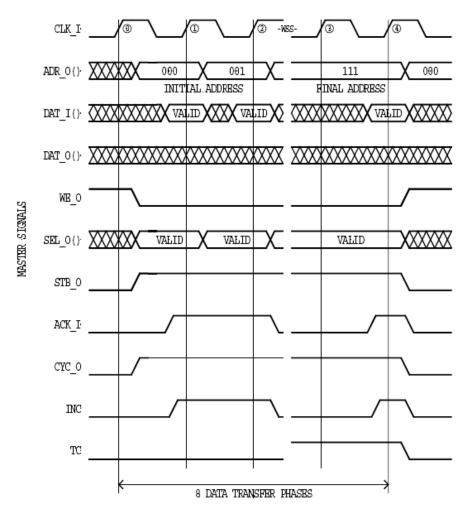

|      | 2.7.3 Block Read/ Write Cycle          | 36 |

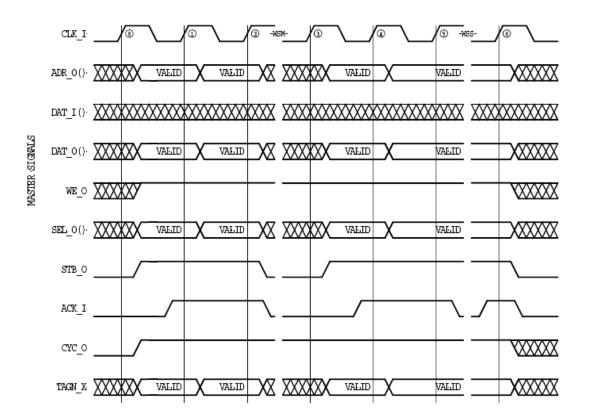

|      | 2.7.4 Read-Modify-Write (RMW) Cycle    | 37 |

| 2.8  | Data Organization and Customized Tag   | 39 |

| 2.9  | WISH    | BONE SOC Bus Comparison with AMBA and CoreConnect      | 39 |

|------|---------|--------------------------------------------------------|----|

| 2.10 | Conclu  | usions                                                 | 41 |

| 3.   | Design  | and verification of WISHBONE Interconnections          | 43 |

| 3.1  | Design  | n of WISHBONE Compatible Slave IP Core                 | 44 |

|      | 3.1.1   | 16-Bit Slave Output Port Design with 8-Bit Granularity | 44 |

|      | 3.1.2   | Simulation Results                                     | 46 |

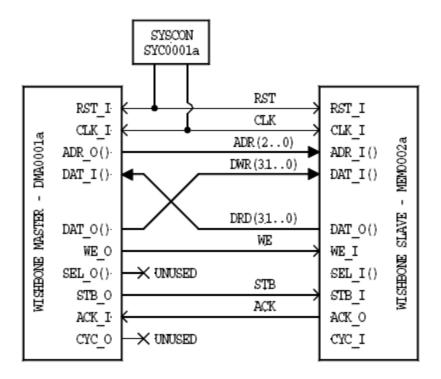

| 3.2  | Point-t | to-Point Interconnection                               | 46 |

|      | 3.2.1   | Core specification and internal architecture           | 47 |

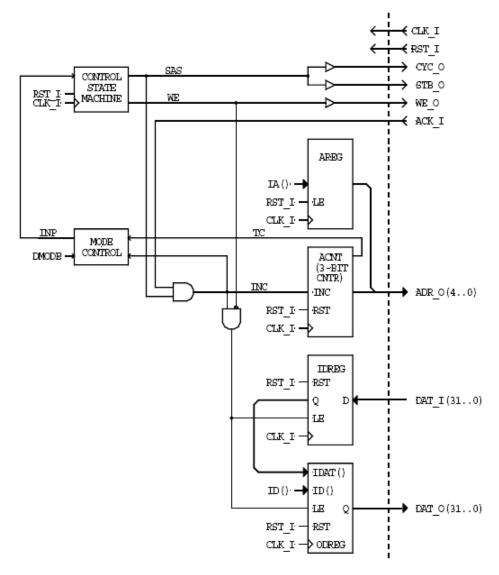

|      | I.      | DMA                                                    | 47 |

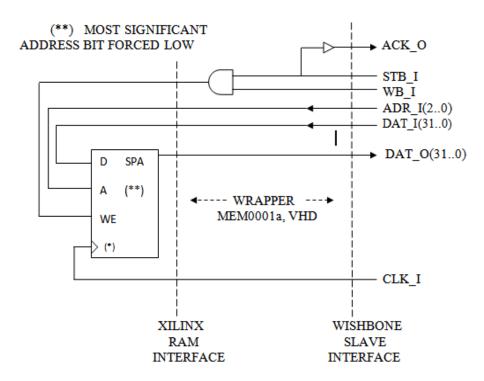

|      | I.      | MEMORY                                                 | 50 |

|      | III.    | SYSCON                                                 | 51 |

|      | 3.2.2   | Interconnection Architecture                           | 52 |

|      | 3.2.3   | Verification Results                                   | 52 |

|      | 3.2.4   | Synthesis Results                                      | 54 |

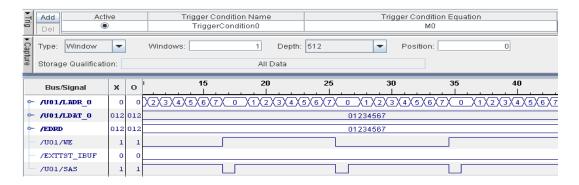

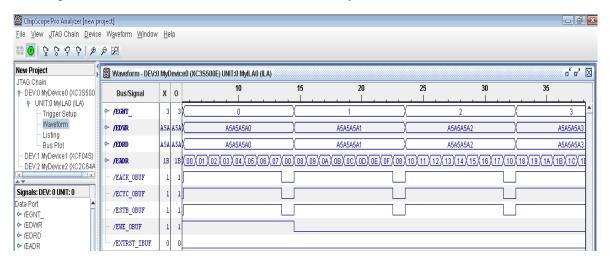

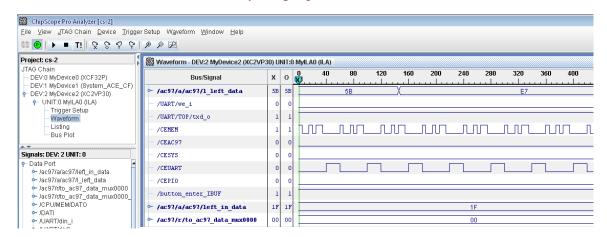

|      | 3.2.5   | ChipScope Pro Result:                                  | 55 |

|      | 3.2.6   | Benchmarking Results                                   | 56 |

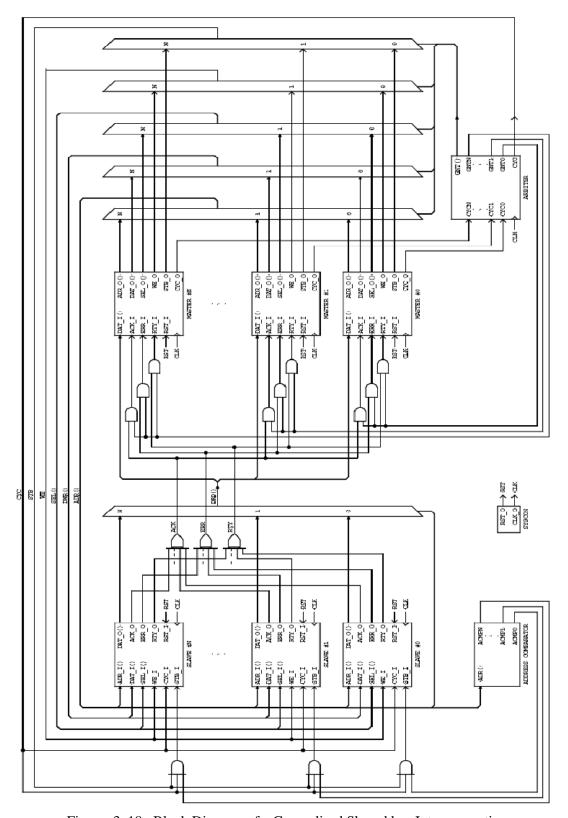

| 3.3. | Shared  | Bus Interconnection                                    | 56 |

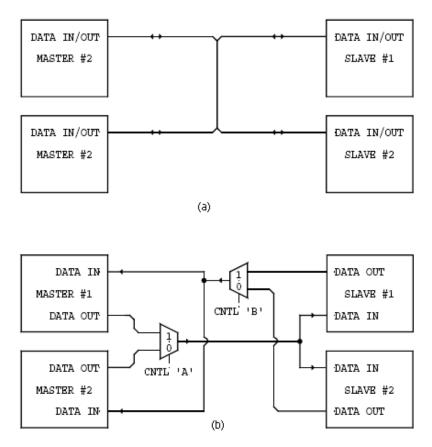

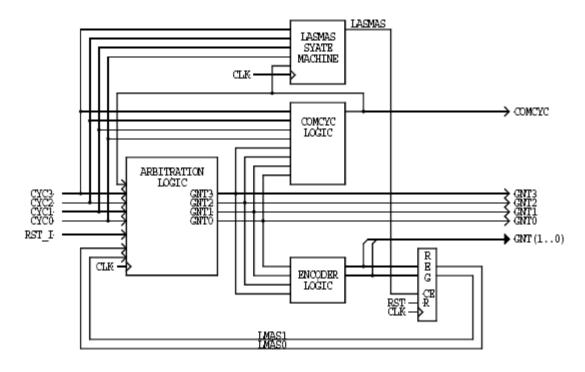

|      | 3.3.1.  | Bus topology                                           | 57 |

|      | 3.3.2.  | Interconnection logic                                  | 58 |

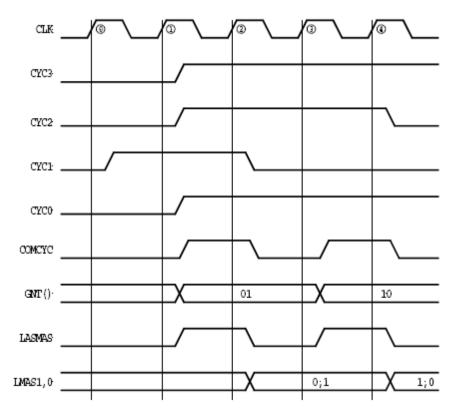

|      | 3.3.3.  | Arbiter Topology                                       | 60 |

|      | 3.3.4.  | Partial address decoding and address map               | 63 |

|      | 3.3.5.  | Interconnection topology                               | 64 |

|      | 3.3.6.  | Verification Results                                   | 67 |

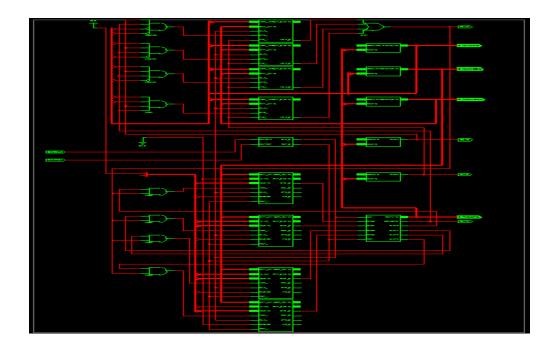

|      | 3.3.7.  | Synthesis Results                                      | 67 |

|      | 3.3.8.  | ChipScope Pro Result                                   | 69 |

|      | 3.3.9. | Benchmarking Results                | 70  |

|------|--------|-------------------------------------|-----|

| 3.4. | Concl  | lusions                             | 71  |

| 4.   | SOC    | Architecture and Design Methodology | 72  |

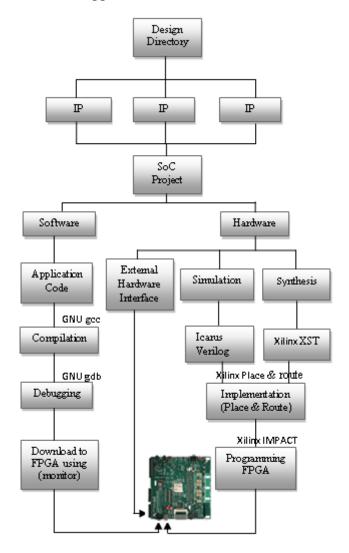

| 4.1  | Propo  | osed SoC Design Methodology         | 73  |

|      | 4.1.1  | Hardware Design Flow                | 73  |

|      | 4.1.2  | Software Design Flow                | 75  |

| 4.2  | Hardv  | ware Gateway of SoC Architecture    | 75  |

| 4.3  | Descr  | iptions of IP Cores                 | 76  |

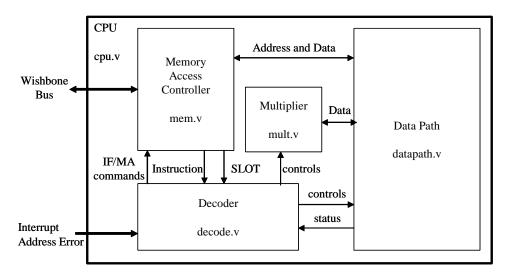

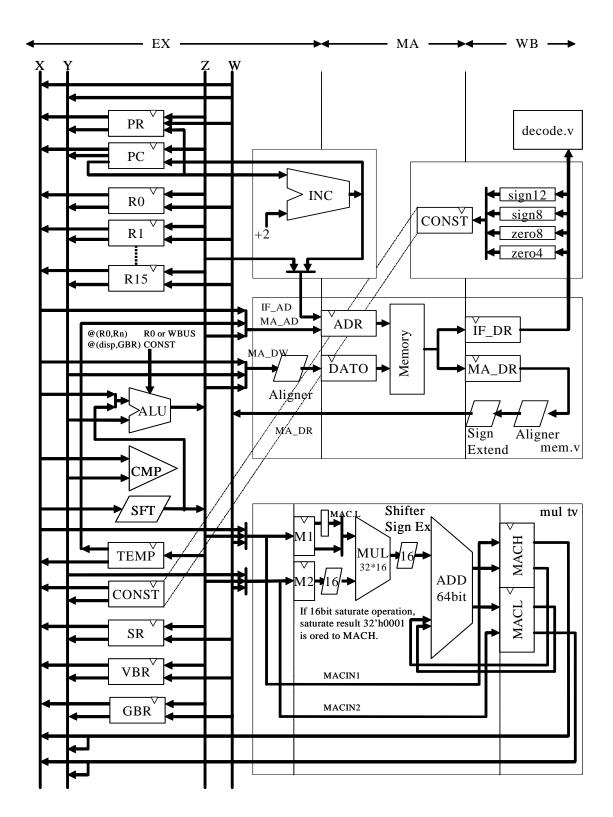

|      | 4.3.1  | CPU                                 | 76  |

|      | I.     | Specification                       | 76  |

|      | II.    | Structure of CPU                    | 76  |

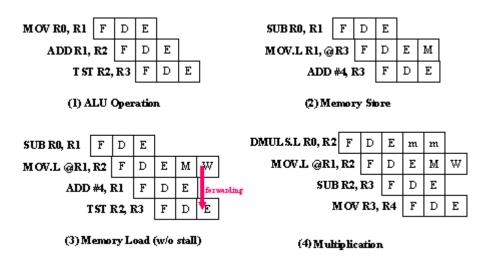

|      | Decod  | der Unit                            | 81  |

|      | Memo   | ory Access Controller Unit          | 86  |

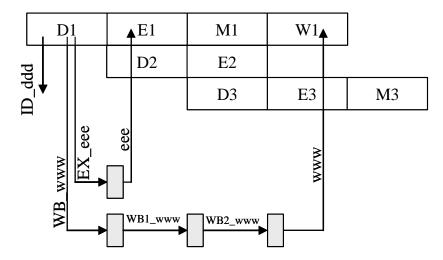

|      | Data I | Path Unit                           | 92  |

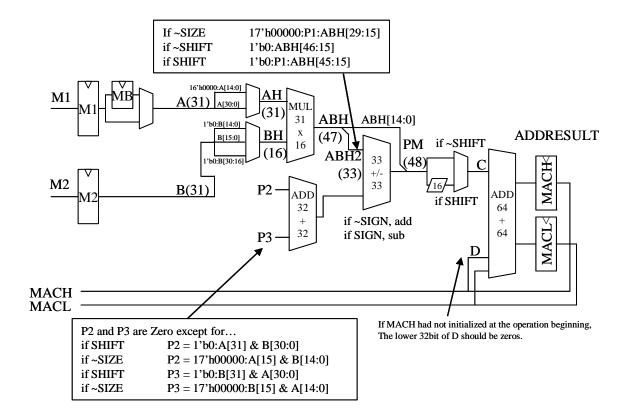

|      | Multij | plier Unit                          | 92  |

|      | 4.3.2  | PIO: Parallel Input and Output      | 94  |

|      | I.     | Specification                       | 94  |

|      | II.    | Structure of PIO                    | 94  |

|      | 4.3.3  | Serial Input Output (UART)          | 96  |

|      | I.     | Specification                       | 96  |

|      | II.    | Structure of PIO                    | 96  |

|      | 4.3.4  | System Controller (SYS)             | 97  |

|      | I.     | Specification                       | 97  |

|      | II.    | Structure of SYS                    | 98  |

|      | 4.3.5  | On chip memory                      | 100 |

|      | I.     | Specification                       | 100 |

|      | II.    | Structure of SYS                    | 100 |

| 4.4 | Concl                        | usions                                                     | 101 |

|-----|------------------------------|------------------------------------------------------------|-----|

| 5.  | SOC                          | Integration, Verification and FPGA Implementation          | 102 |

| 5.1 | Integra                      | ation of IP Cores                                          | 103 |

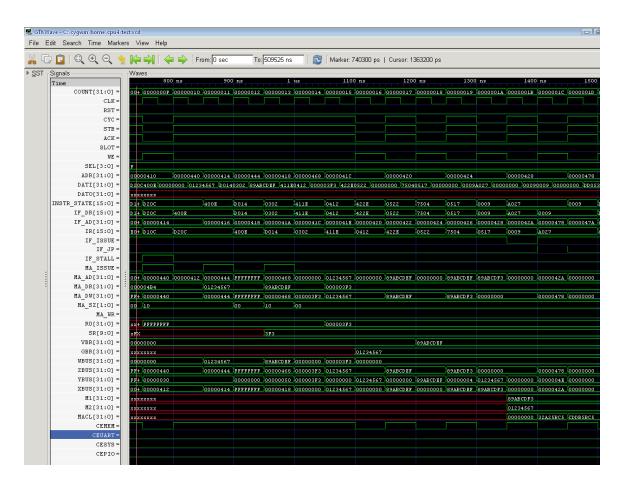

| 5.2 | Verifi                       | cation of SOC                                              | 106 |

|     | 5.2.1                        | Verification Environment                                   | 106 |

|     | 5.2.2                        | Test Bench Development                                     | 106 |

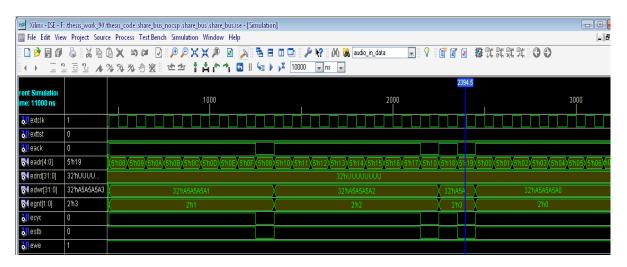

|     | 5.2.3                        | Simulation Results                                         | 108 |

| 5.3 |                              | Synthesis results                                          | 110 |

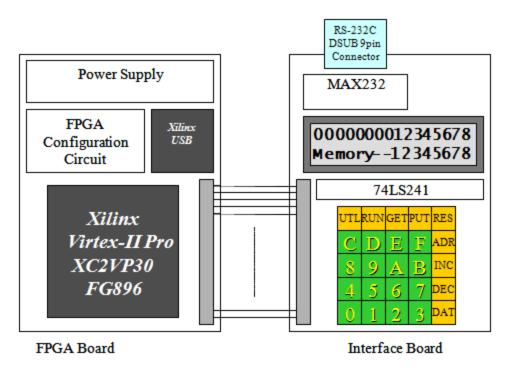

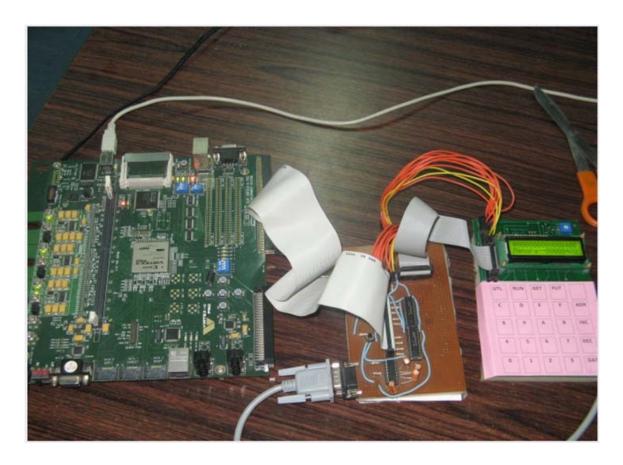

| 5.4 |                              | FPGA Implementation                                        | 112 |

|     | 5.4.1                        | FPGA development tool and board                            | 112 |

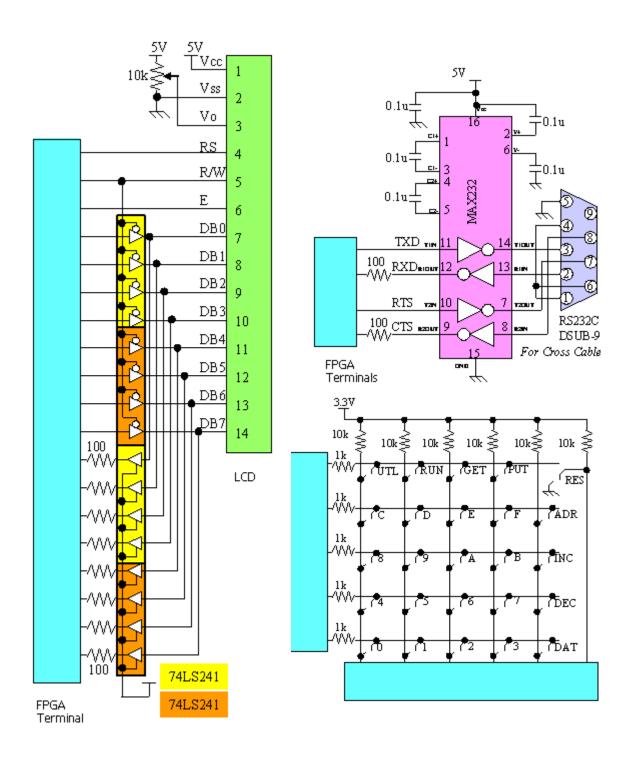

|     | 5.4.2                        | Interface Board Circuit Diagram                            | 112 |

|     | 5.4.3                        | FPGA Configuration                                         | 115 |

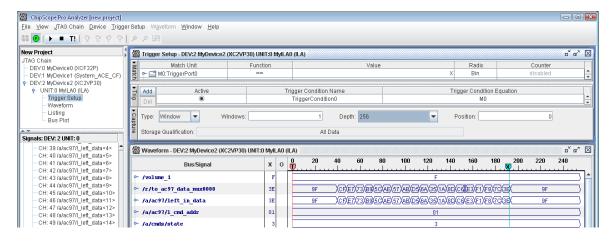

| 5.5 |                              | ChipScope Pro Result                                       | 116 |

| 5.6 |                              | Conclusion                                                 | 116 |

| 6   | Appli                        | cation Development for SOC                                 | 117 |

| 6.1 |                              | Application Programs                                       | 118 |

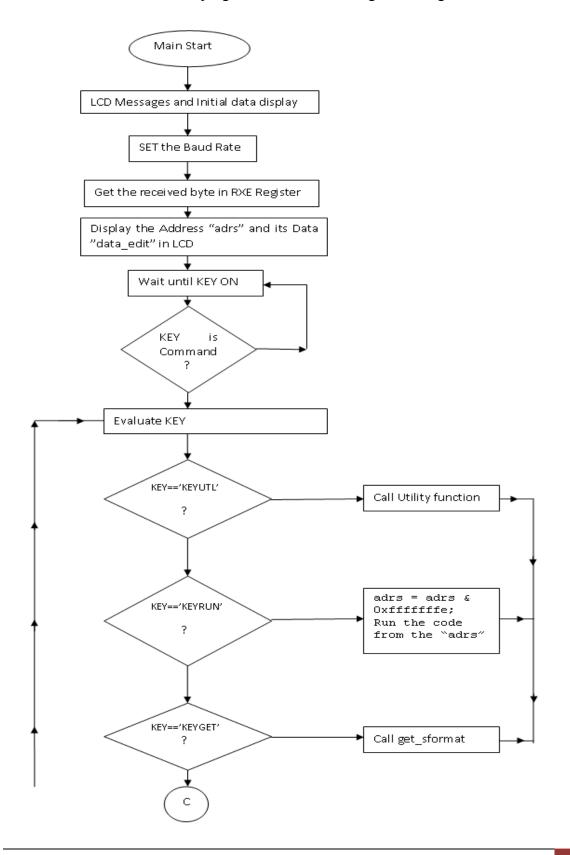

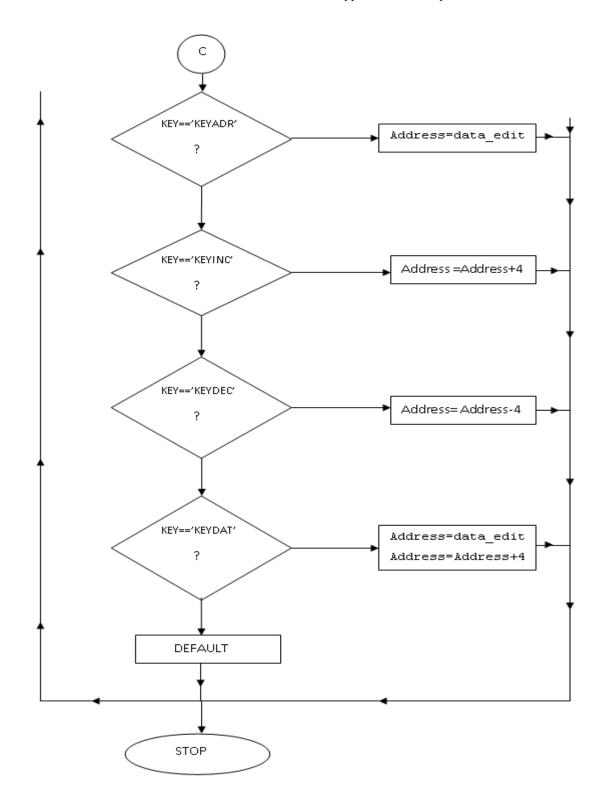

| 6.2 |                              | Monitor Program Application                                | 118 |

|     | 6.2.1                        | Algorithm for monitor program                              | 118 |

|     | 6.2.2                        | How Monitor Program Works                                  | 122 |

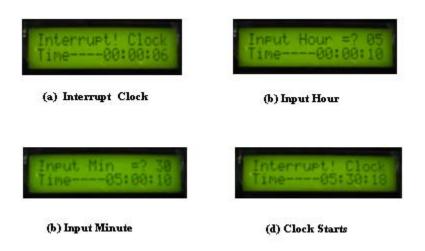

| 6.3 | Digita                       | l Clock Application                                        | 125 |

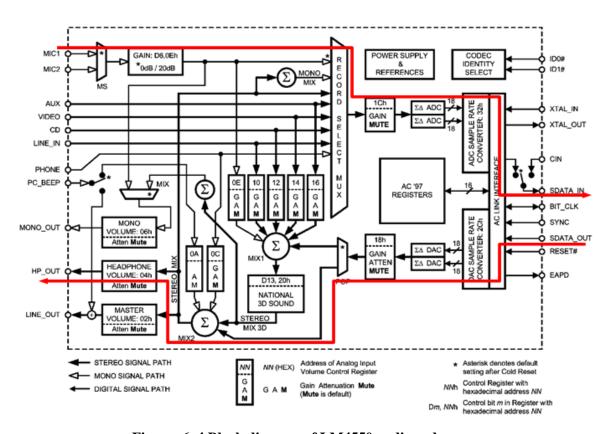

| 6.4 | Audio Processing Application |                                                            | 126 |

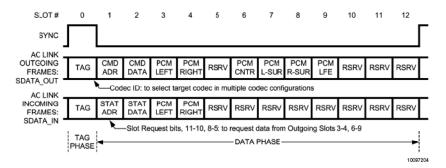

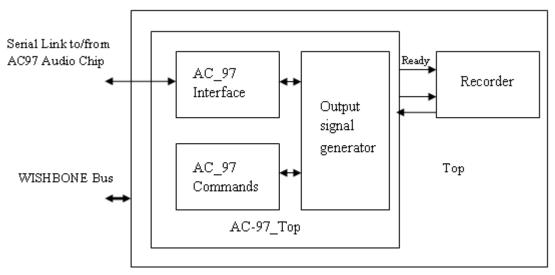

|     | 6.4.1                        | AC97 Codec                                                 | 127 |

|     | 6.4.2<br>Verifi              | Wishbone compatible AC97 Controller core design and cation | 129 |

| 6.5 |                              | Conclusions                                                | 132 |

| 7.  | Concl                        | usions                                                     | 133 |

| 7.1 | Concl                        | usions                                                     | 133 |

| 7.2 | Scope                        | for Future Work                                            | 135 |

|     | References                   |                                                            | 136 |

## List of Figures:

| Figure 1. 1      | Idea of SOC design                                             | 3  |

|------------------|----------------------------------------------------------------|----|

| Figure 1. 2      | A canonical SOC design.                                        | 6  |

| Figure 1. 3      | Water fall design process                                      | 8  |

| Figure 1. 4      | Spiral Design Flow                                             | 10 |

| Figure 1. 5      | Core based SOC Test Architecture                               | 17 |

| Figure 1. 6      | Block Diagram of P1500 Wrapper for BIST DFT Core               | 18 |

| Figure 1.7       | Integration of Cores using P1500 wrapper                       | 19 |

| Figure 2.1       | system                                                         | 27 |

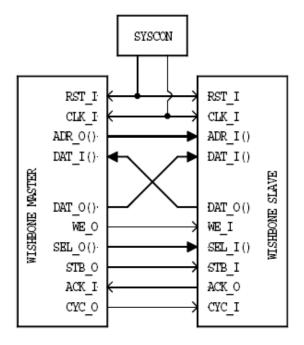

| Figure 2.2       | Point to point interconnection with WISHBONE interface signals | 32 |

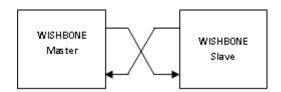

| Figure 2.3(a)    | Point-to-Point<br>Interconnection                              | 32 |

| Figure 2.3(b)    | Data flow Interconnection                                      | 33 |

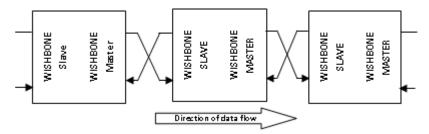

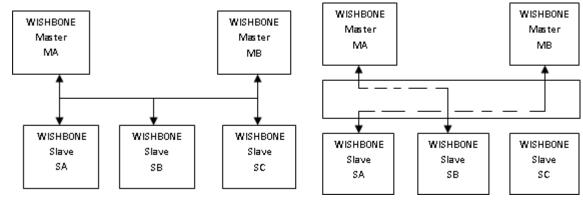

| Figure: 2. 4 (a) | Shared bus interconnection                                     | 33 |

| Figure 2.4 (b)   | Crossbar switch interconnection                                | 33 |

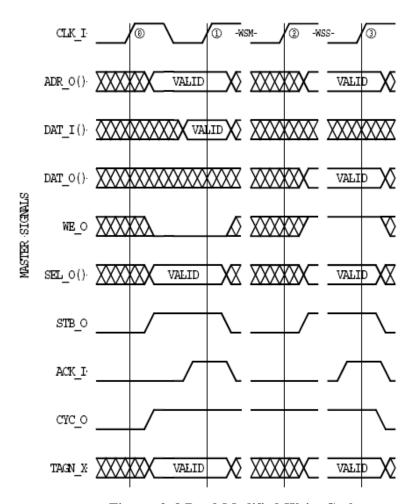

| Figure: 2. 5     | Handshaking protocol                                           | 35 |

| Figure: 2. 6 (a) | Single Read Cycle                                              | 35 |

| Figure: 2.6 (b)  | Single write cycle                                             | 35 |

| Figure: 2. 7 (a) | Block Read cycle                                               | 36 |

| Figure: 2. 7 (b) | Block Write cycle                                              | 37 |

| Figure: 2. 8     | Read-Modified-Write Cycle                                      | 38 |

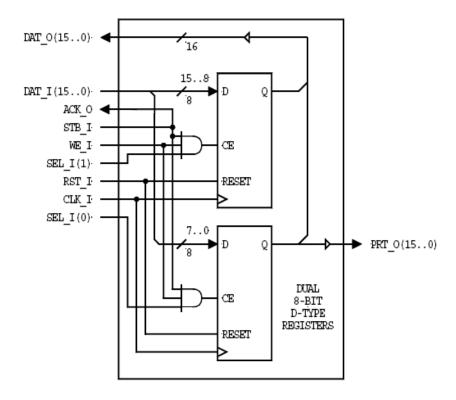

| Figure: 3. 1     | Block diagram of UART                                          | 45 |

|                   | Simulation result of 16-bit output port with 8-bit            |    |

|-------------------|---------------------------------------------------------------|----|

| Figure: 3. 2      | granularity                                                   | 46 |

| Figure: 3. 3      | Point-to-point interconnection                                | 47 |

| Figure: 3. 4      | Block diagram of DMA                                          | 48 |

| Figure: 3. 5      | Block write cycle.                                            | 49 |

| Figure: 3. 6      | Block read cycle                                              | 50 |

| Figure: 3. 7      | Block diagram of memory module                                | 51 |

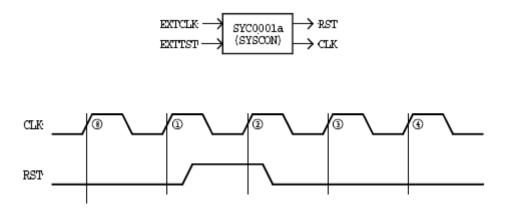

| Figure: 3. 8      | Block diagram and timing diagram of SYSCON                    | 52 |

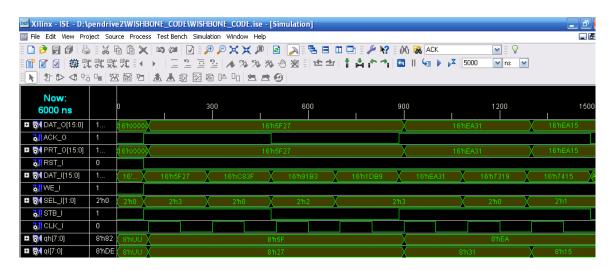

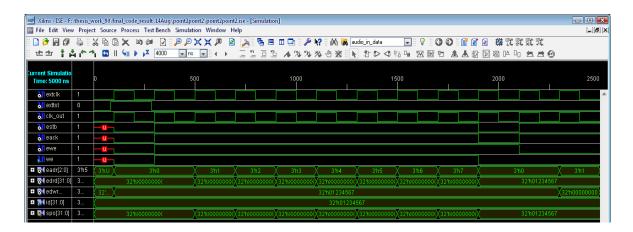

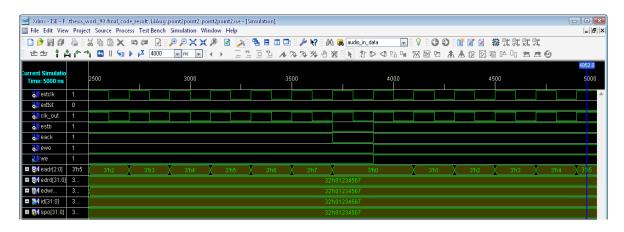

| Figure: 3. 9      | Simulation result for a clock period of 2500 ns               | 53 |

| Figure: 3. 10     | Simulation results for a clock period of 5000 ns              | 53 |

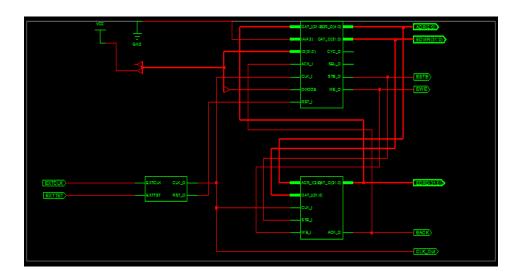

| Figure: 3. 11     | RTL schematic of interconnection                              | 54 |

| Figure: 3. 12     | ChipScope Pro results of real time signals of interconnection | 55 |

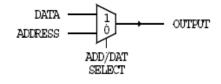

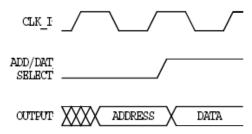

| Figure: 3. 13     | Multiplexed address/ data bus                                 | 58 |

| Figure: 3. 14 (a) | Three-state Interconnection                                   | 59 |

| Figure: 3. 15 (b) | Multiplexor logic Interconnection                             | 59 |

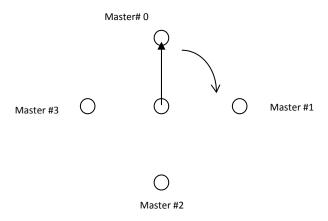

| Figure: 3. 16     | Round-robin arbiter working as a rotary switch                | 60 |

| Figure: 3. 17     | Round-robin arbiter working as a rotary switch                | 61 |

| Figure: 3. 18     | Timing diagram of arbiter                                     | 62 |

| Figure: 3. 19 | Block Diagram of a Generalized Shared bus Interconnection      | 65 |

|---------------|----------------------------------------------------------------|----|

| Figure: 3. 20 | Simulation result for a clock period of 4000 ns                | 67 |

| Figure: 3. 21 | RTL Schematics of shared bus interconnection                   | 68 |

| Figure: 3. 22 | ChipScope Pro results of real time signals of interconnection. | 69 |

| Figure: 4. 1  | Design Methodology                                             | 74 |

| Figure: 4. 2  | Hardware gateway of SOC architecture                           | 75 |

| Figure: 4. 3  | Block diagram of CPU                                           | 77 |

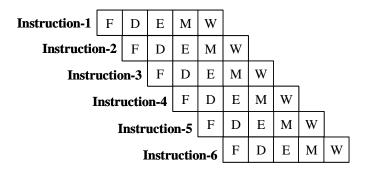

| Figure: 4. 4  | Pipeline stages of CPU                                         | 78 |

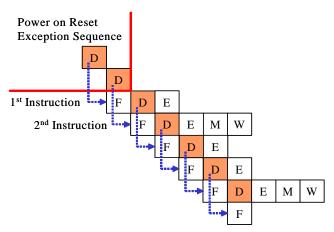

| Figure: 4. 5  | pipeline stages of instructions                                | 80 |

| Figure: 4. 6  | IF Issue                                                       | 80 |

| Figure: 4. 7  | Block Diagram of Decoder Unit                                  | 81 |

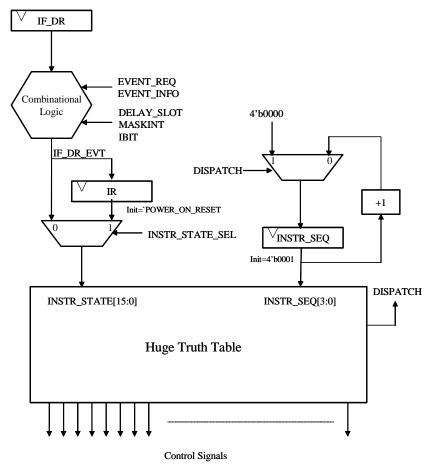

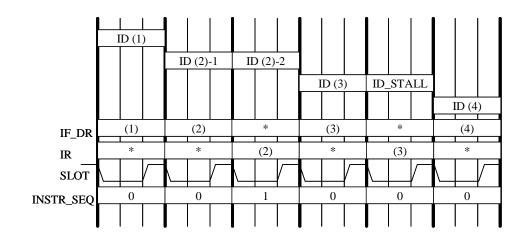

| Figure: 4. 8  | Basic Operation of ID Stage                                    | 82 |

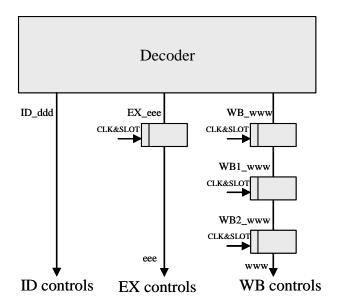

| Figure: 4. 9  | Shifting of Control Signal                                     | 83 |

| Figure: 4. 10 | Circuit diagram for Shifting Operation                         | 84 |

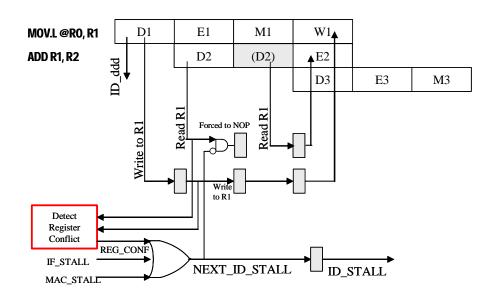

| Figure: 4. 11 | Circuit of Detecting Register Conflict                         | 84 |

| Figure: 4. 12 | Pipeline Control during Memory Load Contention                 | 85 |

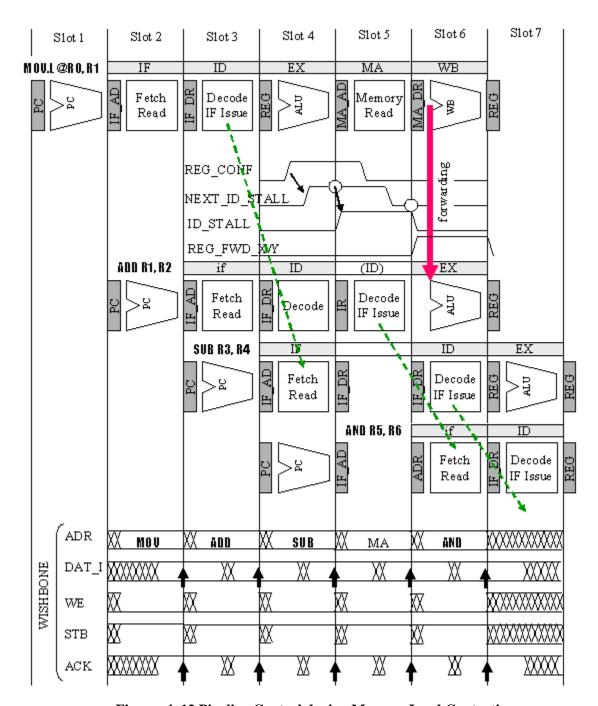

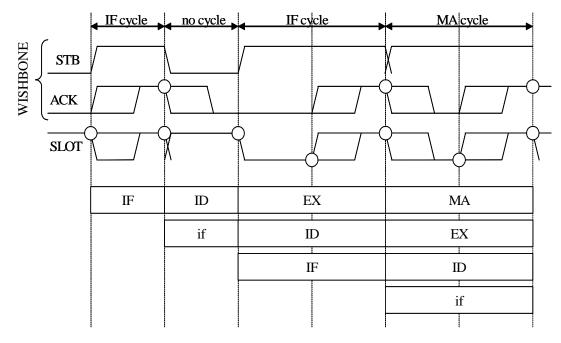

| Figure: 4. 13 | Wishbone ACK and CPU's SLOT                                    | 86 |

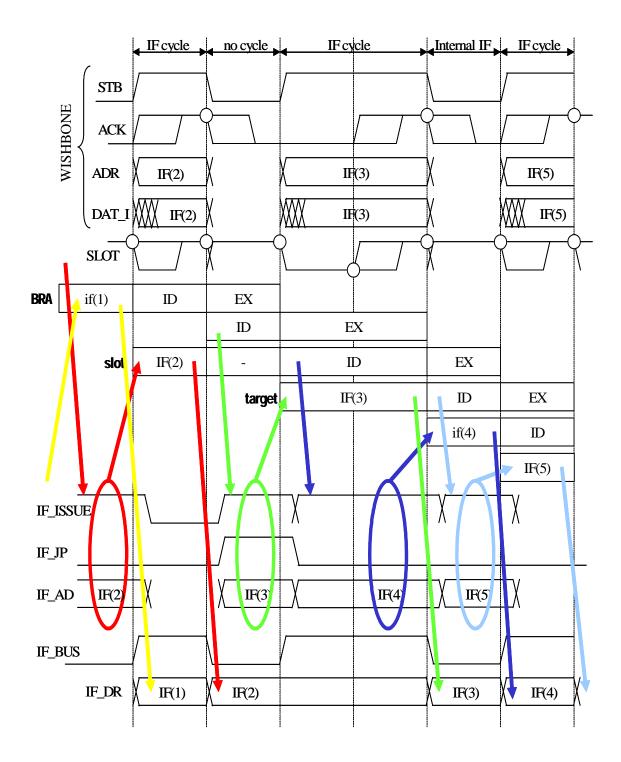

| Figure: 4. 14 | Instruction Fetch Cycle                                        | 88 |

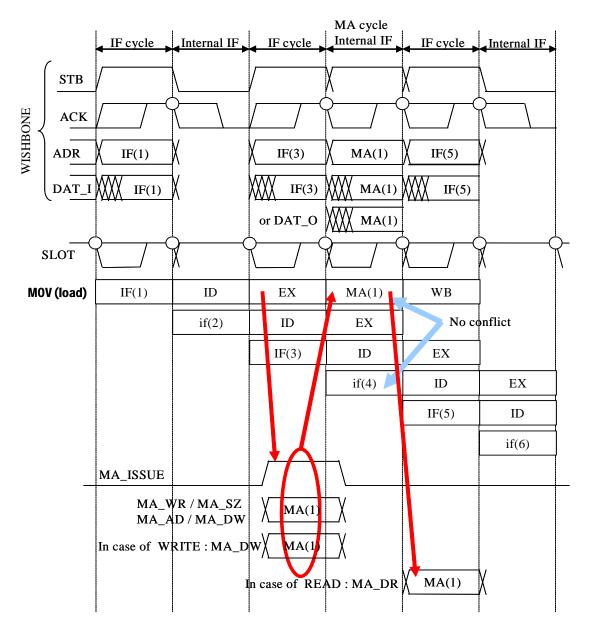

| Figure: 4. 15 | Memory Access Cycle                                            | 89 |

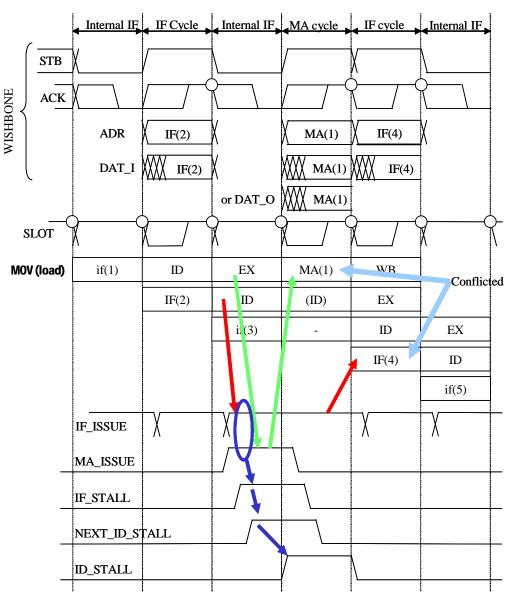

| Figure: 4. 16 | IF_MA Conflict                                                 | 90 |

| Figure: 4. 16 | IF_MA Conflict                                                 | 90 |

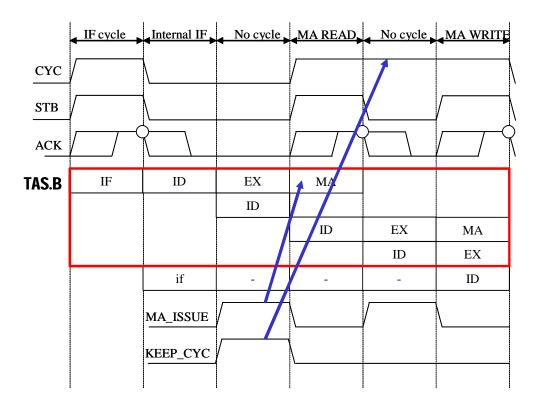

| Figure: 4. 17 | Read modify write cycle                                        | 91 |

| Figure: 4. 18 | Block Diagram of Data Path Unit                                | 93 |

| Figure: 4. 19 | Block Diagram of Multiplier Unit                               | 94 |

| Figure: 4. 20 | Registers of PIO                                             | 95  |

|---------------|--------------------------------------------------------------|-----|

| Figure: 4. 21 | UART Registers and its address                               | 97  |

| Figure: 4. 22 | System Controller (SYS) Registers                            | 99  |

| Figure: 5. 1  | Block Diagram of Experimental Set-Up for FPGA Implementation | 107 |

| Figure: 5. 2  | Circuit diagram of interfacing board                         | 108 |

| Figure: 5. 3  | Experimental Set-Up pf FPGA Implementation                   | 190 |

| Figure: 6. 1  | Flow Chart of Monitor Program                                | 121 |

| Figure: 6. 2  | Monitor output presented in a pictorial form                 | 124 |

| Figure: 6. 3  | Output of Real Time Clock Application                        | 125 |

| Figure: 6. 4  | Block diagram of LM4550 audio codec                          | 126 |

| Figure: 6. 5  | AC link serial interface                                     | 127 |

| Figure: 6. 6  | protocol  Block Diagram of AC97 Controller  Core             | 130 |

| Figure: 6. 7  | Real time signals of AC 97 Controller for the loop back test | 131 |

| Figure: 6. 8  | performed                                                    | 131 |

## List of Tables

| Table: 2. 1 | Master Signals                                                 | 30  |

|-------------|----------------------------------------------------------------|-----|

| Table: 2. 2 | Slave Signal                                                   | 31  |

| Table: 2. 3 | Signals Common to both Masters and Slaves                      | 31  |

| Table: 2. 4 | Comparison of WISHBONE, AMBA and CoreConnect                   | 40  |

| Table: 3. 1 | Device utilization summary for Spartan3e                       | 54  |

| Table: 3. 2 | Device utilization summary for Virtex-II Pro                   | 55  |

| Table: 3. 3 | 32-bit Point-to-Point interconnection benchmark results        | 56  |

| Table: 3. 4 | Address map used by Interconnection                            | 64  |

| Table: 3. 5 | Device utilization summary of interconnection Spartan3e        | 68  |

| Table: 3. 6 | Device utilization summary in Virtex-II Pro                    | 69  |

| Table: 3. 7 | 32-bit shared bus interconnection benchmark results            | 70  |

| Table: 4. 1 | Input Output Signals of CPU                                    | 78  |

| Table: 4. 2 | Input Output Signals of PIO                                    | 95  |

| Table: 4. 3 | UART Input Output Signals                                      | 96  |

| Table: 4. 4 | Baud Rate Settings Example                                     | 97  |

| Table: 4. 5 | System Controller Input Output Signals                         | 98  |

| Table: 4. 6 | On-chip Memory Input Output Signals                            | 100 |

| Table: 5. 1 | Address Map of the Peripherals                                 | 104 |

| Table: 5. 2 | Top module Input Output Signals                                | 105 |

| Table: 5. 3 | Assembly Instruction with Hex Code, Bus transaction and Output | 108 |

| Table: 5. 4 | Synthesis Results with Area Optimization                       | 111 |

| Table: 5. 5 | Synthesis Results with Speed Optimization                      | 111 |

| Table: 5. 6 | Comparison of Synthesis Results                                | 112 |

| Table: 6. 1 | List of Functions used in Monitor Program                      | 119 |

| Table: 6. 2 | Device Utilization Summary for Audio Processing application    | 132 |

#### **List of Abbreviations:**

SOC System on Chip

IP Intellectual Property

PBD Platform Based Design

CAD Computer Aided Design

GPL General Public License

LGPL Lesser General Public License

RTL Register Transfer Logic

VGA Video Graphics Array

UART Universal Asynchronous Receiver/Transmitter

MAC Multiply and Accumulate

PCI Peripheral Interconnect Component

VME VERSAmodule Eurocard bus ISA Instruction Set Architecture

RISC Reduction Instruction Set Architecture

DSP Digital Signal Processing

ASIC Application Specific Integrated Circuit

FPGA Field Programmable Gate Array

VHDL VHSIC Hardware Description Language

RMW Read Modify Write

ASB Advanced System Bus

AHB Advanced High performance Bus

APB Advanced Peripheral Bus

PLB Processor Local Bus

OPB On-Chip Peripheral Bus

## Chapter 1

## System-on-Chip: An Overview

- Concept of System-on-Chip

- History of SOC

- Design Reuse Concept

- The system on chip design flow and process

- System level Design Issues

- Motivation

- Work Presented in the Thesis

- Thesis Outline

- Conclusions

This chapter describes the System-on-Chip (SOC) design concept. Various issues related to SOC design such as "Design Reuse", system design flow and system design processes are discussed in this chapter. The system level issues such as on-chip buses, SOC test methodologies and SOC verifications are also discussed. In the final section the motivation behind the thesis, work presented in this thesis with thesis outline is presented.

#### 1.1 Concept of System-on-Chip

The rapid development in the field of mobile communication, digital signal processing (DSP) motivated the design engineer to integrate complex systems of multimillion transistors in a single chip. The integration of the transistor in a single chip greatly increases the performance of the system while reduction in system size. There is a considerable increase in the application front in recent time. Moore's law states that integration density gets doubled every two years so the complexity of the integrated systems also increases by keeping the used chip area constant. In order to keep pace with the levels of integration available, design engineers have developed new methodologies and techniques to manage the increased complexity in these large chips [1].

System-on-Chip (SOC) design is proposed as an extended methodology to this problem where IP cores of embedded processors, memory blocks, interface blocks, and analog blocks are combined on a single chip targeting a specific application. These chips may have one or more processors on chip, a large amount of memory, bus-based architectures, peripherals, co- processors, and I/O channels [2]. These chips integrates systems far more similar to the boards designed ten years ago that to the chips of even a few years ago [2]. The integration process involves connecting the IP blocks to the communication network, implementing design-for-test (DFT) techniques and using methodologies to verify and validate the overall system-level design [1].

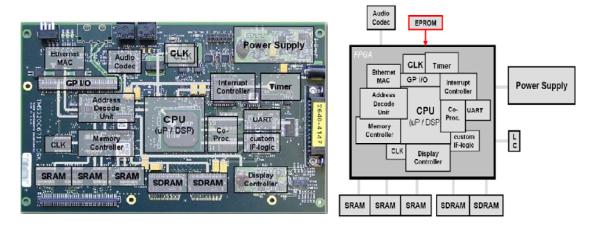

Figure: 1.1 shows idea of SOC the a system of several ICs out of a printed circuit board is being integrated into a single chip while maintaining the overall structure the same.

Figure: 1. 1 Idea of SOC design

The benefits of SOC design include:

- Smaller space requirements.

- Reduction in chip count.

- Lower memory requirements.

- Greater design freedom.

- Lower consumer costs.

- Higher performance and more reliable as the system will be on a single chip.

These benefits also come with challenges including:

- Larger design space, higher design and prototype costs

- A high level of debugging methodology,

- Power management,

- Longer design and prototyping cycle time

Apart from these challenges, the design again needs an expertise in both hardware and software levels for proper hardware and software co-design. Another important aspect of SOC integration is the development of a proper test methodology for post manufacturing test. All these integration issues makes the design time consuming and also expensive.

#### 1.2 History of SOC

In 1974 digital Watch is the first developed System-On-Chip Integrated Circuit. The Microma liquid crystal display (LCD) digital watch is the first product to integrate a complete electronic system onto a single silicon chip, called a System-on-Chip. The first true SOC appeared in a Microma watch in 1974 when Peter Stoll integrated the LCD driver transistors as well as the timing functions onto a single Intel 5810 CMOS chip [14]. Many ASIC vendors addressed SOC opportunities in the 1990s by embedding microcontrollers and DSPs into system-level chips that enabled hand-held games and instruments, as well as speech processing, data communications, and PC peripheral products.

#### 1.3 Design Reuse Concept

With the evolution of technology, the ways of designing the chips have been changed. It differs from the traditional design procedure such as writing the RTL from scratch, integrating RTL blocks into a top-level designing and doing synthesis followed by placement & routing.

**Design reuse** – the use of pre-designed and pre-verified cores – is now the cornerstone of SOC design [2]. It uses reusable IP blocks that supports plug and play integration and in turn allows huge chips to be designed at an acceptable cost, and quality. This section discusses various issues related to design of reusable Intellectual Property (IP) core, integration of cores to form a System on Chip design.

As Submicron technology is being used to design, the SOC it presents a whole set of design challenges including interconnect delays, clock and power distribution, and the placement and routing of millions of gates. These may have impact on the functional design of the SOCs and the design process itself. Hence Interconnect issues, floor planning and timing design must be engaged early in the design processes.

SOC design is now a driver for many other improvements in the IC industry like buses, bus interface, IP exchange formats, documentation, IP protection and tracking and test wrapper [1]. It has also forced suppliers to improve the quality of reusable IP.

SOC design also involves development of software in addition to the hardware itself; software plays an essential role in the design, integration, and test of SOC systems.

Hence the designers and developers migrated to the system level to address hardware/software co-design issues.

#### 1.3.1 Design for reuse

Extensive libraries of reusable blocks or macros are used to design block-based design methodology [2]. A set of design methodology has to be followed in order to produce consistently reusable cores.

The methodologies are based on the following rules:

- 1. The macros must be extremely easy to integrate into the overall chip design.

- 2. The macros must be so robust that the integrator has to perform no functional verification of internals of the macros.

Some of the techniques for design reuse are good documentation, good code, thorough commenting, well designed verification environments, and robust scripts. In addition to the requirements mentioned above for a robust design, there are some additional requirements for a design to be fully re useable [2].

The macros may be:

#### • Design must be configurable and use in multiple technologies

The macros must be easily configurable to fit different applications. The soft macros should be supplied with a synthesis script which would produce quality of results with a variety of libraries. In the case of hard macros, this means having an effective porting strategy for mapping the macro onto new technologies.

#### • Design for simulation with a variety of simulators

Both Verilog and VHDL version of model and test bench should be available, and they should work with all the major commercial simulators.

#### • Designed with Standards- based interfaces

Unique or custom interfaces should be used only if no standards- based interface exists.

#### Verified independently of the chip in which it will be used and to a high level of confidence

Macros are designed and only partially tested before being integrated into a chip for verification, thus saving the effort of developing a full test bench for the design.

Reusable designs must have full, stand-alone test benches and verification suites that afford very high levels of test coverage. A rigorous verification is done and a physical prototype is being build that is tested in an actual system running real software.

# • Fully documented in terms of appropriate restrictions and applications: Valid configuration and parameter values must be documented. How the macro can be used and the restrictions on configurations or parameters must be stated.

#### 1.4 The system on chip design flow and process

#### 1.4.1 A canonical SOC design

Real SOC designs are much more complex than the generic form of SOC design shown in Figure: 1.2, but this miniature version of SOC design allows us to discuss the challenges of developing these chips utilizing reusable IP cores. The design process comprises specifying such a system for developing and verifying the cores, and integrates them into a single fabricated chip.

The above canonical SOC design contains the following blocks.

- A microprocessor may be 8 bit to 64 bit depending on the application.

- A memory module which may be single or multi-level and may include SRAM and DRAM.

- An external memory controller for controlling flash or SRAM.

- A video decoder which may be MPEG or AVI.

- A I/O controller which may include PCI, Ethernet, USB, analog to digital, digital to analog converter.

- A GPIO for general input output for interfacing external devices like LEDs or LCDs or for sampling data.

#### 1.4.2 System Design Flow

A two major way of design flows are being used by design engineers in order to meet the challenges of SOC design.

- From a waterfall model to a spiral model

- From a top-down methodology to a combinational of top-down and bottom-up

#### I. Waterfall vs. Spiral

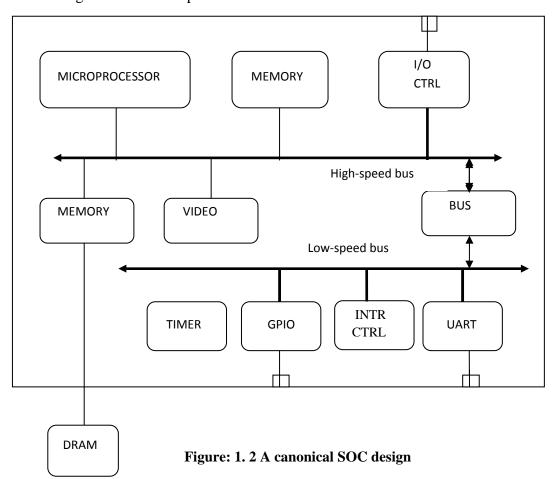

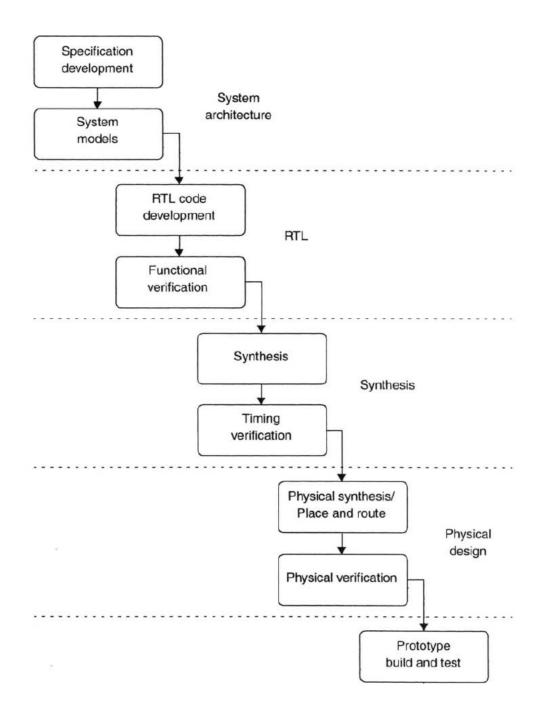

A traditional way of ASIC development, called waterfall model is shown in Figure: 1.3. In a waterfall model [2], the SOC design transits from phase to phase in a step, and never returns to the activities of the previous phase. In this model, the design often tossed "over the wall" from one team to the next with little interaction among them.

The phase of the design process starts with the development of a specification for the ASIC. For complex ASIC the high algorithmic content is developed and given to the design team to develop the RTL for the SOC. A set of verification is done in order to ensure the proper functionality of the SOC design. After the complete verification, the design is delivered to a team of synthesis experts to generate a gate level net list for the hardware design of SOC. The proper functionality of the design is based on the timing between the blocks of the design; a timing verification is performed to verify that the ASIC meets timing.

Figure: 1. 3 Water fall design process

After timing is performed the design is given to the physical design team, which places and routes the design. Finally, a prototype is built and tested. The prototype is delivered to the software team for software debug. Software development is started shortly after the hardware design is started.

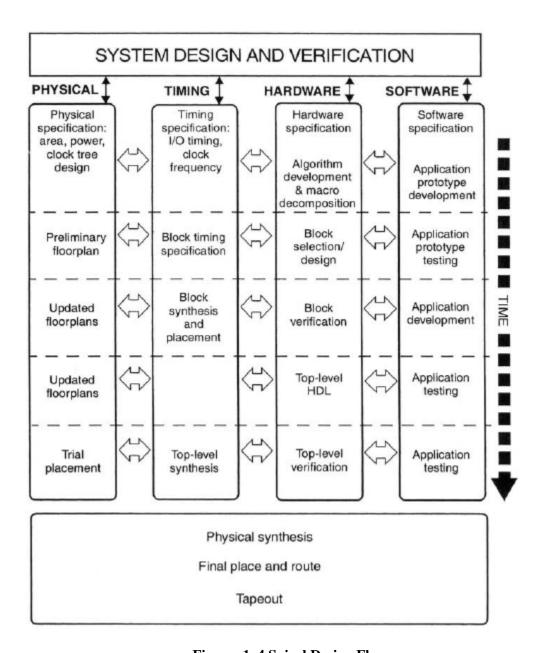

This flow has worked well in designs of up to 100 k gates and down to 0.5 um [2]. A major demerit of this flow is the improper handoffs from one team to another. For example the RTL design team may have to go back to the system designer and tell him that the algorithm is not implementable, or the synthesis team may have to go back to the RTL team and inform them that the RTL must be modified to meet the timing. As complexity of system increases, geometry shrinks, and time to market pressures continue to escalate, chip designers are turning to a modified flow to produce today's larger SOC designs. Hence design teams are moving from the old waterfall model to the newer spiral development model, where the team works on multiple aspects of the design simultaneously, incrementally improving in each area up to the completion of the design. Figure: 1.4 shows the spiral SOC design flow [2] where designer addresses all aspects of hardware and software design concurrently: functionality, timing, physical design and verification.

- Concurrent development of hardware and software.

- Parallel verification and synthesis of modules.

- Floor planning and place-and-route included in the synthesis process.

- Modules developed only if a pre-designed hard and soft macro is not available.

- Planned iteration throughout.

#### II. Top-down Vs. Bottom up

The top down process begins with specification and decomposition, and ends with integration and verification. These processes steps are describes as follows:-

- 1. Prepare a complete specification for the system and its subsystem.

- 2. Refine its algorithm and architecture, including software design and hardware/software co-simulation if necessary.

- 3. Decompose the architecture into well -defined macros.

- 4. Design or select macros.

- 5. Integrate macros into the top level; verify functionality and timing.

- 6. Deliver the subsystem/system to the next higher level of integration; at the top level, this is tape out.

- 7. Verify all aspects of the design (functionality, timing, etc.).

Figure: 1. 4 Spiral Design Flow

In order to accelerate the design process and to meet the time-to-market pressures, increasingly powerful tools, such as synthesis and simulation tools have been developed. But the top-down methodology is an idealization process, it assumes that the lowest level blocks specified can, in fact, be designed and built. If a block is not feasible to design the

whole specification process has to be repeated which increases the design time again. In order to deal with this situation a mixture of top-down and bottom-up methodologies is being used; where libraries of reusable hard and soft macros are used as a source of preverified blocks; and it assures that at least some parts of the design can be designed and fabricated in the target technology in order to meet the desired specification.

#### 1.4.3 The System Design Process

#### 1. Create the system specification

The design process begins with identifying the objectives of the design; such as system requirements, the required functions, performance, and cost and development time for the system. A set specification is recursively developed, verified and refined until they are detailed enough to allow RTL coding to begin. Specification describes how to manipulate the interfaces of a system to produce the desired behavior. Specifications are to be provided for both hardware and software portions of the design. The following are the specification requirements for the hardware and software portion of the design [2].

#### Hardware:

- functionality, external interfaces to other hardware (pins, buses and how to use them)

- Interface to software (register definitions)

- Tiring and performance

- Area and power

#### *Software:*

- Functionality,

- Timing,

- Performance,

- Interface to hardware, software, structure and kernel.

These specifications are written jointly by engineering and marketing teams, in a natural language, such as English. In order to avoid the ambiguities, incompleteness and errors, companies have started using executable specifications for some or all of the system. An executable specification is an abstract model for the hardware and software being used. It

is written in C, C++ or SystemC or a Hardware verification language (HVL) for high level specifications. At lower levels, hardware is usually described in Verilog or VHDL. As executable specifications are only addressing the functional behavior of a system, so it is necessary to describe critical physical specifications such as timing, clock frequency, area and power requirements.

#### 2. Develop a behavioral model

After specification is defined an initial high level of design is developed along with a high-level behavioral model for the overall system. This model can be used to test the basic algorithms of the system design and to show that meet the requirements outline in the specification. For example, in an image and video processing design may need to demonstrate that losses in compression/decompression are at or acceptable level. This way of high-level model specification is termed as executable specification. These specifications can be used as the reference for the future versions of the design.

#### 3. Refine and test the behavioral models

After the behavioral model is defined in order to refine test algorithm a verification environment for the high-level model is developed. This environment provides a mechanism for refining the high-level design, verifying the functionality and performance of the algorithm. This can be used later to verify models for the hardware and software, such as RTL model verified using hardware/software simulation.

For example: - A multimedia or a graphics system may be initially coded in C/C++ with all floating point operations. This allows the system architect to code and debug the basic algorithm quickly. Once the algorithm is determined, a fixed-point version of the model is developed that allows the architect to determine the accuracy level required in each operation to achieve performance goals while minimizing die area.

Finally, a cycle-accurate and bit accurate model is developed, providing a very realistic model for implementation. These multiple models are very useful for hardware/software co-simulation to debug their software.

#### 4. Determine the hardware/software partition

The hardware/software partition is the division of system functionality between hardware and software. This is a manual process requiring judgment and experience on the part of

the system architects and a good understanding of the cost/performance trade offs for various architectures. A rich library of pre-verified, characterized macros and a rich library of reusable software modules are the key things for identifying the size and performance of various hardware and software functions. Finally, the interface between the hardware and software is defined and the communication protocols between them are also defined.

#### 5. Specify and develop a hardware architectural model

Once the hardware requirements are defined, detail hardware architecture is specified. The issues related to this are determining which hardware blocks will be used, and how they will communicate, memory architecture, and bus structure and its bandwidth. Most of the SOC communicates with different blocks over one or more bus, thus the required bandwidth can be applicant dependent. A substantially amounts of application code is run on the architecture to evaluate the bandwidth of the system. Running significant amounts of application code on an RTL design is time consuming. In order to overcome this problem, transaction-level models are developed to model interfaces and bus behavior. This model can run considerably faster than RTL models and gives accurate estimates of performance. SystemC is used to facilitate the design of transaction level modeling. Finally, the hardware architecture is developed, tested and modified until a final architecture meets the system requirements.

#### 6. Refine and test the architectural model (co-simulation)

The software development often starts only once the hardware has been built. This serialization may lead to delayed product. The architectural model for the system can be used for hardware/software co-simulation. It provides sufficient accuracy that software can be developed and debugged on it, long in advance of getting actual hardware. Hence having accurate models of the hardware is the key issue in SOC design.

#### 7. Specify implementation blocks

After the model is co-simulated hardware specification is provided which is a detailed specification of the performance, functionality, and interfaces for the hardware system and its component blocks. It also specify a description of the basic functions, the timing,

area and the power requirements, and the physical and software interfaces and the descriptions of the I/O pins and the register map.

#### 1.5 System level Design Issues

This section discusses system level design issues such as different types of IP cores, on chip buses, SOC test methodologies and SOC verification.

#### 1.5.1 Different Types of IP Cores

#### I. Digital IP

In the previous section Design reuse is elaborated and we observed that well-designed IP is the key to successful SOC design. The block used for SOC design must be designed well unless, the tape out of the system becomes very painful and time-consuming. Hence, well-designed IP core can be integrated with any SOC flow, and produce good results quickly [2]. This section presents an issue related to produce well-designed IP cores. The IP cores are classified into three categories [1]: *Soft, firm and hard*.

#### Soft IP:

Soft IP blocks are specified in hardware description languages using RTL or higher level descriptions. These are generally provided by the vendor in form of software code which are process independent and can be synthesized to the gate level. Hence these are more suitable for digital IP core design. These types of cores are sometimes not guaranteed power or timing characteristics, as the implementation and application in different process may produce variation in performance. But these types of IP cores are very much flexible, portable and reusable and prevents the user frame introducing any design errors into block.

#### Hard IP:

Hard IP blocks have fixed layout and already go through physical design process. This IPs is optimized for a given applicator in a specific process. As the timing characteristics are optimized the performance of the IPs are predictable. The only drawback is that, it requires additional effort and cost to produce this IPs. These are also

limited to specific application but as this IPs are tested on Silicon the vendors gives more assurance about its accuracy and correctness.

#### Firm IP:

Firm IP are provided as parameterized circuit description so that designers can optimize core for their specific design needs. Hence firm IPs are more predictable. These are more flexible and portable than soft and hard IP.

Most of the digital processor blocks are being designed with hard IP in order to achieve the performance goals. Memory cells are designed by transistor level and memory arrays are tiled from these cells using a compiler [RMM]. Recently soft IP blocks preferred as hand off level [1]. The typical soft IPs available is interface blocks (USB, UART, and PCI), encryption blocks (DES, AES), multimedia blocks (JPEG, MPEG 2/4), and networking blocks (ATM, Ethernet and Micro Controllers [1].

#### II. AMS IP

Another important IP which is gaining interest is Analog mixed signal IP. The typical AMS components include operational amplifiers, analog to digital converters (ADCs), digital to analog converters (DACs), phase locked loops (PLL), and radio frequency (RF) modules etc. This IPs is designed using Hard IP and target to one application in a specific fabrication technology.

#### 1.5.2 System Interconnect and On Chip-Buses

In earlier days every chip designer had unique bus designed for optimum performance for their own design project. This made difficult to reuse blocks from other projects to their own designs. Hence, there was need of standard bus, which allows reusable blocks developed with a single interface to be used for a variety of applications. ARM [11] uses AMBA as system interconnects solution for their system design. CoreConnect is being by IBM. The comparisons of three types of bus architecture are presented in the Chapter-2 of the thesis.

#### 1.5.3 SOC Test Methodologies

Another important aspect of SOC integration is the development of a test methodology for post manufacturing tests. Testing of SOC designs has many similarities

with the traditional system on Board (SOB) designs. Cores in SOC are the components of an SOC where as in printed circuit boards ICs are the components of SOB. In SOB, IC design manufacturing and testing are performed by the IC provider and the system integrator has to only design the board level designing using these ICs. In SOC, the core providers supplies only the description of cores and the system integrator is responsible to design any blocks called User Defined Logic (UDL), and integrates these predesigned cores.

As the system is in logic level the system integrator cannot perform post manufacturing test. Hence the integrator can only test the core logic wires between cores and expects a set of test patterns with high fault coverage from the core provider. Another key difference between the SOB and SOC is that unlike SOB the physical input output of the cores are not accessible by the user in SOC. The test access to the embedded cores is the responsibility of the system integrator. Hence additional logic and wiring, mechanisms are required which leads to the development of core test access architecture [1].

#### I. IP core level test

The testing of an IP core consists of an internal DFT Structures Design for Test (DFT) structure and a required set of test patterns to be applied and captured on the core periphery. The test pattern includes *the data and protocol patterns*. The data pattern contains actual stimulus and response values. The protocol pattern specifies how to apply and capture the test data. As the system integrator has very limited knowledge about the structural content of the core, the core internal test should be carried at by the core provider. Hence the core provider should provide the internal DFT hardware structure of the core, the stimulus patterns of the core and the validation of these stimulus patterns. The core provider must determine the internal core requirement of the core without knowing the target process, application and the desired test coverage level. BIST is another solution that can be used by core provider for core level testing.

#### II. SOC level test

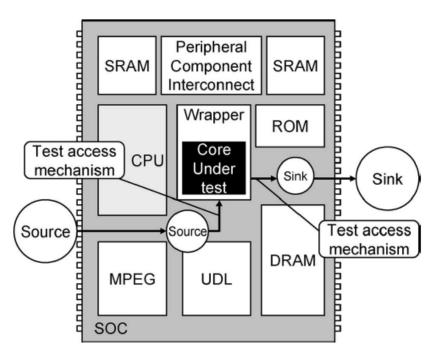

Figure: 1.5 shows a conceptual architecture for testing-embedded core based SOC. This architecture consists of

- 1. Test pattern source and sink: the test pattern source is responsible for generating the core stimuli. Test sink is used to receive the test responses.

- 2. Test access mechanism (TAM): the on-chip test pattern transportation is performed by test access mechanism. It is useful in transferring the test pattern source from the source to the core under test or for transferring the test responses from core under test to a test pattern sink.

- 3. Core test wrapper: it forms the interface between the embedded core and its environment, by connecting the embedded core to the rest of the IC and to the TAM.

Figure: 1. 5 Core based SOC Test Architecture

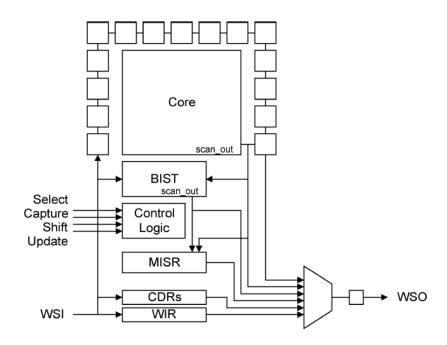

A new standard IEEE-1500 was developed to facilitate SOC testing for both the core provider and the system integrator. The purpose of this is to provide a uniform interface between the core and the chip-level test access mechanism; it uses parallel test port instead of the test access port (TAP) controller. Figure: 1.6 shows the block diagram

of a P1500 wrapper which consists of four control inputs and one pair of serial data input and output. Serial wrapper scan input (WSI) is used to transport wrapper instruction and test data. Instructions are shifted serially into the wrapper instruction register (WIR) and various enable signals are generated from the control logic based on the context of the WIR and the four control inputs. CDRs are used to captures the test results. The ring of flip flops around the core form the boundary data register (BDR) that isolates the core's functional interface from the other blocks during testing. While performing full-scan test the test vector is serially shifted in through WSI and scan output serially shifted out through to the wrapper scan output (WSO) [1].

Figure: 1. 6 Block Diagram of P1500 Wrapper for BIST DFT Core

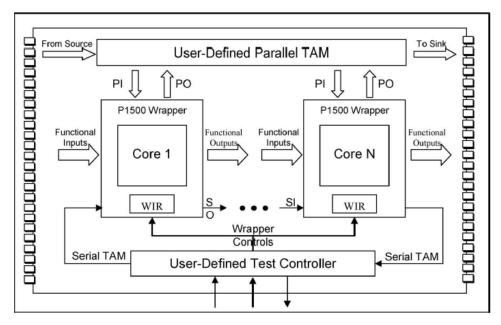

Figure: 1.7 shows the integration of the cores with P1500 Standard. Each core is encapsulated with P1500 wrapper and user defined test controller signals enabled by external sources is used to provide control signals to the wrapper. A user-defined parallel TAM is used to transport test data to/from individual IP cores.

Figure: 1. 7 Integration of Cores using P1500 wrapper

### 1.5.4 SOC Verification

As the design complexity is increasing the verification the complete SOC is becoming bottleneck of system designers. As the ITRS [13] has noted while design sizes have grown exponentially over time in accordance with Moore's law, verification complexity has been growing double exponentially. This is due to the fact that the number of states that must, be verified is exponential in the size of design. In industrial practice, two methods are used to solve the verification bottleneck: *verification information are encapsulated within IP cores to make the verification effort reusable, and use of standard IP cores to reduce the bugs during integration.* The main stream verification utilizes the dynamic methods such as simulation and emulation. Hence the encapsulation consists of supplying of simulation test benches along with the IP cores. Assertion based verification strategy helps in reducing the verification problem. In this methodology, the design core and interfaces specified with the correct behavior. This gives rise to standardizing languages for more complex assertions such, PSL or SVA [1] later.

On the other hand several companies are developed standardized bus protocols for on chip communication such as AMBA [11], CoreConnect [12] and WISHBONE [4].

Adopting a standard interconnect not only eliminates the common errors occurring during the design of an interconnection protocol, but also reduces the incorrect interfacing of cores and interconnect. The above described methods help in reducing the verification problems. But as the designed complexity increases the dynamic verification methods suffers from poor verification coverage. Poor coverage increases the undetected bugs in IP cores are undermine the goal of reusing IP cores without needing to completely reverify them.

Hence the formal verification methodology is used which minimizes the probability of bugs in a design. More research activities focusing this area of verification. The key research areas are compositional model checking. The specifications that are verified and the assumption under which they are verified are documented and can be exploited during integration verification. Again the methodology advancement in dynamic verification helps in growing formal verification approach. Formal verification is being used in many industry applications such as RTL gate-level equivalence checking and microprocessor verification. Finally despite all the research advances now and in future, it is impossible that the verification challenge can be solved without help from designs. Leading companies involve verification experts early in the design process to steer the design toward better verifiability [1].

#### 1.6 Motivation

SoC design requires a standard bus interface for IP cores to communicate with each other. There exist many other bus interfaces, but AMBA [11], CoreConnect [12] and WISHBONE [4] are well known and well used SOC bus architectures. All three bus architectures are open bus architectures, which require no fees or royalties to use them. WISHBONE offers advantage compared to AMBA and CoreConnect. All designer using WISHBONE bus interface are allowed to upload their design in Open Core site where there exists many IP cores that support WISHBONE bus interface and they are all free to use. So depending upon the design specification the designer can select the IP cores from the site and glue them to the WISHBONE bus architecture to design the final SOC. Comparing the architecture of these three buses, it is observed that all are supported by multiplexer interconnections. WISHBONE supports variable interconnection and variable time

specification. It can be coded using any hardware description language like VHDL and Verilog®, and it takes the shapes of simple logic gates supported by most of the FPGA and ASIC devices. WISHBONE also supports Single and Block Read/Write cycles, Read-Modify-Write (RMW) transfer. In respect to all of the above issues WISHBONE supports almost all features also supported by AMBA and CoreConnect. It also offers advantage of using predesigned IP cores available freely Open Core site for the portable and reliable SOC design. Keeping in view of the above, in this dissertation we adopt WISHBONE for SOC design and explore the Open Core based SOC design platform.

# 1.7 Work Presented in the Thesis

The major contributions of this thesis are:

- The possibility of using an existing bus interface for faster and low cost SoC design is evaluated. The design, verification, FPGA implementation of WISHBONE interconnection architectures in terms of size and speed for SoC design is evaluated.

- A set of wishbone compatible cores such as 32-bit RISC CPU, on chip memory, universal asynchronous receiver and transmitter (UART), Parallel Input Output (PIO) and System controller (SYS) are collected from Open Core and integrated to develop a portable low cost SoC design.

- The integration issues are discussed and the synthesis results in terms of size and speed are presented. A test bench is developed in order to verify the CPU instruction with the final integrated architecture.

- Finally, FPGA implementation of SoC architecture has been done using VIRTEX-II Pro FPGA and the functionality of the system is verified through porting the application software on the SoC architecture.

### 1.8 Thesis Outline

The layout of this thesis compiled is as follows:

**Chapter 1:** The first chapter presents introduction to SOC design. This chapter also discusses SOC design process and system level issues such as design of reusable IP core,

on chip bus interface and strategies for synthesis, verification and testing. A brief overview of the thesis outline is presented here.

**Chapter 2:** The second chapter describes the concept of Open Hardware. The Open Core based SOC design platform is illustrated. The design reuse using Wishbone bus specification is also presented in this chapter.

**Chapter 3:** In this chapter Design and verification of a point-to-point interconnection and shared bus interconnection using DMA MASTER and memory SLAVE core is presented. The bench marking of the interconnections in terms of size and speed is evaluated by using two FPGA technologies.

**Chapter 4:** This chapter presents a description of design methodology to implement proposed SOC Architecture in FPGA using Wishbone bus interface. The design specifications of the IP cores are described here.

**Chapter 5:** SOC integration issues and verification results, synthesis and FPGA implementation of the SOC architecture is presented in this chapter.

**Chapter 6:** This chapter demonstrates the validation of SOC architecture with porting application software developed in GNU C compiler and debugger.

**Chapter 7:** Finally, a conclusion is drawn in this last chapter. This chapter also lists the future research scopes from the studies undertaken.

### 1.9 Conclusions

The concept of SOC design through design reuse is discussed, and the design flow and design process steps are described. The various issues related to system level design are addressed and observed that

- Design Reuse through well design IP cores is the key factor behind reliable time to market SOC design.

- A standard interface bus must be adopted to get reduced integration efforts.

- The design of test circuits must be done properly in during the SOC integration to avoid post manufacturing physical error.

- A proper verification methodology must be adopted to validate the final functionality of the SOC.

# Chapter 2

# Open Core Based SOC Design Platform

- Platform Based SOC Design

- Open Core Based SOC Design Platform

- The Objective behind WISHBONE

- WISHBONE Basics

- WISHBONE Interface Specification

- Wishbone Interconnections

- WISHBONE Bus Cycle

- Data Organization and Customized Tag

- WISHBONE SOC Bus Comparison with AMBA and CoreConnect

- Conclusions

SOC design increases the density of transistor in a chip. The increased density of transistor in turn increases the complexity of the system. The SOC design methodology offers definite benefits; however there are certain challenges like larger design space, higher design and prototype costs, high level of debugging methodology, power management, and longer design and prototyping cycle time. Apart from these challenges, the design again needs an expertise in both hardware and software levels for proper hardware and software co-design. Another important aspect of SOC integration is the development of a proper test methodology for post manufacturing test. All these integration issues makes the design time consuming and also expensive.

To deal with this inherent integration problems and reduction in design cycle time, many methods for SOC design are proposed by research and industry community. There are several methods for SOC design, however in this thesis we limit our discussion for two methods of SOC design. These are *Platform based SOC design* and *Open Core SOC design methodology*. This chapter also explains about the features of Open Core on chip bus interface WISHBONE which is the key factor in Open core SOC design methodology. Finally, different bus interfaces available for SOC design have been compared.

# 2.1 Platform Based SOC Design

In Platform based design (PBD), new designs could be quickly created from the original platform over many design derivatives. More specifically a platform is an abstraction level that covers a number of refinements to a lower level resulting in improvement of the design productivity. An SOC platform consists of hardware IP, software IP, programmable IP, standardized bus structures and communication networks, computer-aided design (CAD) flows for hardware/software design, verification and implementation, system validation tools, design derivative creation tools and dedicated hardware for system prototyping [1]. PBD is a design methodology which starts at system level and high productivity is achieved by using predictable, pre-verified blocks that uses standard interfaces.

The two major areas in PBD methodology are (a) *block authoring and* (b) *system-chip integration* [15]. Block authoring uses a methodology which creates block that

interfaces easily with multiple target designs. Two design concepts used in block authoring are interfacing standardization and virtual system design.

In interfacing standardization, both internal and external design teams can do block authoring, as long as they are using the same design methodology and the same interface specifications. The interface standard used can be product or application specific.

In virtual system design, the designer has to focus about the power profile, clocking schemes, internal clock distribution, and testing schemes of the design. Also block interfaces (with a single bus or multiple bus) types, and the type of block such as soft, hard or firm are also decided during virtual system design.

System chip integration focuses on designing and verifying the system architecture and the interfaces between the blocks. Integration process starts with partitioning the system around the pre-existing block level functions and identifying the new or differentiating function needed. These partitioning are done at the system level, along with performance analysis, hardware /software design trade-offs, and functional verification.

#### The benefits of PBD are as follows:

- Design uses diverse and specialized functions from multiple sources. Hence planned design reuse yields very high productivity.

- Hierarchical routing and timing reduce design focus.

- Interface based design promotes and multiple reuse for blocks allows amortization of development cost and more optimal block design.

#### The challenges of PBD include:

- Planned reuse requires proper design planning and accurate future product plans.

- Significant software portions require extensive hardware/software co-verification.

- Platform migration to new process technology requires re-characterization of hard, soft IPs and platform architecture.

- Requires organizational change to support separate block authoring and system chip integration.

Hence, PBD can be treated as a convergence design where previously separated functions are integrated. The pre-existing blocks can be accurately estimated and the

design variability limited to the new blocks and the interface architecture. It requires organizational support to create a PBD.

# 2.2 Open Core Based SOC Design Platform

On the other hand, a new concept that is gaining interest is the Open Core SOC design methodology which publishes all necessary information about the hardware [3]. This is termed as open hardware. All the information regarding the hardware is disclosed for free, according to the term of GPL/LGPL license. Open Core [4] group has provided many pre-synthesized and pre-verified hardware core for the designer. These cores are well documented with design specifications, RTL codes, and simulation test benches and therefore can be re-used for different applications. Making a design compatible with an on-chip bus interface is one way to produce re-usable design. Different IP cores developed independently can be tied together and tested by standardizing the IP core interfaces. Many re-usable digital designs available in the Open Core site are compatible with a standard on-chip interface called WISHBONE [5] bus interface. More than 800 projects are available in open core site. Some of them are Open RISC1200 processor, VGA controller, USB 2.0, memory controller, UART, MAC, PCI and many DSP functionality cores. The designer has to collect the IP cores from the site and integrate it into the design to complete the SOC design. All these cores are available at no cost and are reusable. Hence it helps in producing low cost, portable, reliable, time-to-market SOC design. The EDA tools used to develop open hardware are also open. Hence in Open Core SOC design methodology openness of resources is a key factor to develop design reuse and improve the productivity of SOC designs.

# 2.3 The Objective behind WISHBONE

The WISHBONE System-on-Chip (SOC) Interconnection is a method for connecting IP cores together to form integrated circuits. Open core SOC design methodology utilizes WISHBONE bus interface to foster design reuse by alleviating system-on-chip integration problems. With use of this standardize bus interface it is much easier to connect the cores, and therefore much easier to create a custom System-on-Chip. This way of SOC design improves the portability and reliability of the system, and results in faster time-to-market for the end user. The objective behind WISHBONE is to create a

portable interface that supports both FPGA and ASIC that is independent of the semiconductor technology and WISHBONE interfaces should be independent of logic signaling levels. Another important reason is to create a flexible interconnection scheme that is independent of the type of IP core delivery (Hard, Soft IP) method. The next reasons are to have a standard interface that can be written using any hardware description language such as VHDL and VERILOG®. It supports a variety of bus transfer cycle in which the data transaction is independent of the application specific functions of the IP cores. It also supports different types of interconnection architectures with theoretically infinite range of operating frequency [5]. The final objective of WISHBONE bus is that it is absolutely free to use by developers without paying any fee for the cores available.

### 2.4 WISHBONE Basics

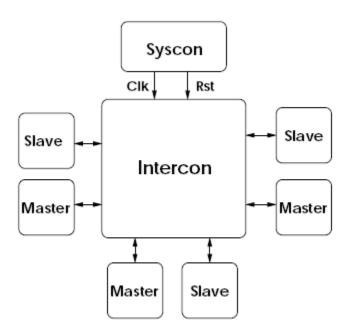

WISHBONE utilizes "Master" and "Slave" architectures which are connected to each other through an interface called "Intercon". Master is an IP core that initiates the data transaction to the SLAVE IP core.

Figure: 2. 1 WISHBONE Intercon system

Master starts transaction providing an address and control signal to Slave. Slave in turn responds to the data transaction with the Master with the specified address range.

The Intercon is the medium consists of wires and logics which help in data transfer between Master and Slave. The Intercon also requires a "SYSCON" module which generates WISHBONE reset and clock signal for the proper functioning of the system. Figure: 2.1 show the WISHBONE Intercon system which consists of Masters and Slaves and SYSCON modules. WISHBONE Intercon can be designed to operate over an infinite frequency range. This is called as *variable time specification*. The speed of the operation is only limited by the technology of the integrated circuits. The interconnection can be described using hardware description languages like VHDL and Verilog®, and the system integrator can modify the interconnection according to the requirement of the design. Hence WISHBONE interface is different from traditional microcomputer buses such as PCI, VME bus and ISA bus.

# 2.5 WISHBONE Interface Specification

WISHBONE Interface specification specifies the signaling method used by Master and Slave interface and the SYSCON module. It also specifies the way to create a proper documentation for the WISHBONE Compatible IP cores which is the main driving factor for design reuse.

#### 2.5.1 Documentation for IP Cores

As specified above each WISHBONE Compatible IP cores must be supplied with a WISHBONE datasheet, which describes the interface of the cores. This datasheet helps in understanding the operation of the cores, and the user can reuse these cores to integrate with other cores to produce System on a Chip. The WISHBONE datasheet must include the following information:

- The revision level of the WISHBONE specification after which it is designed.

- If the IP designed is a Master or Slave IP core.

- The signal names used in the design must be defined. If any signal name different than that defined in the specification, must have a cross reference to the original signal of the specification.

- If a Master supports a retry and error signal, then it must specify how they react in response to the signals. If a Slave supports retry and error signal, then it must specify under which conditions the signal must be generated.

- The design supporting tag signals must specify the name, TAG TYPE and operation of the tag.

- The port size must be 8-bit, 16-bit, 32-bit or 64-bit.

- The maximum operand size used must be 8-bit, 16-bit, 32-bit or 64-bit.

- The data transfer ordering such as LITTLE ENDIAN or BIG ENDIAN must be specified.

- Any constraints on the clock signal [CLK\_I] must be specified in terms of clock frequency, application specific timing constraints, use of gated clocks or use of variable clock generators.

# 2.5.2 WISHBONE Interface Signal

WISHBONE interface signals and bus cycles are design in a reusable manner, so that the WISHBONE Master and Slave interfaces can be connected together using several interconnection methods. These signals are classified into three categories, *Master signals, Slave signals, and signals common to both Masters and Slaves*. These entire interface signals must be active high logic.

The signal definitions must follow these requirements:

- The signal must allow Master and Slave to use variable interconnections.

- The signals must support all the basic types of bus cycle.

- A handshaking mechanism must be used for either the Master or the participating

Slave interface to adjust the data transfer rate.

- Every interface must support acknowledgement signal but the retry and error acknowledgement signals are optional.

- Address and data bus widths can be altered to fit different applications like 8-bit,

16-bit, 32-bit and 64-bit data buses.

- All the signals should be either output or input. The signals may be bidirectional,

if the target device supports it.

The Tables: 2.1, 2.2 and 2.3 below show the descriptions of these three types of signals. The optional requirement of the signal is also specified in the table.

| Signal  | Name           | Description                            | Optional |

|---------|----------------|----------------------------------------|----------|

| ACK_I   | Acknowledge    | When asserted, indicates the           | No       |

|         | input          | normal termination of a bus cycle.     |          |