# Pico Blaze

# KCPSM3

8-bit Micro Controller for Spartan-3, Virtex-II and Virtex-IIPRO

For Spartan-II(E) and Virtex(E) please use KCPSM Virtex-II and Virtex-IIPro are also supported by KCPSM2

Ken Chapman Xilinx Ltd

October 2003 Rev.7

### **Contents**

### **Understanding KCPSM3**

- 1 Title

- 2 Contents page

- 3 Limitations

- 4 What is KCPSM3?

- 5-6 KCPSM3 is small

- 7 Size and Performance

- 8 KCPSM3 Architecture

- 9-11 KCPSM3 Feature Set

- 12 Constant (k) Coded

- 13 Using KCPSM3 (VHDL)

- 14 Connecting the Program ROM

- 15 Verilog and System Generator

### **Instruction Set**

- 16 KCPSM3 Instruction Set

- 17 JUMP

- 18 CALL

- 19 RETURN

- 20 RETURNI

- 21 ENABLE/DISABLE INTERRUPT

- 22 LOAD

- 23 AND

- 24 OR

- 25 XOR

- 26 TEST

- 27 ADD

- 28 ADDCY

- 29 SUB

- 30 SUBCY

- 31 COMPARE

- 32 SR0, SR1, SRX, SRA, RR

- 33 SL0, SL1, SLX, SLA, RL

- 34 OUTPUT

- 35 INPUT

- 36 STORE

- 37 FETCH

### **Interface Signals**

- 38 READ and WRITE STOBES

- 39 RESET

### **KCPSM3 Assembler**

- 40 KCPSM3 Assembler Basic usage.

- 41 Assembler Errors

- 42 Assembler Files

- 43 ROM form.vhd File

- 44 ROM form.v File

- 45 ROM\_form.coe File

- 46 <filename>.fmt File

- 47 <filename>.log file

- 48 constant.txt & labels.txt Files

- 49 pass.dat files

- 50-51 Program Syntax

- 52 CONSTANT Directive

- 53 NAMEREG Directive

- 54 ADDRESS Directive

- 55 KCPSM and KCPSM2 Compatibility

- 56 PicoBlaze Comparison

### **Interrupts and worked example**

- 57 Interrupt Handling

- 58 Basics of Interrupt Handling

- 59 Example Design (VHDL)

- 60 Interrupt Service Routine

- 61 Interrupt Operation

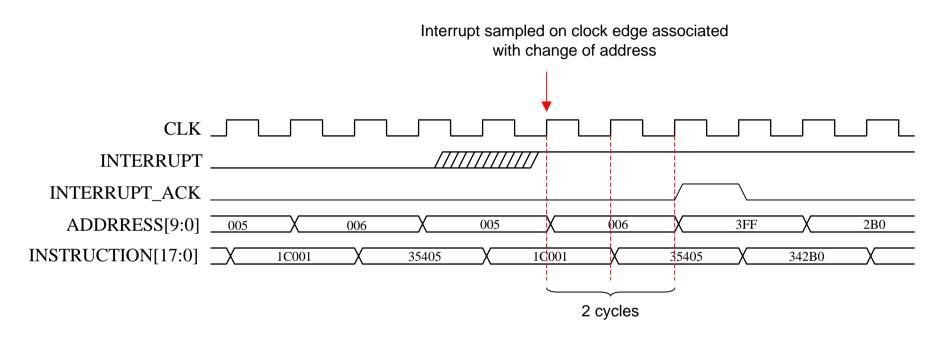

- 62 Timing of Interrupt Pluses

### **Hints and Tips**

- 63 CALL/RETURN Stack

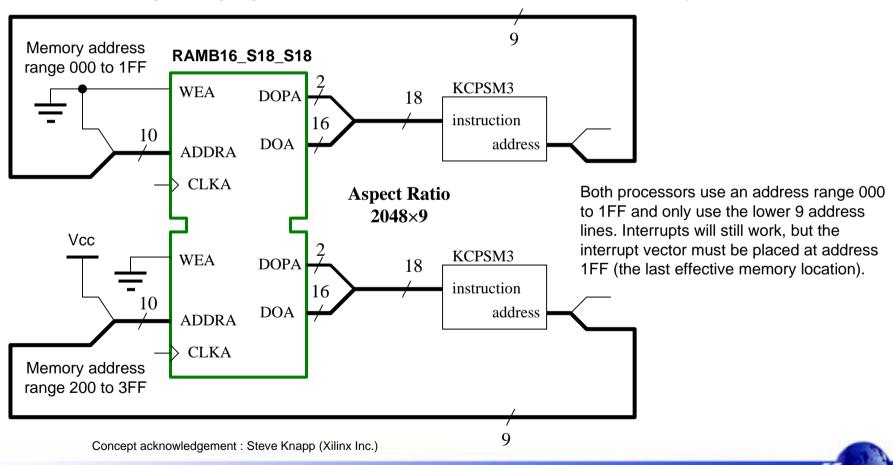

- 64 Sharing program space

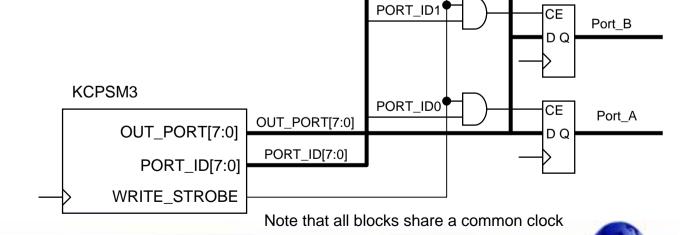

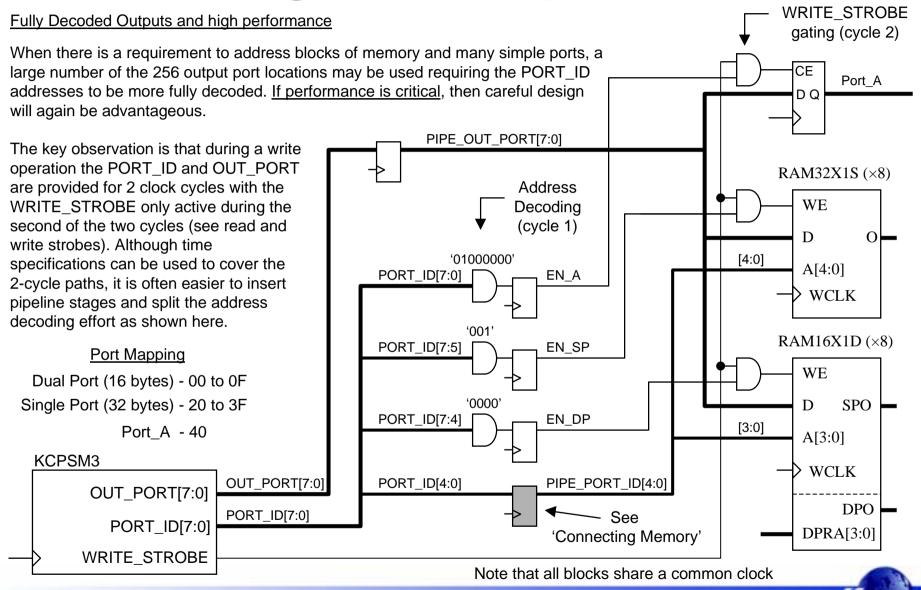

- 65-66 Design of Output Ports

- 67-68 Design of Input Ports

- 69 Connecting Memory

- 70 Simulation of KCPSM3

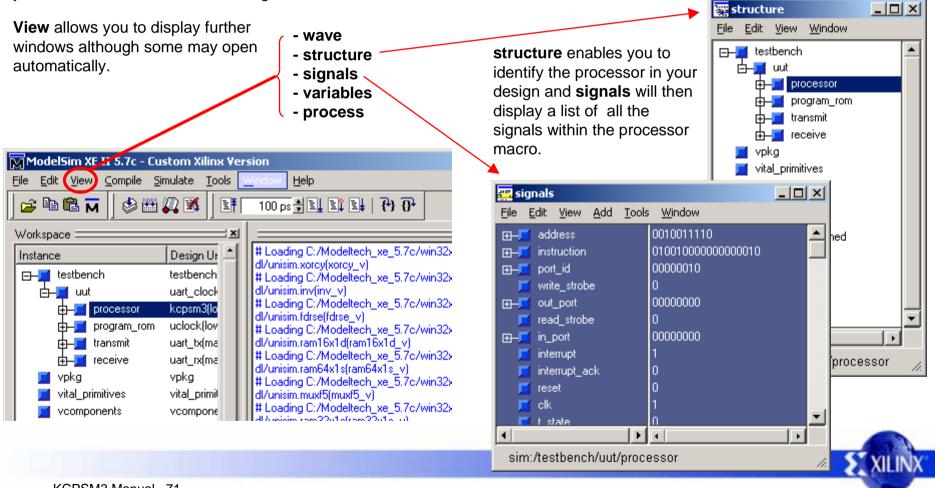

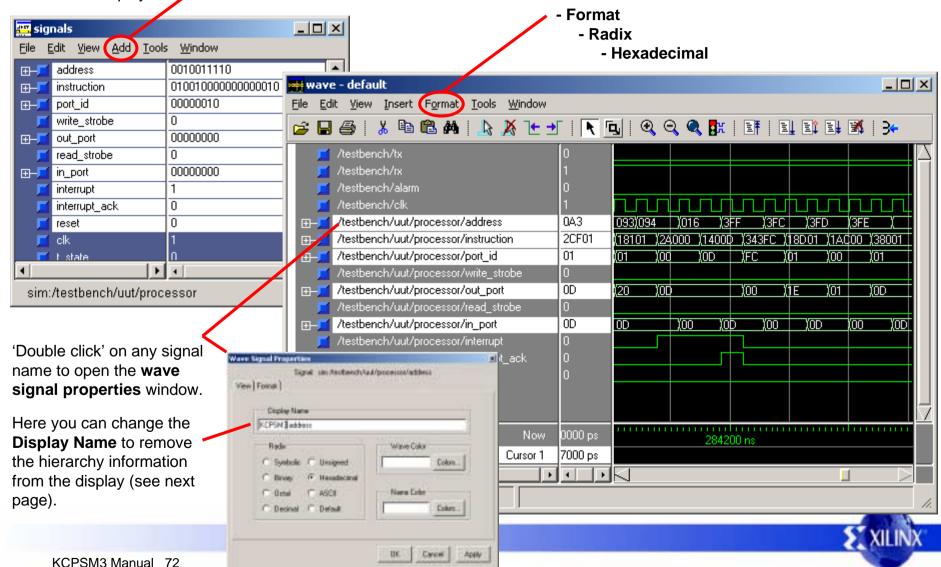

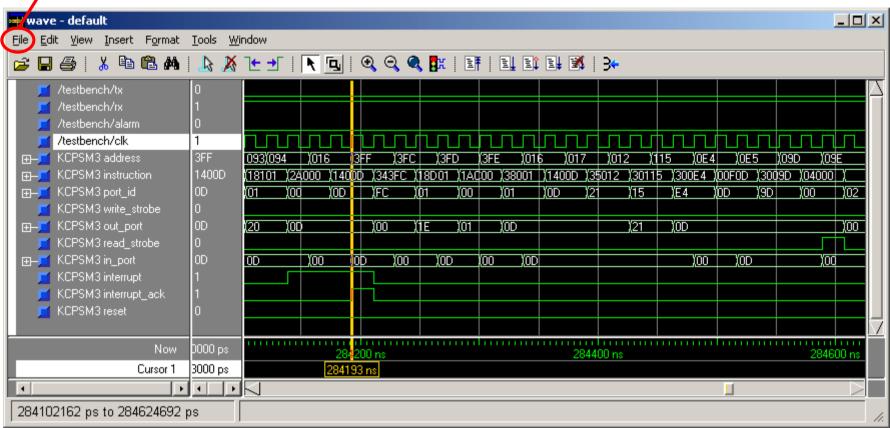

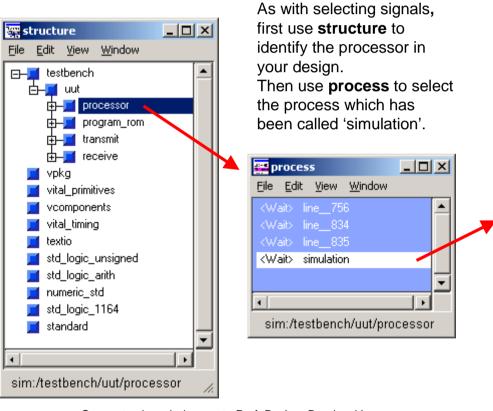

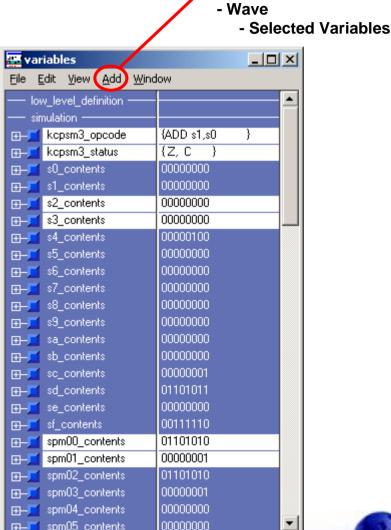

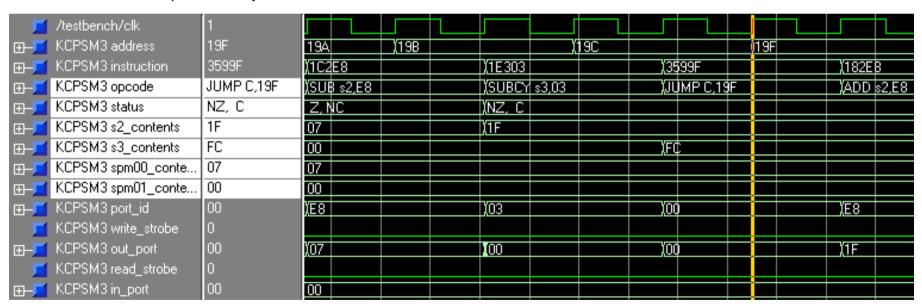

- 71-75 VHDL Simulation

### Limitations

**Limited Warranty and Disclaimer**. These designs are provided to you "as is". Xilinx and its licensors make and you receive no warranties or conditions, express, implied, statutory or otherwise, and Xilinx specifically disclaims any implied warranties of merchantability, non-infringement, or fitness for a particular purpose. Xilinx does not warrant that the functions contained in these designs will meet your requirements, or that the operation of these designs will be uninterrupted or error free, or that defects in the Designs will be corrected. Furthermore, Xilinx does not warrant or make any representations regarding use or the results of the use of the designs in terms of correctness, accuracy, reliability, or otherwise.

**Limitation of Liability**. In no event will Xilinx or its licensors be liable for any loss of data, lost profits, cost or procurement of substitute goods or services, or for any special, incidental, consequential, or indirect damages arising from the use or operation of the designs or accompanying documentation, however caused and on any theory of liability. This limitation will apply even if Xilinx has been advised of the possibility of such damage. This limitation shall apply not-withstanding the failure of the essential purpose of any limited remedies herein.

This module is <u>not</u> supported by general Xilinx Technical support as an official Xilinx Product. Please refer any issues initially to the provider of the module.

Any problems or items felt of value in the continued improvement of KCPSM3 would be gratefully received by the author.

Ken Chapman Senior Staff Engineer - Applications Specialist email: chapman@xilinx.com

The author would also be pleased to hear from anyone using KCPSM or KCPSM2 with information about your application and how these macros have been useful.

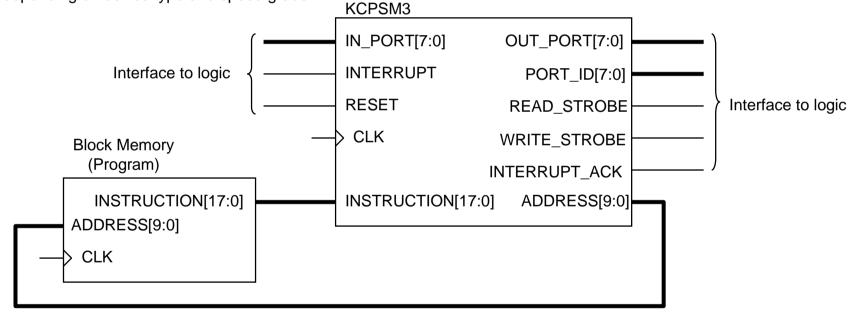

### What is KCPSM3?

KCPSM3 is a very simple 8-bit microcontroller primarily for the Spartan-3 devices but also suitable for use in Virtex-II and Virtex-IIPRO devices. Although it could be used for processing of data, it is most likely to be employed in applications requiring a complex, but non-time critical state machine. Hence it has the name of '(K)constant Coded Programmable State Machine'.

This revised version of popular KCPSM macro has still been developed with one dominant factor being held above all others - Size! The result is a microcontroller which occupies just **96 Spartan-3 Slices** which is just 5% of the XC3S200 device and less than 0.3% of the XC3S5000 device. Together with this small amount of logic, a single block RAM is used to form a ROM store for a program of up to 1024 instructions. Even with such size constraints, the performance is respectable at approximately **43 to 66 MIPS** depending on device type and speed grade.

One of the most exciting features of the KCPSM3 is that it is totally embedded into the device and requires no external support. The very fact that ANY logic can be connected to the module inside the Spartan-3 or Virtex-II device means that any additional features can be added to provide ultimate flexibility. It is not so much what is inside the KCPSM3 module that makes it useful, but the environment in which it lives.

## KCPSM3 is small!

KCPSM3 is supplied as VHDL and as a pre-compiled soft macro which is handled by the place and route tools to merge with the logic of a design. In large devices, the KCPSM3 is virtually free! The potential to place multiple KCPSM3 within a single design is obvious. Whenever a non time critical complex state machine is required, this macro is easy to insert and greatly simplifies design.

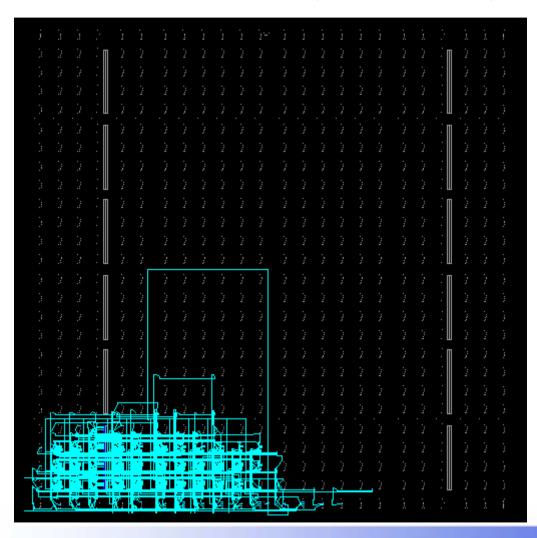

This plot from the FPGA Editor viewer shows the macro in isolation within the XC3S200 Spartan-3 device.

96 Slices

5% of XC3S200 Spartan-3 device

~87MHz in -4 Speed Grade

~43.5 MIPS

## KCPSM3 is small!

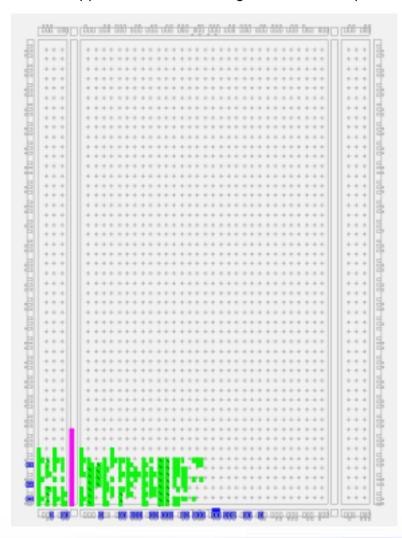

This plot from the Xilinx Floorplanner shows the same implementation of KCPSM3 in an XC3S200 Spartan-3 device. This makes it easier to appreciate the actual logic resources required by the macro without the interconnect obscuring the detail.

The placement in this Floorplanner view was achieved using a simple area constraint in the project UCF file.

```

INST processor_* LOC=SLICE_X0Y0:SLICE_X19Y4;

```

Such constraints are not required in normal designs and it has only been used in this case because so little of the device is occupied. Experiments have shown that placement constraints have very little effect on performance.

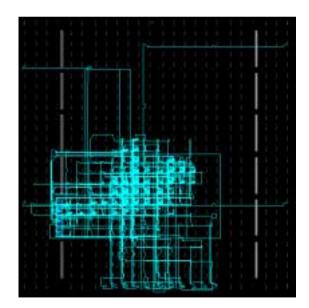

The FPGA Editor view shown to the right was the result when no constraints were used. The size is still 96 slices but this is now a little less obvious! The performance was actually a little higher than when using the area constraint indicating that a 'tidy' design is not always the fastest!

## Size and Performance

The following device resource information is taken from the ISE reports for the KCPSM3 macro in an XC3S200 device. The reports reveal the features that are utilised and the efficiency of the macro. The 96 'slices' reported by the MAP process in this case may reduce to the minimum of 89 'slices' when greater packing is used to fit a complete design into a device.

### **XST Report**

### LUT1 : 2 LUT2 : 6 LUT3 : 68 (55 slices)

LUT4 : 33

MUXCY : 39

MUXF5 : 9

XORCY : 35

Carry and MUX logic (Free with LUTs)

FDE : 24

FDE : 2

FDR : 30

FDRE : 8

FDRGE : 8

FDRSE : 10 FDS : 2

RAM16X1D

RAM32X1S : 10 — Call/Return Stack (10 slices)

RAM64X1S : 8 — Scratch Pad Memory (16 slices)

Total = 89 Slices

: 8 — Register bank (8 slices)

### **MAP Report**

Number of occupied Slices: 96 out of 1920 5% Number of Block RAMs: 1 out of 12 8% Total equivalent gate count for design: 74,814

12 x KCPSM3 can fit into the XC3S200 device (40% of the logic slices remaining). An equivalent gate count of 897,768 gates in a 200,000 gate device!

### **TRACE Report**

Device, speed: xc3s200,-4 (PREVIEW 1.22 2003-03-16)

Minimum period: 11.403ns

(Maximum frequency: 87.696MHz)

43.8 MIPS

### TRACE Report for Virtex-IIPRO

Device, speed: xcvp2,-7 (ADVANCED 1.76 2003-03-16)

Minimum period: 7.505ns

(Maximum frequency: 133.245MHz) 66.6 MIPS

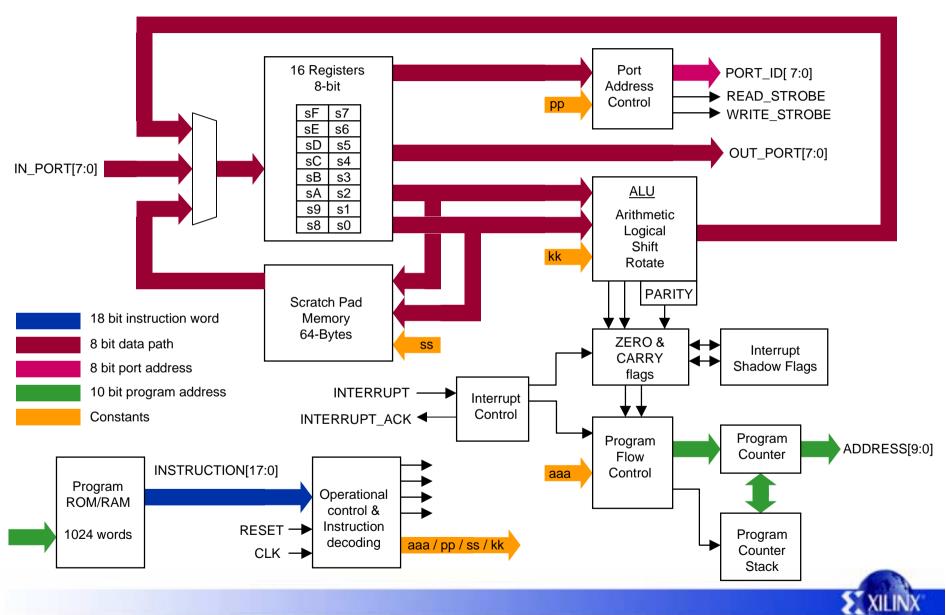

## **KCPSM3** Architecture

### **KCPSM3** Feature Set

#### Features new to KCSPM3

KCPSM3 is a very simple processor architecture and anyone familiar with PSM, KCSPM or KCSPM2 will recognise that this is just the latest in a close family of 8-bit programmable state machines (see 'PicoBlaze Comparison'). The motivation to develop this variant was the release of Spartan-3 devices and the highly constructive feedback from so many users of its predecessors.

Spartan-3 has adopted the 18Kbit Block RAM elements previously seen in the Virtex-II devices. This enables KCPSM3 to support programs up to 1024 locations which overcomes the most commonly encountered limit of KCPSM with Spartan-II(E).

At the risk of making KCPSM3 appear more complex than previous versions, some additional features have been included to address the most popular requests. COMPARE and TEST instructions enable register contents to be interrogated without changing their contents. The TEST instruction also calculates PARITY, useful for many communication applications. A 64-byte internal scratch pad memory allows many more variables to be held internally, more intuitive programs to be written and will typically eliminate requirement for memory attached to the I/O ports. Finally, an interrupt acknowledgement signal is provided.

The additional features make KCPSM3 26% larger than KCPSM and 14% larger than KCPSM2. However, It is expected that the additional features will enable more efficient programs to be written and for designs to require less peripheral logic.

#### **Program Size**

KCPSM3 supports a program up to a length of 1024 instructions utilising one block memory. Requirements for larger program space are typically addressed by using multiple KCPSM3 processors each with an associated block memory to distribute the various system tasks. Programs requiring significantly more memory are normally the domain of a full data processor such as MicroBlaze with its C-language programming support.

#### 16 General Purpose Registers.

There are 16 general purpose registers of 8-bits specified as 's0' through to 'sF' which may be renamed in the assembler code. All operations are completely flexible about the use of registers with no registers reserved for special tasks or having any priority over any other register. There is no accumulator as any register can be adopted for this task.

### **KCPSM3** Feature Set

#### ALU

The Arithmetic Logic Unit (ALU) provides many simple operations expected in an 8-bit processing unit.

All operations are performed using an operand provided from any register (sX). The result is returned to the same register. For operations requiring a second operand, a second register can be specified (sY) or a constant 8-bit value (kk) can be supplied. The ability to specify any constant value with no additional penalty to program size or performance enhances the simple instruction set i.e. the ability to 'ADD 1' is the same as a dedicated INCREMENT operation.

Addition (ADD) and Subtraction (SUB) have the option to include the carry flag as an input (ADDCY and SUBCY) for the support of arithmetic operations requiring more than 8-bits.

LOAD, AND, OR and XOR bit-wise operators provide ability to manipulate and test values.

Comprehensive SHIFT and ROTATE group.

COMPARE and TEST instructions enable register contents to be tested without altering their contents and determine PARITY.

#### Flags and Program Flow Control

The results of ALU operations determine the status of the ZERO and CARRY flags. The ZERO flag is set whenever the ALU result has all bits reset  $(00_{16})$ . The CARRY flag is set when there is an overflow from an arithmetic operation. It is also used to capture the bit moved out of a register during shift and rotate instructions. During a TEST instruction, the carry flag is used to indicate if the 8-bit temporary result has ODD PARITY.

This status of the flags can be used to determine the execution sequence of the program using conditional and non-conditional program flow control instructions. JUMP commands are used to specify absolute addresses (aaa) within the program space. CALL and RETURN commands provide sub-routine facilities for commonly used sections of code. A CALL is made to an absolute address (aaa) and an internal program counter stack preserves the associated address required by the RETURN instruction. The stack supports up to 31 nested subroutine levels.

#### Reset

The RESET input forces the processor back into the initial state. The program will execute from address '000' and interrupts will be disabled. The status flags and CALL/RETURN stack will also be reset. Note that register contents are not affected.

# **KCPSM3** Feature Set

#### Input/Output

KCPSM3 effectively has 256 input ports and 256 output ports. The port being accessed is indicated by an 8-bit address value provided on the 'PORT\_ID'. The port address can be specified in the program as an absolute value (pp), or may be indirectly specified as the contents of any of the 16 registers ( (sY) ).

During an 'INPUT' operation the value provided at the input port is transferred into any of the 16 registers. An input operation is indicated by a pulse being output on the READ\_STROBE. It is not always necessary to use this signal in the input interface logic, but it can be useful to indicate that data has been acquired by the processor. During an 'OUTPUT', the contents of any of the 16 registers are transferred to the output port. An output operation is indicated by a pulse being output on the WRITE\_STROBE. This strobe signal will be used by the interface logic to ensure that only valid data is passed to external systems. Typically, WRITE\_STROBE will be used as a clock enable or write enable (see 'READ and WRITE STROBES').

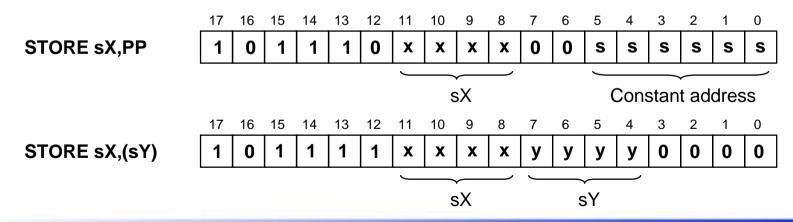

#### **Scratch Pad Memory**

This is an internal 64 byte general purpose memory. The contents of any of the 16 registers can be written to any of the 64 locations using a STORE instruction. The complementary FETCH instruction allows the contents of any of the 64 memory locations to be written to any of the 16 registers. This allows a much greater number of variables to be held within the boundary of the processor and tends to reserve all of the I/O space for real inputs and output signals.

The 6-bit address to specify a scratch pad memory location can be specified in the program as an absolute value (ss), or may be indirectly specified as the contents of any of the 16 registers (sY). Only the lower 6-bits of the register are used, so care must be taken not to exceed the 00 - 3F<sub>16</sub> range of the available memory.

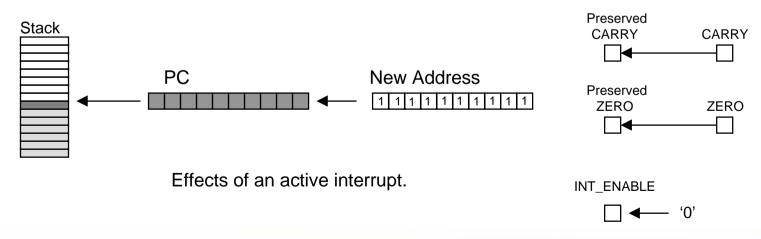

#### Interrupt

The processor provides a single INTERRUPT input signal. Simple logic can be used to combine multiple signals if required. Interrupts are disabled (masked) by default, and are then enabled and disabled under program control. An active interrupt forces KCPSM3 to initiate a 'CALL 3FF' (a subroutine call to the last program memory location) from where the user can define a suitable jump vector to an Interrupt Service Routine (ISR). At this time, a pulse is generated on the INTERRUPT\_ACK output, the ZERO and CARRY flags are automatically preserved and any further interrupts are disabled. The 'RETURNI' instruction ensures that the end of an ISR restores the status of the flags and specifies if future interrupts will be enabled or disabled.

# Constant(k) Coded

The KCPSM3 is in many ways a machine based on Constants......

#### **Constant Values**

Constant values may be specified for use in most aspects of a program....

- Constant data value for use in an ALU operation.

- Constant port address to access a specific piece of information or control logic external to KCPSM3.

- Constant address values for controlling the execution sequence of the program.

- Constant address values for accessing internal scratch pad memory.

The KCPSM3 instruction set coding has been designed to allow constants to be specified within any instruction word. Hence the use of a constant carries no additional overhead to the program size or its execution. This effectively extends the simple instruction set with a whole range of 'virtual instructions'.

#### **Constant Cycles**

<u>All</u> instructions under <u>all</u> conditions will execute over <u>2 clock cycles</u>.

Such constant execution rate is of great value when determining the execution time of a program particularly when embedded into a real time situation.

#### **Constant Program Length**

The program length is 1024 instructions and therefore conforms to the 1024x18 format of a single Spartan-3, Virtex-II or Virtex-IIPRO Block RAM. This means that all address values are specified as 10-bits contained within the instruction coding (the assembler supports line labels to simplify the writing of programs). The fixed memory size promotes a consistent level of performance from the module. See also 'Sharing Program Space'.

# **Using KCPSM3 (VHDL)**

The principle method by which KCPSM3 will be used is in a VHDL design flow. The KCPSM3 macro is provided as source VHDL (kcspm3.vhd) which has been written to provide an optimum and predictable implementation in a Spartan-3 or Virtex-II(PRO) device. The code is suitable for implementation and simulation of the macro. It has been developed and tested using XST for implementation and ModelSim for simulation. The code should not be modified in any way.

VHDL Component declaration of KCPSM3

VHDL Component instantiation of KCPSM3

# Connecting the Program ROM

The principle method by which KCPSM3 program ROM will be used is in a VHDL design flow. The KCPSM3 assembler will generate a VHDL file in which a block RAM and its initial contents are defined (see assembler notes for more detail). This VHDL can be used for implementation and simulation of the processor. It has been developed and tested using XST for implementation and ModelSim for simulation.

VHDL Component declaration of program ROM

VHDL Component instantiation of program ROM

```

program: prog_rom

port map(          address => address_signal,

instruction => instruction_signal,

clk => clk_signal);

```

Note - The name of the program ROM (shown as 'prog\_rom' in the above examples) will depend on the name of your program. For example, if your program file was called 'phone.psm', then the assembler will generate a program ROM definition file called 'phone.vhd'.

To aid with development, a VHDL file called 'embedded\_kcpsm3.vhd' is also supplied in which the KCPSM3 macro is connected to its associated block RAM program ROM. This entire module can be embedded in the design application, or simply used to cut and paste the component declaration and instantiation information into your own code.

Note: It is recommended that 'embedded\_kcpsm3.vhd' is used for the generation of an ECS schematic symbol.

# Verilog and System Generator

Although the primary design flow is VHDL, KCPSM3 can be used in any design flow supported by Xilinx. The assembler also generates program memory definition files suitable for Verilog and the Simulink based System Generator design flows.

<filename>.v - The assembler generates a Verilog file in which a block RAM and its initial contents are defined (see assembler notes for more detail). This Verilog can be used for implementation and simulation of the processor. The kcspm3.ngc file will be used to define the processor.

**kcpsm3.ngc** - The NGC file provided was generated by synthesising the kcpsm3.vhd file with XST (without inserting I/O buffers). This file can be used as a 'black box' in a Spartan-3, Virtex-II or Virtex-IIPRO design, and it will be merged with the rest of your design during the translate phase (ngdbuild). Note that busses are defined in the style 'IN\_PORT<7:0>' with individual signals 'in\_port\_0' through to 'in\_port\_7'.

<filename>.m - The assembler generates a m-function used to define the contents of a System Generator memory block within the MATLAB Simulink environment. (see System Generator documentation for more information on this design flow).

<filename>.coe - The COE file generated by the assembler is suitable for use with the Xilinx Core Generator. The file defines the initial contents of a block ROM. The files generated by Core Generator can then be used as normal in your chosen design flow and connected to the kcpsm3 'black box' in your design (see assembler notes for more details).

#### **Simulation Models**

If the NGC file is used in the design flow, then some form of back annotated description will be required for simulation of your design in order to fill in the 'black box' details. The following command can be used to generate a Verilog simulation model (see the Xilinx online manuals for more details - Synthesis and Simulation Design Guide - section 6).

ngd2ver kcspm3.ngd sim\_model\_kcpsm3.v

# **KCPSM3 Instruction Set**

<sup>&#</sup>x27;ss' represents an internal storage address in the range 00 to 3F.

| <b>Program Control Group</b>                                                                         | Arithmetic Group                                                                      | Logical Group                                                         | Shift and Rotate Group                                                       |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------|

| JUMP aaa<br>JUMP Z,aaa<br>JUMP NZ,aaa<br>JUMP C,aaa<br>JUMP NC,aaa                                   | ADD sX,kk ADDCY sX,kk SUB sX,kk SUBCY sX,kk COMPARE sX,kk                             | LOAD sX,kk AND sX,kk OR sX,kk XOR sX,kk TEST sX,kk                    | SR0 sX<br>SR1 sX<br>SRX sX<br>SRA sX<br>RR sX                                |

| CALL aaa<br>CALL Z,aaa<br>CALL NZ,aaa<br>CALL C,aaa<br>CALL NC,aaa                                   | ADD sX,sY ADDCY sX,sY SUB sX,sY SUBCY sX,sY COMPARE sX,sY                             | LOAD sX,sY AND sX,sY OR sX,sY XOR sX,sY TEST sX,sY                    | SLO sX<br>SL1 sX<br>SLX sX<br>SLA sX<br>RL sX                                |

| RETURN Z RETURN NZ RETURN C RETURN NC  Note that call and return supports up to a stack depth of 31. | Interrupt Group  RETURNI ENABLE  RETURNI DISABLE  ENABLE INTERRUPT  DISABLE INTERRUPT | Storage Group  STORE sX,ss  STORE sX,(sY)  FETCH sX,ss  FETCH sX,(sY) | Input/Output Group  INPUT sX,pp  INPUT sX,(sY)  OUTPUT sX,pp  OUTPUT sX,(sY) |

<sup>&#</sup>x27;X' and 'Y' refer to the definition of the storage registers 's' in the range 0 to F.

<sup>&#</sup>x27;kk' represents a constant value in the range 00 to FF.

<sup>&#</sup>x27;aaa' represents an address in the range 000 to 3FF.

<sup>&#</sup>x27;pp' represents a port address in the range 00 to FF.

### **JUMP**

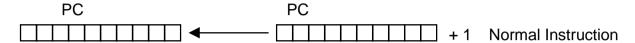

Under normal conditions, the program counter (PC) increments to point to the next instruction. The address space is fixed to 1024 locations (000 to 3FF hex) and therefore the program counter is 10 bits wide. It is worth noting that the top of memory is 3FF hex and will increment to 000.

The JUMP instruction may be used to modify this sequence by specifying a new address. However, the JUMP instruction may be conditional. A conditional JUMP will only be performed if a test performed on either the ZERO flag or CARRY flag is valid. The JUMP instruction has no effect on the status of the flags.

Each JUMP instruction must specify the 10-bit address as a 3 digit hexadecimal value. The assembler supports labels to simplify this process.

Bit 11 Bit 10 Condition

| 17 | 16       | 15 | 14     | 13         | 12    | 11  | 10  | 9    | 8   | 7 | 6 | 5 | 4        | 3 | 2 | 1        | 0        |   |   | if Zero      |

|----|----------|----|--------|------------|-------|-----|-----|------|-----|---|---|---|----------|---|---|----------|----------|---|---|--------------|

| 1  | 1        | 0  | 1      | 0          |       |     |     | а    | а   | а | а | а | а        | а | а | а        | а        | 0 | 1 | if NOT Zero  |

|    | <u> </u> |    | 1      | 1          |       |     |     |      |     |   |   |   | <u> </u> |   |   | <u> </u> | <u> </u> | 1 | 0 | if Carry     |

|    |          | j  | Bit 12 | <u>2</u> ( | ) - U | NCC | NDI | TION | IAL |   |   |   |          |   |   |          |          | 1 | 1 | if NOT Carry |

1 - CONDITIONAL

## CALL

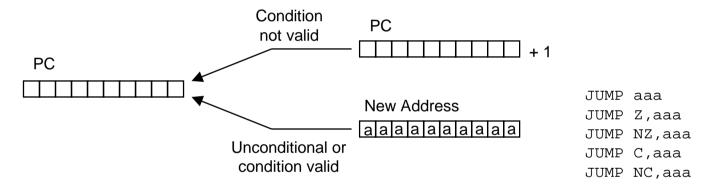

The CALL instruction is similar in operation to the JUMP instruction in that it will modify the normal program execution sequence by specifying a new address. The CALL instruction may also be conditional. In addition to supplying a new address, the CALL instruction also causes the current program counter (PC) value to be pushed onto the program counter stack. The CALL instruction has no effect on the status of the flags.

The program counter stack supports a depth of 31 address values. This enables nested 'CALL' sequences to a depth of 31 levels to be performed. However, the stack will also be used during an interrupt operation and hence at least one of these levels should be reserved when interrupts are enabled. The stack is implemented as a separate cyclic buffer. When the stack becomes full, it simply overwrites the oldest value. Hence it is not necessary to reset the stack pointer when performing a software reset. This also explains why there are no instructions to control the stack and why no other memory needs to be reserved or provided for the stack.

Each CALL instruction must specify the 10-bit address as a 3 digit hexadecimal value. The assembler supports labels to simplify this process.

Bit 11 Bit 10 Condition

|    |          |    |                                              |     |       |     |      |      |     |   |   |   |   |   |          |          |   | <u> </u> | <u> </u> | <u>condition</u> |

|----|----------|----|----------------------------------------------|-----|-------|-----|------|------|-----|---|---|---|---|---|----------|----------|---|----------|----------|------------------|

| 17 | 16       | 15 | 14                                           | 13  | 12    | 11  | 10   | 9    | 8   | 7 | 6 | 5 | 4 | 3 | 2        | 1        | 0 | . 0      | Ο        | if Zero          |

| 4  |          |    |                                              |     |       |     |      | l _  | _   | _ | _ |   |   |   |          |          |   | 0        |          |                  |

| 1  | 1        | 0  | 0                                            | 0   |       |     |      | a    | a   | a | a | a | a | a | a        | a        | a | 0        | 1        | if NOT Zero      |

|    | <u> </u> |    | <u>.                                    </u> | !   |       |     |      |      | !   | ! | ! | ! | ! | ! | <u>!</u> | <u>!</u> | ! | 1        | 0        | if Carry         |

|    |          | I  | 3it 12                                       | 2 ( | ) - U | NCC | )NDI | TION | IAL |   |   |   |   |   |          |          |   | 1        | 1        | if NOT Carry     |

**EXILINX**

1 - CONDITIONAL

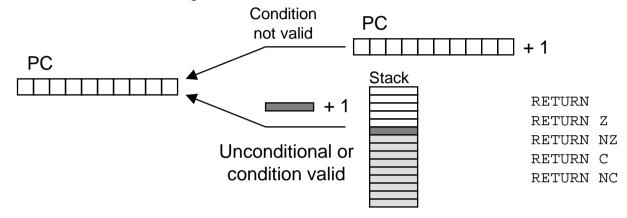

### **RETURN**

The RETURN instruction is the complement to the CALL instruction. The RETURN instruction may also be conditional. In this case the new program counter (PC) value will be formed internally by incrementing the last value on the program address stack. This ensures that the program will execute the instruction following the CALL instruction which resulted in the subroutine. The RETURN instruction has no effect on the status of the flags.

It is the responsibility of the programmer to ensure that a RETURN is only performed in response to a previous CALL instruction such that the program counter stack contains a valid address. The cyclic implementation of the stack will continue to provide values for RETURN instructions which can not be defined.

| 17 |   |   |   |   | <br> | <br> |   |   |   |   |   |   |   |   |   |

|----|---|---|---|---|------|------|---|---|---|---|---|---|---|---|---|

| 1  | 0 | 1 | 0 | 1 |      | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bit 12 0 - UNCONDITIONAL 1 - CONDITIONAL

| <u>Bit 11</u> | <u>Bit 10</u> | <u>Condition</u> |

|---------------|---------------|------------------|

| 0             | 0             | if Zero          |

| 0             | 1             | if NOT Zero      |

| 1             | 0             | if Carry         |

| 1             | 1             | if NOT Carry     |

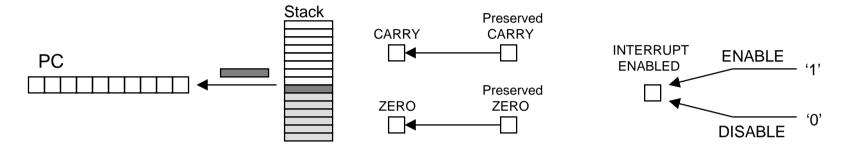

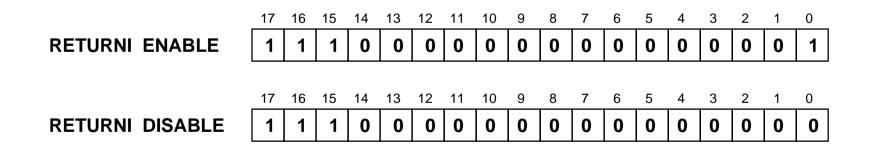

### **RETURNI**

The RETURNI instruction is a special variation of the RETURN instruction which should be used to conclude an interrupt service routine. The RETURNI is unconditional and therefore will always load the program counter (PC) with the last address on the program counter stack (the address is not incremented in this case since the instruction at the address stored will need to be executed). The RETURNI instruction restores the flags to the condition they were in at the point of interrupt. The RETURNI also determines the future ability of interrupts using ENABLE and DISABLE as an operand.

It is the responsibility of the programmer to ensure that a RETURNI is only performed in response to an interrupt. Each RETURNI must specify if further interrupt is to be enabled or disabled.

# **ENABLE/DISABLE INTERRUPT**

These instructions are used to set and reset the INT\_ENABLE flag. Before using ENABLE INTERRUPT a suitable interrupt routine must be associated with the interrupt address vector (located at address 3FF). Interrupts should never be enabled whilst performing an interrupt service routine.

Interrupts are masked when the INT\_ENABLE flag is low. This is the default state of the flag following device configuration or a KCPSM3 reset. The INT\_ENABLE is also reset during an active interrupt.

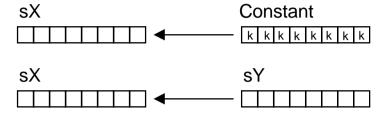

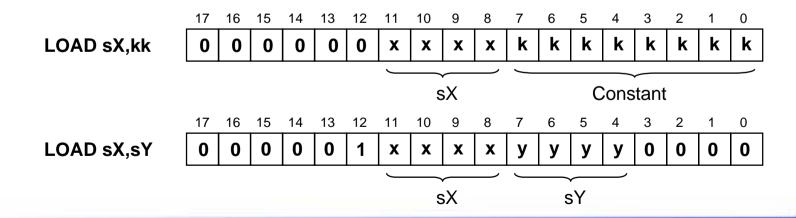

### LOAD

The LOAD instruction provides a method for specifying the contents of any register. The new value can be a constant, or the contents of any other register. The LOAD instruction has no effect on the status of the flags.

Since the LOAD instruction does not effect the flags it may be used to reorder and assign register contents at any stage of the program execution. The ability to assign a constant with no impact to the program size or performance means that the load instruction is the most obvious way to assign a value or clear a register.

The first operand of a LOAD instruction must specify the register to be loaded as register 's' followed by a hexadecimal digit. The second operand must then specify a second register value in a similar way or specify an 8-bit constant using 2 hexadecimal digits. The assembler supports register naming and constant labels to simplify the process.

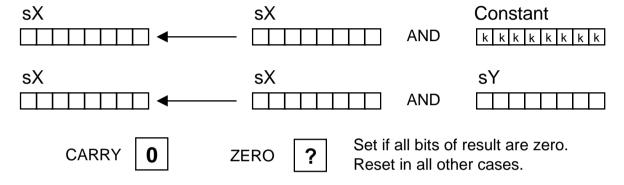

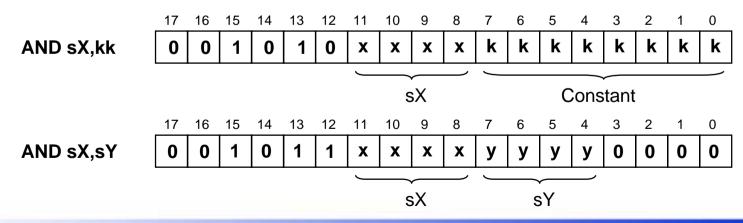

### **AND**

The AND instruction performs a bit-wise logical 'AND' operation between two operands. For example 00001111 AND 00110011 will produce the result 00000011. The first operand is any register, and it is this register which will be assigned the result of the operation. A second operand may also be any register or an 8-bit constant value. Flags will be effected by this operation. The AND operation is useful for resetting bits of a register and performing tests on the contents (see also TEST instruction). The status of the ZERO flag will then control the flow of the program.

Each AND instruction must specify the first operand register as 's' followed by a hexadecimal digit. This register will also form the destination for the result. The second operand must then specify a second register value in a similar way or specify an 8-bit constant using 2 hexadecimal digits. The assembler supports register naming and constant labels to simplify the process.

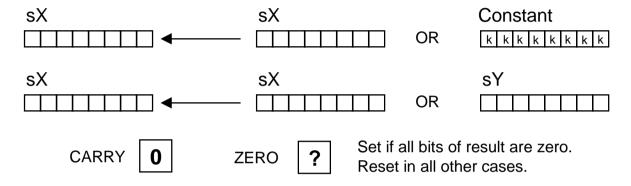

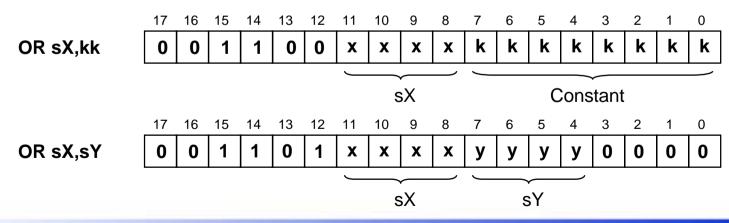

### OR

The OR instruction performs a bit-wise logical 'OR' operation between two operands. For example 00001111 OR 00110011 will produce the result 00111111. The first operand is any register, and it is this register which will be assigned the result of the operation. A second operand may also be any register or an 8-bit constant value. Flags will be effected by this operation. OR provides a way to force any bits of the specified register to be set which can be useful in forming control signals.

Each OR instruction must specify the first operand register as 's' followed by a hexadecimal digit. This register will also form the destination for the result. The second operand must then specify a second register value in a similar way or specify an 8-bit constant using 2 hexadecimal digits. The assembler supports register naming and constant labels to simplify the process.

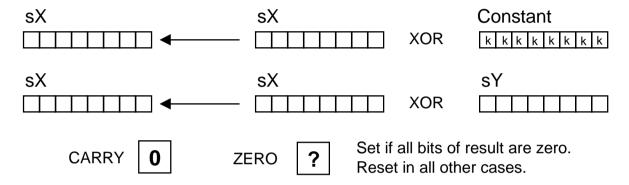

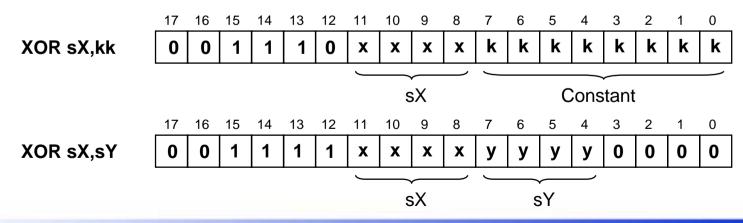

## **XOR**

The XOR instruction performs a bit-wise logical 'XOR' operation between two operands. For example 00001111 XOR 00110011 will produce the result 00111100. The first operand is any register, and it is this register which will be assigned the result of the operation. A second operand may also be any register or an 8-bit constant value. Flags will be effected by this operation. The XOR operation is useful for inverting bits contained in a register which is useful in forming control signals.

Each XOR instruction must specify the first operand register as 's' followed by a hexadecimal digit. This register will also form the destination for the result. The second operand must then specify a second register value in a similar way or specify an 8-bit constant using 2 hexadecimal digits. The assembler supports register naming and constant labels to simplify the process.

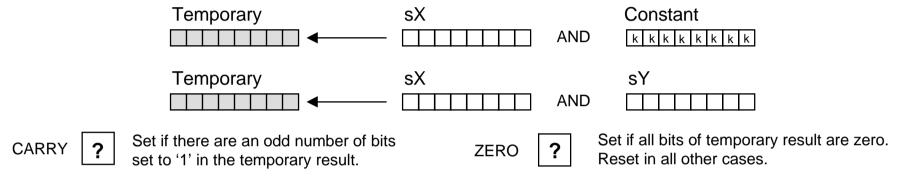

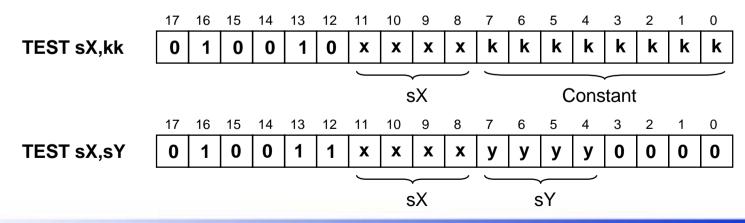

### **TEST**

The TEST instruction performs a bit-wise logical 'AND' operation between two operands. Unlike the 'AND' instruction, the result of the operation is discarded and only the flags are affected. The ZERO flag is set if all bits of the temporary result are low. The CARRY flag is used to indicate the **ODD PARITY** of the temporary result. Parity checks typically involve a test of all bits, i.e. if the contents of 's5' = 3D (00111101), the execution of TEST s5,FF will set the CARRY flag indicating ODD parity. Bit testing is typically used to isolate a single bit. For example TEST s5,04 will test bit2 of the 's5' register which would set the CARRY flag if the bit is high (reset if the bit is low) and set the ZERO flag if the bit is low (reset if the bit is high).

Each TEST instruction must specify the first operand register as 's' followed by a hexadecimal digit. The second operand must then specify a second register value in a similar way or specify an 8-bit constant using 2 hexadecimal digits. The assembler supports register naming and constant labels to simplify the process.

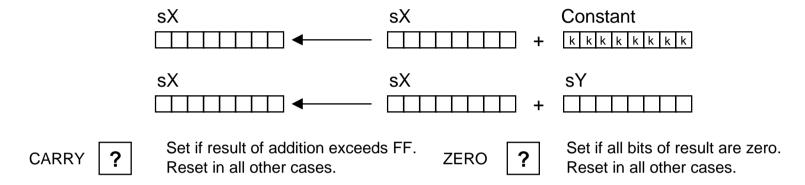

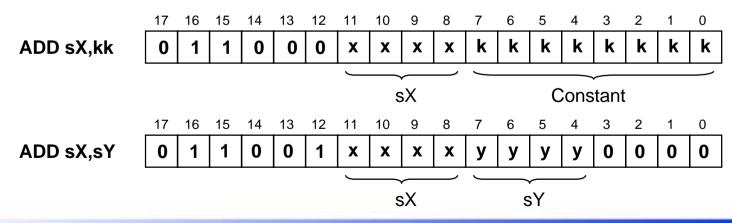

### **ADD**

The ADD instruction performs an 8-bit addition of two operands. The first operand is any register, and it is this register which will be assigned the result of the operation. A second operand may also be any register or an 8-bit constant value. Flags will be effected by this operation. Note that this instruction does not use the CARRY as an input, and hence there is no need to condition the flags before use. The ability to specify any constant is useful in forming control sequences and counters.

Each ADD instruction must specify the first operand register as 's' followed by a hexadecimal digit. This register will also form the destination for the result. The second operand must then specify a second register value in a similar way or specify an 8-bit constant using 2 hexadecimal digits. The assembler supports register naming and constant labels to simplify the process.

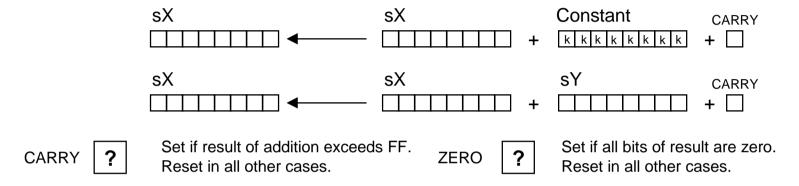

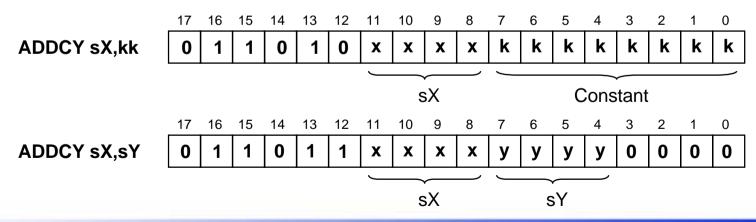

## **ADDCY**

The ADDCY instruction performs an addition of two 8-bit operands together with the contents of the CARRY flag. The first operand is any register, and it is this register which will be assigned the result of the operation. A second operand may also be any register or an 8-bit constant value. Flags will be effected by this operation. The ADDCY operation can be used in the formation of adder and counter processes exceeding 8 bits.

Each ADDCY instruction must specify the first operand register as 's' followed by a hexadecimal digit. This register will also form the destination for the result. The second operand must then specify a second register value in a similar way or specify an 8-bit constant using 2 hexadecimal digits. The assembler supports register naming and constant labels to simplify the process.

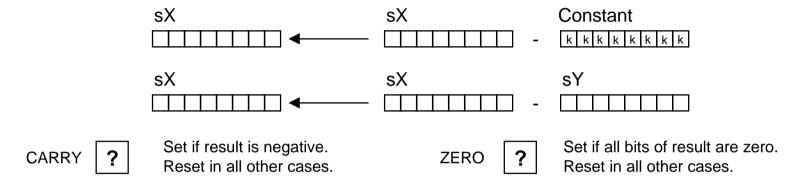

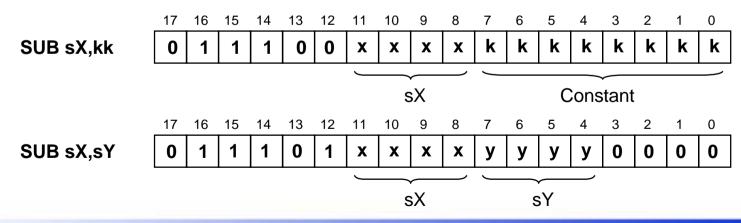

# **SUB**

The SUB instruction performs an 8-bit subtraction of two operands. The first operand is any register, and it is this register which will be assigned the result of the operation. The second operand may also be any register or an 8-bit constant value. Flags will be effected by this operation. Note that this instruction does not use the CARRY as an input, and hence there is no need to condition the flags before use. The CARRY flag indicates when an underflow has occurred. For example, if 's05' contains 27 hex and the instruction SUB s05,35 is performed, then the stored result will be F2 hex and the CARRY flag will be set.

Each SUB instruction must specify the first operand register as 's' followed by a hexadecimal digit. This register will also form the destination for the result. The second operand must then specify a second register value in a similar way or specify an 8-bit constant using 2 hexadecimal digits. The assembler supports register naming and constant labels to simplify the process.

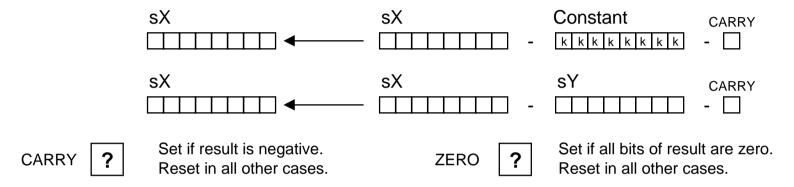

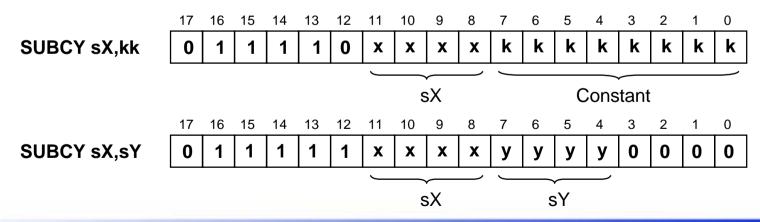

## **SUBCY**

The SUBCY instruction performs an 8-bit subtraction of two operands together with the contents of the CARRY flag. The first operand is any register, and it is this register which will be assigned the result of the operation. The second operand may also be any register or an 8-bit constant value. Flags will be effected by this operation. The SUBCY operation can be used in the formation of subtract and down counter processes exceeding 8 bits.

Each SUBCY instruction must specify the first operand register as 's' followed by a hexadecimal digit. This register will also form the destination for the result. The second operand must then specify a second register value in a similar way or specify an 8-bit constant using 2 hexadecimal digits. The assembler supports register naming and constant labels to simplify the process.

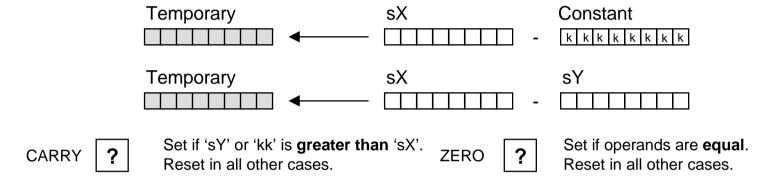

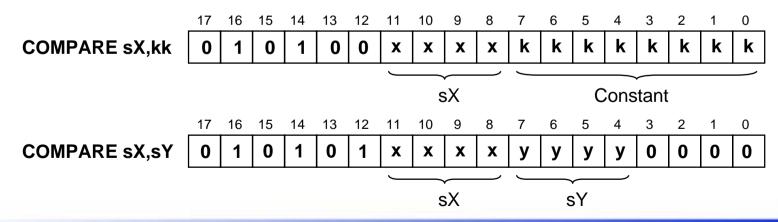

## **COMPARE**

The COMPARE instruction performs an 8-bit subtraction of two operands Unlike the 'SUB' instruction, the result of the operation is discarded and only the flags are affected. The ZERO flag is set when all the bits of the temporary result are low and indicates that both input operands were identical. The CARRY flag indicates when an underflow has occurred and indicates that the second operand was larger than the first. For example, if 's05' contains 27 hex and the instruction COMPARE s05,35 is performed, then the CARRY flag will be set (35>27) and the ZERO flag will be reset (35≠27).

Each COMPARE instruction must specify the first operand register as 's' followed by a hexadecimal digit. The second operand must then specify a second register value in a similar way or specify an 8-bit constant using 2 hexadecimal digits. The assembler supports register naming and constant labels to simplify the process.

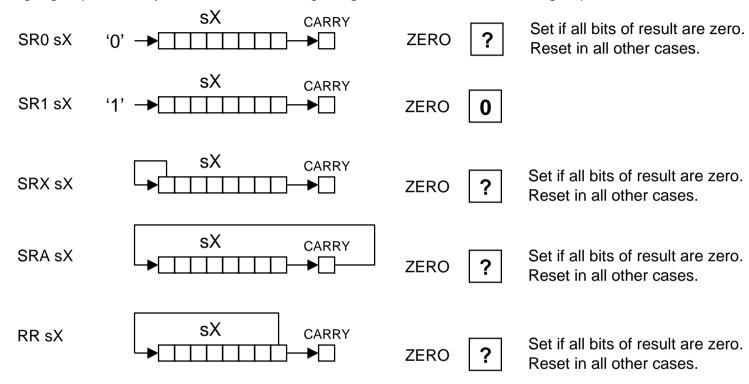

# SR0, SR1, SRX, SRA, RR

The shift and rotate right group all modify the contents of a single register. All instructions in the group have an effect on the flags.

Each instruction must specify the register as 's' followed by a hexadecimal digit. The assembler supports register naming to simplify the process.

Bit 2 Bit 1 Bit 0 Instruction

| _1 | 7 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 1 | 1      | 0 | SR0 sX |

|----|---|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|---|--------|---|--------|

| Γ. | 1 | 0  | n  | 0  | 0  | n  | x  | X  | x | x | 0 | 0 | 0 | 0 | 1 |   |   |   | 1 | 1      | 1 | SR1 sX |

| L  | • | •  |    |    |    |    |    |    |   |   |   |   |   |   | • |   |   |   | 0 | 1      | 0 | SRX sX |

|    |   |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   | 0 | 0 | 0 | SRA sX |   |        |

|    |   |    |    |    |    |    |    | s  | X |   |   |   |   |   |   |   |   |   | 1 | 0      | 0 | RR sX  |

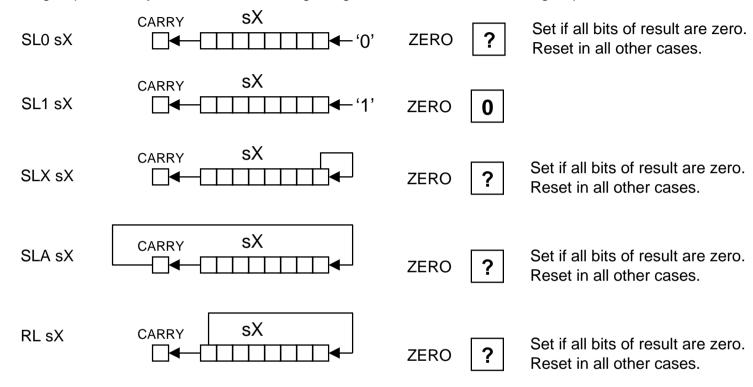

# SLO, SL1, SLX, SLA, RL

The shift and rotate left group all modify the contents of a single register. All instructions in the group have an effect on the flags.

Each instruction must specify the register as 's' followed by a hexadecimal digit. The assembler supports register naming to simplify the process.

Bit 2 Bit 1 Bit 0 Instruction

|   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |  | 0 |     | 1 | 0      | SL0 sX |

|---|---|---|---|---|---|---|---|----|---|---|---|---|---|---|--|---|-----|---|--------|--------|

| 1 | 0 | 0 | 0 | 0 | n | X | x | x  | x | 0 | 0 | 0 | 0 | 0 |  |   | 1 1 | 1 | 1      | SL1 sX |

|   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |  |   | 1   | 0 | 0      | SLX sX |

|   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |  | 0 | 0   | 0 | SLA sX |        |

|   |   |   |   |   |   |   | S | sΧ |   |   |   |   |   |   |  |   | 0   | 1 | 0      | RL sX  |

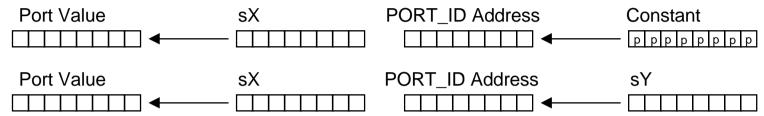

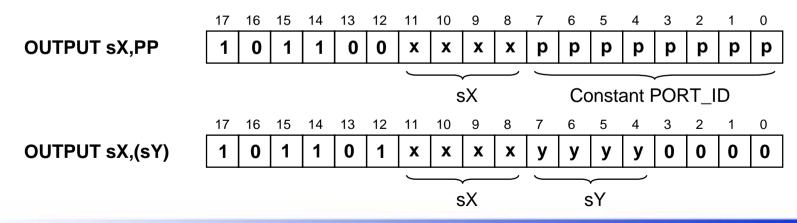

### **OUTPUT**

The OUTPUT instruction enables the contents of any register to be transferred to logic external to KCPSM3. The port address (in the range 00 to FF) can be defined by a constant value or indirectly as the contents of any other register. The Flags are not affected by this operation.

The user interface logic is required to decode the PORT\_ID port address value and capture the data provided on the OUT\_PORT. The WRITE\_STROBE is set during an output operation (see 'READ and WRITE STROBES'), and should be used to clock enable the capture register or write enable a RAM (see 'Design of Output Ports').

Each OUTPUT instruction must specify the source register as 's' followed by a hexadecimal digit. It must then specify the output port address using a register value in a similar way or specify an 8-bit constant port identifier using 2 hexadecimal digits. The assembler supports register naming and constant labels to simplify the process.

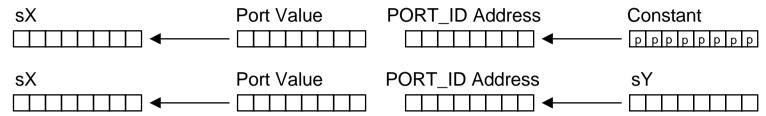

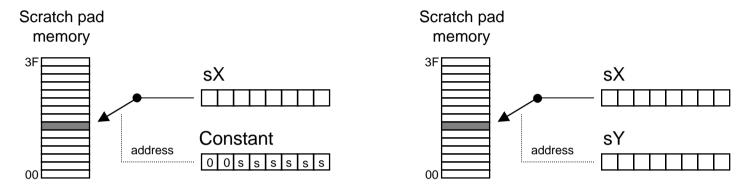

### **INPUT**

The INPUT instruction enables data values external to KCPSM3 to be transferred into any one of the internal registers. The port address (in the range 00 to FF) can be defined by a constant value or indirectly as the contents of any other register. The Flags are not affected by this operation.

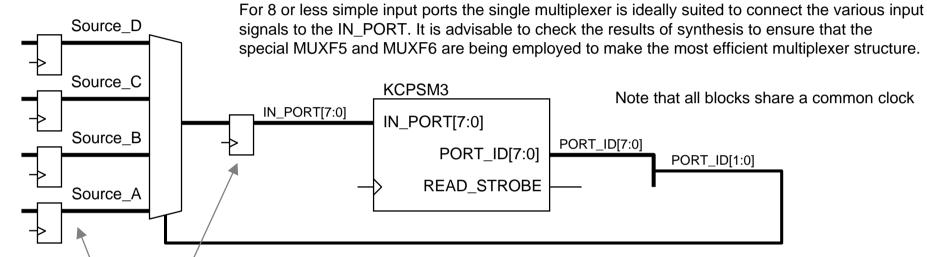

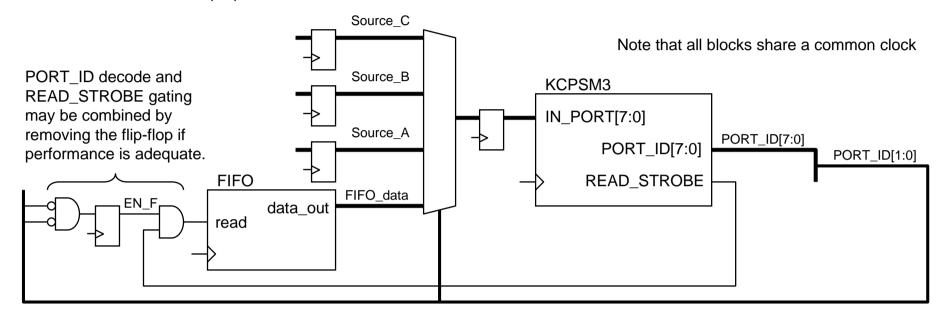

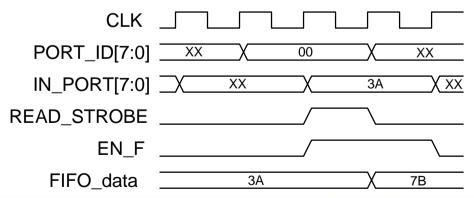

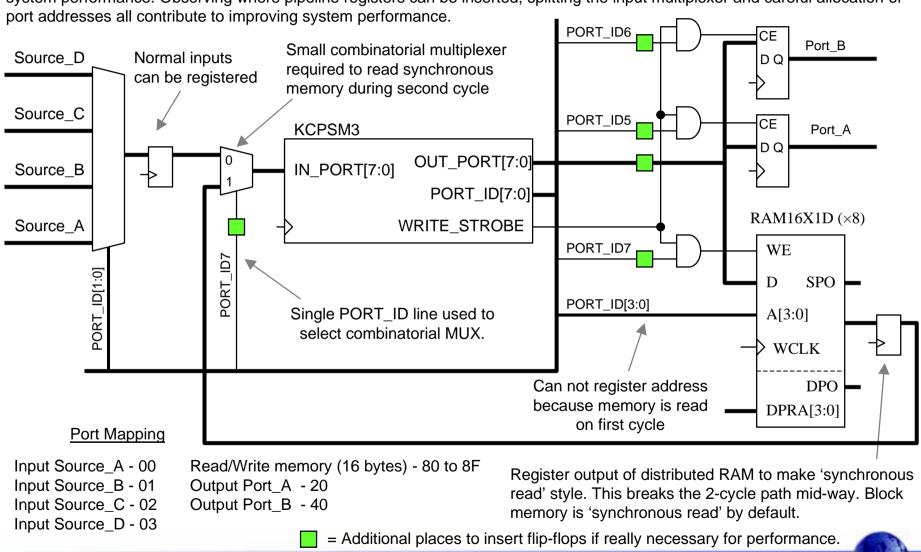

The user interface logic is required to decode the PORT\_ID port address value and supply the correct data to the IN\_PORT. The READ\_STROBE is set during an input operation (see 'READ and WRITE STROBES'), but it is not always necessary for the interface logic to decode this strobe. However, it can be useful for determining when data has been read, such as when reading a FIFO buffer (see 'Design of Input Ports').

Each INPUT instruction must specify the destination register as 's' followed by a hexadecimal digit. It must then specify the input port address using a register value in a similar way or specify an 8-bit constant port identifier using 2 hexadecimal digits. The assembler supports register naming and constant labels to simplify the process.

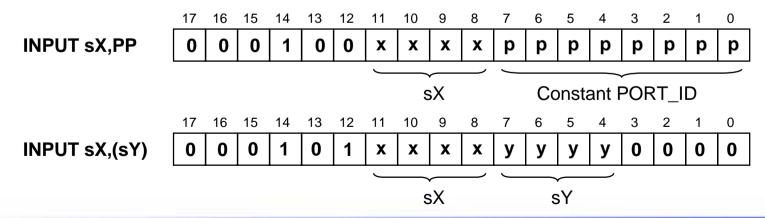

## **STORE**

The STORE instruction enables the contents of any register to be transferred to the 64-byte internal scratch pad memory. The storage address (in the range 00 to 3F) can be defined by a constant value or indirectly as the contents of any other register. The Flags are not affected by this operation.

Each STORE instruction must specify the source register as 's' followed by a hexadecimal digit. It must then specify the storage address using a register value in a similar way or specify a 6-bit constant storage address using 2 hexadecimal digits. The assembler supports register naming and constant labels to simplify the process. Although the assembler will reject constants greater than 3F, it is the responsibility of the programmer to ensure that the value of 'sY' is within the address range.

## **FETCH**

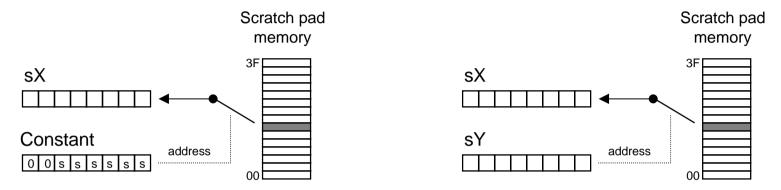

The FETCH instruction enables data held in the 64-byte internal scratch pad memory to be transferred any of the internal registers. The storage address (in the range 00 to 3F) can be defined by a constant value or indirectly as the contents of any other register. The Flags are not affected by this operation.

Each FETCH instruction must specify the destination register as 's' followed by a hexadecimal digit. It must then specify the storage address using a register value in a similar way or specify a 6-bit constant storage address using 2 hexadecimal digits. The assembler supports register naming and constant labels to simplify the process. Although the assembler will reject constants greater than 3F, it is the responsibility of the programmer to ensure that the value of 'sY' is within the address range.

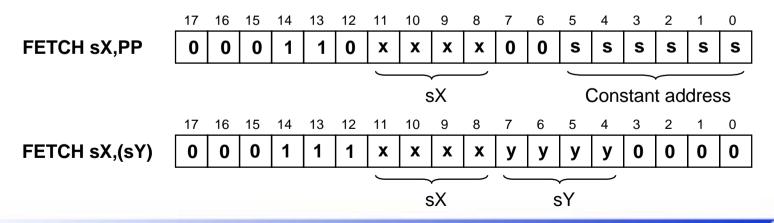

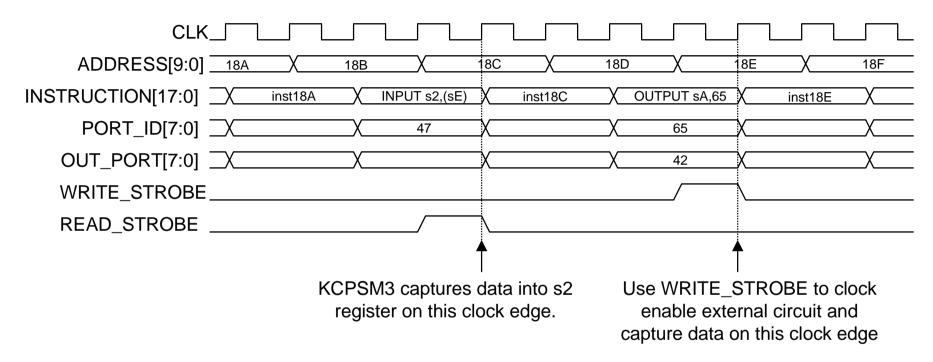

## **READ and WRITE STROBES**

These pulses are used by external circuits to confirm input and output operations. In the waveforms below, it is assumed that the content of register sE is 47, and the content of register sA is 42.

PORT\_ID[7:0] is valid for 2 clock cycles providing additional time for external decoding logic and enabling the connection of synchronous RAM. The WRITE\_STROBE is provided on the second clock cycle to confirm an active write by KCPSM3. In most cases, the READ\_STROBE will not be utilised by the external decoding logic, but again occurs in the second cycle and indicates the actual clock edge on which data is read into the specified register.

Note for timing critical designs, your timing specifications can allow 2 clock cycles for PORT\_ID and data paths, and only the strobes need to be constrained to a single clock cycle. Ideally, a pipeline register can be inserted where possible (see 'Design of Input Ports', 'Design of Output Ports' and 'Connecting Memory').

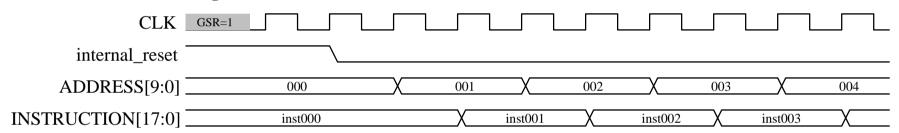

## RESET

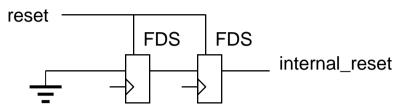

KCPSM3 contains an internal reset control circuit to ensure the correct start up of KCPSM3 following device configuration or global reset (GSR). This reset can also be activated within your design.

The KCPSM3 reset is sampled synchronous to the clock and used to form a controlled internal reset signal which is distributed locally as required. A small 'filter' circuit (see right) ensures that the release of the internal reset is clean and controlled.

### Release of Reset after configuration.

### **Application of user reset input**

The reset input can be tied to logic '0' if not required and the 'filter' will still be used to ensure correct power-up sequence.

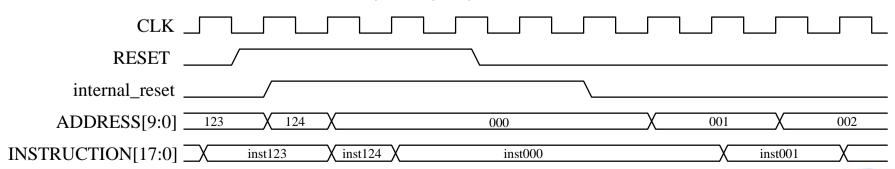

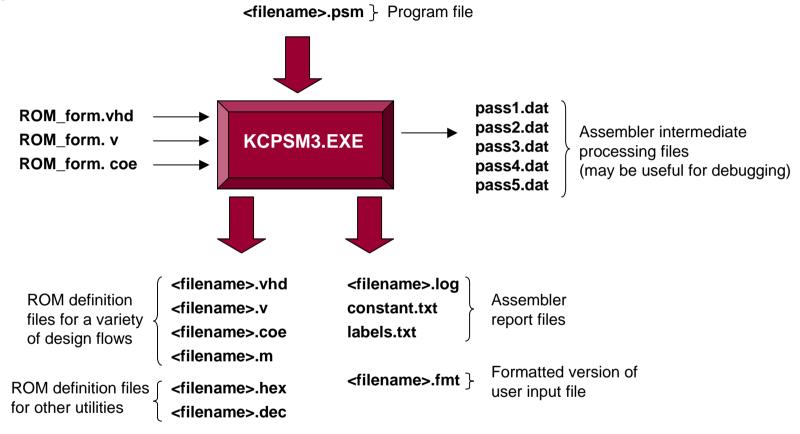

## KCPSM3 Assembler

The KCPSM3 Assembler is provided as a simple DOS executable file together with three template files. Copy <u>all</u> the files KCPSM3.EXE, ROM\_form.vhd, ROM\_form.v and ROM\_form.coe into your working directory.

Programs are best written with either the standard Notepad or Wordpad tools. The file is saved with a '.psm' file extension (8 character name limit).

Open a DOS box and navigate to the working directory. Then run the assembler 'kcpsm3 <filename>[.psm]' to assemble your program. It all happens very fast!!

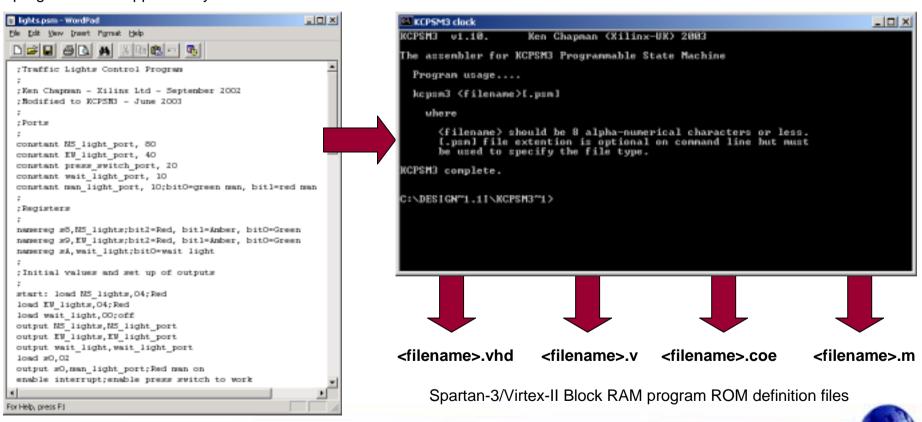

## **Assembler Errors**

The assembler will stop as soon as an error is detected. A short message will be displayed to help determine the reason for the error. The assembler will also display the line it was analyzing when it detected the problem. The user should fix each reported problem in turn and re-execute the assembler.

Since the execution of the assembler is very fast, it is unlikely that you will be able to 'see' it making progress and the display will appear to be immediate. If you would like to review everything that the assembler has written to the screen, the DOS output can be redirected to a text file using...... kcpsm3 <filename>[.psm] > screen\_dump.txt

## **Assembler Files**

The KCPSM3 assembler actually reads four input files and generates 15 output files. These are described in more detail on the following pages.

Note - All output files are overwritten each time the assembler is executed.

The 'hex' and 'dec' files provide the program ROM contents in unformatted hexadecimal and decimal which is useful for conversion to other formats not supported directly by the assembler. There is no further description in this manual.

## ROM\_form.vhd File

This file provides the template for the VHDL file generated by the assembler and suitable for synthesis and simulation. This file is provided with the assembler and must be placed in the working directory.

The supplied ROM\_form.vhd template file defines a Single Port Block RAM for Spartan-3, Virtex-II or Virtex-IIPRO configured as a ROM. You can adjust this template to define the type of memory you want. The template supplied includes some additional notes on how the template works

#### ROM form.vhd

The assembler reads the ROM\_form.vhd template and simply copies the information into the output file <filename>.vhd. There is no checking of syntax, so any alterations are the responsibility of the user.

The template contains some special text strings contained in {} brackets. These are {begin template}, {name}, and a whole family of initialisation identifiers such as {INIT\_01}. The assembler uses {begin template} to identify where the VHDL definition begins. It then intercepts and replaces all other special strings with the appropriate information. {name} is replaced with the name of the input program '.psm' file.

## **ROM\_form.v File**

This file provides the template for the Verilog file generated by the assembler and suitable for synthesis and simulation. This file is provided with the assembler and must be placed in the working directory.

The supplied ROM\_form.v template file defines a Single Port Block RAM for Spartan-3, Virtex-II or Virtex-IIPRO configured as a ROM. You can adjust this template to define the type of memory you want. The template supplied includes some additional notes on how the template works

#### ROM form.v

```

module {name} (address, instruction, clk);

input [9:0] address;

input clk;

output [17:0] instruction;

.

.

. defparam ram_1024_x_18.INIT_00 = 256'h{INIT_00};

defparam ram_1024_x_18.INIT_01 = 256'h{INIT_01};

defparam ram_1024_x_18.INIT_02 = 256'h{INIT_02};

```

The assembler reads the ROM\_form.v template and simply copies the information into the output file <filename>.v. There is no checking of syntax, so any alterations are the responsibility of the user.

The template contains some special text strings contained in {} brackets. These are {begin template}, {name}, and a whole family of initialisation identifiers such as {INIT\_01}. The assembler uses {begin template} to identify where the Verilog definition begins. It then intercepts and replaces all other special strings with the appropriate information. {name} is replaced with the name of the input program '.psm' file.

## **ROM\_form.coe File**

This file provides the template for the coefficient file generated by the assembler and suitable for the Core Generator. This file is provided with the assembler and must be placed in the working directory.

The supplied ROM\_form.coe template file defines a Dual Port Block RAM for Spartan-3, Virtex-II or Virtex-IIPRO in which the A-port is read only and the B-port is read/write. You can adjust this template to define the type of memory you want Core Generator to implement.

### ROM\_form.coe

```

component_name={name};

width_a=18;

depth_a=1024;

.

.

memory_initialization_radix=16;

global_init_value=00000;

memory_initialization_vector=

```

KCPSM3 Assembler

The assembler reads the ROM\_form.coe template and simply copies the information into the output file <filename>.coe. There is no checking of syntax, so any alterations are the responsibility of the user.

The template may contain the special text string **{name}** which the assembler will intercept and replace with the name of the program file. In this example you can see that **{name}** has been replaced with 'simple'.

It is vital that the last line of the template contains the key words...

memory\_initialization\_vector=

These are used by the Core Generator to identify that the data values follow, and the assembler will append the 1024 values required. Indeed, the template could simply contain this one line provided the Core Generator GUI is used to define all other parameters.

### <filename>.coe

```

component_name=simple;

width_a=18;

depth_a=1024;

.

.

memory_initialization_radix=16;

global_init_value=00000;

memory_initialization_vector=

01400, 23412, 09401, 100A0, 0C018, 35401, 34000, 00000, ...

```

## <filename>.fmt File

When a program passes through the assembler additional files to the '.vhd' and '.coe' files are produced to be of assistance to the programmer. One of these is called '<filename>.fmt'. This file is the original program but formatted to look nice. Looking at this file is also an easy way to see that everything has been interpreted the way you had expected.

#### <filename>.psm

constant max\_count, 18;count to 24 hours

namereg s4,counter\_reg;define register for counter

constant count\_port, 12

start: load counter\_reg,00;initialise counter

loop:output counter\_reg,count\_port

add counter\_reg,01;increment

load s0,counter\_reg

sub s0,max\_count;test for max value

jump nz,loop;next count

jump start;reset counter

- Formats labels and comments

- Puts all commands in upper case

- correctly spaces operands

- Gives registers an 'sX' format

- Converts hex constants to upper case

Write your PSM program quickly and then use KCPSM3 to make a nice formatted version for you to adopt as your own.

### <filename>.fmt

CONSTANT max count, 18 ; count to 24 hours NAMEREG s4, counter req ;define register for counter CONSTANT count port, 12 start: LOAD counter\_reg, 00 ; initialise counter loop: OUTPUT counter req, count port ADD counter req, 01 ; increment LOAD s0, counter req SUB s0, max count itest for max value JUMP NZ, loop inext count JUMP start reset counter

KCPSM3 Assembler

# <filename>.log File

The '.log' file provides you with the most detail about the assembly process which has been performed. This is where you can observe how each instruction and directive has been used. Address and op-code values are associated with each line of the program and the actual values of addresses, registers, and constants defined by labels are specified.

### <filename>.log

```

KCPSM3 Assembler log file for program 'simple.psm'.

Generated by KCPSM3 version 1.01

Ken Chapman (Xilinx Ltd) 2003.

Addr Code

000

CONSTANT max count, 18

count to 24 hours

000

NAMEREG s4, counter req

;define register for counter

CONSTANT count port, 12

000

start: LOAD counter reg[s4], 00

000

00400

; initialise counter

001

2C412

loop: OUTPUT counter reg[s4], count port[12]

002 18401

ADD counter reg[s4], 01

; increment

LOAD s0, counter req[s4]

003 01040

004 18018

ADD s0, max count[18]

itest for max value

005 35401

JUMP NZ, loop[001]

inext count

006 34000

JUMP start[000]

;reset counter

Comment

Instruction

Op-Code

Values contained in [1] brackets indicate

the value associated with the label

Address

Label

i.e. 'loop' is resolved to be address '001'.

```

### constant.txt & labels.txt Files

These two files provide a list of the line labels and their associated addresses, and a list of constants and their values as defined by 'constant' directives in the program file. These can be useful during the development and testing of larger programs.

### constant.txt Table of constant values and their specified constant labels. max\_count 18 count\_port Constant Label labels.txt Table of addresses and their specified labels. Value 000 start 001 loop Line Label Address

## pass.dat Files

These are really internal files to the assembler and represent intermediate stages of the assembly process. <u>These files will typically be ignored</u>, but may just help in identifying how the assembler has interpreted the program file syntax. The files are automatically deleted at the start of the assembly process. If there is an error detected by the assembler, the '.dat' files will only be complete until the point of the last successful processing.

### Part of pass1.dat

```

LABEL-

INSTRUCTION-add

OPERAND1-counter_reg

OPERAND2-01

COMMENT-;increment

```

### Part of pass5.dat

```

ADDRESS-002

LABEL-

FORMATTED-ADD counter_reg, 01

LOGFORMAT-ADD counter_reg[s4], 01

INSTRUCTION-ADD

OPERAND1-counter_reg

OP1 VALUE-s4

OPERAND2-01

OP2 VALUE-01

COMMENT-; increment

```

The '.dat. Files segment the information from each line into the different fields. Each pass resolves more information.

The example shown here is related to the line......

```

ADD counter_reg, 01 ;increment

```

It can be seen that pass1 has purely segmented the fields of the line. In the final pass5, you can see that the assembler has resolved all the relevant information.

# **Program Syntax**

Probably the best way to understand what is and is not valid syntax is to look at the examples and try the assembler. However there are some simple rules which are of assistance from the beginning.

**No blank lines** - A blank line will be ignored by the assembler and removed from any formatted files. If you would like to keep a line use a blank comment (a semicolon).

**Comments** - Any item on a line following a semi-colon (;) will be ignored by the assembler. Whilst comments are useful, it is helpful if they are kept concise otherwise you will have very long lines and find it difficult to print out programs and log files.

**Registers** - All registers should be defined as the letter 's' immediately followed by one hexadecimal digit the range 0 to F. The assembler will accept any mixture of upper and lower case characters and automatically convert them to the 'sX' format where 'X' is one of 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F. The NAMEREG directive can be used to assign new register names.

**Constants** - A constant must be specified using hexadecimal. Data values and Port Addresses in range 00 to FF. Memory store values in the range 00 to 3F and program addresses in the range 000 to 3FF. The assembler will accept any mixture of upper and lower case characters and automatically convert them to upper case.

**Labels** - Labels are any text string which the user defines. Labels are case sensitive for additional flexibility. Labels must not contain any spaces although the under-score character is supported. Valid characters are '0' to '9', 'a' to 'z', and 'A' to 'Z'. Again it is helpful for labels to be reasonably concise if only for the formatting of a program to be reasonable. Labels which could be confused with hexadecimal values or register specifications are rejected by the assembler.

**Line Labels** - A label is used to identify a program line for reference in a JUMP or CALL instruction and should be followed by a colon (:). The following example shows the use of a label to identify a program line and its use later in a JUMP instruction.

```

loop: OUTPUT counter_reg, count_port

ADD counter_reg, 01 ;increment

LOAD s0, counter_reg

SUB s0, max_count ;test for max value

JUMP NZ, loop ;next count

```

# **Program Syntax**

**Instructions** - The instructions should be of the format described in the "KCPSM3 instruction set" page of this document. The assembler is very forgiving over the use of spaces and <TAB> characters, but instructions and the first operand must be separated by at least one space. Instructions with two operands must ensure that a comma (,) separator is used.

The assembler will accept any mixture of upper and lower case characters for the instruction and automatically convert them to upper case. The following examples all show acceptable instruction specifications, but the formatted output shows how it was expected.

| load s5,7E         |           | LOAD s5, 7E        |

|--------------------|-----------|--------------------|

| AddCY s8,SE        |           | ADDCY s8, sE       |

| ENABLE interrupt   |           | ENABLE INTERRUPT   |

| Output S2, (S8)    | Assembler | OUTPUT s2, (s8)    |

| jump Nz, 2a7       |           | JUMP NZ, 2A7       |

| ADD sF, step_value |           | ADD sF, step_value |

| INPUT S9,28        |           | INPUT s9, 28       |

| sl1 se             |           | SL1 sE             |

| store S8,(Sf)      |           | STORE s8, (sF)     |

Most other syntax issues will be solved by reading the error messages provided by the assembler.

### **CONSTANT** Directive

The assembler supports three assembler directives. These are commands included in the program which are used purely by the assembly process and do not correspond to instructions executed by KCPSM3.

The CONSTANT directive provides a way to assign an 2-digit hexadecimal value to a label. In this way the program can declare constants such as port and storage addresses and particular data values needed in the program. By defining constant values in this way it is often easier to understand their meaning in the program rather than using absolute values in the program lines. The following example illustrates the directive syntax and its uses.

```

CONSTANT light port, 03

;light sensor port

CONSTANT light sensor, 01

;bit0 is light sensor

CONSTANT temp sensor, 40

;temperature sensor port

NAMEREG sF, light count msb ;16-bit light pulse counter

NAMEREG sE, light_count_lsb

NAMEREG sD, new temp

; current temperature

CONSTANT peak temp, 2E

; peak temperature memory

light test: INPUT s1, light port

;test for light

TEST s1, light sensor

; jump if no light

JUMP Z, temp_test

ADD light count lsb, 01

;increment counter

ADDCY light count msb, 00

temp test: INPUT new temp, temp sensor ; read temperature

FETCH s2, peak temp

COMPARE s2, new temp

; compare with peak value

JUMP NC, light_test

;new value is smaller

STORE new_temp, peak_temp

; write new peak value

JUMP light_test

```

Note - A constant is global. Even if a constant is defined at the end of the program file, it can be used in instructions anywhere in the program.

Constant names must not contain any spaces although the under-score character is supported. Valid characters are '0' to '9', 'a' to 'z', and 'A' to 'Z'.

'light\_port' and 'temp\_sensor' are used to specify port addresses. This is particularly useful when defining the hardware interface, and allows the program to be developed before the I/O addresses are fully defined. 'light\_sensor' is being used to specify a data constant which in this case identifies which bit is to be tested. 'peak\_temp' defines a scratch pad memory location which is then used to hold a variable.

### **NAMEREG** Directive

The NAMEREG directive provides a way to assign a new name to any of the 16 registers. In this way the program can refer to 'variables' by name rather than as absolute register specifications. By naming registers in this way it is often easier to understand the meaning in the program without the need for so many comments. It can also help to prevent inadvertent reuse of a register with associated data corruption.

**Important** - The NAMEREG directive is applied in-line with the code by the assembler. Before the NAMEREG directive, the register will be named in the 'sX' style. Following the directive, <u>only</u> the new name will apply. It is also possible to rename a register again (i.e. NAMEREG counter\_reg, hours) and only the new name will apply in the subsequent program lines.

```

CONSTANT light port, 03

;light sensor port

CONSTANT light sensor, 01

;bit0 is light sensor

CONSTANT temp_sensor, 40

;temperature sensor port

NAMEREG sF, light_count_msb ;16-bit light pulse counter

NAMEREG sE, light count 1sb

NAMEREG sD, new temp

; current temperature

CONSTANT peak temp, 2E

; peak temperature memory

light_test: INPUT s1, light_port

;test for light

TEST s1, light_sensor

JUMP Z, temp_test

; jump if no light

ADD light count lsb, 01

;increment counter

ADDCY light count msb, 00

temp test: INPUT new temp, temp sensor ; read temperature

FETCH s2, peak_temp

COMPARE s2, new_temp

; compare with peak value

JUMP NC, light_test

; new value is smaller

STORE new_temp, peak_temp

;write new peak value

JUMP light test

```

Register names must not contain any spaces although the under-score character is supported. Valid characters are '0' to '9', 'a' to 'z', and 'A' to 'Z'.

The register 'sD' has been renamed to be 'new\_temp' and is then used in multiple instructions making it clear what the meaning of the register contents actually are.

### **ADDRESS Directive**

The ADDRESS directive provides a way force the assembly of the following instructions commencing at a new address value. This is useful for separating subroutines into specific locations, and vital for handling interrupts. The address must be specified as a 3-digit hexadecimal value in the range '00' to '3FF'.

In the following code segment, the ADDRESS directive defines the address for the interrupt vector.

```

JUMP NZ, inner_long

RETURN

;Interrupt Service Routine

ISR: LOAD wait_light, 01 ;register press of switch

OUTPUT wait_light, wait_light_port ;turn on light

RETURNI DISABLE ;continue light sequence but no more interrupts

ADDRESS 3FF ;Interrupt vector

JUMP ISR

;end of program

```

The log file clearly shows that the ADDRESS directive has forced the last instruction into the highest memory location in the program RAM. This is the address to which the program counter is forced during an active interrupt.

```

3E3 357E1

JUMP NZ, inner long[3E1]

3E4 2A000

RETURN

;Interrupt Service Routine

3E5

ISR: LOAD wait_light[sA], 01

register press of switch

3E5 00A01

OUTPUT wait light[sA], wait light port[10] ; turn on light

3E6 2CA10

3E7 38000

; continue light sequence but...

RETURNI DISABLE

;Interrupt vector

3FF

ADDRESS 3FF

3FF 343E5

JUMP ISR[3E5]

3FF

; end of program

```

## KCPSM and KCPSM2 Compatibility

KCPSM and KCPSM2 are very much 'brothers' with many similarities (see 'PicoBlaze Comparison'). However, each has been tuned to the specific device architecture so there are differences.

### **Common points**

The KCPSM3 assembler has slightly different rules concerning which labels for lines, constants, and registers are acceptable. Therefore, it may be necessary to adjust some of the user names in your program code. Typically, labels are nicely 'descriptive' and this issue will not be encountered.

The KCPSM3 macro has an INTERRUPT\_ACK output signal which the previous versions did not have. It is not vital to use this signal in your design, but should be included in the component port definitions.

The internal scratch pad memory will often mean that external memory connected to I/O ports can be removed. This will simplify the logic design and require the code to reflect the use of STORE and FETCH instructions in place of INPUT and OUTPUT.

### **KCPSM to KCPSM3**

KCPSM3 is in every way a superset of of KCPSM so there will be very few issues migrating a KCPSM based design and code. The address range of KCPSM3 supports a program which is four times larger than KCPSM and therefore all programs will be able to fit. Code will need to reflect that absolute address values need to be specified with 3 hexadecimal digits (not 2). The use of line labels will mean that most cases will be handled automatically by the assembler, but special care should be taken with ADDRESS directives. Most critical is that the interrupt vector will need to be located at '3FF' (not FF).

### KCPSM2 to KCPSM3

KCPSM3 has 16 registers compared with the 32 registers of KCPSM2. The default register names used in KCPSM2 are 's00' to 's1F' and will need to be modified to conform to the default names 's0' to 'sF' available in KCSPM. Although the use of NAMEREG directives will be helpful, some fundamental changes will almost certainly be required to compensate for the lower number of available registers. The internal scratch pad memory provides 64 locations which should more than compensate for the lower number of registers but obviously requires a change to the coding style. The program address range and interrupt vector are identical.

## **PicoBlaze Comparison**

This chart shows a comparison of the features offered by the FPGA variants of PicoBlaze. XAPP387 describes the CoolRunner implementation of an 8-bit micro controller which was also based on the original KCPSM processor.

|                       | KCPSM                                                                           | KCPSM2                                                                                      | КСРЅМЗ                                                                               |

|-----------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Target Devices        | Spartan-II, Spartan-IIE,<br>Virtex, Virtex-E                                    | Virtex-II, Virtex-IIPRO                                                                     | Spartan-3,<br>Virtex-II, Virtex-IIPRO                                                |

| Program Size          | 256 instructions<br>(256×16 Block RAM)                                          | 1024 instructions<br>(1024×18 Block RAM)                                                    | 1024 instructions<br>(1024×18 Block RAM)                                             |

| Registers             | 16                                                                              | 32                                                                                          | 16                                                                                   |

| Scratch-Pad Memory    | -                                                                               | -                                                                                           | 64 Bytes                                                                             |

| Size                  | 76 Slices                                                                       | 84 Slices                                                                                   | 96 Slices                                                                            |

| CALL/RETURN stack     | 15 levels                                                                       | 31 levels                                                                                   | 31 levels                                                                            |

| Features and Comments | Smallest and oldest! Very well used and proven. Relatively small program space. | Register rich. Virtex-II devices only. Can <u>not</u> migrate design directly to Spartan-3. | COMPARE and TEST instructions, PARITY test, Scratch-pad memory, INTERRUPT_ACK signal |

As with most things, there is a clear trend for PicoBlaze to become larger as more features are added. The author welcomes all feedback regarding this trend to determine the size acceptable for a programmable state machine (PSM).

# **Interrupt Handling**

Effective interrupt handling is a skillful task and this document does not attempt to explain how and when an interrupt should be used. The information supplied should be adequate for the capability of KCPSM3 to be assessed and for interrupt based systems to be created.

**Default State -** By default the interrupt input is disabled. This means that the entire 1024 words of program space can be used without any regard to interrupt handling or use of the interrupt instructions.

**Enabling Interrupts** - For an interrupt to take place the ENABLE INTERRUPT command must be used. At critical stages of a program execution where an interrupt would be unacceptable, a DISABLE INTERRUPT can be used. Since an active interrupt will automatically disable the interrupt input, the interrupt service routine will end with a RETURNI instruction which also includes the option to ENABLE or DISABLE the interrupt input as it returns to the main program.

What happens during an interrupt? The program counter is pushed onto the stack and the values of the CARRY and ZERO flags are preserved (to be restored by the RETURNI instruction). The interrupt input is automatically disabled. Finally the program counter is forced to address 3FF (last program memory location) from which the next instruction is executed.

# **Basics of Interrupt Handling**

Since the interrupt will force the program counter to address '3FF' it will generally be necessary to ensure that a jump vector to a suitable interrupt service routine (ISR) is located at this address otherwise the program will 'roll over' to address zero.

In most cases an ISR will be provided. The routine can be located at any position in the program and jumped to by the interrupt vector located at the '3FF" address. The ISR will perform the required tasks and then end in RETURNI with ENABLE or DISABLE.

**Simple Example -** The following example illustrates a very simple interrupt handling routine......

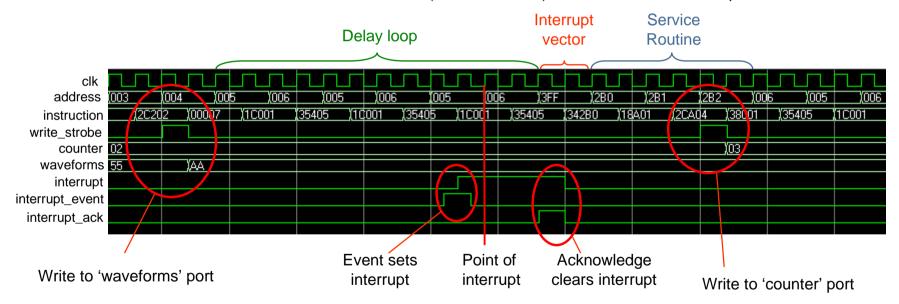

The KCPSM3 is generally involved with generating waveforms to an output by writing the values '55' and 'AA' to the 'waveform\_port' (port address 02). It does this at regular intervals by decrementing a register (s0) based counter 7 times in a loop.

When an interrupt is asserted, the KCPSM3 breaks off from the waveform generation and simply increments a separate counter register (sA) and writes the counter value to the 'counter\_port' (port address 04).

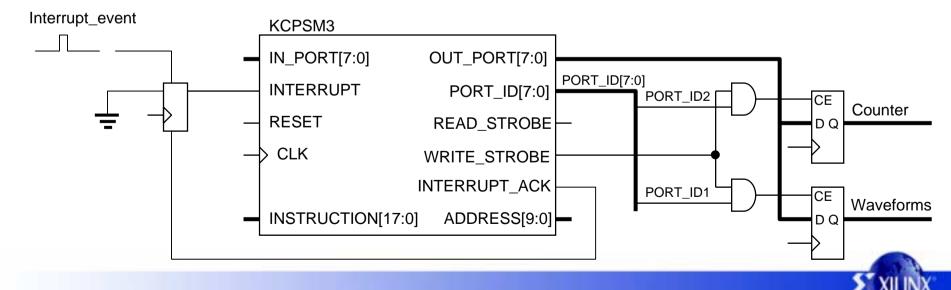

# **Example Design (VHDL)**

The following VHDL shows the addition of the data capture registers and interrupt control to the processor. Note the simplified port decoding logic through careful selection of port addresses. The complete VHDL file is supplied as 'kcpsm3\_int\_test.vhd'.

```

IO_registers: process(clk)

begin

if clk'event and clk='1' then

-- waveform register at address 02

if port_id(1)='1' and write_strobe='1' then

waveforms <= out_port;

end if;

-- Interrupt Counter register at address 04

if port_id(2)='1' and write_strobe='1' then

counter <= out_port;

end if;

end if;

end process IO_registers;</pre>

```

```

interrupt_control: process(clk)

begin

if clk'event and clk='1' then

if interrupt_ack='1' then

interrupt <= '0';

elsif interrupt_event='1' then

interrupt <= '1';

else

interrupt <= interrupt;

end if;

end process interrupt_control;</pre>

```

# **Interrupt Service Routine**

In the assembler log file for the example, it can be seen that the interrupt service routine has been force to compile at address '2B0', and that the waveform generation is located in the base addresses. This makes it easier to observe the interrupt in action in the operation waveforms. This program is supplied as 'int\_test.psm' for you to assemble yourself.

```

; Interrupt example

CONSTANT waveform port, 02

;bit0 will be data

CONSTANT counter port, 04

CONSTANT pattern 10101010, AA

NAMEREG sA, interrupt counter

start: LOAD interrupt counter[sA], 00

;reset interrupt counter

00A00

LOAD s2, pattern 10101010[AA]

; initial output condition

001

002AA

3C001

ENABLE INTERRUPT

Main program delay loop where

003

most time is spent

drive wave: OUTPUT s2, waveform port[02]

003

2C202

004

00007

LOAD s0, 07

;delay size

;delay loop

loop: SUB s0, 01

005

1C001

JUMP NZ, loop[005]

006

35405

XOR s2, FF

OE2FF

;toggle waveform

JUMP drive wave[003]

34003

008

Interrupt Service Routine

009

(located at address 2B0 onwards)

ADDRESS 2B0 ◀

2B0

int routine: ADD interrupt counter[sA], 01

2B0

18A01

; increment counter

OUTPUT interrupt counter[sA], counter port[04]

2B1

2CA04

38001

RETURNI ENABLE

2B2

2B3

Interrupt vector set at address 3FF

ADDRESS 3FF

3FF

and causing JUMP to service routine

3FF

342B0

JUMP int routine[2B0]

```

# **Interrupt Operation**