# PicoBlaze 8-bit Embedded Microcontroller User Guide

for Extended Spartan®-3 and Virtex®-5 FPGAs Introducing PicoBlaze for Spartan-6, Virtex-6, and 7 Series FPGAs

UG129 June 22, 2011

Xilinx is disclosing this Document and Intellectual Property (hereinafter "the Design") to you for use in the development of designs to operate on, or interface with Xilinx FPGAs. Except as stated herein, none of the Design may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of the Design may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

Xilinx does not assume any liability arising out of the application or use of the Design; nor does Xilinx convey any license under its patents, copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of the Design. Xilinx reserves the right to make changes, at any time, to the Design as deemed desirable in the sole discretion of Xilinx. Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Design.

THE DESIGN IS PROVIDED "AS IS" WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DESIGN, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE DESIGN, EVEN IF YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN CONNECTION WITH YOUR USE OF THE DESIGN, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT EXCEED THE AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE DESIGN. YOU ACKNOWLEDGE THAT THE FEES, IF ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT CC THAT XILINX WOULD NOT MAKE AVAILABLE THE DESIGN TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY.

The Design is not designed or intended for use in the development of on-line control equipment in hazardous environments requiring fail-safe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control, life support, or weapons systems ("High-Risk Applications"). Xilinx specifically disclaims any express or implied warranties of fitness for such High-Risk Applications. You represent that use of the Design in such High-Risk Applications is fully at your risk.

© 2004-2005, 2008-2011 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. PowerPC is a trademark of IBM Corp. and used under license. PCI, PCI-X, and PCI EXPRESS are registered trademarks of PCI-SIG. All other trademarks are the property of their respective owners.

# **Revision History**

The following table shows the revision history for this document...

| Date     | Version | Revision                                                                                                                          |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| 05/20/04 | 1.0     | Initial Xilinx release.                                                                                                           |

| 06/10/04 | 1.1     | Various minor corrections, updates, and enhancements throughout.                                                                  |

| 11/21/05 | 1.1.1   | Minor updates.                                                                                                                    |

| 06/24/08 | 1.1.2   | Corrected typo in example for "LOAD sX, Operand — Load Register sX with Operand". Updated trademarks and links.                   |

| 10/09/09 | 1.1.3   | Added Spartan-6, Virtex-5, and Virtex-6 FPGA callouts in Title page.                                                              |

| 1/28/10  | 2.0     | Updated to v2.0; removed references to Virtex-II; clarified device family optimization; converted to current user guide template. |

| 6/22/11  | 2.1     | Removed Technical Support Limitations section; updated Title page, Preface, and Chapter 1; incorporated CRs 592626 and 550821.    |

# Table of Contents

| Preface: About This Guide                                                    |

|------------------------------------------------------------------------------|

| Guide Contents                                                               |

| Chapter 1: Introduction                                                      |

| PicoBlaze Microcontroller Features                                           |

| PicoBlaze Microcontroller Functional Blocks                                  |

| General-Purpose Registers                                                    |

| 1,024-Instruction Program Store                                              |

| Arithmetic Logic Unit (ALU)                                                  |

| Flags                                                                        |

| 64-Byte Scratchpad RAM                                                       |

| Input/Output1                                                                |

| Program Counter (PC)                                                         |

| Program Flow Control                                                         |

| CALL/RETURN Stack                                                            |

| Interrupts                                                                   |

| Reset                                                                        |

| Why the PicoBlaze Microcontroller?                                           |

| Chapter 2: PicoBlaze Interface Signals  Chapter 3: PicoBlaze Instruction Set |

| Address Spaces                                                               |

| Processing Data 2                                                            |

| Logic Instructions                                                           |

| Arithmetic Instructions                                                      |

| Multiplication                                                               |

| Division                                                                     |

| No Operation (NOP)                                                           |

| Setting and Clearing CARRY Flag                                              |

| Test and Compare                                                             |

| Shift and Rotate Instructions                                                |

| Moving Data 33                                                               |

| Program Flow Control                                                         |

| JUMP                                                                         |

| CALL/RETURN                                                                  |

| Chapter 4: Interrupts                                                        |

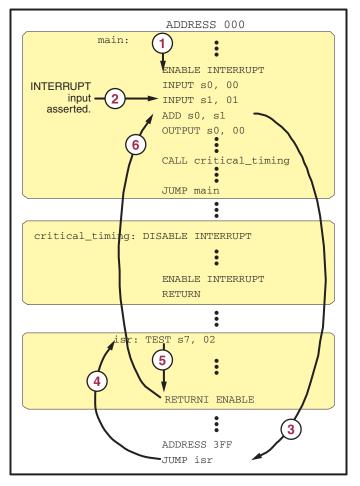

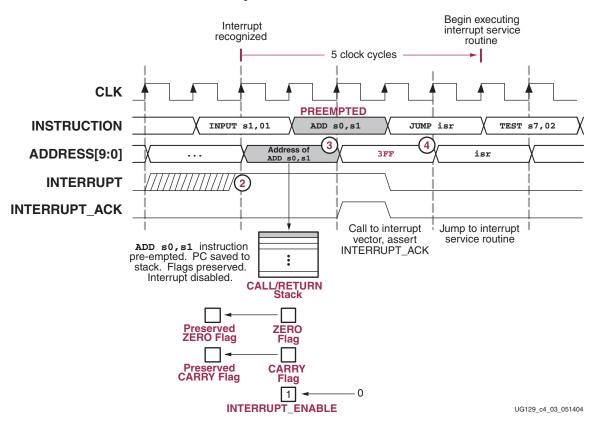

| Example Interrupt Flow                                                       |

| Chapter 5: Scratchpad RAM                                                        |   |

|----------------------------------------------------------------------------------|---|

| <b>Address Modes</b>                                                             |   |

| Direct Addressing                                                                |   |

| Indirect Addressing                                                              |   |

| Implementing a Look-Up Table                                                     |   |

| Stack Operations 43                                                              |   |

| FIFO Operations                                                                  |   |

| Chapter 6: Input and Output Ports                                                |   |

| <b>PORT_ID Port</b>                                                              |   |

| INPUT Operations 46                                                              |   |

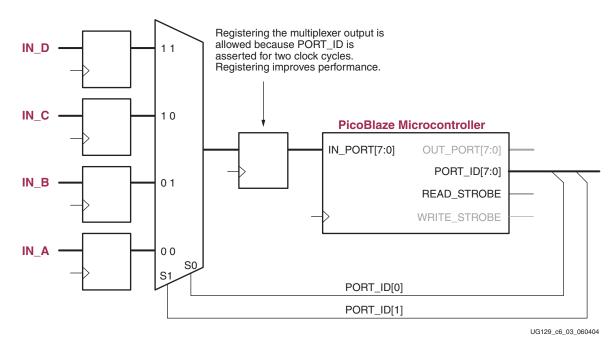

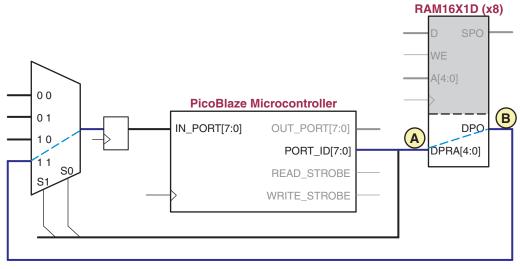

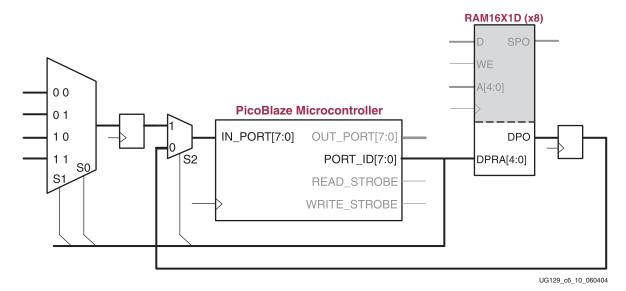

| Applications with Few Input Sources                                              |   |

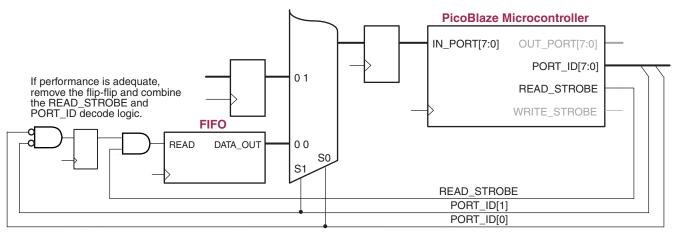

| READ_STROBE Interaction with FIFOs                                               |   |

| OUTPUT Operations 49                                                             |   |

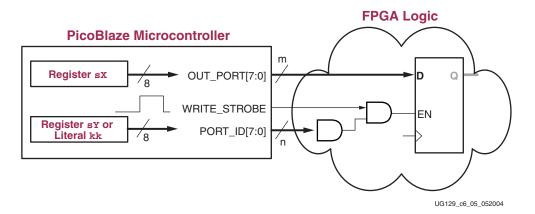

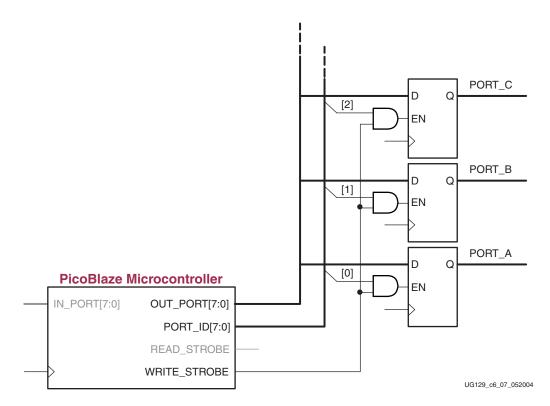

| Simple Output Structure for Few Output Destinations                              |   |

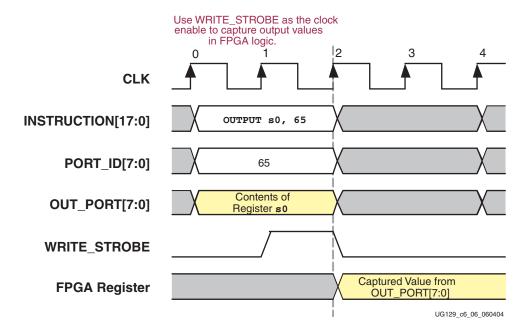

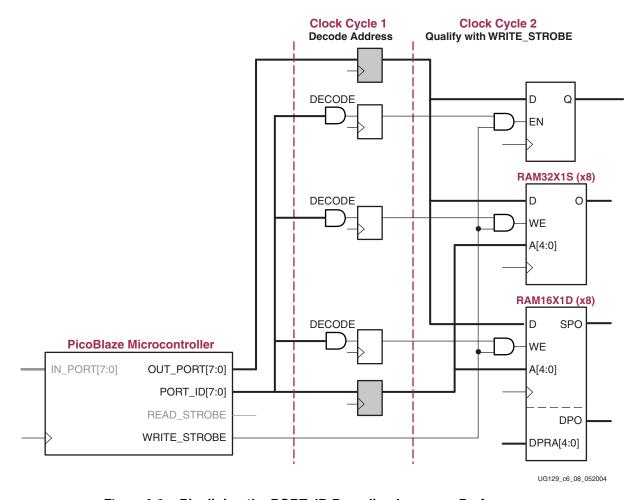

| Pipelining for Maximum Performance                                               |   |

| Repartitioning the Design for Maximum Performance                                |   |

| Chapter 7: Instruction Storage Configurations                                    |   |

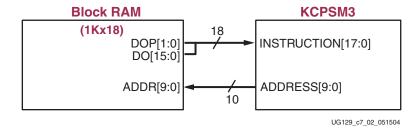

| Standard Configuration – Single 1Kx18 Block RAM 55                               |   |

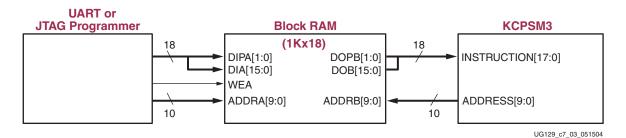

| Standard Configuration with UART or JTAG Programming Interface 56                |   |

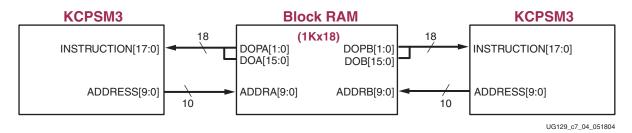

| Two PicoBlaze Microcontrollers Share a 1Kx18 Code Image 56                       |   |

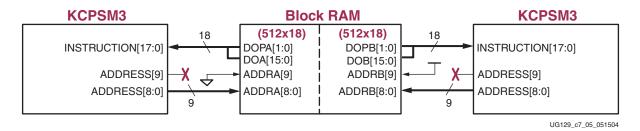

| Two PicoBlaze Microcontrollers with Separate 512x18 Code Images in a Block RAM 5 | 7 |

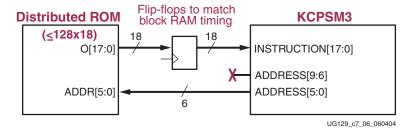

| Distributed ROM Instead of Block RAM                                             |   |

| Chapter 8: Performance                                                           |   |

| Input Clock Frequency 59                                                         |   |

| Predicting Executing Performance                                                 |   |

| Chapter 9: Using the PicoBlaze Microcontroller in an FPGA Design                 |   |

| VHDL Design Flow                                                                 |   |

| KCPSM3 Module                                                                    |   |

| Connecting the Program ROM                                                       |   |

| Black Box Instantiation of KCPSM3 using KCPSM3.ngc                               |   |

| Generating the Program ROM using prog_rom.coe                                    |   |

| Verilog Design Flow                                                              |   |

| verios design flow 00                                                            |   |

| Chapter 10: PicoBlaze Development Tools                                                               |   |

|-------------------------------------------------------------------------------------------------------|---|

| KCPSM360                                                                                              | 5 |

| Assembler                                                                                             |   |

| Assembly Errors                                                                                       |   |

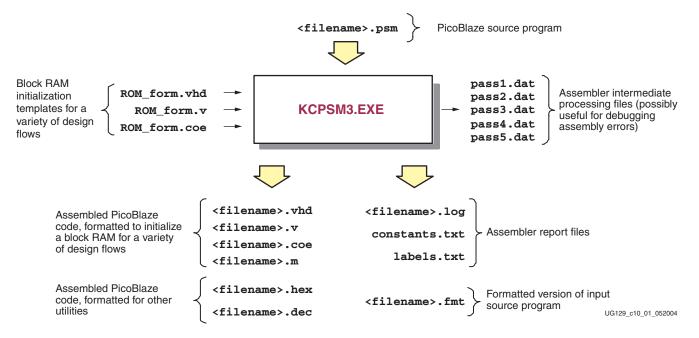

| Input and Output Files                                                                                |   |

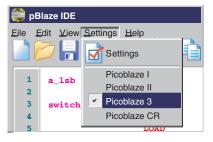

| Mediatronix pBlazIDE       65         Configuring pBlazIDE for the PicoBlaze Microcontroller       65 |   |

| Importing KCPSM3 Code into pBlazIDE                                                                   |   |

| Differences Between the KCPSM3 Assembler and pBlazIDE                                                 |   |

| Directives                                                                                            |   |

| Chapter 11: Assembler Directives                                                                      |   |

| Locating Code at a Specific Address                                                                   | 1 |

| Naming or Aliasing Registers                                                                          |   |

| Defining Constants                                                                                    |   |

| Naming the Program ROM Output File                                                                    |   |

| KCPSM3                                                                                                |   |

| pBlazIDE                                                                                              | 2 |

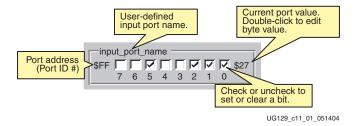

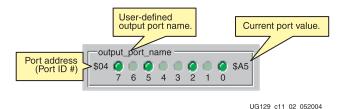

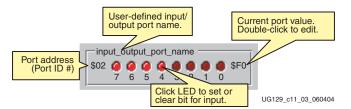

| Defining I/O Ports (pBlazIDE)                                                                         |   |

| Input Ports                                                                                           |   |

| Output Ports                                                                                          |   |

| Custom Instruction Op-Codes                                                                           |   |

| Chapter 12: Simulating PicoBlaze Code                                                                 |   |

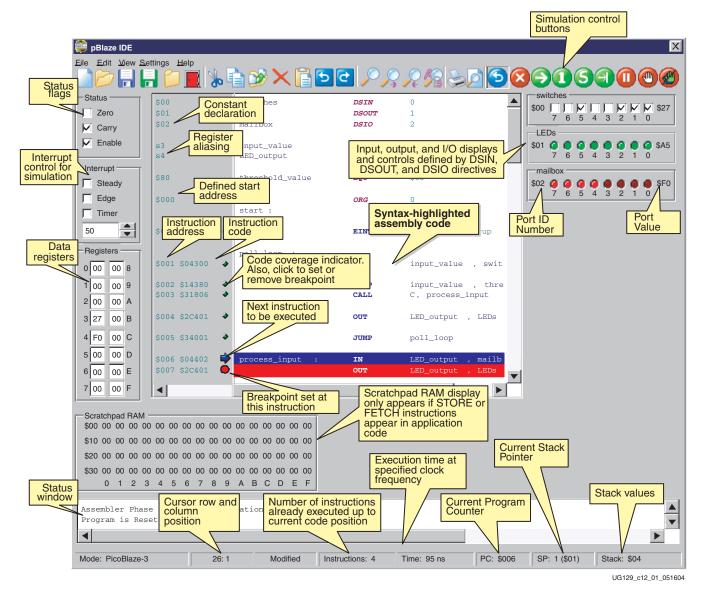

| Instruction Set Simulation with pBlazIDE                                                              |   |

| Simulator Control Buttons                                                                             |   |

| Simulating FPGA Interaction with the pBlazIDE Instruction Set Simulator 8                             |   |

| Turbocharging Simulation using FPGAs!                                                                 |   |

| Appendix A: Related Materials and References                                                          |   |

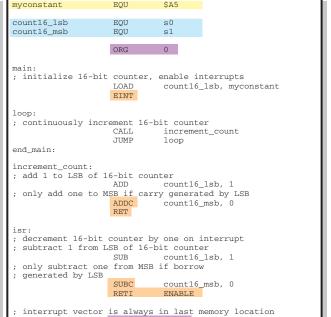

| Appendix B: Example Program Templates                                                                 |   |

| KCPSM3 Syntax                                                                                         | 5 |

| pBlazIDE Syntax                                                                                       |   |

| pbiazibe symax                                                                                        | 5 |

| Appendix C: PicoBlaze Instruction Set and Event Reference                                             |   |

| ADD sX, Operand —Add Operand to Register sX                                                           |   |

| ADDCY sX, Operand —Add Operand to Register sX with Carry                                              |   |

| AND sX, Operand — Logical Bitwise AND Register sX with Operand 89                                     |   |

| CALL [Condition,] Address — Call Subroutine at Specified Address, Possibly v                          |   |

| Conditions 9                                                                                          |   |

| COMPARE sX, Operand — Compare Operand with Register sX                                                |   |

| DISABLE INTERRUPT — Disable External Interrupt Input                                                  | 3 |

| INTERRUPT Event, When Enabled96                                                                 |

|-------------------------------------------------------------------------------------------------|

| JUMP [Condition,] Address — Jump to Specified Address, Possibly with Conditio                   |

| LOAD sX, Operand — Load Register sX with Operand                                                |

| OR sX, Operand — Logical Bitwise OR Register sX with Operand 99                                 |

| OUTPUT sX, Operand — Write Register sX Value to OUT_PORT, Set PORT_ID to Operand                |

| <b>RESET Event</b>                                                                              |

| RETURN [Condition] — Return from Subroutine Call, Possibly with Conditions 1                    |

| RETURNI [ENABLE/DISABLE] — Return from Interrupt Service Routine and Enab<br>Disable Interrupts |

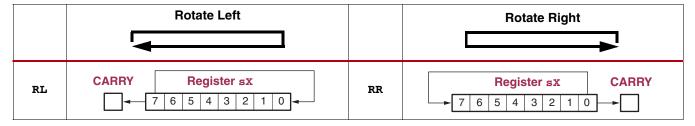

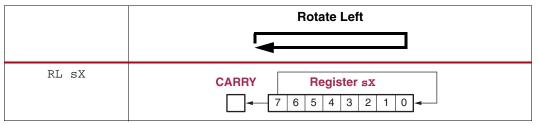

| RL sX — Rotate Left Register sX                                                                 |

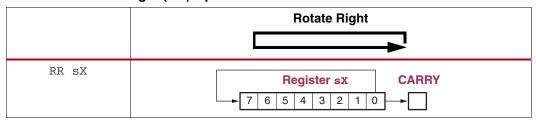

| RR sX — Rotate Right Register sX                                                                |

| <b>SL[0   1   X   A] sX — Shift Left Register sX</b>                                            |

| SR[0   1   X   A] sX — Shift Right Register sX.       106                                       |

| STORE sX, Operand — Write Register sX Value to Scratchpad RAM Location 108                      |

| SUB sX, Operand —Subtract Operand from Register sX                                              |

| SUBCY sX, Operand —Subtract Operand from Register sX with Borrow 110                            |

| TEST sX, Operand — Test Bit Location in Register sX, Generate Odd Parity . 112                  |

| XOR sX, Operand — Logical Bitwise XOR Register sX with Operand 114                              |

| endix D: Instruction Codes                                                                      |

# About This Guide

The PicoBlaze™ embedded microcontroller is an efficient, cost-effective embedded processor core for Xilinx FPGAs. This user guide describes in detail the capabilities, features, and benefits of the KCPSM3 version of PicoBlaze for Spartan®-3 and Virtex®-5 FPGAs covering the hardware design and how to effectively use the PicoBlaze instruction set and tools to create software applications. It is also an introduction to the superior KCPSM6 version of PicoBlaze for use with Spartan-6, Virtex-6 and 7 Series FPGAs.

#### **Guide Contents**

This manual contains the following chapters:

- Chapter 1 Introduction describes the features and functional blocks of the PicoBlaze microcontroller.

- Chapter 2 PicoBlaze Interface Signals defines the PicoBlaze signals.

- Chapter 3 PicoBlaze Instruction Set summarizes the instruction set of the PicoBlaze microcontrollers.

- Chapter 4 Interrupts describes how the PicoBlaze microcontroller uses interrupts.

- Chapter 5 Scratchpad RAM describes the 64-byte scratchpad RAM.

- Chapter 6 Input and Output Ports describes the input and output ports supported by the PicoBlaze microcontroller.

- Chapter 7 Instruction Storage Configurations provides several examples of instruction storage with the PicoBlaze microcontroller.

- Chapter 8 Performance provides performance values for the PicoBlaze microcontroller.

- Chapter 9 Using the PicoBlaze Microcontroller in an FPGA Design describes the design flow process with the PicoBlaze microcontroller.

- Chapter 10 PicoBlaze Development Tools describes the available development tools.

- Chapter 11 Assembler Directives describes the assembler directives that provide advanced control.

- Chapter 12 Simulating PicoBlaze Code describes the tools that simulate PicoBlaze code.

- Appendix A Related Materials and References provides additional resources useful for the PicoBlaze microcontroller design.

- Appendix B Example Program Templates provides example KCPSM3 and pBlazIDE code templates for use in application programs.

- Appendix C PicoBlaze Instruction Set and Event Reference summarizes the PicoBlaze instructions and events in alphabetical order.

- Appendix D Instruction Codes provides the 18-bit instruction codes for all PicoBlaze instructions.

- Appendix E Register and Scratchpad RAM Planning Worksheets provides worksheets to use for the PicoBlaze microcontroller design.

# Introduction

The PicoBlaze™ microcontroller is a compact, capable, and cost-effective fully embedded 8-bit RISC microcontroller core optimized for the Xilinx FPGA families. The KCPSM3 version described in this user guide occupies just 96 FPGA slices in a Spartan®-3 Generation FPGA which is only 12.5% of an XC3S500 device and a miniscule 0.3% of an XC3S5000 device. In typical implementations, a single FPGA block RAM stores up to 1024 program instructions, which are automatically loaded during FPGA configuration. Even with such resource efficiency, the PicoBlaze microcontroller performs a respectable 44 to 100 million instructions per second (MIPS) depending on the target FPGA family and speed grade.

The KCPSM6 version of the PicoBlaze microcontroller is optimized for the Spartan-6, Virtex®-6, and 7 Series FPGAs and exploits the progress in technology to provide an even higher degree of efficiency. The KCPSM6 microcontroller is a superset of KCPSM3 and is incredibly small occupying only 26 Slices. Full documentation is provided with KCPSM6 available for download from the Xilinx website (see Appendix A, "Related Materials and References").

The PicoBlaze microcontroller core is totally embedded within the target FPGA and requires no external resources. The PicoBlaze microcontroller is extremely flexible. The basic functionality is easily extended and enhanced by connecting additional FPGA logic to the microcontroller's input and output ports.

The PicoBlaze microcontroller provides abundant, flexible I/O at much lower cost than off-the-shelf controllers. Similarly, the PicoBlaze peripheral set can be customized to meet the specific features, function, and cost requirements of the target application. Because the PicoBlaze microcontroller is delivered as synthesizable VHDL source code, the core is future-proof and can be migrated to future FPGA architectures, effectively eliminating product obsolescence fears. Being integrated within the FPGA, the PicoBlaze microcontroller reduces board space, design cost, and inventory.

The PicoBlaze FPC is supported by a suite of development tools including an assembler, a graphical integrated development environment (IDE), a graphical instruction set simulator, and VHDL source code and simulation models. Similarly, the PicoBlaze microcontroller is also supported in the Xilinx System Generator development environment.

The various PicoBlaze code examples throughout this application note are written for the Xilinx KCPSM3 assembler. The Mediatronix pBlazIDE assembler has a code import function that reads the KCPSM3 syntax.

#### **PicoBlaze Microcontroller Features**

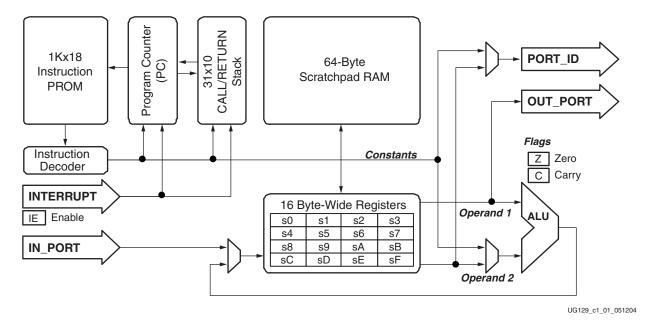

As shown in the block diagram in Figure 1-1, the PicoBlaze microcontroller supports the following features:

- 16 byte-wide general-purpose data registers

- 1K instructions of programmable on-chip program store, automatically loaded during FPGA configuration

- Byte-wide Arithmetic Logic Unit (ALU) with CARRY and ZERO indicator flags

- 64-byte internal scratchpad RAM

- 256 input and 256 output ports for easy expansion and enhancement

- Automatic 31-location CALL/RETURN stack

- Predictable performance, always two clock cycles per instruction, up to 200 MHz or 100 MIPS in a Virtex-II Pro FPGA

- Fast interrupt response; worst-case 5 clock cycles

- Optimized for Xilinx Spartan-3 architecture—just 96 slices and 0.5 to 1 block RAM

- Support in Spartan-6, and Virtex-6 FPGA architectures

- Assembler, instruction-set simulator support

Figure 1-1: PicoBlaze Embedded Microcontroller Block Diagram

# **PicoBlaze Microcontroller Functional Blocks**

# General-Purpose Registers

The PicoBlaze microcontroller includes 16 byte-wide general-purpose registers, designated as registers s0 through sF. For better program clarity, registers can be renamed using an assembler directive. All register operations are completely interchangeable; no registers are reserved for special tasks or have priority over any other register. There is no dedicated accumulator; each result is computed in a specified register.

## 1,024-Instruction Program Store

The PicoBlaze microcontroller executes up to 1,024 instructions from memory within the FPGA, typically from a single block RAM. Each PicoBlaze instruction is 18 bits wide. The instructions are compiled within the FPGA design and automatically loaded during the FPGA configuration process.

Other memory organizations are possible to accommodate more PicoBlaze controllers within a single FPGA or to enable interactive code updates without recompiling the FPGA design. See Chapter 7 Instruction Storage Configurations for more information.

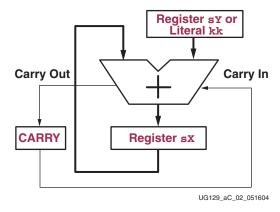

# Arithmetic Logic Unit (ALU)

The byte-wide Arithmetic Logic Unit (ALU) performs all microcontroller calculations, including:

- basic arithmetic operations such as addition and subtraction

- bitwise logic operations such as AND, OR, and XOR

- arithmetic compare and bitwise test operations

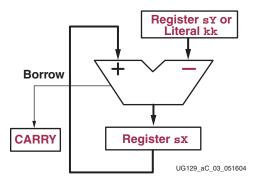

- comprehensive shift and rotate operations

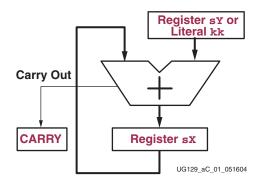

All operations are performed using an operand provided by any specified register (sx). The result is returned to the same specified register (sx). If an instruction requires a second operand, then the second operand is either a second register (sx) or an 8-bit immediate constant (kk).

# Flags

ALU operations affect the ZERO and CARRY flags. The ZERO flag indicates when the result of the last operation resulted in zero. The CARRY flag indicates various conditions, depending on the last instruction executed.

The INTERRUPT\_ENABLE flag enables the INTERRUPT input.

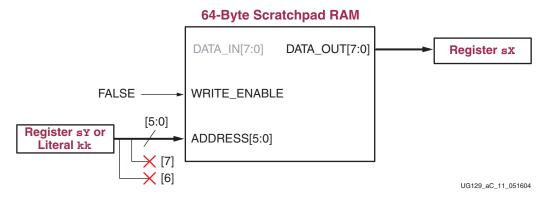

# 64-Byte Scratchpad RAM

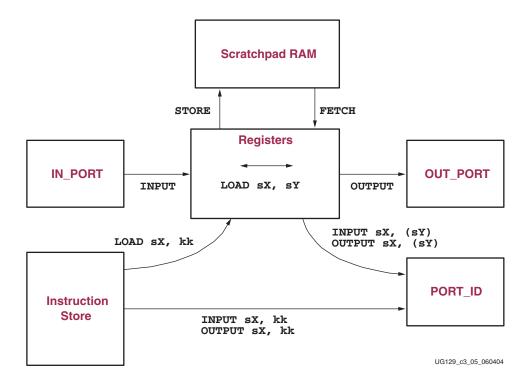

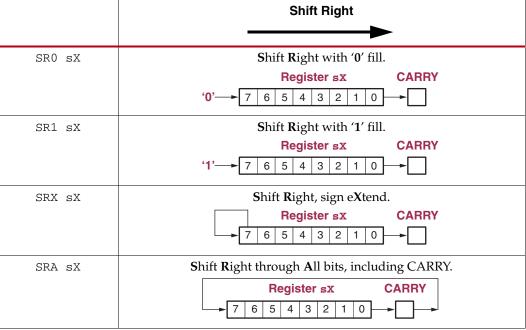

The PicoBlaze microcontroller provides an internal general-purpose 64-byte scratchpad RAM, directly or indirectly addressable from the register file using the STORE and FETCH instructions.

The STORE instruction writes the contents of any of the 16 registers to any of the 64 RAM locations. The complementary FETCH instruction reads any of the 64 memory locations into any of the 16 registers. This allows a much greater number of variables to be held within the boundary of the processor and tends to reserve all of the I/O space for real inputs and output signals.

The six-bit scratchpad RAM address is specified either directly (ss) with an immediate constant, or indirectly using the contents of any of the 16 registers (sy). Only the lower six bits of the address are used; the address should not exceed the 00 - 3F range of the available memory.

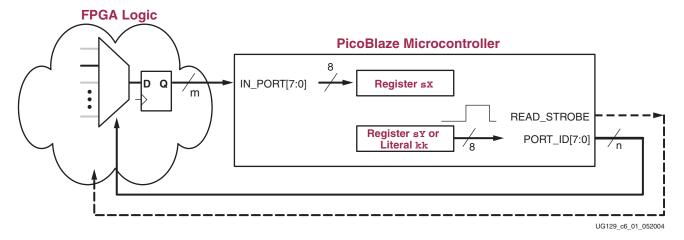

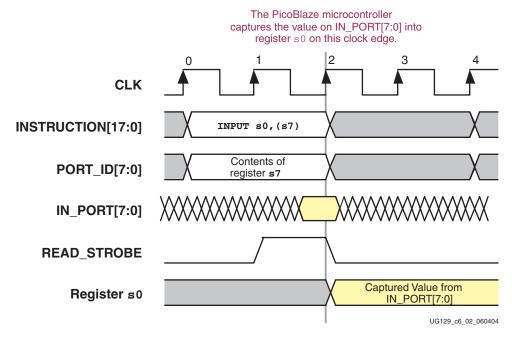

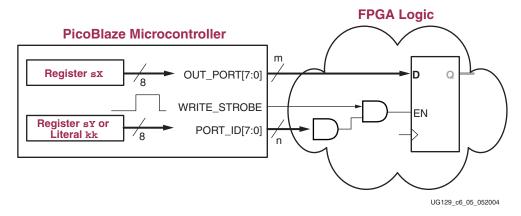

## Input/Output

The Input/Output ports extend the PicoBlaze microcontroller's capabilities and allow the microcontroller to connect to a custom peripheral set or to other FPGA logic. The PicoBlaze microcontroller supports up to 256 input ports and 256 output ports or a combination of input/output ports. The PORT\_ID output provides the port address. During an INPUT operation, the PicoBlaze microcontroller reads data from the IN\_PORT port to a specified register, sx. During an OUTPUT operation, the PicoBlaze microcontroller writes the contents of a specified register, sx, to the OUT\_PORT port.

See Chapter 6 Input and Output Ports for more information.

## Program Counter (PC)

The Program Counter (PC) points to the next instruction to be executed. By default, the PC automatically increments to the next instruction location when executing an instruction. Only the JUMP, CALL, RETURN, and RETURNI instructions and the Interrupt and Reset Events modify the default behavior. The PC cannot be directly modified by the application code; computed jump instructions are not supported.

The 10-bit PC supports a maximum code space of 1,024 instructions (000 to 3FF hex). If the PC reaches the top of the memory at 3FF hex, it rolls over to location 000.

## **Program Flow Control**

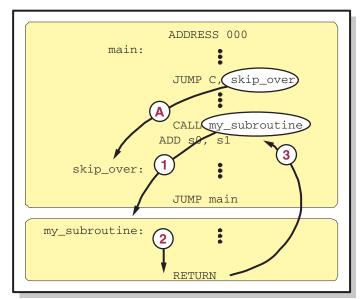

The default execution sequence of the program can be modified using conditional and non-conditional program flow control instructions.

The JUMP instructions specify an absolute address anywhere in the 1,024-instruction program space.

CALL and RETURN instructions provide subroutine facilities for commonly used sections of code. A CALL instruction specifies the absolute start address of a subroutine, while the return address is automatically preserved on the CALL/RETURN stack.

If the interrupt input is enabled, an Interrupt Event also preserves the address of the preempted instruction on the CALL/RETURN stack while the PC is loaded with the interrupt vector, 3FF hex. Use the RETURNI instruction instead of the RETURN instruction to return from the interrupt service routine (ISR).

#### CALL/RETURN Stack

The CALL/RETURN hardware stack stores up to 31 instruction addresses, enabling nested CALL sequences up to 31 levels deep. Since the stack is also used during an interrupt operation, at least one of these levels should be reserved when interrupts are enabled.

The stack is implemented as a separate cyclic buffer. When the stack is full, it overwrites the oldest value. Consequently, there are no instructions to control the stack or the stack pointer. No program memory is required for the stack.

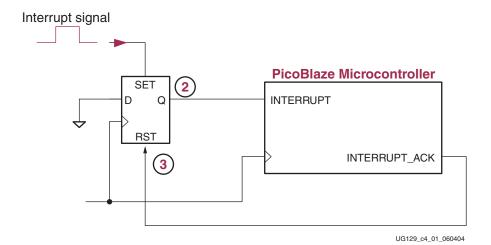

# Interrupts

The PicoBlaze microcontroller has an optional INTERRUPT input, allowing the PicoBlaze microcontroller to handle asynchronous external events. In this context, "asynchronous" relates to interrupts occurring at any time during an instruction cycle. However,

recommended design practice is to synchronize all inputs to the PicoBlaze controller using the clock input.

The PicoBlaze microcontroller responds to interrupts quickly in just five clock cycles.

See Chapter 4 Interrupts for more information.

#### Reset

The PicoBlaze microcontroller is automatically reset immediately after the FPGA configuration process completes. After configuration, the RESET input forces the processor into the initial state. The PC is reset to address 0, the flags are cleared, interrupts are disabled, and the CALL/RETURN stack is reset.

The data registers and scratchpad RAM are not affected by Reset.

See RESET Event in Appendix C for more information.

# Why the PicoBlaze Microcontroller?

There are literally dozens of 8-bit microcontroller architectures and instruction sets. Modern FPGAs can efficiently implement practically any 8-bit microcontroller, and available FPGA soft cores support popular instruction sets such as the PIC, 8051, AVR, 6502, 8080, and Z80 microcontrollers. Why use the PicoBlaze microcontroller instead of a more popular instruction set?

The PicoBlaze microcontroller is specifically designed and optimized for the Spartan-3 family, and with support for Spartan-6, and Virtex-6 FPGA architectures. Its compact yet capable architecture consumes considerably less FPGA resources than comparable 8-bit microcontroller architectures within an FPGA. Furthermore, the PicoBlaze microcontroller is provided as a free, source-level VHDL file with royalty-free re-use within Xilinx FPGAs.

Some standalone microcontroller variants have a notorious reputation for becoming obsolete. Because it is delivered as VHDL source, the PicoBlaze microcontroller is immune to product obsolescence as the microcontroller can be retargeted to future generations of Xilinx FPGAs, exploiting future cost reductions and feature enhancements. Furthermore, the PicoBlaze microcontroller is expandable and extendable.

Before the advent of the PicoBlaze and MicroBlaze<sup>TM</sup> embedded processors, the microcontroller resided externally to the FPGA, limiting the connectivity to other FPGA functions and restricting overall interface performance. By contrast, the PicoBlaze microcontroller is fully embedded in the FPGA with flexible, extensive on-chip connectivity to other FPGA resources. Signals remain within the FPGA, improving overall performance. The PicoBlaze microcontroller reduces system cost because it is a single-chip solution, integrated within the FPGA and sometimes only occupying leftover FPGA resources.

The PicoBlaze microcontroller is resource efficient. Consequently, complex applications are sometimes best portioned across multiple PicoBlaze microcontrollers with each controller implementing a particular function, for example, keyboard and display control, or system management.

# Why Use a Microcontroller within an FPGA?

Microcontrollers and FPGAs both successfully implement practically any digital logic function. However, each has unique advantages in cost, performance, and ease of use. Microcontrollers are well suited to control applications, especially with widely changing

requirements. The FPGA resources required to implement the microcontroller are relatively constant. The same FPGA logic is re-used by the various microcontroller instructions, conserving resources. The program memory requirements grow with increasing complexity.

Programming control sequences or state machines in assembly code is often easier than creating similar structures in FPGA logic.

Microcontrollers are typically limited by performance. Each instruction executes sequentially. As an application increases in complexity, the number of instructions required to implement the application grows and system performance decreases accordingly. By contrast, performance in an FPGA is more flexible. For example, an algorithm can be implemented sequentially or completely in parallel, depending on the performance requirements. A completely parallel implementation is faster but consumes more FPGA resources.

A microcontroller embedded within the FPGA provides the best of both worlds. The microcontroller implements non-timing crucial complex control functions while timing-critical or data path functions are best implemented using FPGA logic. For example, a microcontroller cannot respond to events much faster than a few microseconds. The FPGA logic can respond to multiple, simultaneous events in just a few to tens of nanoseconds. Conversely, a microcontroller is cost-effective and simple for performing format or protocol conversions.

Table 1-1: PicoBlaze Microcontroller Embedded within an FPGA Provides the Optimal Balance between Microcontroller and FPGA Solutions

|            | PicoBlaze Microcontroller                                                                                                                                                                                                                       | FPGA Logic                                                                                                                                                                                                                                    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Strengths  | <ul> <li>Easy to program, excellent for control and state machine applications</li> <li>Resource requirements remain constant with increasing complexity</li> <li>Re-uses logic resources, excellent for lower-performance functions</li> </ul> | <ul> <li>Significantly higher performance</li> <li>Excellent at parallel operations</li> <li>Sequential vs. parallel implementation tradeoffs optimize performance or cost</li> <li>Fast response to multiple, simultaneous inputs</li> </ul> |

| Weaknesses | <ul> <li>Executes sequentially</li> <li>Performance degrades with increasing complexity</li> <li>Program memory requirements increase with increasing complexity</li> <li>Slower response to simultaneous inputs</li> </ul>                     | <ul> <li>Control and state machine applications more<br/>difficult to program</li> <li>Logic resources grow with increasing<br/>complexity</li> </ul>                                                                                         |

# PicoBlaze Interface Signals

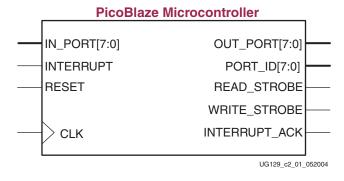

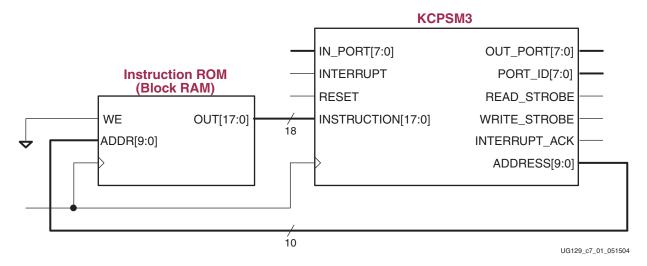

The top-level interface signals to the PicoBlaze™ microcontroller appear in Figure 2-1 and are described in Table 2-1. Figure 7-1 provides additional detail on the internal structure of the PicoBlaze controller.

Figure 2-1: PicoBlaze Interface Connections

Table 2-1: PicoBlaze Interface Signal Descriptions

| Signal        | Direction | Description                                                                                                                                                                                                                                                                                                      |

|---------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN_PORT[7:0]  | Input     | <b>Input Data Port:</b> Present valid input data on this port during an INPUT instruction. The data is captured on the rising edge of CLK.                                                                                                                                                                       |

| INTERRUPT     | Input     | <b>Interrupt Input:</b> If the INTERRUPT_ENABLE flag is set by the application code, generate an INTERRUPT Event by asserting this input High for at least two CLK cycles. If the INTERRUPT_ENABLE flag is cleared, this input is ignored.                                                                       |

| RESET         | Input     | <b>Reset Input:</b> To reset the PicoBlaze microcontroller and to generate a RESET Event, assert this input High for at least one CLK cycle. A Reset Event is automatically generated immediately following FPGA configuration.                                                                                  |

| CLK           | Input     | Clock Input: The frequency may range from DC to the maximum operating frequency reported by the Xilinx ISE® development software. All PicoBlaze synchronous elements are clocked from the rising clock edge. There are no clock duty-cycle requirements beyond the minimum pulse width requirements of the FPGA. |

| OUT_PORT[7:0] | Output    | Output Data Port: Output data appears on this port for two CLK cycles during an OUTPUT instruction. Capture output data within the FPGA at the rising CLK edge when WRITE_STROBE is High.                                                                                                                        |

| PORT_ID[7:0]  | Output    | <b>Port Address:</b> The I/O port address appears on this port for two CLK cycles during an INPUT or OUTPUT instruction.                                                                                                                                                                                         |

Table 2-1: PicoBlaze Interface Signal Descriptions (Cont'd)

| Signal        | Direction | Description                                                                                                                                                                                                                                                                                                                                  |

|---------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READ_STROBE   | Output    | <b>Read Strobe:</b> When asserted High, this signal indicates that input data on the IN_PORT[7:0] port was captured to the specified data register during an INPUT instruction. This signal is asserted on the second CLK cycle of the two-cycle INPUT instruction. This signal is typically used to acknowledge read operations from FIFOs. |

| WRITE_STROBE  | Output    | Write Strobe: When asserted High, this signal validates the output data on the OUT_PORT[7:0] port during an OUTPUT instruction. This signal is asserted on the second CLK cycle of the two-cycle OUTPUT instruction. Capture output data within the FPGA on the rising CLK edge when WRITE_STROBE is High.                                   |

| INTERRUPT_ACK | Output    | Interrupt Acknowledge: When asserted High, this signal acknowledges that an INTERRUPT Event occurred. This signal is asserted during the second CLK cycle of the two-cycle INTERRUPT Event. This signal is optionally used to clear the source of the INTERRUPT input.                                                                       |

# PicoBlaze Instruction Set

Table 3-1 summarizes the entire PicoBlaze™ processor instruction set, which appears alphabetically. Instructions are listed using the KCPSM3 syntax. If different, the pBlazIDE syntax appears in parentheses. Each instruction includes an overview description, a functional description, and how the ZERO and CARRY flags are affected. For more details on each instruction, see Appendix C PicoBlaze Instruction Set and Event Reference.

Table 3-1: PicoBlaze Instruction Set (alphabetical listing)

| Instruction              | Description                                                       | Function                                                      | ZERO | CARRY |

|--------------------------|-------------------------------------------------------------------|---------------------------------------------------------------|------|-------|

| ADD sX, kk               | Add register sX with literal kk                                   | $sX \leftarrow sX + kk$                                       | ?    | ?     |

| ADD sX, sY               | Add register sX with register sY                                  | $sX \leftarrow sX + sY$                                       | ?    | ?     |

| ADDCY sX, kk<br>(ADDC)   | Add register sX with literal kk with CARRY bit                    | $sX \leftarrow sX + kk + CARRY$                               | ?    | ?     |

| ADDCY sX, sY<br>(ADDC)   | Add register sX with register sY with CARRY bit                   | $sX \leftarrow sX + sY + CARRY$                               | ?    | ?     |

| AND sX, kk               | Bitwise AND register sX with literal kk                           | sX ← sX AND kk                                                | ?    | 0     |

| AND sX, sY               | Bitwise AND register sX with register sY                          | sX ← sX AND sY                                                | ?    | 0     |

| CALL aaa                 | Unconditionally call subroutine at aaa                            | TOS ← PC                                                      | -    | -     |

|                          |                                                                   | PC ← aaa                                                      |      |       |

| CALL C, aaa              | If CARRY flag set, call subroutine at aaa                         | If CARRY=1, {TOS ← PC, PC ← aaa}                              | -    | -     |

| CALL NC, aaa             | If CARRY flag not set, call subroutine at aaa                     | If CARRY=0, {TOS ← PC, PC ← aaa}                              | -    | -     |

| CALL NZ, aaa             | If ZERO flag not set, call subroutine at aaa                      | If ZERO=0, $\{TOS \leftarrow PC, PC \leftarrow aaa\}$         | -    | -     |

| CALL Z, aaa              | If ZERO flag set, call subroutine at aaa                          | If ZERO=1, $\{TOS \leftarrow PC, PC \leftarrow aaa\}$         | -    | -     |

| COMPARE sX, kk           | Compare register sX with literal kk. Set                          | If sX=kk, ZERO ← 1                                            | ?    | ?     |

| (COMP)                   | CARRY and ZERO flags as appropriate.<br>Registers are unaffected. | If sX <kk, 1<="" carry="" td="" ←=""><td></td><td></td></kk,> |      |       |

| COMPARE sX, sY           | Compare register sX with register sY. Set                         | If sX=sY, ZERO ← 1                                            | ?    | ?     |

| (COMP)                   | CARRY and ZERO flags as appropriate.<br>Registers are unaffected. | If sX <sy, <math="" carry="">\leftarrow 1</sy,>               |      |       |

| DISABLE INTERRUPT (DINT) | Disable interrupt input                                           | INTERRUPT_ENABLE ← 0                                          | -    | -     |

Table 3-1: PicoBlaze Instruction Set (alphabetical listing)

| Instruction                      | Description                                                                                                                | Function                                                                                 | ZERO | CARRY |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------|-------|

| ENABLE INTERRUPT<br>(EINT)       | Enable interrupt input                                                                                                     | INTERRUPT_ENABLE ← 1                                                                     | -    | -     |

| Interrupt Event                  | Asynchronous interrupt input. Preserve flags and PC. Clear INTERRUPT_ENABLE flag. Jump to interrupt vector at address 3FF. | Preserved ZERO ← ZERO  Preserved CARRY ← CARRY  INTERRUPT_ENABLE ← 0  TOS ← PC  PC ← 3FF | -    | -     |

| FETCH sX, (sY)<br>(FETCH sX, sY) | Read scratchpad RAM location pointed to by register sY into register sX                                                    | $sX \leftarrow RAM[(sY)]$                                                                | -    | -     |

| FETCH sX, ss                     | Read scratchpad RAM location ss into register sX                                                                           | $sX \leftarrow RAM[ss]$                                                                  | -    | -     |

| INPUT sX, (sY)<br>(IN sX, sY)    | Read value on input port location pointed to by register sY into register sX                                               | PORT_ID ← sY<br>sX ← IN_PORT                                                             | -    | -     |

| INPUT sX, pp<br>(IN)             | Read value on input port location pp into register sX                                                                      | PORT_ID ← pp<br>sX ← IN_PORT                                                             | -    | -     |

| JUMP aaa                         | Unconditionally jump to aaa                                                                                                | PC ← aaa                                                                                 | -    | -     |

| JUMP C, aaa                      | If CARRY flag set, jump to aaa                                                                                             | If CARRY=1, PC ← aaa                                                                     | -    | -     |

| JUMP NC, aaa                     | If CARRY flag not set, jump to aaa                                                                                         | If CARRY=0, PC ← aaa                                                                     | -    | -     |

| JUMP NZ, aaa                     | If ZERO flag not set, jump to aaa                                                                                          | If ZERO=0, PC ← aaa                                                                      | -    | -     |

| JUMP Z, aaa                      | If ZERO flag set, jump to aaa                                                                                              | If ZERO=1, PC ← aaa                                                                      | -    | -     |

| LOAD sX, kk                      | Load register sX with literal kk                                                                                           | sX ← kk                                                                                  | -    | -     |

| LOAD sX, sY                      | Load register sX with register sY                                                                                          | sX ← sY                                                                                  | -    | -     |

| OR sX, kk                        | Bitwise OR register sX with literal kk                                                                                     | sX ← sX OR kk                                                                            | ?    | 0     |

| OR sX, sY                        | Bitwise OR register sX with register sY                                                                                    | sX ← sX OR sY                                                                            | ?    | 0     |

| OUTPUT sX, (sY)<br>(OUT sX, sY)  | Write register sX to output port location pointed to by register sY                                                        | PORT_ID ← sY OUT_PORT ← sX                                                               | -    | -     |

| OUTPUT sX, pp<br>(OUT sX, pp)    | Write register sX to output port location pp                                                                               | PORT_ID ← pp<br>OUT_PORT ← sX                                                            | -    | -     |

| RETURN<br>(RET)                  | Unconditionally return from subroutine                                                                                     | PC ← TOS+1                                                                               | -    | -     |

| RETURN C<br>(RET C)              | If CARRY flag set, return from subroutine                                                                                  | If CARRY=1, PC ← TOS+1                                                                   | -    | -     |

| RETURN NC<br>(RET NC)            | If CARRY flag not set, return from subroutine                                                                              | If CARRY=0, PC ← TOS+1                                                                   | -    | -     |

| RETURN NZ<br>(RET NZ)            | If ZERO flag not set, return from subroutine                                                                               | If ZERO=0, PC ← TOS+1                                                                    | -    | -     |

| RETURN Z<br>(RET Z)              | If ZERO flag set, return from subroutine                                                                                   | If ZERO=1, PC ← TOS+1                                                                    | -    | -     |

Table 3-1: PicoBlaze Instruction Set (alphabetical listing)

| Instruction                       | Description                                                                  | Function                                                                    | ZERO | CARRY |

|-----------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------|-------|

| RETURNI DISABLE<br>(RETI DISABLE) | Return from interrupt service routine. Interrupt remains disabled.           | PC ← TOS ZERO ← Preserved ZERO CARRY ← Preserved CARRY INTERRUPT_ENABLE ← 0 | ?    | ?     |

| RETURNI ENABLE<br>(RETI ENABLE)   | Return from interrupt service routine. Re-enable interrupt.                  | PC ← TOS ZERO ← Preserved ZERO CARRY ← Preserved CARRY INTERRUPT_ENABLE ← 1 | ?    | ?     |

| RL sX                             | Rotate register sX left                                                      | $sX \leftarrow \{sX[6:0], sX[7]\}$<br>$CARRY \leftarrow sX[7]$              | ?    | ?     |

| RR sX                             | Rotate register sX right                                                     | $sX \leftarrow \{sX[0], sX[7:1]\}$<br>$CARRY \leftarrow sX[0]$              | ?    | ?     |

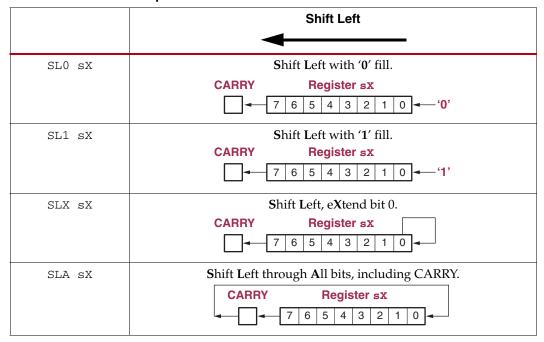

| SL0 sX                            | Shift register sX left, zero fill                                            | $sX \leftarrow \{sX[6:0],0\}$<br>$CARRY \leftarrow sX[7]$                   | ?    | ?     |

| SL1 sX                            | Shift register sX left, one fill                                             | $sX \leftarrow \{sX[6:0],1\}$<br>$CARRY \leftarrow sX[7]$                   | 0    | ?     |

| SLA sX                            | Shift register sX left through all bits, including CARRY                     | $sX \leftarrow \{sX[6:0],CARRY\}$<br>$CARRY \leftarrow sX[7]$               | ?    | ?     |

| SLX sX                            | Shift register sX left. Bit sX[0] is unaffected.                             | $sX \leftarrow \{sX[6:0], sX[0]\}$<br>$CARRY \leftarrow sX[7]$              | ?    | ?     |

| SR0 sX                            | Shift register sX right, zero fill                                           | $sX \leftarrow \{0, sX[7:1]\}$<br>$CARRY \leftarrow sX[0]$                  | ?    | ?     |

| SR1 sX                            | Shift register sX right, one fill                                            | $sX \leftarrow \{1, sX[7:1]\}$ $CARRY \leftarrow sX[0]$                     | 0    | ?     |

| SRA sX                            | Shift register sX right through all bits, including CARRY                    | $sX \leftarrow \{CARRY, sX[7:1]\}$<br>$CARRY \leftarrow sX[0]$              | ?    | ?     |

| SRX sX                            | Arithmetic shift register sX right. Sign extend sX. Bit sX[7] Is unaffected. | $sX \leftarrow \{sX[7], sX[7:1]\}$<br>$CARRY \leftarrow sX[0]$              | ?    | ?     |

| STORE sX, (sY)<br>(STORE sX, sY)  | Write register sX to scratchpad RAM location pointed to by register sY       | $RAM[(sY)] \leftarrow sX$                                                   | -    | -     |

| STORE sX, ss                      | Write register sX to scratchpad RAM location ss                              | $RAM[ss] \leftarrow sX$                                                     | -    | -     |

| SUB sX, kk                        | Subtract literal kk from register sX                                         | $sX \leftarrow sX - kk$                                                     | ?    | ?     |

| SUB sX, sY                        | Subtract register sY from register sX                                        | $sX \leftarrow sX - sY$                                                     | ?    | ?     |

| SUBCY sX, kk<br>(SUBC)            | Subtract literal kk from register sX with CARRY (borrow)                     | $sX \leftarrow sX - kk - CARRY$                                             | ?    | ?     |

| SUBCY sX, sY<br>(SUBC)            | Subtract register sY from register sX with CARRY (borrow)                    | $sX \leftarrow sX - sY - CARRY$                                             | ?    | ?     |

Table 3-1: PicoBlaze Instruction Set (alphabetical listing)

| Instruction | Description                                                                                               | Function                                                                                                       | ZERO | CARRY |

|-------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|-------|

| TEST sX, kk | Test bits in register sX against literal kk.<br>Update CARRY and ZERO flags. Registers<br>are unaffected. | If $(sX \text{ AND } kk) = 0$ , ZERO $\leftarrow 1$<br>CARRY $\leftarrow$ odd parity of $(sX \text{ AND } kk)$ | ?    | ?     |

| TEST sX, sY | Test bits in register sX against register sX. Update CARRY and ZERO flags. Registers are unaffected.      | If $(sX \text{ AND } sY) = 0$ , ZERO $\leftarrow 1$<br>CARRY $\leftarrow$ odd parity of $(sX \text{ AND } kk)$ | ?    | ?     |

| XOR sX, kk  | Bitwise XOR register sX with literal kk                                                                   | sX ← sX XOR kk                                                                                                 | ?    | 0     |

| XOR sX, sY  | Bitwise XOR register sX with register sY                                                                  | sX ← sX XOR sY                                                                                                 | ?    | 0     |

- sX = One of 16 possible register locations ranging from s0 through sF or specified as a literal

- sY = One of 16 possible register locations ranging from s0 through sF or specified as a literal

- aaa = 10-bit address, specified either as a literal or a three-digit hexadecimal value ranging from 000 to 3FF or a labeled location

- kk = 8-bit immediate constant, specified either as a literal or a two-digit hexadecimal value ranging from 00 to FF or specified as a literal

- pp = 8-bit port address, specified either as a literal or a two-digit hexadecimal value ranging from 00 to FF or specified as a literal

- ss = 6-bit scratchpad RAM address, specified either as a literal or a two-digit hexadecimal value ranging from 00 to 3F or specified as a literal

- RAM[n] = Contents of scratchpad RAM at location n

- TOS = Value stored at Top Of Stack

# **Address Spaces**

As shown in Table 3-2, the PicoBlaze microcontroller has five distinct address spaces. Specific instructions operate on each of the address spaces.

Table 3-2: PicoBlaze Address Spaces and Related Instructions

| Address Space     | Size<br>(Depth x Width) | Addressing<br>Modes | Instructions that Operate on<br>Address Space                                                                                                                                                                   |

|-------------------|-------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction       | 1Kx18                   | Direct              | <ul> <li>JUMP</li> <li>CALL</li> <li>RETURN</li> <li>RETURNI</li> <li>INTERRUPT event</li> <li>RESET event</li> <li>All others increment the PC to the next location</li> </ul>                                 |

| Register File     | 16x8                    | Direct              | • LOAD • AND • OR • XOR • TEST (read only) • ADD • ADDCY • SUB • SUBCY • COMPARE (read only) • SRO • SR1 • SRX • SRA • RR • SLO • SL1 • SLX • SLA • RL • INPUT • OUTPUT (read only) • STORE (read only) • FETCH |

| Scratchpad RAM    | 64x8                    | Direct<br>Indirect  | • STORE • FETCH                                                                                                                                                                                                 |

| I/O               | 256x8                   | Direct<br>Indirect  | • INPUT<br>• OUTPUT                                                                                                                                                                                             |

| CALL/RETURN Stack | 31x10                   | N/A                 | <ul> <li>CALL</li> <li>Enabled INTERRUPT event</li> <li>RETURN</li> <li>RETURNI</li> <li>RESET event</li> </ul>                                                                                                 |

# **Processing Data**

All data processing instructions operate on any of the 16 general-purpose registers. Only the data processing instructions modify the ZERO or CARRY flags as appropriate for the instruction. The data processing instructions consists of the following types:

- Logic instructions

- Arithmetic instructions

- Test and Compare instructions

- Shift and Rotate instructions

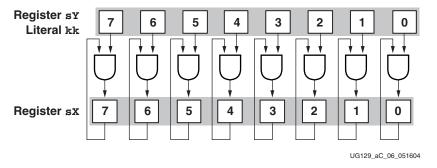

### Logic Instructions

The logic instructions perform a bitwise logical AND, OR, or XOR between two operands. The first operand is a register location. The second operand is either a register location or a literal constant. Besides performing pure AND, OR, and XOR operations, the logic instructions provide a means to:

- complement or invert a register

- clear a register

- set or clear specific bits within a register

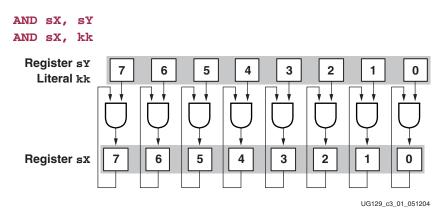

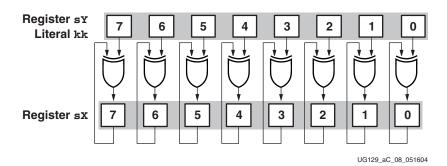

#### Bitwise AND, OR, XOR

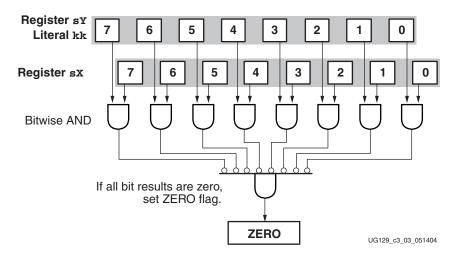

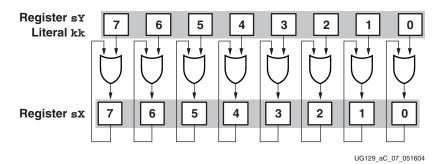

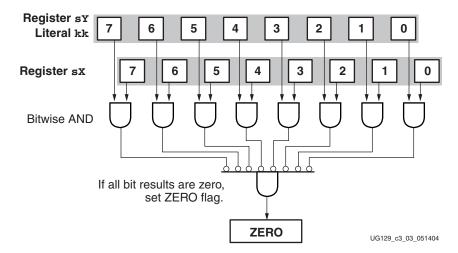

All logic instructions are bitwise operations. The AND operation, illustrated in Figure 3-1, shows that corresponding bit locations in both operands are logically ANDed together and the result is placed back into register sx. If the resulting value in register sx is zero, then the ZERO flag is set. The CARRY flag is always cleared by a logic instruction.

Figure 3-1: Bitwise AND Instruction

The OR and XOR instructions are similar to the AND instruction illustrated in Figure 3-1 except that they perform an OR or XOR logical operation, respectively.

#### See also:

- AND sX, Operand Logical Bitwise AND Register sX with Operand, page 89

- OR sX, Operand Logical Bitwise OR Register sX with Operand, page 99

- XOR sX, Operand Logical Bitwise XOR Register sX with Operand, page 114

#### Complement/Invert Register

The PicoBlaze microcontroller does not have a specific instruction to invert individual bits within register sx. However, the XOR sx, FF instruction performs the equivalent operation, as shown in Figure 3-2.

```

If reading this document in Adobe Acrobat, use the Select Text tool to select code snippets, then copy and paste the text into your text editor.

```

```

complement:

; XOR sX, FF invert all bits in register sX, same as one's complement

LOAD s0, AA ; load register s0 = 10101010

XOR s0, FF ; invert contents s0 = 01010101

```

Figure 3-2: Complementing a Register Value

#### Invert or Toggle Bit

The PicoBlaze microcontroller does not have a specific instruction to invert or toggle an individual bit or bits within a specific register. However, the XOR instruction performs the equivalent operation. XORing register sX with a bit mask inverts or toggles specific bits, as shown in Figure 3-3. A '1' in the bit mask inverts or toggles the corresponding bit in register sX. A '0' in the bit mask leaves the corresponding bit unchanged.

```

toggle_bit:

; XOR sX, <bit_mask>

XOR s0, 01 ; toggle the least-significant bit in register sX

```

Figure 3-3: Inverting an Individual Bit Location

#### Clear Register

The PicoBlaze microcontroller does not have a specific instruction to clear a specific register. However, the XOR sX, sX instruction performs the equivalent operation. XORing register sX with itself clears registers sX and sets the ZERO flag, as shown in Figure 3-4.

```

XOR sX, sX ; clear register sX, set ZERO flag

```

Figure 3-4: Clearing a Register and Setting the ZERO Flag

The LOAD sX, 00 instruction also clears register sX, but it does not affect the ZERO flag, as shown in Figure 3-5.

```

LOAD sX,00 ; clear register sX, ZERO flag unaffected

```

Figure 3-5: Clearing a Register without Modifying the ZERO Flag

#### Set Bit

The PicoBlaze microcontroller does not have a specific instruction to set an individual bit or bits within a specific register. However, the OR instruction performs the equivalent operation. ORing register sx with a bit mask sets specific bits, as shown in Figure 3-6. A '1'

in the bit mask sets the corresponding bit in register sx. A '0' in the bit mask leaves the corresponding bit unchanged.

```

set_bit:

; OR sX, <bit_mask>

OR s0, 01 ; set bit 0 of register s0

```

Figure 3-6: 16-Setting a Bit Location

#### Clear Bit

The PicoBlaze microcontroller does not have a specific instruction to clear an individual bit or bits within a specific register. However, the AND instruction performs the equivalent operation. ANDing register sX with a bit mask clears specific bits, as shown in Figure 3-7. A '0' in the bit mask clears the corresponding bit in register sX. A '1' in the bit mask leaves the corresponding bit unchanged.

```

clear_bit:

; AND sX, <bit_mask>

AND s0, FE ; clear bit 0 of register s0

```

Figure 3-7: Clearing a Bit Location

#### Arithmetic Instructions

The PicoBlaze microcontroller provides basic byte-wide addition and subtraction instructions. Combinations of instructions perform multi-byte arithmetic plus multiplication and division operations. If the end application requires significant arithmetic performance, consider using the 32-bit MicroBlaze RISC processor core for Xilinx FPGAs (see Reference 4).

#### ADD and ADDCY Add Instructions

The PicoBlaze microcontroller provides two add instructions, ADD and ADDCY, that compute the sum of two 8-bit operands, either without or with CARRY, respectively. The first operand is a register location. The second operand is either a register location or a literal constant. The resulting operation affects both the CARRY and ZERO flags. If the resulting sum is greater than 255, then the CARRY flag is set. If the resulting sum is either 0 or 256 (register sx is zero with CARRY set), then the ZERO flag is set.

The ADDCY instruction is an add operation with carry. If the CARRY flag is set, then ADDCY adds an additional one to the resulting sum.

The ADDCY instruction is commonly used in multi-byte addition. Figure 3-8 demonstrates a subroutine that adds two 16-bit integers and produces a 16-bit result. The upper byte of each 16-bit value is labeled as MSB for most-significant byte; the lower byte of each 16-bit value is labeled LSB for least-significant byte.

```

ADD16:

NAMEREG s0, a_lsb ; rename register s0 as "a_lsb"

NAMEREG s1, a_msb ; rename register s1 as "a_msb"

NAMEREG s2, b_lsb ; rename register s2 as "b_lsb"

NAMEREG s3, b_msb ; rename register s3 as "b_lsb"

ADD a_lsb, b_lsb ; add LSBs, keep result in a_lsb

ADDCY a_msb, b_msb ; add MSBs, keep result in a_msb

RETURN

```

Figure 3-8: 16-Bit Addition Using ADD and ADDCY Instructions

#### See also:

- ADD sX, Operand —Add Operand to Register sX, page 87

- ADDCY sX, Operand —Add Operand to Register sX with Carry, page 88

#### SUB and SUBCY Subtract Instructions

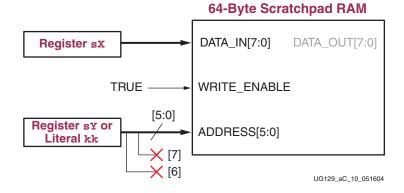

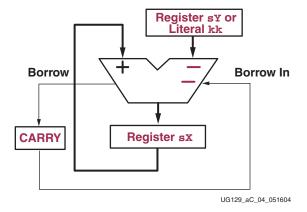

The PicoBlaze microcontroller provides two subtract instructions, SUB and SUBCY, that compute the difference of two 8-bit operands, either without or with CARRY (borrow), respectively. The CARRY flag indicates if the subtract operation generates a borrow condition. The first operand is a register location. The second operand is either a register location or a literal constant. The resulting operation affects both the CARRY and ZERO flags. If the resulting difference is less than 0, then the CARRY flag is set. If the resulting difference is 0 or -256, then the ZERO flag is set.

The SUBCY instruction is a subtract operation with borrow. If the CARRY flag is set, then SUBCY subtracts an additional one from the resulting difference.

The SUBCY instruction is commonly used in multi-byte subtraction. Figure 3-9 demonstrates a subroutine that subtracts two 16-bit integers and produces a 16-bit difference. The upper byte of each 16-bit value is labeled as MSB for most-significant byte; the lower byte of each 16-bit value is labeled LSB for least-significant byte.

```

NAMEREG s0, a_lsb ; rename register s0 as "a_lsb"

NAMEREG s1, a_msb ; rename register s1 as "a_msb"

NAMEREG s2, b_lsb ; rename register s2 as "b_lsb"

NAMEREG s3, b_msb ; rename register s3 as "b_lsb"

SUB a_lsb, b_lsb ; subtract LSBs, keep result in a_lsb

SUBCY a_msb, b_msb ; subtract MSBs, keep result in a_msb

RETURN

```

Figure 3-9: 16-Bit Subtraction Using SUB and SUBCY Instructions

#### See also:

- SUB sX, Operand —Subtract Operand from Register sX, page 109

- SUBCY sX, Operand —Subtract Operand from Register sX with Borrow, page 110

#### Increment/Decrement

The PicoBlaze microcontroller does not have a dedicated increment or decrement instruction. However, adding or subtracting one using the ADD or SUB instructions provides the equivalent operation, as shown in Figure 3-10.

```

ADD sX,01 ; increment register sX

SUB sX,01 ; decrement register sX

```

Figure 3-10: Incrementing and Decrementing a Register

If incrementing or decrementing a multi-register value—i.e., a 16-bit value—perform the operation using multiple instructions. Incrementing or decrementing a multi-byte value requires using the add or subtract instructions with carry, as shown in Figure 3-11.

```

inc_16:

; increment low byte

ADD lo_byte,01

; increment high byte only if CARRY bit set when incrementing low byte

ADDCY hi_byte,00

```

Figure 3-11: Incrementing a 16-bit Value

#### Negate

The PicoBlaze microcontroller does not have a dedicated instruction to negate a register value, taking the two's complement. However, the instructions in Figure 3-12 provide the equivalent operation.

```

Negate:

; invert all bits in the register performing a one's complement

XOR sX,FF

; add one to sX

ADD sX,01

RETURN

```

Figure 3-12: Destructive Negate (2's Complement) Function Overwrites Original

Another possible implementation that does not overwrite the value appears in Figure 3-13.

```

Negate:

NAMEREG sY, value

NAMEREG sX, complement

; Clear 'complement' to zero

LOAD complement, 00

; subtract value from 0 to create two's complement

SUB complement, value

RETURN

```

Figure 3-13: Non-destructive Negate Function Preserves Original Value

# Multiplication

The PicoBlaze microcontroller core does not have a dedicated hardware multiplier. However, the PicoBlaze microcontroller performs multiplication using the available arithmetic and shift instructions. Figure 3-14 demonstrates an 8-bit by 8-bit multiply routine that produces a 16-bit multiplier product in 50 to 57 instruction cycles, or 100 to 114 clock cycles. By contrast, the 8051 microcontroller performs the same multiplication in eight instruction cycles or 96 clock cycles on a the standard 12-cycle 8051.

```

; Multiplier Routine (8-bit x 8-bit = 16-bit product)

; Shift and add algorithm

mult_8x8:

NAMEREG s0, multiplicand ; preserved

; preserved

NAMEREG s1, multiplier

NAMEREG s2, bit_mask

; modified

NAMEREG s3, result_msb

; most-significant byte (MSB) of result,

modified

NAMEREG s4, result_lsb

; least-significant byte (LSB) of result

; modified

LOAD bit_mask, 01

; start with least-significant bit (lsb)

LOAD result_msb, 00

; clear product MSB

LOAD result_lsb, 00

; clear product LSB (not required)

; loop through all bits in multiplier

mult_loop: TEST multiplier, bit_mask ; check if bit is set

JUMP Z, no_add

; if bit is not set, skip addition

ADD result_msb, multiplicand; addition only occurs in MSB

no_add: SRA result_msb

; shift MSB right, CARRY into bit 7,

; lsb into CARRY

; shift LSB right,

SRA result_lsb

lsb from result_msb into bit 7

SLO bit_mask

; shift bit_mask left to examine

next bit in multiplier

JUMP NZ, mult_loop

; if all bit examined, then bit_mask = 0,

```

Figure 3-14: 8-bit by 8-bit Multiply Routine Produces a 16-bit Product

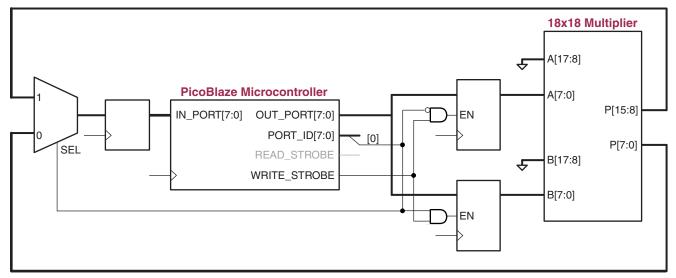

If multiplication performance is important to the application, connect one of the FPGA's 18x18 hardware multipliers the PicoBlaze I/O ports, as shown in Figure 3-15. The hardware multiplier computes the 16-bit result in less than one instruction cycle. Figure 3-16 shows the routine required to multiply two 8-bit values using the hardware multiplier. This same technique can be expanded to multiply two 16-bit values to produce a 32-bit result. This example also illustrates how to use FPGA logic attached to the PicoBlaze microcontroller to accelerate algorithms.

UG129\_c3\_02\_052004

Figure 3-15: 8-bit by 8-bit Hardware Multiplier Using the FPGA's 18x18 Multipliers

```

Multiplier Routine (8-bit x 8-bit = 16-bit product)

; Connects to embedded 18x18 Hardware Multiplier via ports

mult_8x8io:

NAMEREG s0, multiplicand ; preserved

NAMEREG s1, multiplier ; preserved

NAMEREG s3, result_msb

; most-significant byte (MSB) of result, modified

NAMEREG s4, result_1sb

; least-significant byte (LSB) of result, modified

; Define the port ID numbers as constants for better clarity

CONSTANT multiplier_lsb, 00

CONSTANT multiplier_msb, 01

; Output multiplicand and multiplier to FPGA registers connected to the

inputs of

the embedded multiplier.

OUTPUT multiplicand, multiplier_lsb

OUTPUT multiplier, multiplier_msb

; Input the resulting product from the embedded multiplier.

INPUT result_lsb, multiplier_lsb

INPUT result_msb, multiplier_msb

```

Figure 3-16: 8-bit by 8-bit Multiply Routine Using Hardware Multiplier

#### Division

The PicoBlaze microcontroller core does not have a dedicated hardware divider. However, the PicoBlaze microcontroller performs division using the available arithmetic and shift instructions. Figure 3-17 demonstrates a subroutine that divides an unsigned 8-bit number by another unsigned 8-bit number to produce an 8-bit quotient and an 8-bit remainder in 60 to 74 instruction cycles, or 120 to 144 clock cycles.

```

; Divide Routine (8-bit / 8-bit = 8-bit result, remainder)

; Shift and subtract algorithm

div_8by8:

NAMEREG s0, dividend

; preserved

NAMEREG s1, divisor

; preserved

NAMEREG s2, quotient

; preserved

NAMEREG s3, remainder

; modified

NAMEREG s4, bit_mask

; used to test bits in dividend,

; one-hot encoded, modified

LOAD remainder, 00

; clear remainder

; start with most-significant bit (msb)

LOAD bit_mask, 80

div loop:

TEST dividend, bit_mask ; test bit, set CARRY if bit is '1'

SLA remainder ; shift CARRY into 1sb of remainder

SLO quotient

; shift quotient left (multiply by 2)

COMPARE remainder, divisor; is remainder > divisor?

JUMP C, no_sub ; if divisor is greater, continue to next bit

SUB remainder, divisor

; if remainder > divisor, then subtract

ADD quotient, 01

; add one to quotient

no_sub:

SRO bit_mask

; shift to examine next bit position

JUMP NZ, div_loop

; if bit_mask=0, then all bits examined

```

Figure 3-17: 8-bit Divided by 8-bit Routine

# No Operation (NOP)

The PicoBlaze instruction set does not have a specific NOP instruction. Typically, a NOP instruction is completely benign, does not affect register contents or flags, and performs no operation other than requiring an instruction cycle to execute. A NOP instruction is therefore sometimes useful to balance code trees for more predictable execution timing.

There are a few possible implementations of an equivalent NOP operation, as shown in Figure 3-18 and Figure 3-19. Loading a register with itself does not affect the register value or the status flags.

```

nop:

LOAD sX, sX

```

Figure 3-18: Loading a Register with Itself Acts as a NOP Instruction

A similar NOP technique is to simply jump to the next instruction, which is equivalent to the default program flow. The JUMP instruction consumes an instruction cycle (two clock cycles) without affecting register contents.

```

JUMP next

next: <next instruction>

```

Figure 3-19: Alternative NOP Method Using JUMP Instructions

## Setting and Clearing CARRY Flag

Sometimes, application programs need to specifically set or clear the CARRY flag, as shown in the following examples.

#### Clear CARRY Flag

ANDing a register with itself clears the CARRY flag without affecting the register contents, as shown in Figure 3-20.

```

clear_carry_bit:

AND sX, sX ; register sX unaffected, CARRY flag cleared

```

Figure 3-20: ANDing a Register with Itself Clears the CARRY Flag

#### Set CARRY Flag

There are various methods for setting the CARRY flag, one of which appears in Figure 3-21. Generally, these methods affect a register location.

```

set_carry:

LOAD sX, 00

COMPARE sX, 01 ; set CARRY flag and reset ZERO flag

```

Figure 3-21: Example Operation that Sets the CARRY Flag

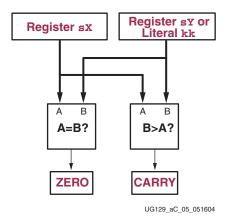

# **Test and Compare**

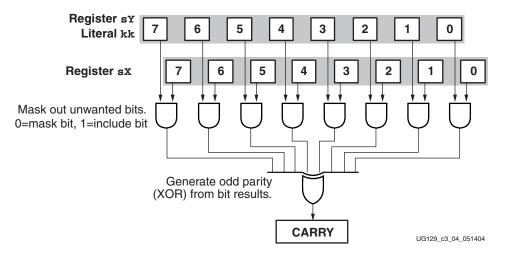

The PicoBlaze microcontroller introduces two new instructions not available on previous PicoBlaze variants. The PicoBlaze microcontroller provides the ability to test individual bits within a register and the ability to compare a register value against another register or an immediate constant. The TEST or COMPARE instructions only affect the ZERO and CARRY flags; neither instruction affects register contents.

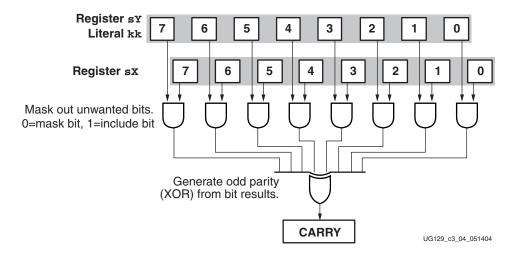

#### Test