# Tone Ordering and Constellation Encoder Specification

Günter Dannoritzer

July 9, 2007

### 1 Introduction

The Tone Ordering and Constellation Encoder core implements the tone ordering and constellation encoding as described in ADSL recommendation ITU G.992.1.

### 2 Architecture

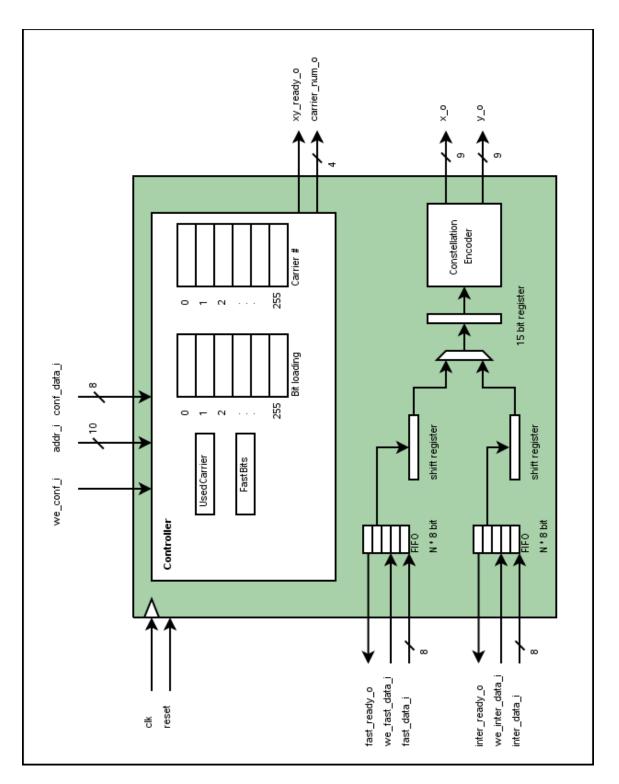

The core consists out of the tone ordering block, the constellation encoder block, and the controller block.

Figure ?? shows the architecture of the Tone Ordering and Constellation Encoder core. Data entering the tone ordering block one byte at a time are stored in FIFOs. There is a FIFO for the fast path and one for the interleaved path. Each carrier can be loaded with 2-15 bits, with the data from the fast path being assigned first to carriers followed by the data from the interleaved path. The processing can only start if enough bytes are in the FIFO to fill the first carrier. The controller block watches over this and if enough bytes are in the FIFO one or two bytes are copied to the shift register. After that the shift register will shift out the amount of bits for the first carrier. Now it depends on the amount of bits needed for the next carrier how many bytes need to get copied out of the FIFO into the shift register. After shifting out the fast path bits, data from the interleaved path are used to fill the resgister for the constellation encoder input.

From the shift register the bits are shifted into a 15 bits wide register. After all bits for a carrier are shifted into that register, the data are loaded into the constellation encoder block.

Figure 1: Architecture

The constellation encoder puts out the result of the constellation encoding, which is the result of the top core.

## 3 Operation

#### 3.1 Reset

Performing a reset will reset all internal state machines and set all registers to 0. After a reset the core needs to be configured for proper operation.

### 3.2 Configuration

The configuration requires the setting of bit loading per carrier. The core has two register sets for this case. The first register set holds the number of bits per carrier and the second register set the carrier number. Tone ordering is done by assigning the first data bits to carriers with the lower number of bits. The core handles this by having a register set configured in the order the bits are to be extracted. After the configuration the core just processes the register list in ascending order. As not all carrier will be used, there is an additional register that specifies how many registers of the list should be processed.

#### 3.3 Data Processing

There are two FIFO buffered data input interfaces. One for data of the fast path and one for data of the interleaved path.

If a data input interface is ready for accepting data, it is signaling that via the ready input. The core takes data in 1 byte groups and stores them in a FIFO. To write data to the data input the write enable signal needs to be asserted and the valid data are entered into the FIFO with the next raising edge of the clk signal.

Once enough data are entered to encode the first carrier, as specified in the register array, data are extracted and passed to the constellation encoder. The output of the encoder is passed along with the carrier number as output of the core.

## 4 Registers

| Name          | Address       | Width | Access | Description                  |  |

|---------------|---------------|-------|--------|------------------------------|--|

| BitLoading    | 0x000 - 0x0FF | 4     | W      | Specifies how many bits a    |  |

|               |               |       |        | carrier is loaded with       |  |

| CarrierNumber | 0x100 - 0x1FF | 8     | W      | Specifies the carrier number |  |

| UsedCarrier   | 0x200         | 8     | W      | How many of the BitLoading   |  |

|               |               |       |        | and CarrierNumber registers  |  |

|               |               |       |        | are filled with information  |  |

| FastBits      | 0x201         | 8     | W      | How many bits are used for   |  |

|               |               |       |        | the fast path                |  |

Table **??** lists the registers which are accessible over the address and configuration data bus.

Table 1: List of registers

### 4.1 BitLoading

The BitLoading register is of size 256\*4 bits and only writeable. It lists the amount of bits to be loaded on a carrier. The core will process the list in ascending order, so the registers need to be configured in the way the tone ordering should be performed. That means carriers with the least amount of non-zero bits have to be written first into the registers. The stored information is only meaningful in connection with the CarrierNumber registers.

#### 4.2 CarrierNumber

The information of the CarrierNumber registers are tight to the BitLoading registers by the register number. For example, BitLoading register 0 at address 0x000 specifies the amount of bits loaded onto the carrier, specified in CarrierNumber register 0 at address 0x100.

#### 4.3 UsedCarriers

Although ADSL supports 256 carriers, not all of them will be loaded with bits. As the BitLoading and the CarrierNumber registers are storing the information in ordered form, only the first n of 256 registers will be filled with information and need to be

processed by the tone ordering and constellation encoder. The UsedCarriers register specified how many of those registers need to be processed.

#### 4.4 FastBits

The FastBits register specifies how many bits from the fast path are shifted into the constellation encoder. After this amount of bits are shifted out, the multiplexer is switched and data are shifted from the interleaved path.

# 5 Interface Description

| Port            | Width | Direction | Description                                 |

|-----------------|-------|-----------|---------------------------------------------|

| clk             | 1     | Input     | Clock input                                 |

| reset           | 1     | Input     | Reset the block                             |

| fast_ready_o    | 1     | Output    | Fast path FIFO is ready to receive data     |

| we_fast_data_i  | 1     | Input     | Write enable for fast path data             |

| fast_data_i     | 8     | Input     | Fast path data                              |

| inter_ready_o   | 1     | Output    | Interleaved path FIFO is ready to receive   |

|                 |       |           | data                                        |

| we_inter_data_i | 1     | Input     | Write enable for interleaved path data      |

| inter_data_i    | 8     | Input     | Interleaved path data                       |

| addr_i          | 10    | Input     | Address for configuration registers         |

| we_conf_i       | 1     | Input     | Write enable for configuration data         |

| conf_data_i     | 8     | Input     | Configuration data                          |

| xy_ready_o      | 1     | Output    | Signal that the X and Y output values are   |

|                 |       |           | valid                                       |

| carrier_num_o   | 4     | Output    | Specify the carrier number for which the X  |

|                 |       |           | and Y output values are                     |

| X_0             | 9     | Input     | X output value of the constellation encoder |

| у_0             | 9     | Input     | Y output value of the constellation encoder |

Table ?? shows the I/O port configuration of the Core.

Table 2: List of I/O Ports for the Tone Ordering and Constellation Encoder Core

### 6 Synthesis Results

Table ?? lists some synthesis results.

| Vendor | Family | Device | Resource<br>usage | Max. Clock<br>speed | ζ |

|--------|--------|--------|-------------------|---------------------|---|

| Xilinx |        |        |                   |                     |   |

Table 3: Synthesis results for Core