1

# **File description**

# 1.1 "fifo\_control.v"

Module FIFO\_CONTROL includes control logic for single FIFO. It consists of read and write address generation and full, almost full, empty and almost empty status generation. It also generates read and write allow signals, which are used for enabling/disabling memory used for FIFO. Control logic can be used for independent read and write clocks.

## 1.2 "wbw\_wbr\_fifos.v"

WBW\_WBR\_FIFOS module is actual interface for WISHBONE write and read FIFOs. It instantiates necessary control logic (FIFO\_CONTROL) and RAM modules, which can be synchronous or asynchronous, depending on parameter definition. It provides control, data and status interface signals for both WISHBONE write and WISHBONE read FIFOs.

# 1.3 "pciw\_pcir\_fifos.v"

PCIW\_PCIR\_FIFOS module is actual interface for PCI write and read FIFOs. It instantiates necessary control logic (FIFO\_CONTROL) and RAM modules, which can be synchronous or asynchronous, depending on parameter definition. It provides control, data and status interface signals for both PCI write and PCI read FIFOs. It's almost identical to WBW\_WBR\_FIFOs – it's done separately because of more readable connection to other modules.

#### 1.4 "dp\_async\_ram.v"

Module DP\_ASYNC\_RAM is just a behavioral asynchronous dual port RAM for simulation purposes.

#### 1.5 "dp\_sram.v"

Module DP\_SRAM is behavioral synchronous dual port RAM for simulation purposes.

## 1.6 "wb\_tb.v"

Module WB\_TB is a little test bench (more demonstration than test bench) for WBW\_WBR\_FIFOS module.

# 1.7 "pci\_tb.v"

Module PCI\_TB is a little test bench (more demonstration than test bench) for PCIW\_PCIR\_FIFOS module.

# 2

# Operation

# 2.1 Parameters

FIFO parameters are defined in global "constants.v" file in their own section. Available parameters, their description and FIFO behavior impact:

| Parameter        | Description                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------|

| WBW_DEPTH        | Number of locations in WBW FIFO. Note that one location is always unused. Minimum number is 8.  |

| WBW_ADDR_LENGTH  | Address length for WBW_FIFO RAM. It must be log2(WBW_DEPTH).                                    |

| WBR_DEPTH        | Number of locations in WBR FIFO. Note that one location is always unused. Minimum number is 8.  |

| WBR_ADDR_LENGTH  | Address length for WBR_FIFO RAM. It must be log2(WBR_DEPTH).                                    |

| PCIW_DEPTH       | Number of locations in PCIW FIFO. Note that one location is always unused. Minimum number is 8. |

| PCIW_ADDR_LENGTH | Address length for PCIW_FIFO RAM. It must be log2(PCIW_DEPTH).                                  |

| PCIR_DEPTH       | Number of locations in PCIR_FIFO. Note that one location is always unused. Minimum number is 8. |

| PCIR_ADDR_LENGTH | Address length for PCIR_FIFO RAM. It must be log2(PCIR_DEPTH).                                  |

| FPGA<br>BIG | If FPGA is defined, RAMB4_S16_S16 modules are instantiated for FIFOs storage space. If BIG is commented                                                                                                                                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | out, than 3 Block Select RAM+ modules are shared between<br>two FIFOs (max depth is 128). FPGA must provide at least 6<br>of them. This slows down FIFO operation a bit, since it<br>requires a turnaround cycle between writes and reads. If BIG<br>is defined, 3 Block Select RAMs are used for each FIFO.<br>That means a FPGA with at least 12 of them. (max depth<br>256) |

| SYNCHRONOUS | Only has meaning when FPGA is not defined ( commented<br>out ). It invokes elaboration of FIFO control logic that<br>supports synchronous RAM storage for FIFOs. If FPGA and<br>SYNCHRONOUS are undefined, asynchronous RAM<br>storage and control logic is assumed.                                                                                                           |

# 2.2 Module descriptions

## 2.2.1 WBW\_WBR\_FIFO

Module incorporates both WISHBONE slave unit's FIFOs: WISHBONE read and WISHBONE write FIFO. They are joined in a single module because of same storage space sharing in certain implementations.

Module connections:

• Common signals

| Signal name  | Size | Direction | Description                                                                     |

|--------------|------|-----------|---------------------------------------------------------------------------------|

| wb_clock_in  | 1    | Ι         | WISHBONE bus clock input. It's WBR_FIFO's read clock and WBW_FIFO's write clock |

| pci_clock_in | 1    | Ι         | PCI bus clock input. It's WBR_FIFO's write clock and WBW_FIFO's read clock      |

| reset_in     | 1    | Ι         | System reset input                                                              |

## • WBW\_FIFO signals

| Signal name       | Size | Direction | Description                                                                                                                                                                                                                                                                          |

|-------------------|------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| wbw_wenable_in    | 1    | Ι         | WBW_FIFO's write enable input. When FIFO<br>is not full and write enable is high, data<br>provided on data inputs will be written to FIFO<br>on rising WISHBONE clock edge.                                                                                                          |

| wbw_addr_data_in  | 32   | Ι         | WBW_FIFO's address / data input. Address<br>entry is always first entry of transaction with<br>one or more data entries following.                                                                                                                                                   |

| wbw_cbe_in        | 4    | Ι         | WBW_FIFO's bus command / byte enable<br>input. First entry of transaction written with<br>address is PCI bus command, byte enables are<br>written with data entries ( they are negated<br>SEL_I signals from WISHBONE since PCI BE<br>signals are active low )                       |

| wbw_control_in    | 4    | Ι         | WBW_FIFO's control bus input – encoded<br>control values are written to FIFO to<br>communicate to PCI side. Common controls<br>are defining address entry, intermediate and<br>last data entry of transaction, so opposite side<br>knows when to terminate the cycle.                |

| wbw_renable_in    | 1    | Ι         | WBW_FIFO's read enable input. When FIFO<br>is not empty and read enable is high, data<br>provided on data outputs will change to next<br>written location on rising PCI clock edge.<br>Reading side must only assert read enable<br>when it intends to read currently provided data. |

| wbw_addr_data_out | 32   | 0         | WBW_FIFO's address / data output. Address<br>entry is always first entry of transaction with<br>one or more data entries following.                                                                                                                                                  |

| wbw_cbe_out       | 4    | 0         | WBW_FIFO's bus command / byte enable<br>output. First entry of transaction read<br>concurrently with address is PCI bus<br>command, byte enables are read concurrently<br>with data entries (they are negated SEL_I<br>signals from WISHBONE since PCI BE<br>signals are active low) |

| wbw_control_out           | 4 | 0 | WBW_FIFO's reading side monitors current control bus output for various encoded values, so it knows when to start or end current cycle in progress.                                                                                                                                                                                                                                                                            |

|---------------------------|---|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| wbw_flush_in              | 1 | Ι | WBW_FIFO's flush input. It doesn't actually<br>delete or initialize storage space – it just resets<br>address counters so FIFO is marked empty.<br>Any data in the FIFO is therefore invalid.<br>Flush signal should remain asserted for at least<br>one PCI or WB clock cycle.                                                                                                                                                |

| wbw_almost_full_out       | 1 | 0 | WBW_FIFO's almost full status output.<br>Indicates that only one location in the FIFO is<br>empty. When WB side writes to the FIFO and<br>samples this signal asserted on rising WB<br>clock edge, it should stop writing immediately,<br>since last location was just written.                                                                                                                                                |

| wbw_full_out              | 1 | 0 | WBW_FIFO's full status output – indicates that no free locations are currently available in the FIFO.                                                                                                                                                                                                                                                                                                                          |

| wbw_almost_empty_out      | 1 | 0 | WBW_FIFO's almost empty status output.<br>Indicates that only one location in the FIFO is<br>still valid. When PCI side reads from the FIFO<br>and samples this signal asserted on rising PCI<br>clock edge, it should stop reading immediately,<br>since last location was just read and FIFO is<br>empty.                                                                                                                    |

| wbw_empty_out             | 1 | 0 | WBW_FIFO's empty status output – indicates<br>that no locations containing valid data are<br>currently available in the FIFO.                                                                                                                                                                                                                                                                                                  |

| wbw_transaction_ready_out | 1 | 0 | Indicates that at least one unfinished<br>transaction is present in the WBW_FIFO.<br>Transaction ready generation is done by<br>monitoring control bus input and output. When<br>control bus input indicates last data phase, that<br>means one complete transaction was<br>transferred to the FIFO. When control bus<br>output indicates last data phase it means that<br>one complete transaction was pulled out of<br>FIFO. |

#### • WBR\_FIFO signals

| Signal name     | Size | Direction | Description                                                                                                                                                                                                                                                                         |

|-----------------|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| wbr_wenable_in  | 1    | Ι         | WBR_FIFO's write enable input. When FIFO<br>is not full and write enable is high, data<br>provided on data inputs will be written to FIFO<br>on rising PCI clock edge.                                                                                                              |

| wbr_data_in     | 32   | Ι         | WBR_FIFO's data input.                                                                                                                                                                                                                                                              |

| wbr_be_in       | 4    | Ι         | WBR_FIFO's byte enable input. Byte enables<br>are written with data entries (they are negated<br>BE# signals from PCI bus since WB SEL_I<br>signals are active high)                                                                                                                |

| wbr_control_in  | 4    | Ι         | WBR_FIFO's control bus input – encoded<br>control values are written to FIFO to<br>communicate to WB side. Common controls<br>are defining intermediate and last data entry of<br>transaction, so opposite side knows when to<br>terminate the cycle.                               |

| wbr_renable_in  | 1    | Ι         | WBR_FIFO's read enable input. When FIFO is<br>not empty and read enable is high, data<br>provided on data outputs will change to next<br>written location on rising WB clock edge.<br>Reading side must only assert read enable<br>when it intends to read currently provided data. |

| wbr_data_out    | 32   | 0         | WBR_FIFO's data output.                                                                                                                                                                                                                                                             |

| wbr_be_out      | 4    | 0         | WBR_FIFO's byte enable output. Byte enables<br>are read concurrently with data entries (they<br>are negated BE# signals from PCI since WB<br>SEL_I signals are active high)                                                                                                         |

| wbr_control_out | 4    | 0         | WBR_FIFO's reading side monitors current<br>control bus output for various encoded values,<br>so it knows when to start or end current cycle<br>in progress.                                                                                                                        |

| wbr_flush_in    | 1    | Ι         | WBR_FIFO's flush input. It doesn't actually<br>delete or initialize storage space – it just resets<br>address counters so FIFO is marked empty.<br>Any data in the FIFO is therefore invalid.<br>Flush signal should remain asserted for at least<br>one PCI or WB clock cycle.     |

| wbr_almost_full_out       | 1 | 0 | WBR_FIFO's almost full status output.<br>Indicates that only one location in the FIFO is<br>empty. When PCI side writes to the FIFO and<br>samples this signal asserted on rising PCI clock<br>edge, it should stop writing immediately, since<br>last location was just written.                                                                                                                                              |

|---------------------------|---|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| wbr_full_out              | 1 | 0 | WBR_FIFO's full status output – indicates that<br>no free locations are currently available in the<br>FIFO.                                                                                                                                                                                                                                                                                                                    |

| wbr_almost_empty_out      | 1 | 0 | WBR_FIFO's almost empty status output.<br>Indicates that only one location in the FIFO is<br>still valid. When WB side reads from the FIFO<br>and samples this signal asserted on rising WB<br>clock edge, it should stop reading immediately,<br>since last location was just read and FIFO is<br>empty.                                                                                                                      |

| wbr_empty_out             | 1 | 0 | WBR_FIFO's empty status output – indicates<br>that no locations containing valid data are<br>currently available in the FIFO.                                                                                                                                                                                                                                                                                                  |

| wbr_transaction_ready_out | 1 | 0 | Indicates that at least one unfinished<br>transaction is present in the WBR_FIFO.<br>Transaction ready generation is done by<br>monitoring control bus input and output. When<br>control bus input indicates last data phase, that<br>means one complete transaction was<br>transferred to the FIFO. When control bus<br>output indicates last data phase it means that<br>one complete transaction was pulled out of<br>FIFO. |

## 2.2.2 PCIW\_PCIR\_FIFO

Module incorporates both PCI target unit's FIFOs: PCI read and PCI write FIFO. They are joined in a single module because of same storage space sharing in certain implementations.

Module connections:

• Common signals

| Signal name  | Size | Direction | Description                                                                       |

|--------------|------|-----------|-----------------------------------------------------------------------------------|

| wb_clock_in  | 1    | Ι         | WISHBONE bus clock input. It's PCIR_FIFO's write clock and PCIW_FIFO's read clock |

| pci_clock_in | 1    | Ι         | PCI bus clock input. It's PCIR_FIFO's read clock and PCIW_FIFO's write clock      |

| reset_in     | 1    | Ι         | System reset input                                                                |

## • PCIW\_FIFO signals

| Signal name       | Size | Direction | Description                                                                                                                                                                                                                                                           |

|-------------------|------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pciw_wenable_in   | 1    | Ι         | PCIW_FIFO's write enable input. When FIFO<br>is not full and write enable is high, data<br>provided on data inputs will be written to FIFO<br>on rising PCI clock edge.                                                                                               |

| pciw_addr_data_in | 32   | Ι         | PCIW_FIFO's address / data input. Address<br>entry is always first entry of transaction with<br>one or more data entries following.                                                                                                                                   |

| pciw_cbe_in       | 4    | Ι         | PCIW_FIFO's bus command / byte enable<br>input. First entry of transaction written with<br>address is PCI bus command, byte enables are<br>written with data entries (they are negated BE#<br>signals from PCI since WISHBONE SEL_O<br>signals are active high)       |

| pciw_control_in   | 4    | Ι         | PCIW_FIFO's control bus input – encoded<br>control values are written to FIFO to<br>communicate to WB side. Common controls<br>are defining address entry, intermediate and<br>last data entry of transaction, so opposite side<br>knows when to terminate the cycle. |

| pciw_renable_in       | 1  | Ι | PCIW_FIFO's read enable input. When FIFO<br>is not empty and read enable is high, data<br>provided on data outputs will change to next<br>written location on rising WB clock edge.<br>Reading side must only assert read enable<br>when it intends to read currently provided data.                       |

|-----------------------|----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pciw_addr_data_out    | 32 | 0 | PCIW_FIFO's address / data output. Address<br>entry is always first entry of transaction with<br>one or more data entries following.                                                                                                                                                                       |

| pciw_cbe_out          | 4  | 0 | PCIW_FIFO's bus command / byte enable<br>output. First entry of transaction read<br>concurrently with address is PCI bus<br>command, byte enables are read concurrently<br>with data entries (they are negated BE# signals<br>from PCI since WB SEL_O signals are active<br>high)                          |

| pciw_control_out      | 4  | 0 | PCIW_FIFO's reading side monitors current<br>control bus output for various encoded values,<br>so it knows when to start or end current cycle<br>in progress.                                                                                                                                              |

| pciw_flush_in         | 1  | Ι | PCIW_FIFO's flush input. It doesn't actually delete or initialize storage space – it just resets address counters so FIFO is marked empty. Any data in the FIFO is therefore invalid. Flush signal should remain asserted for at least one PCI or WB clock cycle.                                          |

| pciw_almost_full_out  | 1  | 0 | PCIW_FIFO's almost full status output.<br>Indicates that only one location in the FIFO is<br>empty. When PCI side writes to the FIFO and<br>samples this signal asserted on rising PCI clock<br>edge, it should stop writing immediately, since<br>last location was just written.                         |

| pciw_full_out         | 1  | 0 | PCIW_FIFO's full status output – indicates that no free locations are currently available in the FIFO.                                                                                                                                                                                                     |

| pciw_almost_empty_out | 1  | 0 | PCIW_FIFO's almost empty status output.<br>Indicates that only one location in the FIFO is<br>still valid. When WB side reads from the FIFO<br>and samples this signal asserted on rising WB<br>clock edge, it should stop reading immediately,<br>since last location was just read and FIFO is<br>empty. |

| pciw_empty_out             | 1 | 0 | PCIW_FIFO's empty status output – indicates<br>that no locations containing valid data are<br>currently available in the FIFO.                                                                                                                                                                                                                                                                                                  |

|----------------------------|---|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pciw_transaction_ready_out | 1 | 0 | Indicates that at least one unfinished<br>transaction is present in the PCIW_FIFO.<br>Transaction ready generation is done by<br>monitoring control bus input and output. When<br>control bus input indicates last data phase, that<br>means one complete transaction was<br>transferred to the FIFO. When control bus<br>output indicates last data phase it means that<br>one complete transaction was pulled out of<br>FIFO. |

#### • PCIR\_FIFO signals

| Signal name     | Size | Direction | Description                                                                                                                                                                                                                                             |

|-----------------|------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pcir_wenable_in | 1    | Ι         | PCIR_FIFO's write enable input. When FIFO<br>is not full and write enable is high, data<br>provided on data inputs will be written to FIFO<br>on rising WB clock edge.                                                                                  |

| pcir_data_in    | 32   | Ι         | PCIR_FIFO's data input.                                                                                                                                                                                                                                 |

| pcir_be_in      | 4    | Ι         | PCIR_FIFO's byte enable input. Byte enables<br>are written with data entries (they are negated<br>SEL_O signals from WB bus since PCI BE#<br>signals are active high)                                                                                   |

| pcir_control_in | 4    | Ι         | PCIR_FIFO's control bus input – encoded<br>control values are written to FIFO to<br>communicate to PCI side. Common controls<br>are defining intermediate and last data entry of<br>transaction, so opposite side knows when to<br>terminate the cycle. |

|                       |    |   | PCIR_FIFO's read enable input. When FIFO is                                                                                                                                                                                                                                                                  |

|-----------------------|----|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pcir_renable_in       | 1  | Ι | not empty and read enable is high, data<br>provided on data outputs will change to next<br>written location on rising PCI clock edge.<br>Reading side must only assert read enable<br>when it intends to read currently provided data.                                                                       |

| pcir_data_out         | 32 | 0 | PCIR_FIFO's data output.                                                                                                                                                                                                                                                                                     |

| pcir_be_out           | 4  | 0 | PCIR_FIFO's byte enable output. Byte enables<br>are read concurrently with data entries (they<br>are negated SEL_O signals from WB since PCI<br>BE# signals are active low)                                                                                                                                  |

| pcir_control_out      | 4  | 0 | PCIR_FIFO's reading side monitors current control bus output for various encoded values, so it knows when to start or end current cycle in progress.                                                                                                                                                         |

| pcir_flush_in         | 1  | Ι | PCIR_FIFO's flush input. It doesn't actually delete or initialize storage space – it just resets address counters so FIFO is marked empty. Any data in the FIFO is therefore invalid. Flush signal should remain asserted for at least one PCI or WB clock cycle.                                            |

| pcir_almost_full_out  | 1  | 0 | PCIR_FIFO's almost full status output.<br>Indicates that only one location in the FIFO is<br>empty. When WB side writes to the FIFO and<br>samples this signal asserted on rising WB<br>clock edge, it should stop writing immediately,<br>since last location was just written.                             |

| pcir_full_out         | 1  | 0 | PCIR_FIFO's full status output – indicates that<br>no free locations are currently available in the<br>FIFO.                                                                                                                                                                                                 |

| pcir_almost_empty_out | 1  | 0 | PCIR_FIFO's almost empty status output.<br>Indicates that only one location in the FIFO is<br>still valid. When PCI side reads from the FIFO<br>and samples this signal asserted on rising PCI<br>clock edge, it should stop reading immediately,<br>since last location was just read and FIFO is<br>empty. |

| pcir_empty_out        | 1  | 0 | PCIR_FIFO's empty status output – indicates that no locations containing valid data are currently available in the FIFO.                                                                                                                                                                                     |

| pcir_transaction_ready_out 1 | 0 | Indicates that at least one unfinished<br>transaction is present in the PCIR_FIFO.<br>Transaction ready generation is done by<br>monitoring control bus input and output. When<br>control bus input indicates last data phase, that<br>means one complete transaction was<br>transferred to the FIFO. When control bus<br>output indicates last data phase it means that<br>one complete transaction was pulled out of<br>FIFO. |

|------------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|------------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

#### 2.3 Waveforms

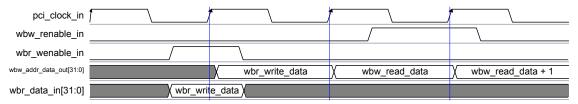

#### 2.3.1 FPGA w/o BIG

As stated in parameters section, in small FPGAs Block Ram sharing is performed, which requires turnaround cycle between writes and reads. Turnaround is not necessary between reads and writes. For example – when PCI master interface writes data to WBR\_FIFO on PCI side, it must wait for at least one clock cycle before it can perform a read from WBW\_FIFO. Since PCI bus protocol also defines turnaround cycles and bus idle states between transactions, this shouldn't have any impact at all to overall bridge performance. In any case, FPGA implementation uses synchronous storage space, so control logic for synchronous RAMs is implemented.

First clock edge: Data from a read transaction is written to WBR\_FIFO. Data is written on the rising edge of PCI clock when wbr\_wenable\_in is high. Data is also mirrored to wbw\_addr\_data\_out output of WBW\_FIFO. Second rising edge is turnaround cycle, when mirrored write data is replaced by actual data coming out of WBW\_FIFO. On the third clock edge this data is read from FIFO and next data is provided immediately after rising PCI clock edge when wbw\_renable\_in is high.

#### 2.3.2 FPGA with BIG defined

This implementation doesn't share Blocks of RAM between FIFOs, so turnaround is not necessary. Everything else is the same as in small FPGAs (w/o BIG). Implementation of control logic is for synchronous storage space.

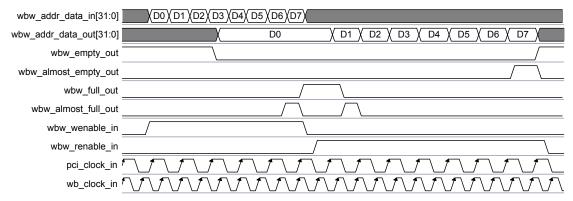

#### 2.3.3 SYNCHRONOUS

If some other storage space is provided and is synchronous, than this storage should be instantiated and properly connected to control logic in files wbw\_wbr\_fifos.v and pciw\_pcir\_fifos.v. Parameter SYNCHRONOUS should be defined, otherwise FIFOs may not work correctly. If storage is not synchronous, than this parameter should be commented out for reduction of additional logic and higher speeds.

Diagram shows basic SYNCHRONOUS storage WBW\_FIFO operation. WBW\_FIFO has WISHBONE clock for write port and PCI clock for read port. There is one special case to note in the diagram – empty/not empty status transition. Empty status generation is registered and synchronized to read (PCI) clock. Empty status is stretched for one PCI clock cycle to assure that valid data is present on the output bus. Data can change only on rising clock edges of PCI clock. There is a reason for stretching empty status: When FIFO is empty, read and write addresses are equal. On the first PCI clock edge that control logic senses difference in read/write address, there is no assurance that there has been enough time for data to be properly written to the FIFO's location pointed by read pointer. That's why empty status is stretched and on the next read clock edge data is 100% valid. Operation is analogous for other FIFOs also.

Almost empty status generation is synchronous to read clock. When it's asserted it will remain asserted for at least one read clock cycle.

Almost full and full statuses generation is synchronous to write clock. Both statuses remain asserted for at least one clock cycle.

There is not much difference in timing between synchronous and asynchronous storage, except for stretched empty status, additional logic and registers needed in synchronous implementation for providing data on outputs from FIFO on any rising clock edge w/o wait cycles.