# PCI IP Core Specification

Authors: Miha Dolenc & Tadej Markovic

mihad@opencores.org

tadej@opencores.org

Rev. 0.6 January 28, 2002

# **Revision History**

| Rev. | Date     | Author               | Description                                           |

|------|----------|----------------------|-------------------------------------------------------|

| 0.0  | 5/1/01   | Miha Dolenc          | First Draft                                           |

|      |          | Tadej Markovic       |                                                       |

| 0.1  | 5/8/01   | Miha Dolenc          | Waveforms added for WISHBONE slave                    |

|      |          | Tadej Markovic       |                                                       |

| 0.2  | 5/15/01  | Miha Dolenc          | Detailed description of FIFO added, Operation of      |

|      |          | Tadej Markovic       | PCI target unit added, Waveforms added for PCI target |

| 0.3  | 5/22/01  | Miha Dolenc          | FIFO structure changed                                |

|      |          | Tadej Markovic       |                                                       |

| 0.4  | 10/13/01 | Jeanne<br>Wiegelmann | First review                                          |

| 0.5  | 10/20/01 | Miha Dolenc          | Updated register descriptions and Configuration       |

|      |          | Tadej Markovic       | Space access                                          |

| 0.6  | 01/28/02 | Miha Dolenc          | Updated descriptions and added Software obligations   |

|      |          | Tadej Markovic       |                                                       |

|      |          |                      |                                                       |

# **List of Contents**

| INTRODUCTION                                           | 1        |

|--------------------------------------------------------|----------|

| 1.1 What is a PCI Bridge?                              |          |

| 1.2 PCI IP CORE INTRODUCTION                           |          |

| 1.3 PCI IP CORE FEATURES                               |          |

| ARCHITECTURE                                           | 3        |

| 2.1 Overview                                           | 3        |

| 2.2 WISHBONE SLAVE UNIT                                |          |

| 2.2.1 WISHBONE Slave Unit Architecture                 |          |

| 2.3 PCI TARGET UNIT                                    |          |

| 2.3.1 PCI Target Unit Architecture                     | 6        |

| 2.4 Clocks                                             | 8        |

| 2.5 FIFO                                               |          |

| 2.6 ADDRESS TRANSLATION LOGIC                          |          |

| 2.6.1 Description of Address Translation Logic         |          |

| OPERATION                                              | 12       |

| 3.1 CONFIGURATION SPACE                                | 12       |

| 3.1.1 Configuration Space Access for Host Bus Bridges  |          |

| 3.1.2 Configuration Space Access for Guest Bridges     |          |

| 3.1.3 Configuration Cycles                             |          |

| 3.1.4 Generating Configuration Cycles                  |          |

| 3.1.5 Generating Interrupt Acknowledge Cycles          |          |

| 3.2 WISHBONE SLAVE UNIT                                | 18       |

| 3.2.1 WISHBONE Slave Unit Functionality                |          |

| 3.2.2 Addressing and Images of the WISHBONE Slave Unit |          |

| 3.2.3 WISHBONE to PCI Write Cycles                     | 21       |

| 3.2.4 WISHBONE to PCI Read Cycles                      |          |

| 3.3 PCI TARGET UNIT                                    |          |

| 3.3.1 PCI Target Unit Functionality                    |          |

| 3.3.2 Addressing and Images of the PCI Target Unit     | 20       |

| 3.3.3 PCI to WISHBONE Write Cycles                     |          |

| 3.4 Transaction Ordering                               |          |

| 3.5 Parity                                             |          |

| 3.6 Interrupts                                         |          |

| REGISTERS                                              | 35       |

| 4.1 Register List and Description                      |          |

| 4.1.1 WISHBONE Slave Unit Control & Status             |          |

| 4.1.2 PCI Target Unit Control & Status                 |          |

| 4.1.3 Reporting Registers                              | 42<br>51 |

| 4.1.4 Interrupt Control & Status Registers.            |          |

| 4.2 Software obligations                               |          |

| IO PORTS                                               | 61       |

| 5.1 PCI Interface                                   | 61 |

|-----------------------------------------------------|----|

| 5.1.1 Required PCI Interface Pins                   | 61 |

| 5.1.1 Required PCI Interface Pins                   | 62 |

| 5.2 WISHBONE INTERFACE                              | 63 |

| WAVEFORMS                                           | 65 |

| 6.1 Wishbone Slave Unit                             | 65 |

| 6.1.1 WISHBONE Configuration Accesses               | 65 |

| 6.1.2 WISHBONE to PČI Accesses                      | 67 |

| 6.1.3 PCI Cycles                                    | 67 |

| 6.1.3 PCI Cycles                                    | 70 |

| 6.2 PCL TARGETUNIT                                  | /4 |

| 6.1.2 PCI Configuration Accesses                    |    |

| 6.2.2 PCI to WISHBONE Accesses With WISHBONE Cycles |    |

| 6.2.3 WISHBONE Terminations                         | 77 |

| CORE HW CONFIGURATION                               | 78 |

| A.1 HW Configuration Parameters                     | 78 |

| INDEX                                               | 99 |

# List of Tables

| TABLE 3-1: VALUE ON AD[31:11] PCI BUS LINES DURING ADDRESS PHASE OF CONFIGURATION CYCLE TYPE 017 |

|--------------------------------------------------------------------------------------------------|

| TABLE 3-2: VALID ADDR_O(1:0) AND SEL_O(3:0) COMBINATIONS FOR I/O MAPPED ADDRESS SPACE ACCESS     |

| TABLE 3-3: BUS COMMAND ENCODING FOR READ CYCLES THROUGH PCI MASTER MODULE24                      |

| TABLE 3-4: VALID AD(1:0) AND BE# (3:0) COMBINATIONS FOR I/O MAPPED ADDRESS SPACE ACCESSES        |

| TABLE 3-5: BURST ORDERING COMBINATIONS FOR MEMORY MAPPED ADDRESS SPACE ACCESSES                  |

| TABLE 3-6: BUS COMMAND ENCODING FOR READ CYCLES THROUGH PCI TARGET MODULE                        |

| TABLE 4-1: LIST OF REGISTERS                                                                     |

| TABLE 4-2: WISHBONE CONFIGURATION SPACE BASE ADDRESS REGISTER 38                                 |

| TABLE 4-3: WISHBONE IMAGE CONTROL REGISTER                                                       |

| TABLE 4-4: WISHBONE IMAGE CONTROL REGISTER BIT DESCRIPTIONS 40                                   |

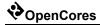

| TABLE 4-5: WISHBONE BASE ADDRESS REGISTER40                                                      |

| TABLE 4-6: WISHBONE BASE ADDRESS REGISTER BIT DESCRIPTIONS40                                     |

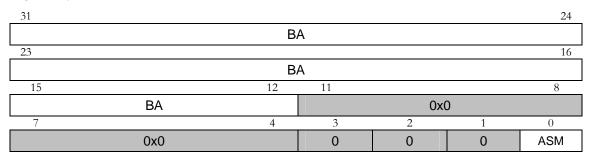

| TABLE 4-7: WISHBONE ADDRESS MASK REGISTER 41                                                     |

| TABLE 4-8: WISHBONE ADDRESS MASK REGISTER BIT DESCRIPTIONS 41                                    |

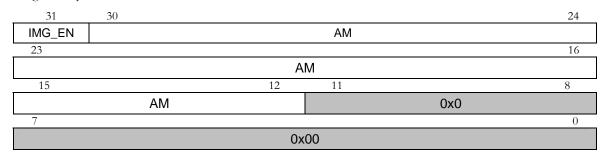

| TABLE 4-9: WISHBONE TRANSLATION ADDRESS REGISTER42                                               |

| TABLE 4-10: WISHBONE TRANSLATION ADDRESS REGISTER BIT DESCRIPTIONS 42                            |

| TABLE 4-11: COMMAND REGISTER OF PCI CONFIGURATION HEADER45                                       |

| TADI E 4 19. CTATUS DECISTED OF DOLCONFICUDATION LIFADED                                         |

| TABLE 4-13: BASE ADDRESS REGISTER OF PCI CONFIGURATION HEADER MEMORY MAPPED SPACE |    |

|-----------------------------------------------------------------------------------|----|

| TABLE 4-14: BASE ADDRESS REGISTER OF PCI CONFIGURATION HEADER FO                  |    |

| TABLE 4-15: PCI IMAGEO BASE ADDRESS REGISTER                                      | 47 |

| TABLE 4-16: PCI IMAGE CONTROL REGISTER                                            | 48 |

| TABLE 4-17: PCI IMAGE CONTROL REGISTER BIT DESCRIPTIONS                           | 48 |

| TABLE 4-18: PCI BASE ADDRESS REGISTER                                             | 49 |

| TABLE 4-19: PCI BASE ADDRESS REGISTER BIT DESCRIPTIONS                            | 49 |

| TABLE 4-20: PCI ADDRESS MASK REGISTER                                             | 50 |

| TABLE 4-21: PCI ADDRESS MASK REGISTER BIT DESCRIPTIONS                            | 50 |

| TABLE 4-22: PCI TRANSLATION ADDRESS REGISTER                                      | 51 |

| TABLE 4-23: PCI TRANSLATION ADDRESS REGISTER BIT DESCRIPTIONS                     | 51 |

| TABLE 4-24: WISHBONE ERROR CONTROL AND STATUS REGISTER                            | 52 |

| TABLE 4-25: WISHBONE ERROR CONTROL AND STATUS REGISTER BIT DESCRIB                |    |

| TABLE 4-26: WISHBONE ERRONEOUS ADDRESS REGISTER                                   | 53 |

| TABLE 4-27: WISHBONE ERRONEOUS DATA REGISTER                                      | 53 |

| TABLE 4-28: PCI ERROR CONTROL AND STATUS REGISTER                                 | 53 |

| TABLE 4-29: PCI ERROR CONTROL AND STATUS REGISTER BIT DESCRIPTIONS                | 55 |

| TABLE 4-30: PCI ERRONEOUS ADDRESS REGISTER                                        | 55 |

| TABLE 4-31: PCI ERRONEOUS DATA REGISTER                                           | 55 |

| TABLE 4-32: CONFIGURATION ADDRESS REGISTER                                        | 55 |

| TABLE 4-33: CONFIGURATION ADDRESS REGISTER BIT DESCRIPTIONS                       | 56 |

| TABLE 4-34: CONFIGURATION DATA REGISTER                                           | 57 |

| TARI E 4.35. INTERRIPT ACKNOWI FIGE RECISTER                                      | 57 |

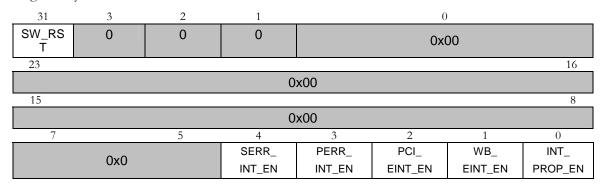

| TABLE 4-36: INTERRUPT CONTROL REGISTER                      | 57 |

|-------------------------------------------------------------|----|

| TABLE 4-37: INTERRUPT CONTROL REGISTER BIT DESCRIPTIONS     | 58 |

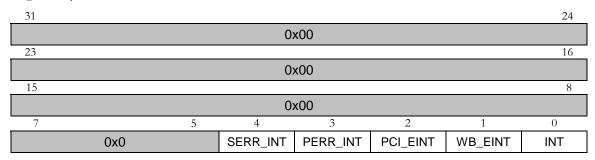

| TABLE 4-38: INTERRUPT STATUS REGISTER                       | 59 |

| TABLE 4-39: INTERRUPT STATUS REGISTER BIT DESCRIPTIONS      | 60 |

| TABLE 5-1: PCI ADDRESS AND DATA PINS                        | 61 |

| TABLE 5-2: PCI INTERFACE CONTROL PINS                       | 62 |

| TABLE 5-3: PCI ERROR REPORTING PINS                         | 62 |

| TABLE 5-4: PCI ARBITRATION PINS (INITIATOR ONLY)            | 62 |

| TABLE 5-5: PCI SYSTEM PINS                                  | 62 |

| TABLE 5-6: PCI INTERRUPT PIN                                | 62 |

| TABLE 5-7: PCI INTERFACE CONTROL PINS                       | 63 |

| TABLE 5-8: PCI TARGET UNIT'S WISHBONE INTERFACE (MASTER)    | 63 |

| TABLE 5-9: WISHBONE SLAVE UNIT'S WISHBONE INTERFACE (SLAVE) | 64 |

| TARLE 5-10 WISHRONE COMMON CONTROL AND SYSTEM I/OS          | 6A |

# List of Figures & Examples

| FIGURE 2-1: PCI BRIDGE CORE ARCHITECTURE                              | 4    |

|-----------------------------------------------------------------------|------|

| FIGURE 2-2: WISHBONE SLAVE UNIT ARCHITECTURE                          | 5    |

| FIGURE 2-3: PCI TARGET UNIT ARCHITECTURE OVERVIEW                     | 7    |

| FIGURE 2-4: DETAILED DESCRIPTION OF FIFO REGISTER LINES               | 8    |

| FIGURE 2-5: FIFO ARCHITECTURE                                         | 9    |

| FIGURE 2-6: ADDRESS TRANSLATION LOGIC                                 | 11   |

| FIGURE 3-1: PCI BRIDGE CONFIGURATION SPACE                            | 13   |

| FIGURE 3-2: CONFIGURATION SPACE ACCESS FOR HOST BUS BRIDGES           | 14   |

| FIGURE 3-3: CONFIGURATION SPACE ACCESS FOR GUEST BRIDGES              | 15   |

| FIGURE 3-4: WISHBONE SLAVE UNIT ARCHITECTURE OVERVIEW                 | 19   |

| EXAMPLE 3-1: ADDRESS RANGE OF WISHBONE SLAVE IMAGE                    | 20   |

| EXAMPLE 3-2: ADDRESS TRANSLATION                                      | 21   |

| FIGURE 3-5: PCI TARGET UNIT ARCHITECTURE OVERVIEW                     | 25   |

| EXAMPLE 3-3: ADDRESS RANGE OF WISHBONE SLAVE IMAGE                    | 27   |

| EXAMPLE 3-4: ADDRESS TRANSLATION                                      | 28   |

| FIGURE 4-1: WISHBONE CONFIGURATION SPACE BASE ADDRESS REGISTER LAYOUT | . 39 |

| FIGURE 4-2: WISHBONE IMAGE CONTROL REGISTER LAYOUT                    | 39   |

| FIGURE 4-3: WISHBONE BASE ADDRESS REGISTER LAYOUT                     | 40   |

| FIGURE 4-4: WISHBONE ADDRESS MASK REGISTER LAYOUT                     | 41   |

| FIGURE 4-5: WISHBONE TRANSLATION ADDRESS REGISTER LAYOUT              | 42   |

| FIGURE 4-6: PCI CONFIGURATION SPACE HEADER (HEADER TYPE 00H)          | 43   |

| FIGURE 4-7: PCI IMAGEO BASE ADDRESS REGISTER LAYOUT - IMAGEO USED ACCESSING THE PCI CONFIGURATION SPACE HEADER (TYPE 00H) |    |

|---------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 4-8: PCI IMAGE CONTROL REGISTER LAYOUT                                                                             | 48 |

| FIGURE 4-9: PCI BASE ADDRESS REGISTER LAYOUT                                                                              | 49 |

| FIGURE 4-10: PCI ADDRESS MASK REGISTER LAYOUT                                                                             | 50 |

| FIGURE 4-11: PCI TRANSLATION ADDRESS REGISTER LAYOUT                                                                      | 51 |

| FIGURE 4-12: WISHBONE ERROR CONTROL AND STATUS REGISTER LAYOUT                                                            | 52 |

| FIGURE 4-13: PCI ERROR CONTROL AND STATUS REGISTER LAYOUT                                                                 | 54 |

| FIGURE 4-14: CONFIGURATION ADDRESS REGISTER LAYOUT                                                                        | 56 |

| FIGURE 4-15: INTERRUPT CONTROL REGISTER LAYOUT                                                                            | 57 |

| FIGURE 4-16: INTERRUPT STATUS REGISTER LAYOUT                                                                             | 59 |

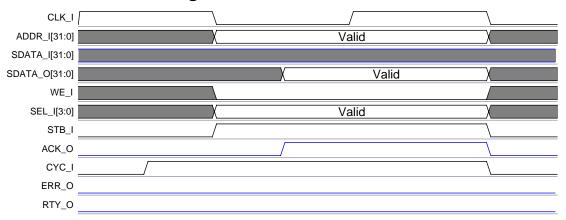

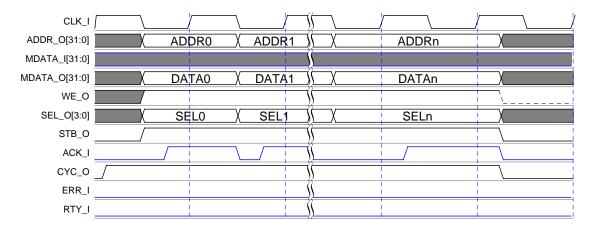

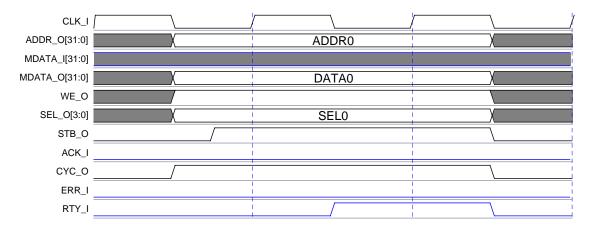

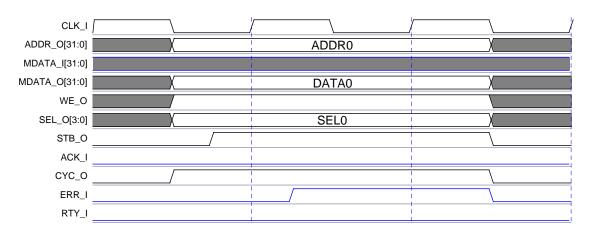

| FIGURE 6-1: WISHBONE CONFIGURATION READ CYCLE                                                                             | 65 |

| FIGURE 6-2: WISHBONE CONFIGURATION WRITE CYCLE                                                                            |    |

| FIGURE 6-3: WISHBONE CONFIGURATION RMW CYCLE                                                                              | 66 |

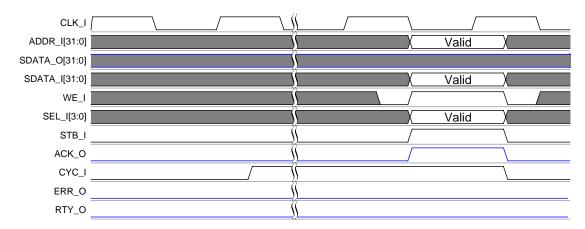

| FIGURE 6-4: WISHBONE ACCESS TO PCI ADDRESS SPACE                                                                          |    |

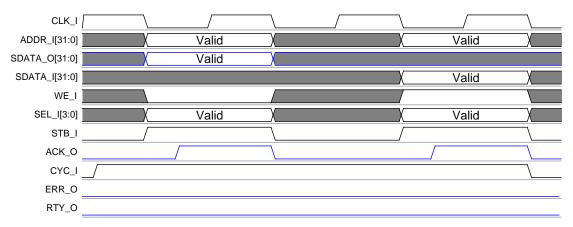

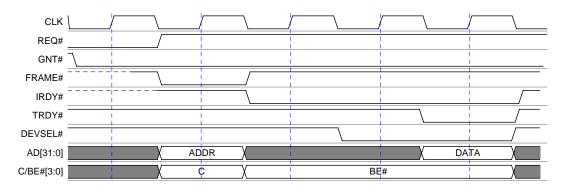

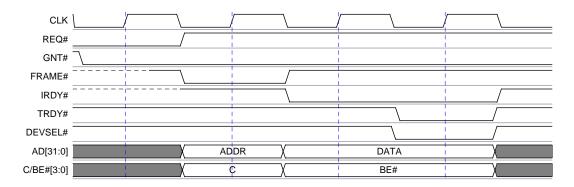

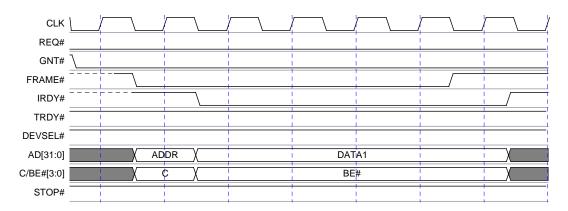

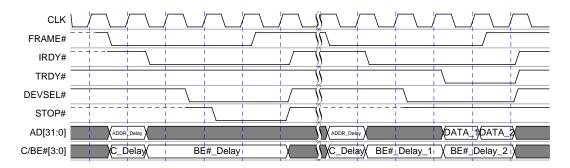

| FIGURE 6-5: PCI SINGLE READ CYCLE                                                                                         |    |

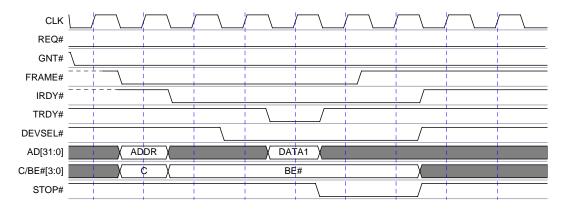

| FIGURE 6-6: PCI SINGLE WRITE                                                                                              | 68 |

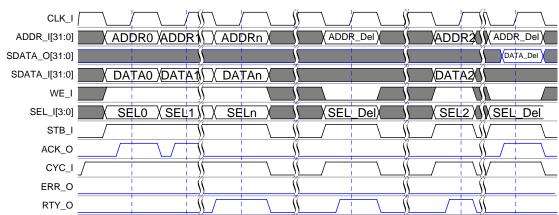

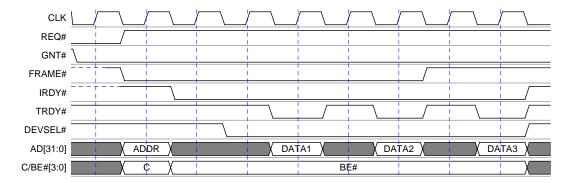

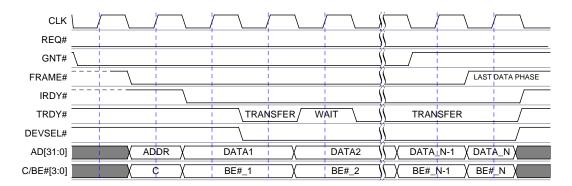

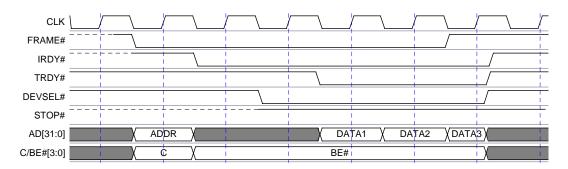

| FIGURE 6-7: PCI BURST READ CYCLE                                                                                          |    |

| FIGURE 6-8: PCI BURST WRITE CYCLE                                                                                         |    |

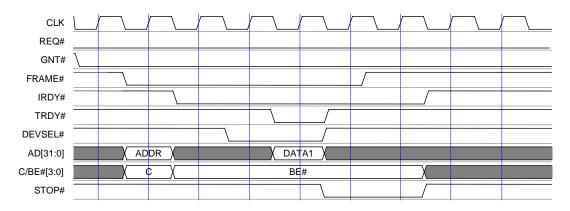

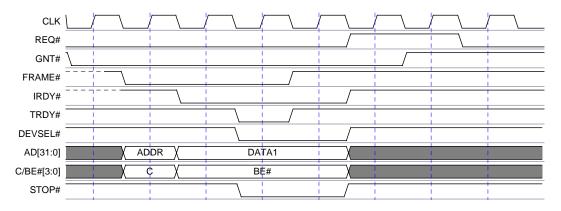

| FIGURE 6-9: MASTER ABORT TERMINATION                                                                                      | 70 |

| FIGURE 6-10: TIMEOUT TERMINATION                                                                                          |    |

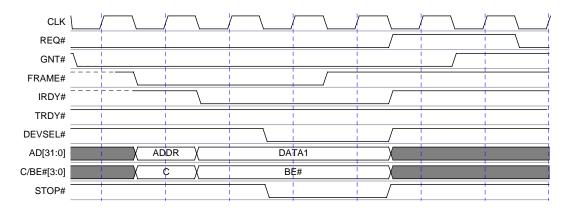

| FIGURE 6-11: TARGET ABORT                                                                                                 |    |

| FIGURE 6-12: TARGET RETRY                                                                                                 |    |

| FIGURE 6-13: TARGET DISCONNECT WITHOUT DATA                                                                               | 73 |

| FIGURE 6-14: TARGET DISCONNECT WITH DATA                                                                                  | 73 |

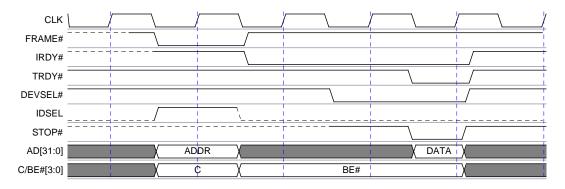

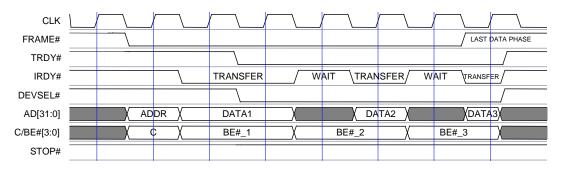

| FIGURE 6-15: PCI CONFIGURATION READ CYCLE                          | 74       |

|--------------------------------------------------------------------|----------|

| FIGURE 6-16: PCI CONFIGURATION WRITE CYCLE                         | 74       |

| FIGURE 6-17: PCI TARGET READ CYCLE                                 | 75       |

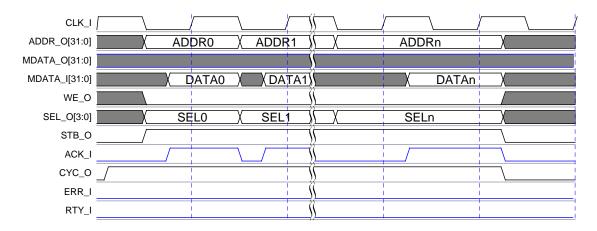

| FIGURE 6-18: PCI TO WISHBONE READ CYCLE                            | 75       |

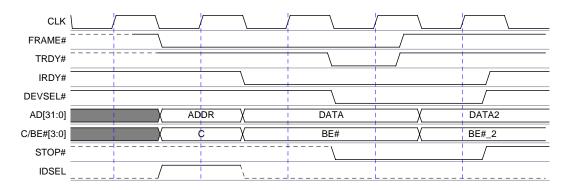

| FIGURE 6-19: PCI INITIATOR TO TARGET BURST READ CYCLE              | 76       |

| FIGURE 6-20: PCI INITIATOR TO TARGET BURST WRITE CYCLE             | 76       |

| FIGURE 6-21: WISHBONE WRITE TRANSFER CAUSED BY PCI TO WISHBO CYCLE |          |

| FIGURE 6-22: RETRY ON WISHBONE BUS CAUSED BY PCI TO WISHBONE TRA   | NSFER 77 |

| FIGURE 6-23: FRROR ON WISHRONE BUS CAUSED BY PCI TO WISHRONE TRA   | NSFER 77 |

1

# Introduction

# 1.1 What is a PCI Bridge?

PCI bridges are used in applications and devices that want to utilize resources provided on a PCI local bus. Systems that have multiple buses must – to enable communication between them – provide an interface that connects the internal buses to the PCI local bus. PCI bridges provide such an interface.

#### 1.2 PCI IP Core Introduction

The PCI IP core (PCI bridge) provides an interface between the WISHBONE SoC bus and the PCI local bus. It consists of two independent units, one handling transactions originating on the PCI bus, the other one handling transactions originating on the WISHBONE bus.

The core has been designed to offer as much flexibility as possible to all kinds of applications.

# 1.3 PCI IP Core Features

The following lists the main features of the PCI IP core:

- > 32-bit PCI interface

- > Fully PCI 2.2 compliant (with 66 MHz PCI specification)

- Separated initiator and target functional blocks

- Supported initiator commands and functions:

- ✓ Memory Read, Memory Write

- ✓ Memory Read Multiple (MRM)

- ✓ Memory Read Line (MRL)

- ✓ I/O Read, I/O Write

- ✓ Configuration Read, Configuration Write

- ✓ Bus Parking

- ✓ Interrupt Acknowledge

- ✓ Host Bridging

- Supported target commands and functions:

- ✓ Type 0 Configuration Space Header

- (Type 0 is used to configure agents on the same bus segment)

(Type 1 is used to configure across PCI-to-PCI bridges) Parity Generation (PAR), Parity Error Detection (PERR# and SERR#)

- ✓ Memory Read, Memory Write

- ✓ Memory Read Multiple (MRM)

- ✓ Memory Read Line (MRL)

- ✓ Memory Write and Invalidate (MWI)

- ✓ I/O Read, I/O Write

- ✓ Configuration Read, Configuration Write

- ✓ Target Abort, Target Retry, Target Disconnect

- ✓ Fast Back-to-Back Capable Target response

- > Full Command/Status registers

- WISHBONE SoC Interconnection Rev. B compliant interface on processor side (master with Target PCI and slave with Initiator PCI interface)

- Configurable on-chip FIFOs

2

# **Architecture**

#### 2.1 Overview

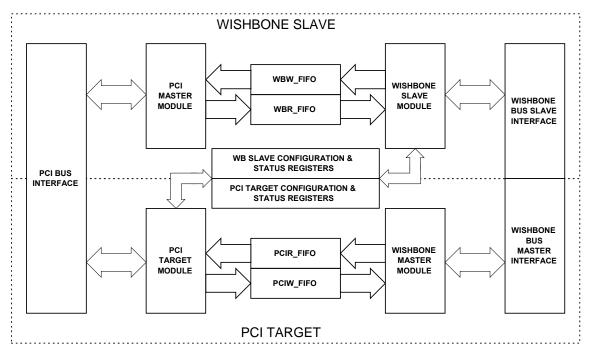

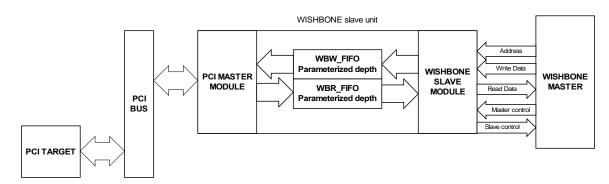

The PCI bridge consists of two units: the PCI target unit and the WISHBONE slave unit. Each holds its own set of functions to support bridging operations from WISHBONE to PCI and from PCI to WISHBONE. The WISHBONE slave unit acts as a slave on the WISHBONE side of the bridge and initiates transactions as a master on the PCI bus. The PCI target unit acts as a target on the PCI side of the bridge and as a master on its WISHBONE side. Both units operate independently of each other. The PCI target unit implements the target interface on the PCI bus and the master interface on the WISHBONE bus, the WISHBONE slave unit implements the slave interface on the WISHBONE bus and the master interface on the PCI bus.

The PCI interface is *PCI Specification 2.2* compliant, whereas the WISHBONE is *SoC Interconnection Specification Rev. B* compliant. The WISHBONE implementation carries out 32-bit bus operations and does not support other bus widths.

Following figure gives an overview of the PCI bridge core architecture.

Figure 2-1: PCI bridge core architecture

#### 2.2 WISHBONE Slave Unit

The WISHBONE bus agents can access the PCI bus through the WISHBONE slave unit. One to five configurable images can be used to access the PCI address space.

Each image consists of:

- Base address register

- Address mask register

- > Translation address register

- Image control register

- Decoder

The Base address, stored in the Base Address register, is masked with a value stored in the Address Mask register. The decoder compares the WISHBONE bus address with the masked base address to identify valid WISHBONE cycles. If needed, each valid address can be translated to a different value before accessing the PCI bus. The value for an address to be presented on the PCI bus is stored in the Address Translation register. The Image Control register is used to control the behavior of an image.

Each image can be configured to access memory or I/O address space on the PCI bus.

Write cycles through the WB slave unit are processed as Posted Writes and Read cycles as delayed reads. Reads can also be pre-fetched if the image accessed is configured properly. The only exception to that rule is Configuration Write, which is initiated by a special mechanism and therefore described separately in subsequent chapters.

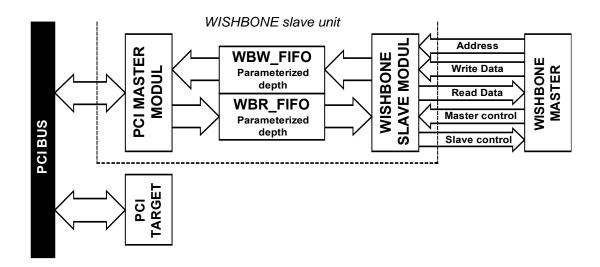

The WISHBONE Write FIFO (WBW\_FIFO) is used to post writes performed on the WISHBONE bus; the WISHBONE Read FIFO (WBR\_FIFO) accumulates pre-fetched reads. The WISHBONE slave unit connects to WISHBONE masters by acting as a slave.

This section describes the architecture of a WISHBONE slave unit and is divided into subsections.

#### 2.2.1 WISHBONE Slave Unit Architecture

The WISHBONE slave unit consists of a few functional parts allowing the WISHBONE master to perform Read/Write access to the PCI bus. The following sections provide detailed descriptions.

Figure 2-2: WISHBONE slave unit architecture

#### 2.2.1.1 WISHBONE Slave Module

The WISHBONE slave module, which includes one to six image units for address translation from the WISHBONE bus, is a 32-bit WISHBONE slave interface as defined in *WISHBONE Specification Rev. 1B*. It handles Read/Write cycles to images of PCI address space and configuration space accesses.

#### 2.2.1.2 WBW\_FIFO

The WISHBONE slave module uses WBW\_FIFO (WISHBONE Write FIFO) for posting memory and I/O Write cycles performed by the WISHBONE master. Parameterized depth provides the option to define the WBW\_FIFO with regard to application specific needs for posting more or less Write cycles.

The WISHBONE bus determines the speed of Write cycles to the WBW\_FIFO, whereas the PCI bus regulates the speed of Write cycles from the WBW\_FIFO.

#### 2.2.1.3 WBR\_FIFO

The WISHBONE slave module uses WBR\_FIFO (WISHBONE Read FIFO) for storing data read from PCI targets.

The PCI bus determines the speed of Read cycles to the WBR\_FIFO, and the WISHBONE bus regulates the speed of Read cycles from the WBR\_FIFO.

#### 2.2.1.4 PCI Master Module

The PCI master module uses information provided by the WISHBONE slave module to perform PCI bus cycles. It is a 32-bit/66MHz (33MHz in FPGA), PCI Local Bus Specification Rev. 2.2 compliant initiator interface.

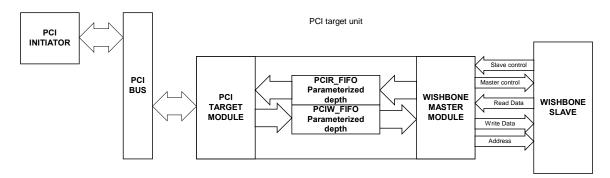

# 2.3 PCI Target Unit

PCI agents can access the WISHBONE bus through the PCI target unit of the bridge, which provides one to six images of the WISHBONE side memory space. Each image is selected by an address provided during the address phase on the PCI bus. It is compared to the base address masked with a mask value stored in PCI Configuration registers and can be mapped into the memory or I/O space. An address can also be translated to a value stored in the Translation Address register if the image is properly configured.

Write cycles through the PCI target unit are handled as Posted Writes. Read cycles and can be prefetched.

The PCIW\_FIFO stores Posted Write cycles; the PCIR\_FIFO saves pre-fetched Read cycles.

# 2.3.1 PCI Target Unit Architecture

This part describes the architecture of the PCI target unit. The following sections provide detailed descriptions.

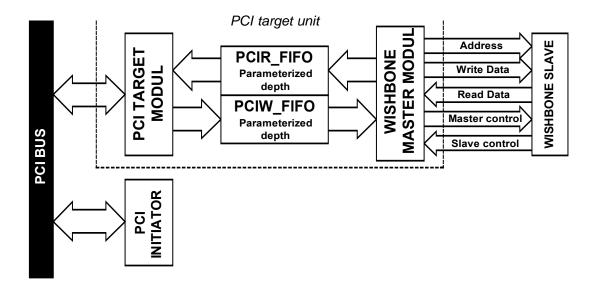

Figure 2-3: PCI target unit architecture overview

The PCI target unit consists of a few functional parts allowing PCI initiators to perform Read/Write accesses to the WISHBONE bus.

The PCI target module is a 32-bit/66MHz (33MHz in FPGA), *PCI Local Bus Specification Rev. 2.2* compliant target interface that includes two to six image units for address translation from the PCI bus. Therefore, it handles Read/Write cycles to images of WISHBONE address space and configuration space accesses.

#### 2.3.1.1 PCI Target Module

The PCI target module uses PCIW\_FIFO (PCI Write FIFO) for posting memory and I/O Write cycles performed by the PCI initiator. Parameterized depth provides the option to define the PCIW\_FIFO with regard to application specific needs for posting more or less Write cycles.

The PCI bus determines the speed of Write cycles to the PCIW\_FIFO, whereas the WISHBONE bus regulates the speed of Write cycles from the PCIW\_FIFO.

#### 2.3.1.2 PCIR FIFO

The WISHBONE master module uses PCIR\_FIFO (PCI Read FIFO) for storing data read from WISHBONE slaves.

The WISHBONE bus determines the speed of Read cycles to PCIR\_FIFO, and the PCI bus regulates the speed of Read cycles from the PCIR\_FIFO.

#### 2.3.1.3 WISHBONE Master Module

The WISHBONE master module is a 32-bit WISHBONE master interface as defined in WISHBONE Specification Rev. 1B. Through its WISHBONE master module, the core sends requests to the WISHBONE bus. Chapter 5.2 WISHBONE Interface, provides detailed information on the WISHBONE interface of the core.

#### 2.4 Clocks

The PCI core has two clock domains, one from the PCI bus, the other one from the WISHBONE bus. With its interconnection logic, the FIFO adjusts the different bus clocks. There is no difference between all four FIFOs, because it is not decisive which bus operates on higher frequency.

#### **2.5 FIFO**

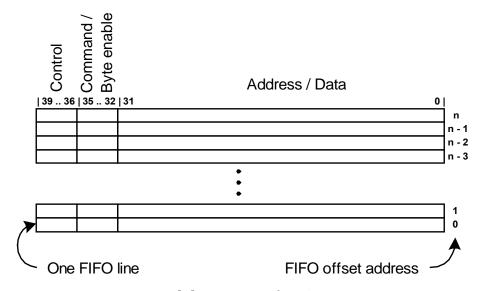

Figure 2-4: Detailed Description of FIFO Register Lines

The FIFO is structured by more than one line. The number of FIFO lines, which is configurable, determines the depth number (the *Design Document and Implementation Notes* discuss in detail how FIFO depth is defined). Figure 2-4 describes the structure of one FIFO line, which consists of 4 control

bits (the *Design Document* describes in detail how they are used—e.g. one bit is used to sign the last data of the burst transfer etc.), 4 command or byte enable bits (coding will be described in detail in the *Design Document*), and 32 address or data bits.

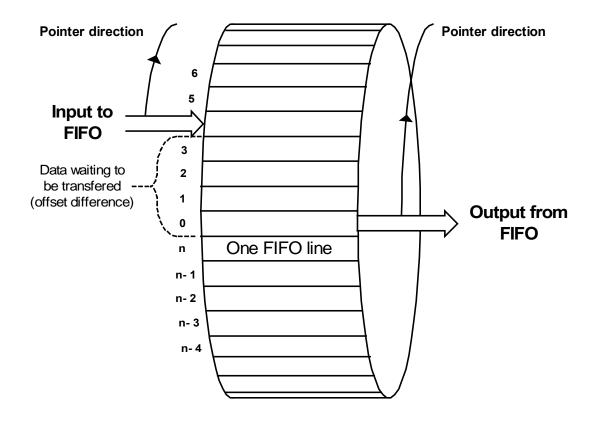

FIFOs are implemented as circular data buffers between WISHBONE and PCI interfaces (Figure 2-5) and adapt to different bus speeds with their interconnection logic. The input bus clock, which is also connected to FIFO registers, writes data to the input side of the FIFO. The input pointer (input counter), which has the same clock frequency as the input bus side, stores the value of the input offset address of the first free FIFO line.

Figure 2-5: FIFO Architecture

The output pointer (output counter) stores the output offset address value of the first FIFO line from which data is to be read. It has the same clock frequency as the output bus side that reads the data.

The comparator between both pointers (counters) validates if any data is waiting in the FIFO to be read (the **Design Document** describes in detail the exact counter/comparator operation). Another comparator is between the counter, which has the value of an input pointer incremented to one, and the output pointer. When both variables are equal, the FIFO is full.

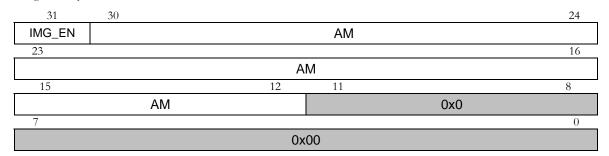

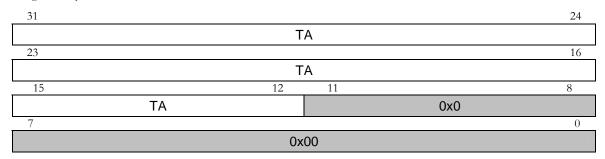

# 2.6 Address Translation Logic

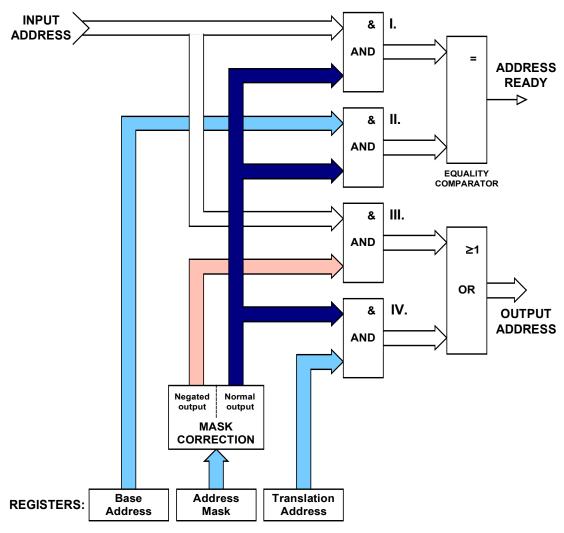

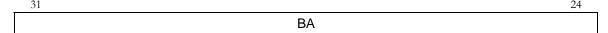

WISHBONE slave unit and PCI target unit incorporate several address space images. Each image must have address translation logic (Figure 2-6) including its own set of 32-bit registers:

- ➤ Base Address register [31:0]

- Address Mask register [31:0]

- > Translation Address register [31:0]

- Image Control register [31:0]

### 2.6.1 Description of Address Translation Logic

For a description of the address translation logic, see Figure 2-6. All AND blocks and OR blocks are bit-oriented operators that stand for logic operations between bits of the same weight (e.g. logic function between bit[n-2] of bus A and bit[n-2] of bus B).

The base address is written into the Base Address register. The Address Mask register, which also defines the size of an image, decides how many most significant bits are masked and replaced by translation address bits. There is a rule how to set the Address Mask register: Address bits that can be masked must start with the MS bit (bit[31]) and continue to the twelfth bit (bit[11]). All bits allowed to be masked define the smallest size of 4KB that can be assigned. No zeros must be between mask bits; otherwise this image will have two base addresses but only one Base Address register—a situation that does not comply with the *PCI Specification*.

To find out if an address falls into the correct address range, the masked bits of input address and base address must be compared (the number of masked bits defines the unchanging address of the current address range and thereby the size of this image).

Figure 2-6: Address Translation Logic

3

# **Operation**

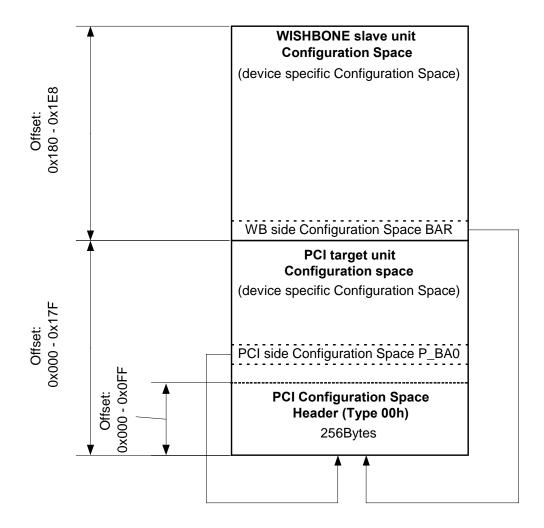

# 3.1 Configuration Space

Depending on core implementation, either the PCI or the WISHBONE agents have full access to configuration space. If the core is implemented as a host bus bridge, the WISHBONE slave unit has exclusive access to this space, whereas the PCI target unit has read-only access (this image can be canceled or changed to normal PCI to WB image). If the core is implemented as a guest (expansion bus bridge), exclusive access to configuration space lies with the PCI target unit and the WISHBONE slave unit has read-only access (this image can also be canceled).

Configuration space has a configurable block size and is divided into two parts—one intended for Configuration, Control, and Status registers of the WB slave unit, the other one for PCI Target Unit registers. If the core is implemented as a host bus bridge, accessing specific registers in the configuration space from the WISHBONE bus can generate PCI configuration cycles; otherwise, another agent on the PCI bus must perform these cycles. Configuration space is accessible only with Single Read and Single Write cycles (e.g. it cannot be accessed with bursts from the PCI side).

All registers in the configuration space of a core are 32-bits wide with 8-bit granularity. All accesses must be DWORD aligned (e.g. two LS bits of address must be 00). The PCI standard defines special encoding for those two bits used for PCI bus memory access. If any of them are non-zero, the WISHBONE slave module signals a bus error, while PCI target module stops burst after one data is transferred. To access individual bytes, the BE# signals for PCI bus access and the SEL\_O signals for WISHBONE bus access must carry an appropriate value.

Figure 3-1: PCI Bridge Configuration Space

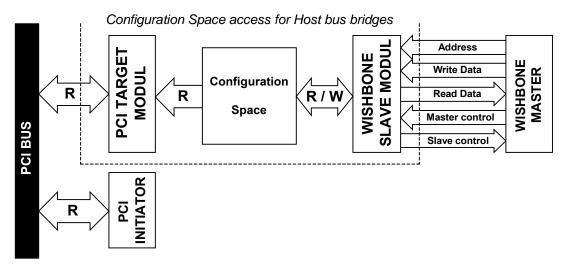

# 3.1.1 Configuration Space Access for Host Bus Bridges

The core's host bus bridge implementation provides two types of access to configuration space: Read/Write access for the WISHBONE slave unit and read-only access for the PCI target unit (unless PCI Target image 0 is canceled or used to access the WISHBONE bus—in which case other PCI device can not read configuration space. See also 3.3.2 Addressing and Images of the PCI Target Unit and 4.1 Register List and Description). Thus, the WISHBONE master takes full responsibility for configuring core registers and any other PCI devices residing on the PCI bus. The WISHBONE side configuration space base address is predefined and cannot be changed once the core has been implemented (the *Design Document* describes in detail how and where the base address is defined.).

Figure 3-2: Configuration space access for Host Bus Bridges

The WISHBONE master can access configuration space either by Single Read, Single Write, or Read Modify Write (RMW) cycles. If the WISHBONE master attempts a Write cycle to non-implemented space, the cycle is acknowledged by the WISHBONE slave module while Read cycles to non-implemented space return all 0s.

The PCI side configuration space base address must be set by the WISHBONE master. The WISHBONE master must perform a Write cycle to the PCI side configuration space Base Address register to enable read-only access to PCI agents. The PCI target module provides read-only access to configuration space from the PCI bus, supporting Memory Read and Memory Write commands, but ignoring all other commands. The Memory Write command has no effect on Configuration registers. During the first data phase, the PCI target module signals **Target Disconnect with Data** to the initiator. Read cycles to non-implemented regions of configuration space return all 0s, whereas Write cycles have no effect.

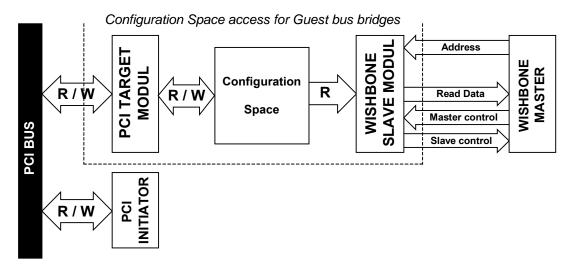

### 3.1.2 Configuration Space Access for Guest Bridges

The implementation of the core as a guest bridge (more commonly referred to as expansion bus bridge) provides two types of configuration space access: Read/Write access for the PCI target unit and read-only access for the WISHBONE slave unit (unless WB slave image 0 is canceled). Other PCI agents take full responsibility for configuring core registers and any other PCI devices residing on the PCI bus. An agent on the PCI bus (most commonly the host bus bridge) sets the PCI side configuration space base address by performing a Type 0 configuration cycle and writing the base address to the PCI configuration space, as stated in the *PCI Local Bus Specification Rev. 2.2.* The PCI side configuration space Base Address register 0 holds the same value as the first Base Address register in the PCI configuration space Header at offset 0x10. This enables device-independent software to map the bridge configuration space anywhere into the memory address space. After the base address has been set by a Type 0 configuration cycle and the bridge is in a normal mode of

operation, the PCI agent can re-map configuration space anywhere within the memory space by writing to the PCI side configuration space Base Address register 0.

Figure 3-3: Configuration space access for Guest Bridges

Configuration space access can be provided to the PCI initiator as Memory Read or Memory Write. In case the PCI initiator requests configuration space access by using a different bus command, the PCI target module does not respond. If the PCI initiator attempts an access (Read or Write) to non-implemented space, the initial data phase is terminated by signaling **Target Disconnect with Data**. Write cycles have no effect on non-implemented configuration space, but Read cycles return all 0s.

The WISHBONE slave module provides read-only access to configuration space from the WISHBONE bus. The WISHBONE side configuration space base address is predefined and cannot be changed (the *Design Document* describes in detail how and where a base address is defined). The WISHBONE slave module accepts Read or Write transfers to configuration space. Write cycles to configuration space have no effect on Configuration Space registers. When the WISHBONE master attempts to access a non-implemented region, Write cycles are acknowledged with no effect on configuration space, but Read cycles return all 0s.

# 3.1.3 Configuration Cycles

Configuration cycles are another way of accessing the configuration space of the core. Only the lower 256 bytes of configuration space are available for Read/Write access with Type 0 configuration cycles for guest (expansion bus) implementation of the core. The host bus bridge implementation provides

the Configuration Read operation only. Configuration Write cycles are accepted and acknowledged but have no effect on Configuration registers.

Addressing in configuration cycles is different from normal Read and Write cycles on a PCI bus (For more information, see *PCI Local Bus Specification Rev 2.2*, chapter 3.1.1, "Command Definition").

Only Type 00h predefined header portion has been implemented in the lower 256 bytes of the configuration space (in this document also called PCI configuration space). For its organization, see *PCI Local Bus Specification Rev 2.2*, chapter 6.1.

### 3.1.4 Generating Configuration Cycles

The host bus bridge implementation of the core provides a mechanism for generating configuration cycles on a PCI bus by accessing the CNF\_ADDR and CNF\_DATA register.

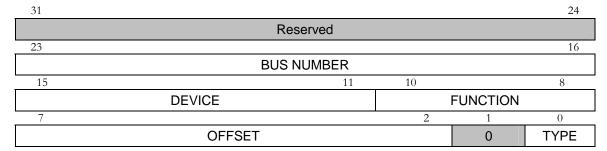

**Step 1:** The WISHBONE master must write the appropriate data to the CNF\_ADDR register, which holds information about register offset, function, device, and bus number. The TYPE bit in this register defines a type of configuration cycle that is generated on the PCI bus (0 = Type 0, 1 = Type 1). The **Offset** field in the CNF\_ADDR register identifies a register offset to or from which the WISHBONE master wishes to write or read. The **Function** field is set to the function number of multifunctional devices being a target of configuration cycles. The **Device** field, which identifies the address line that drives high for generating the IDSEL signal for a Type 0 configuration cycle, is set to the device number on the PCI bus. The **Bus** field is set to the bus number the targeted device resides on.

**Step 2:** To actually begin a configuration cycle on the PCI bus, the WISHBONE master must access the CNF\_DATA register. Accesses to CNF\_DATA are treated as Single Delayed transactions. The WISHBONE master's access to this register is retried. If it is a Read cycle, the PCI master module arbitrates for the PCI bus, performs the Configuration Read command with byte enables provided by the WISHBONE master (signals **SEL\_O(3..0)**), and provides data on the WISHBONE interface when the WISHBONE master retries the transaction. In case of a Write access, the PCI master module arbitrates for the PCI bus, performs a Write cycle with provided byte enables (signals **SEL\_O(3..0)**), and acknowledges the transaction when retried by the WISHBONE master.

Driving of PCI bus AD lines during the configuration cycle address phase depends on the TYPE of the configuration cycle. If the WISHBONE master sets the TYPE bit of CNF\_ADDR to 1 (indicating Type 1 configuration cycle), the value of lines on the PCI bus is driven with contents of the CNF\_ADDR register (AD[31..0] <= CNF\_ADDR[31..0]) during address phase. If the TYPE bit indicates TYPE 0 configuration cycle, then AD[31..11] lines on the PCI bus are driven according to the following table (driving depends on the **Device** field in the CNF\_ADDR register):

<sup>&</sup>lt;sup>1</sup> Note: Because the host bus bridge normally generates configuration commands, and the PCI local bus specification does not require a host bus bridge to respond to configuration cycles, it is most likely that this feature will never be used.

| DEVICE<br>field<br>value | Value on AD[3111] lines during address phase of configuration cycle |

|--------------------------|---------------------------------------------------------------------|

| 0000 0                   | 0000 0000 0000 0000 0000 1                                          |

| 0000 1                   | 0000 0000 0000 0000 0001 0                                          |

| 0001 0                   | 0000 0000 0000 0000 0010 0                                          |

| 0001 1                   | 0000 0000 0000 0100 0                                               |

| 0010 0                   | 0000 0000 0000 1000 0                                               |

| 0010 1                   | 0000 0000 0000 0001 0000 0                                          |

| 0011 0                   | 0000 0000 0000 0010 0000 0                                          |

| 0011 1                   | 0000 0000 0000 0100 0000 0                                          |

| 0100 0                   | 0000 0000 0000 1000 0000 0                                          |

| 0100 1                   | 0000 0000 0001 0000 0000 0                                          |

| 0101 0                   | 0000 0000 0010 0000 0000 0                                          |

| 0101 1                   | 0000 0000 0100 0000 0000 0                                          |

| 0110 0                   | 0000 0000 1000 0000 0000 0                                          |

| 0110 1                   | 0000 0001 0000 0000 0000 0                                          |

| 0111 0                   | 0000 0010 0000 0000 0000 0                                          |

| 0111 1                   | 0000 0100 0000 0000 0000 0                                          |

| 1000 0                   | 0000 1000 0000 0000 0000 0                                          |

| 1000 1                   | 0001 0000 0000 0000 0000 0                                          |

| 1001 0                   | 0010 0000 0000 0000 0000 0                                          |

| 1001 1                   | 0100 0000 0000 0000 0000 0                                          |

| 1010 0                   | 1000 0000 0000 0000 0000 0                                          |

| 1010 1                   | 0000 0000 0000 0000 0000 0                                          |

| 1011 0                   | 0000 0000 0000 0000 0000 0                                          |

| 1011 1                   | 0000 0000 0000 0000 0000 0                                          |

| 1100 0                   | 0000 0000 0000 0000 0000 0                                          |

| 1100 1                   | 0000 0000 0000 0000 0000 0                                          |

| 1101 0                   | 0000 0000 0000 0000 0                                               |

| 1101 1                   | 0000 0000 0000 0000 0000 0                                          |

| 1110 0                   | 0000 0000 0000 0000 0000 0                                          |

| 1110 1                   | 0000 0000 0000 0000 0                                               |

| 1111 0                   | 0000 0000 0000 0000 0                                               |

| 1111 1                   | 0000 0000 0000 0000 0000 0                                          |

Table 3-1: Value on AD[31:11] PCI bus lines during address phase of configuration cycle Type 0

Specified driving of PCI bus lines AD[31..11] provides a mechanism for tying IDSEL signals of target devices directly to AD lines. This way, device 0 is connected with its IDSEL signal to AD[11], device number 1 to AD[12], until device 20 connects to AD[31]. A total of 21 targets can be accessed with configuration cycles through the PCI bridge. Combinations of **Device** field values of CNF\_ADDR register 10101 through 11111 are valid and terminate **Master Abort** on the PCI bus since none of the targets can respond to the cycle without its IDSEL signal being asserted. Configuration Write data is discarded while Read cycles return all 1s on the WISHBONE bus. The transaction is acknowledged as specified in **PCI Specification Rev. 2.2**.

Other AD lines on the PCI bus are driven during the address phase of the Type 0 configuration cycle with data stored in the CNF\_ADDR register, as described in *PCI Specification Rev. 2.2*.

### 3.1.5 Generating Interrupt Acknowledge Cycles

A special mechanism provides the generation of Interrupt Acknowledge cycles on the PCI bus. The WISHBONE master must perform a Read cycle to the INT\_ACK register. This Read cycle is treated as Single Delayed transaction retried until the PCI master module arbitrates for the PCI bus and fetches the data requested. Address and byte enables on the PCI bus are exact copies of ADR\_O(31..0) and SEL(3..0). The address has no meaning during an interrupt acknowledge cycle while byte enables indicate the size of the interrupt vector returned.

Read cycles of this register from the PCI bus have no effect and return all 0s. Write cycles from the WISHBONE or PCI side are accepted but have no effect.

### 3.2 WISHBONE Slave Unit

The WISHBONE slave unit connects to WISHBONE masters acting as a slave. This section describes its basic functionality. It is divided into subsections, each of them describing what the WISHBONE master needs to do to initiate WISHBONE to PCI transactions.

### 3.2.1 WISHBONE Slave Unit Functionality

Figure 3-4: WISHBONE Slave Unit Architecture Overview

The WISHBONE slave unit consists of a few functional parts allowing the WISHBONE master to perform Read/Write accesses to the PCI bus.

#### 3.2.1.1 WISHBONE Slave Module

The WISHBONE slave module is a 32-bit WISHBONE slave interface as defined in *WISHBONE* Specification Rev. 1B. It handles Read/Write cycles to images of PCI address space and configuration space accesses.

#### 3.2.1.2 WBW\_FIFO

The WISHBONE slave module uses WBW\_FIFO (WISHBONE Write FIFO) for posting Memory and I/O Write cycles performed by the WISHBONE master. WBW\_FIFO also performs a different bus clock adaptation.

#### 3.2.1.3 WBR\_FIFO

The WISHBONE slave module uses WBR\_FIFO (WISHBONE Read FIFO) for storing data read from PCI targets. WBR\_FIFO also performs a different bus clock adaptation.

#### 3.2.1.4 PCI Master Module

The PCI master module is a 32-bit/66MHz, *PCI Local Bus Specification Rev. 2.2* compliant initiator interface. The core requests the PCI bus through its PCI master module and performs bus

operations as described in the following subsections. Chapter 5.1 PCI Interface provides a detailed overview of the PCI interface of the core.

### 3.2.2 Addressing and Images of the WISHBONE Slave Unit

As mentioned before, the WISHBONE slave unit incorporates 1 to 5 configurable WISHBONE address space images (the *Design Document and Implementation Notes* discuss in detail how the number of images is defined) and one image used for configuration space accesses from the WISHBONE bus with a fixed base address. This fixed base address points to the starting address of the configuration space. The base address for WISHBONE configuration space points to the offset address of the whole configuration space and is different from the first Base Address register in the PCI header that is also used for the same configuration space, but different bus (PCI).

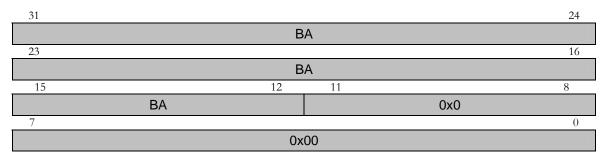

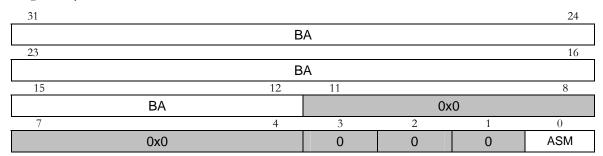

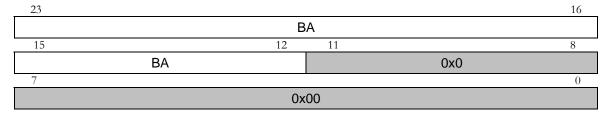

The behavior of each image is controlled by its WISHBONE Base Address (W\_BA1 – W\_BA5), WISHBONE Translation Address (W\_TA1 – W\_TA5), WISHBONE Image Control (W\_IMG\_CTRL1 – W\_IMG\_CTRL5) and WISHBONE Address Mask (W\_AM1 – W\_AM5) registers. Statuses, errors, and interrupts for each image are recorded in the Status registers of an image described later in this document. The WISHBONE slave module claims the cycle initiated by the master on the WISHBONE bus if one of the WISHBONE images is selected and enabled. An image is enabled if the IMG\_EN bit of its W\_AM register is set to 1. An image is selected when the address provided during the initial cycle on the WISHBONE bus falls into the memory range of that image. The range is determined by values of W\_BA and W\_AM registers. Each image can represent 4KB to 2GB of PCI address space. Whether an image is mapped to memory or I/O space is determined by the address space-mapping bit (ASM) of the image's P\_Bax register. If this bit is 0, the image maps to memory space, otherwise to I/O space.

How to specify a 1MB image of PCI address space with an address range of 0x10100000 - 0x101FFFFF?

The software must write a value of 0x10100XX0 to the image's Base Address register (the LSB of this register is set to 0 to indicate a memory space mapping). This way, the base address is set at 0x10100000. Twelve LS bits are marked as Don't Cares. The minimum block size is 4KB. Then, the software writes a value of 0xFFF00XXX into the W\_AM register of the corresponding image. The IMG\_EN bit is the MS bit and set to a value of 1 (it is also used for address masking – i.e. how we limit a maximum image size to 2GB). Each bit in the W\_AM register corresponds to one address line – if a bit is 1, this address line is used for address comparison, and otherwise it is not. A value of 0xFFF00000 in the W\_AM register means that ADDR\_O(31..20) signals are compared to W\_BA[31..20] values. If values match, the image is selected. In this case, ADDR\_O(19..0) lines define an offset in an address range of 1MB.

**Example 3-1: Address range of WISHBONE slave image**

If enabled for a selected image (AT\_EN bit of W\_IMG\_CTRLx is 1), address translation is performed between WISHBONE and PCI address by replacing the masked part of a WISHBONE address with the corresponding bits from the W\_AT register. This provides very flexible address mapping.

Let's assume that base address and address mask are set as described in the previous example. We **WISHBONE** want address range of 0x101FFFFF to be mapped elsewhere on the PCI bus, 0x10100000e.g. 0x01000000 - 0x010FFFFF. To achieve this, we need a translation of addresses coming from the WISHBONE master and set the AT\_EN bit of the corresponding W\_IMG\_CTRL register to a value of 1 and of the corresponding W\_AT register to a value of 0x01000XXX. The W\_AM register is already set, so address translation replaces ADDR\_O(31..20) provided by the WISHBONE master with a value of 0x010 set in the W\_AT register for accesses on the PCI bus. This way, a PCI address range of 0x01000000 - 0x010FFFFF is accessible on the WISHBONE bus within a range of 0x10100000 - 0x101FFFFF.

**Example 3-2: Address translation**

#### 3.2.3 WISHBONE to PCI Write Cycles

This section gives a detailed description of Write accesses, assuming that the WISHBONE slave unit has decoded an address to fall within a range of one of its enabled images.

The WISHBONE slave module is capable of handling Single and Block Write transfers through one of its WISHBONE slave images. Read Modify Write (RMF) cycles are not supported.

#### Note

Serial block transfers (bursts) are still under discussion because the *WISHBONE Bus Specification* does not provide a mechanism to identify them. Until serial block transfers are specified, Block Write cycles will be handled as Single Write cycles. Proposal: It might be good to use an internal signal hardwired to a value indicating non-burst transfers. The definition of bursts in the *WISHBONE Specification* can be used to indicate whether a block transfer is serial or not. All Write cycles from the WISHBONE master to the PCI bus are handled as Posted Writes and are acknowledged on the WISHBONE bus immediately after receiving a request (before they are finished on the PCI bus) and stored in WBW\_FIFO. Each image can be mapped to I/O or memory space, which is determined by a value of the address space-mapping bit (ASM) the W\_BAx register of the corresponding image. If an image maps to I/O space, serial block transfers are not possible and the WISHBONE master receives an error signal. Normal block transfers are possible to I/O and memory space since every data beat in a block is treated as Single Posted Write cycle.

A Write cycle to an address range occupied by an image that is mapped into memory space must be DWORD-aligned (e.g. ADDR\_O(1:0) must be 00), otherwise an error terminates the cycle on the WISHBONE bus.

A Write cycle to an address range occupied by an image that is mapped into I/O space must be bytealigned. The following table describes valid SEL\_O(3:0) encoding for different values on ADDR\_O(1:0).

| Value on ADDR_O(1:0) lines | Valid SEL_O(3:0) encoding |

|----------------------------|---------------------------|

| 00                         | SEL_O(0) must be active   |

| Value on ADDR_O(1:0) lines | Valid SEL_O(3:0) encoding                                |

|----------------------------|----------------------------------------------------------|

| 01                         | SEL_O(1) must be asserted, SEL_O(0) cannot be asserted   |

| 10                         | SEL_O(2) must be asserted, SEL_O(1:0) can't be asserted  |

| 11                         | SEL_O(3) must be asserted, SEL_O(2:0) cannot be asserted |

Table 3-2: Valid ADDR\_O(1:0) and SEL\_O(3:0) combinations for I/O mapped address space access

All other combinations are invalid. An invalid access is terminated with **Error** on the WISHBONE bus.

In some cases, Write cycles initiated by the WISHBONE master cannot be accepted and are terminated with **Retry**:

- > WBW\_FIFO is full or does not have enough space left to accommodate another transfer.

- An uncompleted Delayed Read request is still pending in a WISHBONE slave unit (Write cycles cannot be posted until a Read cycle finishes on the PCI bus).

The PCI master module requests a PCI bus after a complete transaction has been stored in the WISHBONE slave unit WBW\_FIFO. After the PCI bus has been granted to the PCI master module, it initiates a transaction on the PCI bus. The module uses Memory Write or I/O Write PCI bus commands, depending on the value of the address space-mapping bit (0 = memory, 1 = I/O) of the image W\_BAx register. In case the WISHBONE master posted a serial Block Write cycle, the PCI master module performs a burst of the same length to the PCI target. Single Posted Write cycles or non-serial Block Write cycles are completed as Single Write cycles on the PCI bus. If the PCI bus arbiter revokes mastership from the PCI master module (#GNT is deasserted), it finishes the current cycle and releases the PCI bus for which it afterwards has to re-arbitrate in order to continue any Posted Write cycles left in a WBW\_FIFO. The core handles **Retry** and **Target Disconnect** terminations by retrying the transaction until it completes or some other termination is signaled.

Because all Write cycles are posted to and are therefore immediately acknowledged by the WISHBONE master, there is an alternate way of communicating errors signaled on the PCI bus when Posted Write cycles have already been written to their final destination: Error Reporting registers provide an Error Reporting mechanism. Error Reporting must be enabled by the errors enable (ERR\_EN) bit of the WISHBONE Error Control and Status (W\_ERR\_CS) register. When enabled, errors can generate interrupts if the error interrupt enable (EINT\_EN) bit of the W\_ERR\_CS register is 1. Each of the Error Reporting registers stores a part of information about the Posted Write transaction on the PCI that was terminated with an error.

- A value of 1 in the error signaled bit (ERR\_SIG) of the W\_ERR\_CS register indicates that an error has been recorded. The Field Bus Command (BC) of this register stores a bus command used for an access that has been terminated with Error, while field Byte Enables (BE) stores the value of byte enables during the transfer. The error source bit (ES) indicates the source of an error (1 = Master (Master Abort), 0 = Target (**Target Abort**)).

- W\_ERR\_ADDR stores a 32-bit address that the PCI master module tried to access when the error occurred.

> W\_ERR\_DATA stores 32 bits of data used in a transfer that was terminated with an error.

Error terminated write transactions are discarded while other posted transactions proceed normally.

#### 3.2.4 WISHBONE to PCI Read Cycles

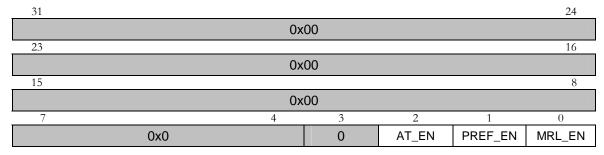

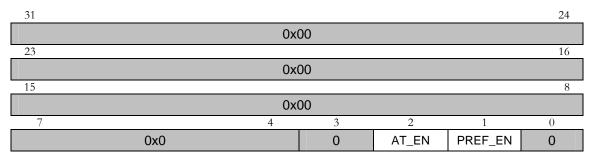

Read cycles initiated by the WISHBONE master are handled as Single Delayed Read cycles. Multiple Delayed Read cycles are not supported. Delayed transactions must be completed on the PCI bus before they can be completed on the WISHBONE bus. The section on addressing and images has described how the WISHBONE slave unit decodes addresses to know if it is a slave for a current cycle. Handling of Read transactions is encoded in the Image Control register (W\_IMG\_CTRLx). There are a few options how to define the behavior of the WISHBONE slave unit during Read transactions for images mapped to memory space:

- > The PREF\_EN bit indicates that the address range of an image is prefetchable, which means that the bridge core can pre-fetch data from the target and store it in WBR\_FIFO. This method increases the system performance since a Delayed Read transaction only knows the starting address of the transfer.

- The MRL\_EN bit indicates that the PCI master module is free to use the Memory Read Line bus command for Burst Read cycles.

- When both PREF\_EN and MRL\_EN bits are set, the bridge will use the Memory Read multiple bus command on the PCI bus.

- > Images mapped to I/O space handle any Read transaction as single Delayed Read cycle (not as Burst Read cycle). If the WISHBONE master attempts to perform a serial Block Read cycle from an I/O space mapped image, the cycle is terminated with an error by the WISHBONE slave module.

- > The bridge core performs pre-fetched Read cycles only through images mapped to memory space. Prefetchable address space is assumed only when the PREF\_EN bit or MRL\_EN bit of the corresponding W\_IMG\_CTRLx register is set, and the WISHBONE master signals a serial Block Read cycle.

Non-prefetchable address space is assumed for the following conditions:

- 1. Accesses to I/O mapped address space are always non-prefetched.

- 2. The WISHBONE master performs a Single or Block Read cycle, or the PREF\_EN bit is cleared.

When the WISHBONE slave unit latches address and SEL(3:0) data of a Read request, the PCI master module requests mastership for the PCI bus. When mastership is granted, the PCI master module initiates a PCI Read transaction. The bus command used for the transaction depends on various parameters described in the following table:

| Address space mapping of image | Cycle initiated by WISHBONE master | PREF_EN bit value | MRL_EN bit value | Bus command used        |

|--------------------------------|------------------------------------|-------------------|------------------|-------------------------|

| I/O                            | Single or Block<br>Read            | X                 | X                | I/O Read                |

| Memory                         | Single or Block<br>Read            | Х                 | Х                | Memory Read             |

|                                | Serial Block<br>Read               | 0                 | 0                | Memory Read             |

|                                |                                    | 0                 | 1                | Memory Read Line        |

|                                |                                    | 1                 | 0                | Memory Read             |

|                                |                                    | 1                 | 1                | Memory Read<br>Multiple |

Table 3-3: Bus command encoding for Read cycles through PCI master module

Read cycles to address space that is not prefechable are performed in one data phase on the PCI bus. Only those byte enables are active on the PCI bus, as SEL(3:0) data were active during the Read request. After the first data phase, the PCI master module releases the PCI bus.

All Delayed Reads from address space marked as prefetchable are performed in Burst Read cycles. Here are all byte enables active on the PCI bus, since PCI bridge can not determine, which bytes are significant for a WB device, that initiated the transaction (SEL(3:0) data were active during the Read request only for first data phase). The PCI master module reads data from the target and puts it into WBR\_FIFO. The PCI master module finishes a Burst Read cycle and releases the PCI bus if any of the following conditions is met:

- 1. WBR\_FIFO is full.

- 2. The target issues **Target Disconnect**.

- 3. The mastership of the PCI bus is revoked by the PCI arbiter (#GNT is de-asserted).

When the WISHBONE master retries this Read transaction, data is ready and the WISHBONE slave module pulls data out of the WBR\_FIFO and provides it on the WISHBONE bus.

Any data left in WBR\_FIFO after the WISHBONE master ends a Read cycle is flushed immediately.

So far, WISHBONE to PCI Read cycles have been described as if always completed successfully, but it is common for PCI bus targets or masters to generate error terminations. Terminations from the PCI bus must be propagated to the WISHBONE bus to let the WISHBONE master know what happened to the transaction it initiated.

The PCI target is capable to operate the following terminations:

- Retry

- > **Disconnect** with data

- Disconnect without data

- Target Abort

The **Retry** termination is not propagated back to the WISHBONE bus. The bridge core simply retries the transaction.

**Disconnect** is a valid termination for Single Read cycles. The PCI master module does not retry these transactions but stores data for Single Read cycles and waits for the WISHBONE master to fetch it.

**Target Abort** is an error signaled to the WISHBONE master. Retrying the transaction, it receives a bus error termination (the WISHBONE slave module asserts ERR\_I).

**Master Abort** is an error termination. The WISHBONE master receives an error when a transaction ends with **Master Abort** on the PCI bus. The only exception to this rule is a Configuration Read cycle, which returns all 0s.

Block Read length can be of Cache Line size or WBR\_FIFO depth. It is the WBR\_FIFO depth if Memory Read Multiple bus command is performed on the PCI bus (see Table 3-3, when this command is performed). But there is NO Block Read if Cache Line size is set to 1 or it is set to unsupported value (valid Cache Line sizes are multiples of 4 - see chapter 4.1.2).

# 3.3 PCI Target Unit

The PCI target unit connects to PCI initiators acting as a target. This section describes the basic functionality of the PCI target unit and is divided into subsections, each of them defining what a PCI initiator needs to do to initiate PCI to WISHBONE transactions.

# 3.3.1 PCI Target Unit Functionality

This part gives a functional overview of the PCI target unit. Detailed description is provided in the following sections.

Figure 3-5: PCI target unit architecture overview

The PCI target unit consists of several functional parts allowing PCI initiators to perform Read/Write access to the WISHBONE bus.

#### 3.3.1.1 PCI Target Module

The PCI target module is a 32-bit/66MHz (33MHz for FPGA implementation) *PCI Local Bus Specification Rev. 2.2* compliant target interface. It handles Read/Write cycles to images of WISHBONE address space and configuration space accesses.

#### 3.3.1.2 PCIW FIFO

The PCI target module uses PCIW\_FIFO (PCI Write FIFO) for posting Memory and I/O Write cycles performed by the PCI initiator. PCIW\_FIFO also performs a different bus clock adaptation.

#### 3.3.1.3 PCIR\_FIFO

The WISHBONE master module uses PCIR\_FIFO (PCI Read FIFO) for storing data read from WISHBONE slaves. PCIR\_FIFO performs a different bus clock adaptation.

#### 3.3.1.4 WISHBONE Master Module

The WISHBONE master module is a 32-bit WISHBONE master interface as defined in WISHBONE Specification Rev. 1B. The core requests the WISHBONE bus through its WISHBONE master module. Chapter 5.2 WISHBONE Interface, describes in detail the WISHBONE interface of the core.

# 3.3.2 Addressing and Images of the PCI Target Unit

As mentioned above, the PCI target unit incorporates 1 to 5 configurable PCI address space images (The *Design Document and Implementation Notes* discuss in detail how to define the number of images) and one special image used for configuration space accesses from the PCI bus with a configurable base address. In host bridge implementations, this special image can be configured to provide access to normal address space or can be canceled – therefore configuration space would not be accessible (see also 3.1.1 Configuration Space Access for Host Bus Bridges and 4.1 Register List and Description).

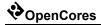

The behavior of each image is controlled by its PCI Base Address (P\_BA0 – P\_BA5), PCI Translation Address (P\_TA0 – P\_TA5), PCI Image Control (P\_IMG\_CTRL0 – P\_IMG\_CTRL5), and PCI Address Mask (P\_AM0 – P\_AM5) registers. Status, errors, and interrupts for each image are recorded in the Status registers described later in this document. The PCI target module claims the

cycle started by the initiator on the PCI bus if one of the PCI images is selected and enabled. An image is enabled if the IMG\_EN bit of its P\_AM register is set to 1. An image is selected when the address provided during the initial cycle on the PCI bus is placed within the memory range of that image. The range is determined with values of P\_BA and P\_AM registers. Each image can represent 4KB to 2GB of the WISHBONE address space.

Each image can be mapped to memory or I/O space, determined by the address space-mapping bit (ASM) of the image's P\_BAx register (bit 0). If the ASM bit is 0, the image maps to memory space, and otherwise to I/O space. For host bridge implementations, the predefined values can later be changed by writing an appropriate value, but for guest bridge implementations, the predefined values are fixed (hardwired), because device independent software must know in advance where to map each PCI Base Address.

How to specify a 1MB image of WISHBONE address space with an address range of 0x10100000 – 0x101FFFFF?

Software must write a value of 0x10100XX0 to the Base Address register of an image (the LSB of this register is set to 0 to indicate memory space mapping). This way, the base address is set at 0x10100000. Twelve LS bits are marked as Don't Cares. The minimum block size is 4KB.Software writes a value of 0xFFF00XXX into the P\_AM register of the corresponding image. The MS bit is the IMG\_EN bit, which is set to a value of 1. It is also used for address masking, i.e. how we limit a maximum image size to 2GB. Each bit in the P\_AM register corresponds to one address line. If the bit is 1, then this address line is used in address comparison, and otherwise it is not. A value of 0xFFF00000 in the P\_AM register means that ADDR\_O(31..20) signals are compared with a P\_BA[31..20] value. If values match, the image is selected. In this case, ADDR\_O(19..0) lines define an offset in an address range of 1MB.

#### **Example 3-3: Address range of WISHBONE slave image**

If address translation is enabled for a selected image (AT\_EN bit of P\_IMG\_CTRLx is 1), it is performed between PCI and WISHBONE address. Address translation is done by replacing the masked part of the PCI address with the corresponding bits from the P\_AT register. This provides very flexible address mapping (off course address translation must be implemented).

Let's assume that base address and address mask are set as described in previous example. We want a PCI address range of 0x10100000 – 0x101FFFFF to be mapped elsewhere on the WISHBONE bus, e.g. at 0x01000000 – 0x010FFFFF. To achieve this, we need a translation of addresses coming from the PCI initiator. The AT\_EN bit of the corresponding IMG\_CTRL register is set to a value of 1 and of the corresponding P\_AT register to a value of 0x01000XXX, respectively. The P\_AM register is already set, so address translation replaces AD(31..20) provided by the PCI initiator with a 0x010 value set in the P\_AT register for accesses on the WISHBONE bus. This way, we have a WISHBONE address range of 0x01000000 – 0x010FFFFF, accessible on the PCI bus in a range of 0x10100000 – 0x101FFFFF.

#### **Example 3-4: Address translation**

# 3.3.3 PCI to WISHBONE Write Cycles

The previous section described how a PCI target unit knows if it is the target of a current cycle initiated by a PCI initiator. In this section, Write accesses are described in detail, assuming that a PCI target unit decodes an address to fall within a range of one of its enabled images.

The PCI target module is capable of handling Single and Burst Write transfers through one of its PCI target images.

#### Note:

Serial block transfers (bursts on the WISHBONE bus) are still under discussion because the WISHBONE Bus Specification does not provide a mechanism to identify them. Until serial block transfers will be specified, all bursts from the PCI bus are handled as Block Write cycles.

All Write cycles from the PCI master to the WISHBONE bus are handled as Posted Writes. Due to this, the Read Modify Write command is not supported on the WISHBONE bus. Write cycles are claimed on the PCI bus immediately after receiving a request and are stored in PCIW\_FIFO. Each image can be mapped to I/O or memory space that is determined by a value of the address spacemapping bit (ASM) in the P\_BAx register of the corresponding image (for guest bridges ASM bit is fixed, for host bridges ASM bit can be changed, see chapter 3.3.2).

If an image maps to I/O space, all 32 AD lines are used for full byte address decoding, and AD(1:0) lines indicate the least significant valid byte for the transaction. The byte enable lines BE#(3:0) indicate the size of the transfer within the DWORD. They must be consistent with AD(1:0) as seen in Table 3-5. All other combinations are invalid. Invalid access is terminated with **Target Abort** on the PCI bus.

All PCI bursts to I/O space are treated as Single Posted Writes; therefore, Burst transfers are broken into single transfers. Their data phase is terminated with **Target Disconnect with Data**. The PCI initiator then attempts to perform the next access with the data following the first transfer. This is repeated until the "burst" transfer has finished.

| Value on AD(1:0) lines | Starting Byte | Valid BE#(3:0) encoding |

|------------------------|---------------|-------------------------|

| 00                     | Byte 0        | xxx0                    |

| 01                     | Byte 1        | xx01                    |

| 10                     | Byte 2        | x011                    |

| 11                     | Byte 3        | 0111                    |

Table 3-4: Valid AD(1:0) and BE# (3:0) combinations for I/O mapped address space accesses

If an image maps to memory space, 30 AD lines (the AD(31:2) bus) provide a DWORD-aligned address. The AD(1:0) lines are not part of the address decoded, but they indicate the order in which the PCI initiator requests data to be transferred, as seen in Table 3-5. The Linear Incrementing Burst mode is fully supported, while the Cache-line Wrap mode is broken into single transfers whose data phase is terminated with **Target Disconnect with Data**. The PCI initiator then attempts to perform

the next access with the data following the first transfer. This is repeated until the Cache-line Wrap mode burst transfer has finished.

| Value on AD(1:0) lines | Burst Ordering encoding                      |  |

|------------------------|----------------------------------------------|--|

| 00                     | Linear Incrementing                          |  |

| 01                     | Reserved (disconnect after first data phase) |  |

| 10                     | Cache-line Wrap mode                         |  |

| 11                     | Reserved (disconnect after first data phase) |  |

Table 3-5: Burst Ordering combinations for memory mapped address space accesses

All other combinations are reserved (because of an earlier version of the *PCI Specification*). Therefore, accesses must be terminated with **Disconnect** after the first data phase, but requested memory address space is not affected. There are additional reasons for the PCI target to terminate a current bus-cycle.

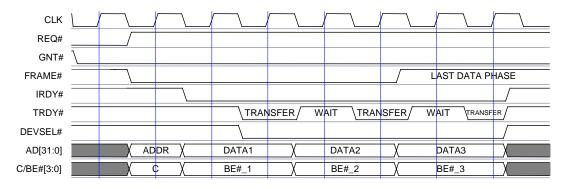

When the PCI target unit is unable to respond within its subsequent latency requirement, it terminates a transfer with **Disconnect with/without Data** while data is being transferred, or immediately afterwards, on the initial data phase. This applies to the following conditions:

- The target is not capable of doing a burst (as mentioned above).

- The target is temporarily unable to continue bursting when PCIW\_FIFO is already fulfilled with the current Burst Write.

The PCI target unit abnormally terminates a transfer with **Target Abort** when it detects a fatal error of the following kind (otherwise it would not be able to complete the requested transfer):

> The master initiates a non-valid combination of AD(1:0) and BE#(3:0) when accessing I/O mapped image space (as mentioned above).

When it is busy and temporarily unable to process the transaction, the PCI target unit terminates a transfer with **Retry** before any data is transferred. This applies to the following situations:

- An internal resource conflict emerges when PCIW\_FIFO is full or cannot provide enough space to accommodate another burst transfer.

- > The target is locked by another master when an uncompleted Delayed Read request is still pending in a PCI target unit (Write cycles cannot be posted until a Read cycle finishes on the WISHBONE bus).

- > The target is locked by WBU, when there is still a WB to PCI delayed read pending or processing.

All PCI bus transfer terminations described above are PCI target terminations, but masters may also terminate transactions.

Regardless whether image mapping occurs to MEMORY or I/O space, the PCI initiator or target can insert wait cycles into the current Write transfer.

The PCI target module must perform address decoding every time the PCI initiator induces a Write transfer in order to determine if this transfer is related to it. The WISHBONE master module

initiates a transaction on the WISHBONE bus after a complete transaction has been stored in the PCIW\_FIFO unit of the PCI target. The module uses Single Write or Block Write transfers, depending on the value of the control bit in the PCIW\_FIFO line that indicates a burst from the PCI bus. Block Write cycles on the WISHBONE bus have the same length as bursts from the PCI. If a burst on the PCI bus was cut because of smaller PCIW\_FIFO depth, the block size is as large as the size of the burst written into the PCIW\_FIFO. When a PCI initiator completes a Burst Write cycle with the next access, it is treated as a new burst transfer written to PCIW\_FIFO.

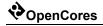

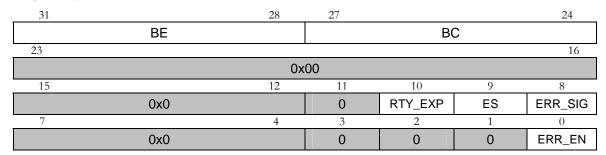

Because all Write cycles are posted and therefore immediately claimed by the PCI Target module and stored to the PCIW\_FIFO, there is an alternate way of communicating errors signaled on a WISHBONE bus when Posted Write cycles actually have been written to their final destination—the mechanism of Error Reporting, which is provided through Error Reporting registers. The error enable bit (ERR\_EN) of the PCI Error Control and Status register (P\_ERR\_CS) must enable this mechanism. If Error Reporting is enabled, errors can generate interrupts when the error interrupt enable bit (EINT\_EN) of the P\_ERR\_CS register is 1. Each Error Reporting register stores part of the information about the Posted Write transaction on the WISHBONE bus that was terminated with an error.

- > A value of 1 in the error signaled bit (ERR\_SIG) of the P\_ERR\_CS register indicates that an error has been recorded. The Field Bus Command (BC) of this register stores the bus command used on the PCI bus for the access that terminated with an error on the WISHBONE bus while the field Byte Enables (BE) stores the value of byte enables (SEL\_O(3:0) lines) during the transfer.

- > P\_ERR\_ADDR stores the 32-bit address the WISHBONE master module tried to access when the error occurred.

- > P\_ERR\_DATA stores the 32 bits of data used in the transfer on the WISHBONE bus that terminated with an error.

Only the Write transaction that generated an error is discarded, any subsequent transactions are processed normally.

# 3.3.4 PCI to WISHBONE Read Cycles

Read cycles induced by the PCI initiator are handled as Single Delayed Read cycles. This explains why the Read Modify Write command on the WISHBONE bus as well as Multiple Delayed Read cycles are not supported. Delayed transactions must be completed on the WISHBONE bus before they can complete on the PCI bus.

Above, the section on addressing and images described how the PCI target unit decodes an address to find out if it is the target for a current cycle. Handling Read transactions is encoded in the PCI Image Control register (P\_IMG\_CTRLx). To define the PCI target unit's behavior towards images mapped to memory space during Read transactions, several options exist:

➣

The PREF\_EN bit indicates that the address range of the PCI memory image is prefetchable, which means that the bridge core can pre-fetch data from the slave and store it in WBR\_FIFO. This method increases system performance since the Delayed Read transaction has information on starting address of the transfer only. Read below Table 3-6 for valid byte enables information.

- > Images mapped to I/O space handle any Read transaction as Single Delayed Read cycle (no bursts). If the PCI initiator attempts a Burst Read cycle from an image mapped to I/O space, the cycle is terminated with **Disconnect with Data**; thus the initiator can continue reading the rest of the data (by disconnecting the bursts).

- > The bridge core performs pre-fetched Reads only through images mapped to memory space. Prefetchable address space is assumed for the following conditions:

- > The PREF\_EN bit of the corresponding P\_IMG\_CTRLx register is set (see Table 3-6).