# PCI IP Core Specification

Authors: Miha Dolenc & Tadej Markovic

mihad@opencores.org

tadej@opencores.org

Rev. 1.2

This page has been intentionally left blank.

## **Revision History**

|     | Date       | Author               | Description                                                                           |

|-----|------------|----------------------|---------------------------------------------------------------------------------------|

| 0.0 | 5/1/01     | Miha Dolenc          | First Draft                                                                           |

|     |            | Tadej Markovic       |                                                                                       |

| 0.1 | 5/8/01     | Miha Dolenc          | Waveforms added for WISHBONE slave                                                    |

|     |            | Tadej Markovic       |                                                                                       |

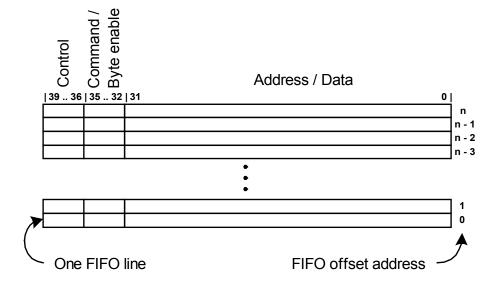

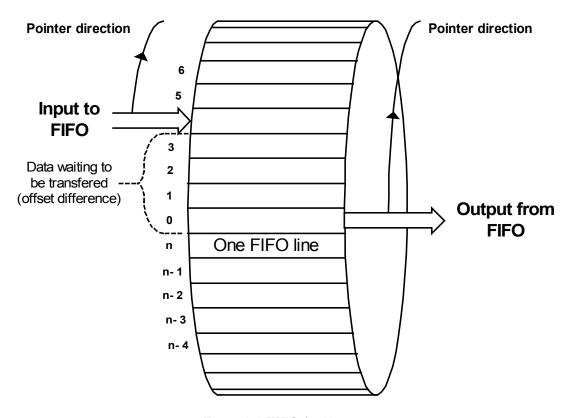

| 0.2 | 5/15/01    | Miha Dolenc          | Detailed description of FIFO added, Operation of                                      |

|     |            | Tadej Markovic       | PCI target unit added, Waveforms added for PCI target                                 |

| 0.3 | 5/22/01    | Miha Dolenc          | FIFO structure changed                                                                |

|     |            | Tadej Markovic       |                                                                                       |

| 0.4 | 10/13/01   | Jeanne<br>Wiegelmann | First review                                                                          |

| 0.5 | 10/20/01   | Miha Dolenc          | Updated register descriptions and Configuration                                       |

|     |            | Tadej Markovic       | Space access                                                                          |

| 0.6 | 01/28/02   | Miha Dolenc          | Updated descriptions and added Software                                               |

|     |            | Tadej Markovic       | obligations                                                                           |

| 8.0 | 12/09/03   | Miha Dolenc          | Added new defines descriptions. Added WISHBONE Slave B3 description.                  |

| 1.0 | 12/10/2003 | Miha Dolenc          | Moved and updated Software Obligations to Initialization and reconfiguration chapter. |

| 1.1 | 12/11/2003 | Miha Dolenc          | Added CompactPCI Hot Swap support descriptions.                                       |

| 1.2 | 01/09/2004 | Miha Dolenc          | Added Serial Power On Configuration interface description.                            |

## **List of Contents**

| INTRODUCTION                                    | 1                                      |

|-------------------------------------------------|----------------------------------------|

| 1.1. WHAT IS A PCI BRIDGE?                      |                                        |

|                                                 |                                        |

|                                                 |                                        |

|                                                 |                                        |

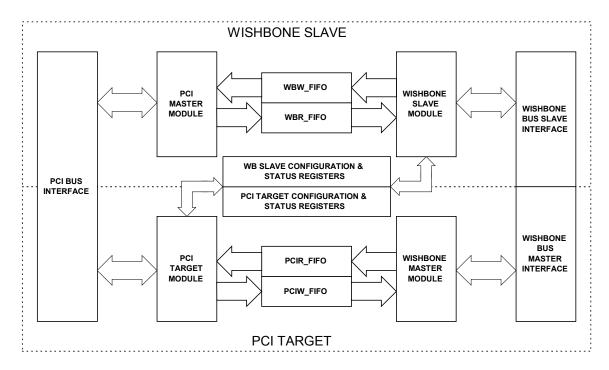

| ARCHITECTURE                                    | 3                                      |

|                                                 |                                        |

|                                                 | 4                                      |

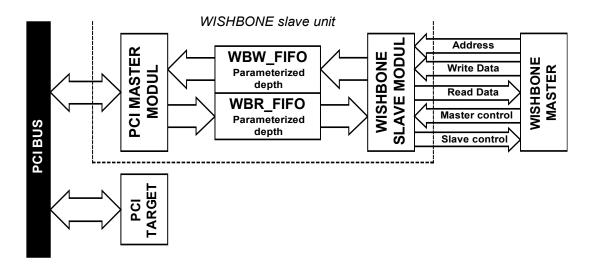

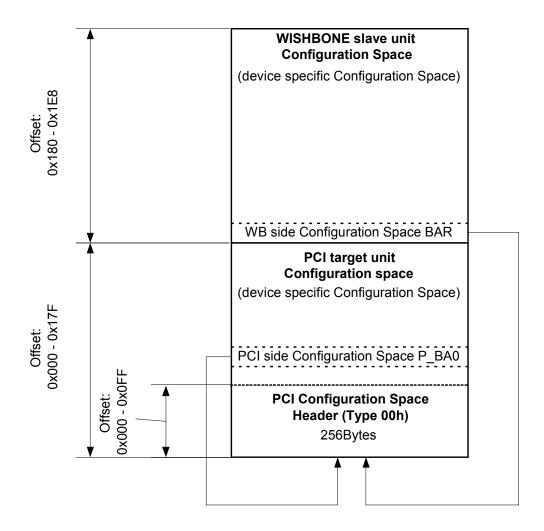

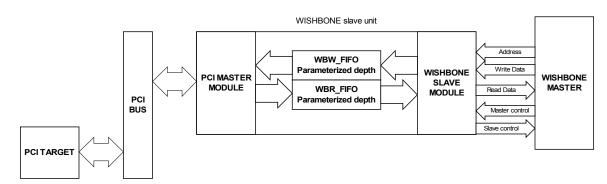

| 2.2.1. WISHBONE Slave Unit Architecture         | 5                                      |

| 2.2.1.1 WISHBONE Slave Module                   | 5                                      |

| <del>=</del>                                    | 5                                      |

|                                                 | 6                                      |

|                                                 | 6                                      |

|                                                 |                                        |

|                                                 |                                        |

|                                                 |                                        |

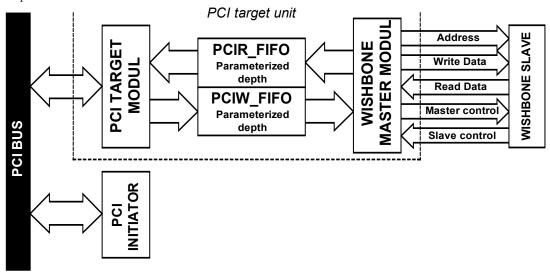

| <del>=</del>                                    | 7                                      |

|                                                 | 8                                      |

|                                                 |                                        |

|                                                 |                                        |

|                                                 | 9                                      |

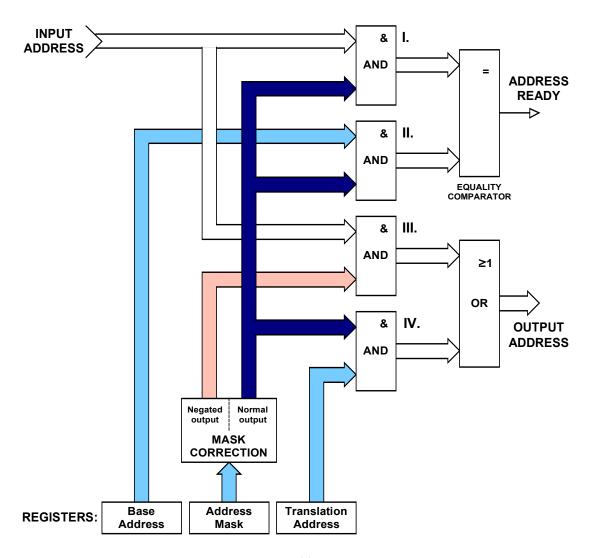

| 2.6.1. Description of Address Translation Logic |                                        |

| OPERATION                                       |                                        |

| 3.1. Initialization                             |                                        |

|                                                 | n                                      |

|                                                 |                                        |

|                                                 | mode                                   |

|                                                 |                                        |

|                                                 | Bridges                                |

|                                                 |                                        |

|                                                 | dges                                   |

|                                                 | Error! Bookmark not defined.           |

|                                                 |                                        |

|                                                 |                                        |

|                                                 |                                        |

|                                                 |                                        |

|                                                 |                                        |

|                                                 |                                        |

| <u>=</u>                                        |                                        |

| 3.3.2. Addressing and Images of the WISHBOI     | NE Slave Unit 22                       |

|                                                 |                                        |

|                                                 |                                        |

|                                                 | B3 supportError! Bookmark not defined. |

|                                                 |                                        |

|                                                 |                                        |

| Ŭ Ž                                             |                                        |

|                                                 |                                        |

|                                                 |                                        |

| 2.44.4 WIGHDONE M. 35.11                        | 20                                     |

| 3.4.2.   | Addressing and Images of the PCI Target Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.4.3.   | PCI to WISHBONE Write Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30 |

| 3.4.4.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 3.4.5.   | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 3.5.     | TRANSACTION ORDERING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 3.6.     | PCI BUS PARITY GENERATION AND CHECKING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 36 |

| 3.7.     | INTERRUPTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| 3.8.     | COMPACT PCI HOT SWAP SUPPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 3.8.1.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 3.8.2.   | I = I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| 3.8.3.   | I = J                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| 3.8.4.   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 3.8.5.   | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 3.8.6.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 3.9.     | SERIAL POWER ON CONFIGURATION INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 3.9.1.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 3.9.2.   | 78 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 3.9.3.   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 3.9.4.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 3.9.5.   | Initiating EPROM Byte Read Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

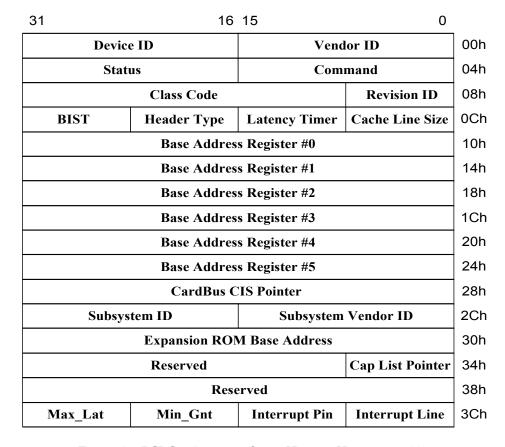

| REGISTE  | RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50 |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 4.1.     | REGISTER LIST AND DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| 4.1.1.   | // -0 0- ( 0 m// 0 |    |

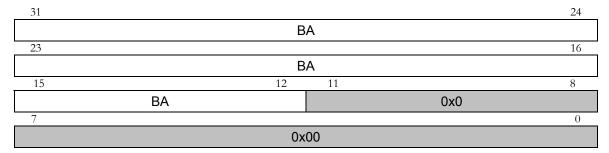

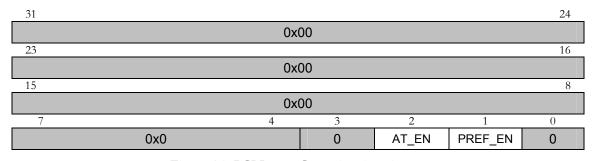

|          | <ul> <li>.1.1 WISHBONE Configuration Space BAR.</li> <li>.1.2 WISHBONE Image Control and Address Registers.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 4.1.2.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|          | 2.1 PCI Image Control and Address Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 4.1.3.   | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|          | .3.1 WISHBONE Slave Unit Error Reporting Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|          | .3.2 PCI Target Unit Error Reporting Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

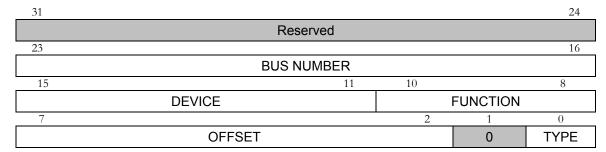

| 4.1      | .3.3 Configuration Cycle Generation Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| 4.1      | .3.4 Interrupt Acknowledge Cycle Generation Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 4.1.4.   | Interrupt Control & Status Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72 |

| IO PORTS | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 76 |