1.2V, 2.5V y 3.3V arranque. Los voltajes utilizados por la FPGA son de tres valores de tensión y distintas características de conmutadas. Permite suministrar energia regulada con La placa S3Power tiene una fuente lineal y dos fuentes

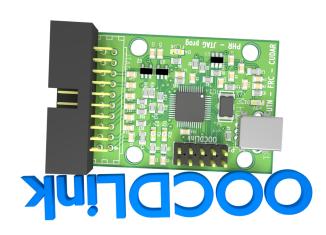

.DATL natroque sup sovitisoqsib s la FPCA y posibilita la interacción con los multiples principal, hace que su utilización no quede restringida tica modular, o de circuito separado de la placa PHR entre una computadora y la placa PHR. Su caracterís-Esta placa es la interfaz que permite la comunicación

- nológicas hacia las PyMEs argentinas. ■ Dinamizar la transferencia de las innovaciones tec-

- Divulgar y difundir los resultados de los trabajos

- de investigación y desarrollo.

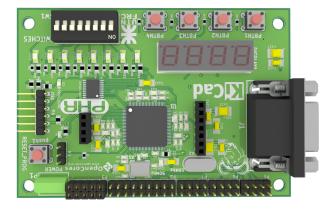

## Proyecto PHR

Lógicos Programables (PLDs). ca relacionado al área digital a través de Dispositivos académicos para la difusión y actualización tecnológitiene como objetivo principal desarrollar recursos El proyecto Plataforma de Hardware Reconfigurable

ware que se publican bajo licencias libres. El desarrollo comprende el diseño de hardware y soft-

cuales la placa principal carece de funcionalidad. conectores especiales para otros dos módulos sin los DIP, Displays de siete segmentos), etc. Además tiene y salidas, periféricos (tales como LEDs, botones, llaves cuentran el chip FPGA, relojes, interfaces de entradas físico. El módulo principal es la placa PHR donde se en-Oonsiste fundamentalmente en tres mòdulos de soporte

## Mas información

encuentran en el sitio web: Todos los documentos y fuentes de este proyecto se

http://opencores.org/project,phr

## Hardware libre

tamaños y otra información acerca del hardware. el lanzamiento de los diagramas esquemáticos, diseños, mación con respecto al hardware, a menudo incluyendo libre con el hardware y el lanzamiento libre de la inforesado principalmente para reflejar el uso del software El término hardware libre se ha

Property cores, o núcleos IP. se distribuyen, son Ilamados semiconductor intellectual tamente en diseños ASIC. Los módulos HDL, cuando mente para instalar sistemas SoC en FPGA o direccompartido. Las descripciones HDL son usadas comúnpartir los diagramas esquemáticos, el código HDL es bién una práctica de hardware libre. En vez de comreconfigurables, el compartir los diseños lógicos es tam-Con el auge de los dispositivos de lógica programable

## Objetivos del CUDAR

- zación de sistemas y/o procesos. to en las áreas que utilizan o involucran automati-Propender al desarrollo sistemático del conocimien-

- simulación de procesos automáticos. putacionales para el cálculo, emulación, solución y Utilizar, obtener y desarrollar herramientas com-

- nente capacitación. Formar recursos humanos mediante una perma-

- fabricación. y operar sistemas automatizados-robotizados de la ingeniería necesaria para proyectar, diseñar científicos-tecnológicos con el fin de obtener Promover las investigaciones y desarrollos