# Plataforma de Hardware Reconfigurable

### Manual de usuario

Documento versión BETA20140314 Marzo de 2014

Centro Universitario de Desarrollo en Automación y Robótica

Universidad Tecnológica Nacional Facultad Regional Córdoba Este documento se trata de una guia de usuario sobre la *Plataforma de Hardware Reconfigurable* desarrollada en el *CUDAR*, *Centro Universitario de Desarrollo en Automación y Robótica*, en la *Universidad Tecnológica Nacional*, *Facultad Regional Córdoba*.

```

<contacto>

<integrantes del proyecto>

<etc>

```

#### **Notas**

Hace falta prefacio ¿? software para programacion¿? El/La FPGA ¿?

#### Historial del documento

BETA20140313 Correcciones en general (maximiq)

```

BETA20140214 Trabajando sobre el estilo del documento. (maximiq)

BETA20140214 Trabajando sobre el estilo y estructuracion del documento. (maximiq)

BETA20140218 Algunas imagenes creadas y añadidas (maximiq)

BETA20140219 Más imagenes creadas y añadidas (maximiq)

BETA20140222 Trabajando en la sección perifericos (maximiq)

BETA20140223 Trabajando en la sección periféricos (maximiq)

BETA20140224 Sección perifericos lista para corrección (maximiq)

BETA20140225 Capitulo s3power actualizado (maximiq)

BETA20140305 Correcciones (maximiq)

BETA20140310 Mas imagenes (maximiq)

```

# Tabla de contenidos

| Pr  | refacio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                |  |  |  |  |  |  |  |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 1.  | Descripción general1.1. Características1.2. Descripción de las placas1.3. Diagrama de bloques del hardware1.4. Componentes de la placa principal                                                                                                                                                                                                                                                                                                                                                                                | 1<br>1<br>1<br>1<br>1                                          |  |  |  |  |  |  |  |  |

| 2.  | La placa PHR  2.1. El chip FPGA  2.1.1. Características principales  2.1.2. Descripción de la arquitectura  2.1.3. Capacidades de E/S  2.1.4. Requerimientos de alimentación  2.2. Configuración de la FPGA  2.2.1. Memoria PROM  2.2.2. Interfaz JTAG  2.3. Fuentes de clock  2.3.1. El reloj de 50 MHz  2.3.2. Relojes seleccionables  2.4. Periféricos  2.4.1. LEDs  2.4.2. Pulsadores (Tact switches)  2.4.3. Llaves DIP  2.4.4. Displays de 7 segmentos  2.4.5. Puerto serie  2.5. Entradas y salidas de propósito general | 44<br>44<br>44<br>55<br>66<br>67<br>77<br>77<br>88<br>89<br>10 |  |  |  |  |  |  |  |  |

| 3.  | La placa OOCDLink 3.1. El chip FT2232D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>13</b>                                                      |  |  |  |  |  |  |  |  |

| 4.  | <b>La placa S3Power</b> 4.1. El chip TPS75003                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>14</b><br>14                                                |  |  |  |  |  |  |  |  |

| Α.  | Conexiones de la FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16                                                             |  |  |  |  |  |  |  |  |

| В.  | Esquemáticos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17                                                             |  |  |  |  |  |  |  |  |

| Bil | bliografía                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | oliografía 19                                                  |  |  |  |  |  |  |  |  |

# Índice de figuras

| 1.1.  | Conexionado de las placas                         | 2  |

|-------|---------------------------------------------------|----|

| 1.2.  | bloques                                           | 2  |

| 1.3.  | Componentes de la placa PHR                       | 3  |

| 2.1.  | Bloques fundamentaled de la FOGA                  | 5  |

| 2.2.  | Esquematico conf modes                            | 7  |

| 2.3.  | Selectores para los relojes                       | 7  |

| 2.4.  | Selectores para los relojes                       | 8  |

| 2.5.  | Tact switches                                     | 8  |

| 2.6.  | DIP switches                                      | 9  |

| 2.7.  | Circuito del display de siete segmentos           | 9  |

| 2.8.  | Diagrama temporal de la multiplexación            | 10 |

| 2.9.  | Caracteres comunes en los displays de 7 segmentos | 10 |

| 2.10. | Circuito de la interfaz RS-232                    | 11 |

| 2.11. | Conectores de propósito general                   | 11 |

| 3.1.  | Componentes de la placa OOCDLink                  | ١3 |

|       | Componentes de la placa S3Power                   |    |

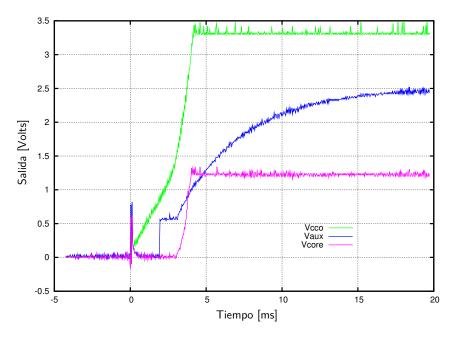

| 4.2.  | Arranque de la placa S3Power                      | 5۔ |

# Índice de tablas

| 2.1.  | Voltajes de alimentación              | 6 |

|-------|---------------------------------------|---|

| 2.2.  | Rampas de las fuentes de alimentación | 6 |

| 2.3.  | Seteo de los modos de configuración   | 6 |

| 2.4.  | Pines para los relojes                | 7 |

| 2.5.  | Pines para los LEDs                   | 8 |

| 2.6.  | Pines para los tact switches          | 8 |

| 2.7.  | Pines para las llavess                | 9 |

| 2.8.  | Pines para el diplay de segmentos     | 0 |

| 2.9.  | Pines para la conexión RS-232         | 0 |

| 2.10. | Pines para las <i>GPIO</i>            | 2 |

# Prefacio

# 1. Descripción general

#### **Características**

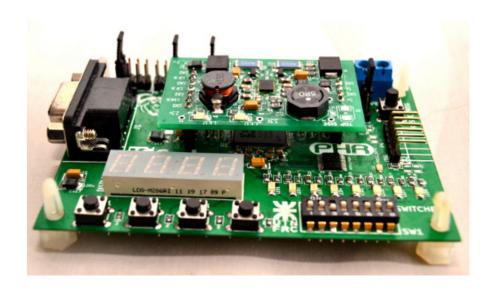

Entre las características de la placa PHR se pueden destacar:

FPGA: Xilinx Spartan-3A XC3S200A (encapsulado VQG100).

PROM: Xilinx XCF02S.

Proposito general io (corrientes)

Conector Modulos expansion

Voltaje de operación

Voltaje de entrada (recomendado): xV - yV.

Voltaje de entrada (limite): xV - yV.

Corriente de entrada [...]

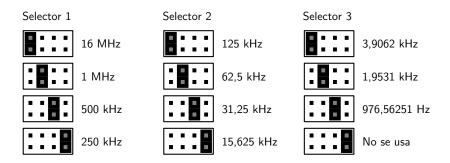

Relojes: 4 relojes en total:

**Clock 0:** 50 MHz.

Clock 1: Seleccionable entre 16 MHz, 1 MHz, 500 kHz y 250 kHz.

Clock 2: Seleccionable entre 125 kHz, 62.5 kHz, 31.25 kHz, 15.625 kHz.

Clock 3: Seleccionable entre 3.91 kHz, 1.95 kHz, 977 Hz.

Multiplicidad de periféricos:

- 8 LEDs.

- 8 llaves (DIP switch).

- 4 pulsadores.

- Displays.

- Puerto serie.

### Descripción de las placas

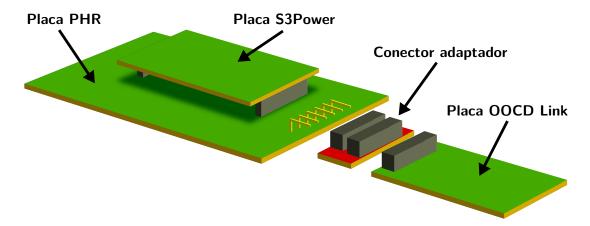

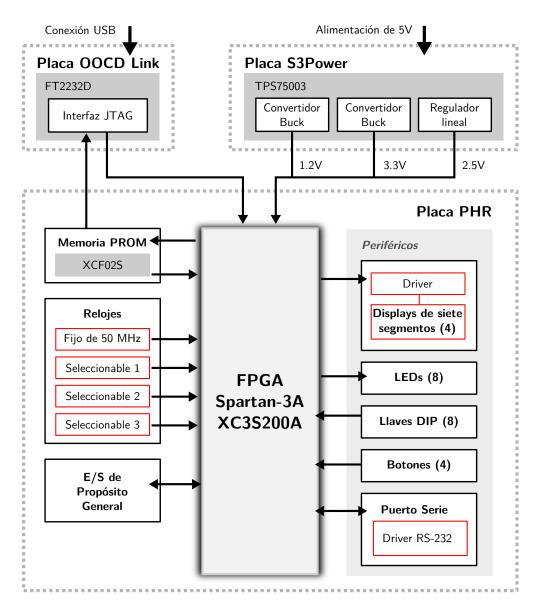

La *Plataforma de Hardware Reconfigurable* consiste fundamentalmente en tres módulos. El módulo principal es la *placa PHR* donde se encuentran el chip FPGA *Spartan-3A* XC3S200A, relojes, interfaces de entradas y salidas, periféricos (tales como LEDs, botones, llaves DIP, Displays de siete segmentos), etc.

Además tiene conectores especiales para los otros dos módulos sin los cuales la placa principal carece de funcionalidad. Uno de los módulos sirve para la regulación de las tensiones que proveen de energía al resto de los dispositivos. Se encuentra en la placa denominada *S3Power*. El otro módulo es necesario para configurar la FPGA o escribir la PROM de configuración y se dispone en la *placa OOCD Link*. La conexión de ambas placas a la placa principal se ilustra en la Fig. 1.1.

La placa S3Power se acopla usando los conectores que se indican con los números 8 y 16 en la Fig. 1.3. Una explicación mas detallada de ésta placa puede consultarse en el capítulo XX.

La placa OOCD Link se une a la principal con el conector demarcado con 7 en la Fig. 1.3. A diferencia de la S3Power, no precisa estar siempre conectada, pero si cada ves que se desee configurar la FPGA o grabar su PROM. Sobre el proceso de configuración refiérase a XX y para conocer mas sobre la placa OOCD Link consulte el capítulo XX.

### Diagrama de bloques del hardware

### Componentes de la placa principal

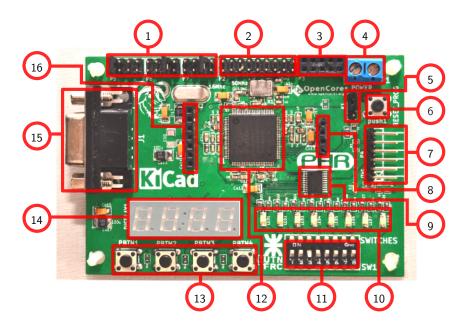

En la Fig. 1.3 se tiene la vista superior de la placa PHR con sus principales componentes demarcados. Según la numeración, éstos componentes son:

Figura 1.1: Conexionado de la placa PHR con las placas auxiliares.

Figura 1.2: bloques.

- 1. Selector de *clock*.

- 2. E/S de propósito general.

- 3. Conector de módulos externos.

Figura 1.3: Componentes de la placa PHR

- 4. Entrada de voltaje de alimentación (5V).

- 5. Selector de modo de configuración.

- 6. Boton de RESET.

- 7. Conector de la plaqueta OOCDLink.

- 8. Alimentación de la placa S3Power.

- 9. Memoria PROM.

- 10. LEDs.

- 11. Llaves DIP.

- 12. FPGA Xilinx Spartan-3A XC3S200A.

- 13. Botones pulsadores.

- 14. Display de 7 segmentos cuádruple.

- 15. Conector para puerto serie.

- 16. Voltajes de alimentación para la FPGA.

# 2. La placa PHR

#### El chip FPGA

#### Características principales

■ Número de compuertas: 200K

■ Celdas lógicas equivalentes: 4032

■ CLBs: 448 (distribuidos en 32 filas y 16 columnas)

bits de RAM distribuida: 28K

bits de Bloques de RAM: 288K

Multiplicadores dedicados: 16

DCMs: 4

• Maximo numero de I/O = 248

■ I/O ppares diferenciales maximo: 112

#### Descripción de la arquitectura

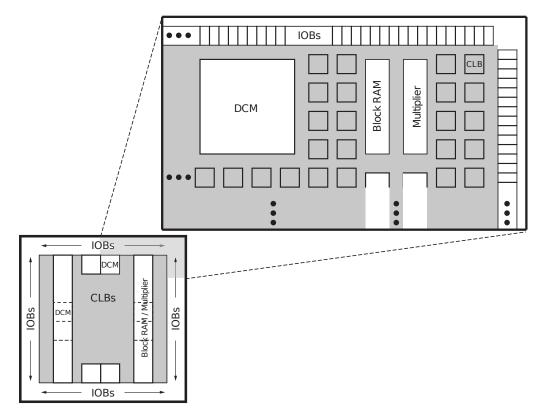

La familia Spartan-3A tiene cinco bloques fundamentales a tener en cuenta respecto de la arquitectura:

**Bloques Lógicos Configurables (CLBs)** contienen *Look-Up Tables* (LUTs) que implementan funciones lógicas y además sirven como elementos de almacenamiento.

**Bloques de Entrada/Salida (IOBs)** controlan el flujo de datos entre los pines de E/S y la lógica interena del dispositivo. Los IOBs soportan datos en forma bidireccional además de la opercion 3-state.

**Bloque de RAM** sirve como forma de almacenamiento.

**Bloques multiplicadores** aceptan como entrada dos numeros de 18 bits cada uno y calcula el producto entre ambos.

**Bloque DCM** (*Digital Clock Manager*) tiene la capacidad para distribuir, retardar, multiplicar, dividir y desplazar en fase las señales de clock.

Para el caso del chip XC3S200A, la Fig. 2.1 muestra la organizacion de éstos bloques fundamentales dentro del dipositivo. Los IOBs se ubican alrededor de la matriz de CLBs. Los bloques de memoria RAM se encuentran en dos columnas, en cada una se disponen varios bloques de RAM de 18 Kbit asociados con un multiplicador dedicado. Dos DCM se ubican en el centro hacia arriba y otros dos en el centro hacia abajo.,

#### Capacidades de E/S

La familia Spartan-3A soporta varios estandares para sus entradas y salidas.

Para el caso de terminaciones simples éstas FPGAs cumplen con:

- TTL de 3.3V (LVTTL).

- CMOS de bajo voltaje (LVCMOS) en tensiones de 3.3V, 2.5V, 1.8V, 1.5V o 1.2V.

- PCI de 3.3V a frecuencias de 33MHz o 66MHz.

- HSTL I, II y III a 1.5V y 1.8V (comunmente usado en memorias).

- SSTL I y II a 1.8V, 2.5V y 3.3V (comunmente usado en memorias).

Los estándares con terminacion diferencial que soportan son:

- Entradas/Salidas LVDS, mini-LVDS, RSDS y PPDS a 2.5V o 3.3V.

- Bus LVDS a 2.5V.

- TMDS a 3.3V.

- HSTL y SSTL diferenciales.

Figura 2.1: Bloques fundamentaled de la FPGA.

■ Entradas LVPECL a 2.5V y 3.3V.

#### Requerimientos de alimentación

El chip XC3S200A tiene varias entradas de alimentación que se describen de manera sucinta en la Tabla 2.1. La FPGA cuenta con un circuito especializado de *Power-On Reset* (POR) que controla tres tensiones de alimentación (VCCINT, VCCAUX y VCCO2) y mantiene al chip en estado de reset hasta que se alcanzan los niveles seguros de trabajo para proseguir con la carga del sistema.

A diferencia de otras FPGAs, la XC3S200A no tiene requerimientos respecto de la secuencia en se deben activar las fuentes de alimentación, pero si respecto de la pendiente de arranque. Los tiempos de pendiente recomendados se muestran en la Tabla 2.2.

Para mas información referida al sistema de alimentación ver el capitulo 4 en la pág. 14.

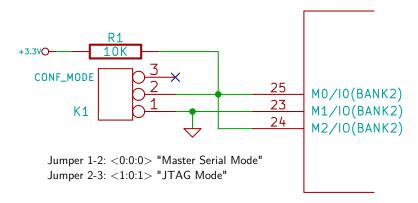

### Configuración de la FPGA

La FPGA al inicializarse no contiene dato alguno y para que pase a trabajar como lo desea el usuario debe que pasar por el proceso de configuración. Los datos se cargan desde el exterior en latches de configuración CMOS (CCLs según las iniciales en inglés) y usando alguno de los siguientes siete modos:

- Master Serial desde una memoria PROM Flash de Xilinx.

- Serial Peripheral Interface (SPI) desde una memoria FLlash SPI.

- Byte Peripheral Interface (BPI) desde una memoria NOR Flash.

- Slave Serial, tipicamente cargada desde un procesador.

- Slave Parallel, tipicamente cargada desde un procesador.

- Boundary Scan (JTAG), tipicamente cargada desde un procesador.

- MultiBoot configuration.

| Entrada | Descripción                                         | Tensión nominal                 |

|---------|-----------------------------------------------------|---------------------------------|

| VCCINT  | Es la tensión de alimentación del núcleo interno.   | 1.2V                            |

|         | Alimenta las funciones lógicas internas como los    |                                 |

|         | CLBs (Bloques Lógicos Configurables) y los blo-     |                                 |

|         | ques de RAM.                                        |                                 |

| VCCAUX  | Fuente de tensión auxiliar. Alimenta elementos      | 2.5V o 3.3V                     |

|         | tales como los DCMs (Digital Clock Managers),       |                                 |

|         | drivers diferenciales, pines de configuración dedi- |                                 |

|         | cados y la interfaz JTAG.                           |                                 |

| VCC00   | Alimenta los buffers de salida del Banco de $E/S$   | Seleccionable entre 3.3V, 3.0V, |

|         | número 0.                                           | 2.5V, 1.8V, 1.5V y 1.2V.        |

| VCCO1   | Alimenta los buffers de salida del Banco de $E/S$   | Seleccionable entre 3.3V, 3.0V, |

|         | número 1.                                           | 2.5V, 1.8V, 1.5V y 1.2V.        |

| VCCO2   | Alimenta los buffers de salida del Banco de $E/S$   | Seleccionable entre 3.3V, 3.0V, |

|         | número 2.                                           | 2.5V, 1.8V, 1.5V y 1.2V.        |

| VCCO3   | Alimenta los buffers de salida del Banco de $E/S$   | Seleccionable entre 3.3V, 3.0V, |

|         | número 3.                                           | 2.5V, 1.8V, 1.5V y 1.2V.        |

Tabla 2.1: Voltajes de alimentación para la familia Spartan-3A.

| Símbolo | Descripción                        | Min    | Max    |

|---------|------------------------------------|--------|--------|

| VCCINTR | Rampa desde GND a VCCINT           | 0.2 ms | 100 ms |

| VCCAUXR | Rampa desde GND a VCCAUX           | 0.2 ms | 100 ms |

| VCCO2R  | Rampa desde GND a VCCO del Banco 2 | 0.2 ms | 100 ms |

Tabla 2.2: Tiempos de subida para las rampas al encender las fuentes de alimentación.

| Pines M[2:0] | Modo                                |

|--------------|-------------------------------------|

| <0:0:0>      | Modo Master Serial (Platform Flash) |

| <0:0:1>      | Modo <i>Master SPI</i>              |

| <0:1:0>      | BPI Up                              |

| <0:1:1>      | Reservado                           |

| <1:0:0>      | Reservado                           |

| <1:0:1>      | Modo JTAG                           |

| <1:1:0>      | Modo <i>Slave Parallel</i>          |

| <1:1:1>      | Modo <i>Slave Serial</i>            |

Tabla 2.3: Seteo de los modos de configuración para la familia Spartan-3A.

#### Memoria PROM

#### Interfaz JTAG

#### Fuentes de clock

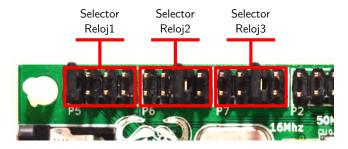

La placa PHR provee a la FPGA de cuatro fuentes de reloj. El más rápido de los relojes oscila a una frecuencia de 50 MHz, mientras que los otros tres relojes mas lentos tienen una frecuencia seleccionable por usuario. En la Fig. 1.3 se indican con el numero 1 los jumpers con los cuales se eligen las frecuencias para éstos relojes.

Los pines de la FPGA a los cuales se asignan cada clock se muestran en la Tabla 2.4. Éstos son pines de *Global Clock* que están especialmente diseñados para tratar señales de alta frecuencia. Proveen una capacidad muy baja y un retardo uniforme para cada bloque dentro del chip.

Figura 2.2: Conf modes.

| <b>Reloj</b> Fijo (50 MHz) |    | Seleccionable 1 | Seleccionable 2 | Seleccionable 3 |  |

|----------------------------|----|-----------------|-----------------|-----------------|--|

| Pin                        | 43 | 44              | 41              | 40              |  |

Tabla 2.4: Pines para los relojes.

#### El reloj de 50 MHz

Ésta frecuencia se genera con el dispositivo ACOL-50MHZ-EK, que tiene un oscilador a cristal y encuentra aplicaciones en chips digitales y microprocesadores. Se alimenta con un bajo nivel de tensión (3.3V) y su salida es compatible con HCMOS y TTL.

#### Relojes seleccionables

Los pines para selección de los relojes se muestran en la Fig. 2.3. En los primeros dos relojes se puede elegir una de entre cuatro frecuencias mientras que para el tercer reloj se puede elegir una de entre tres frecuencias.

Figura 2.3: Selectores para los relojes.

El conexionado de los jumpers para los clocks se muestra junto con las posibles frecuencias seleccionables en la Fig. 2.4.

El oscilador se basa en un cristal y el chip contador MC74HC4060A. Una frecuencia principal de 16 MHz es dividida en dos sucesivamente por el contador para obtener todas las frecuencias seleccionables.

#### **Periféricos**

#### **LEDs**

En la placa se encuentran ocho LEDs de montaje superficial indicados con el numero 10 en la Fig. 1.3. Son etiquetados desde LED1 a LED8 y su relación con los pines de la FPGA se muestra en

Figura 2.4: Selectores para los relojes.

la Tabla 2.5.

| Periférico | LED1 | LED2 | LED3 | LED4 | LED5 | LED6 | LED7 | LED8 |

|------------|------|------|------|------|------|------|------|------|

| Pin        | 84   | 86   | 89   | 93   | 98   | 3    | 5    | 7    |

Tabla 2.5: Correspondencia entre los pines de la FPGA y los LEDs (periféricos).

Los cátodos de cada LED se conectan a potencial cero y los ánodos se conectan a los pines respectivos de la FPGA mediante un resistencia de 330  $\Omega$ . Para enecender un determinado LED basta con poner en alto la señal de control.

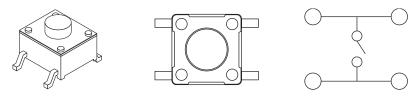

#### Pulsadores (*Tact switches*)

Están disponibles cuatro botones pulsadores como los esquematizados en la Fig. 2.5 y son identificados con el numero 13 en la Fig. 1.3. Los mismos son etiquetados como PBTN1, PBTN2, PBTN3 y PBTN4. Los pines de la FPGA relacionados con éstos periféricos se identifican en la Tabla 2.6. El esquemático detallado del circuito puede encontrarse en el Apéndice B.

Figura 2.5: Tact switches.

| Periférico | PBTN1 | PBTN2 | PBTN3 | PBTN4 |

|------------|-------|-------|-------|-------|

| Pin        | 77    | 78    | 82    | 83    |

Tabla 2.6: Correspondencia entre los pines de la FPGA y los botones.

Cuando se presiona alguno de los botones se genera un valor lógico alto en el pin asociado de la FPGA. No hay circuito antirrebote y ésto debe ser tenido en cuenta al momento de escribir el código que luego vaya a cargarse en el dispositivo.

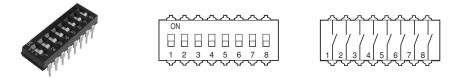

#### Llaves DIP

Alternativamente a los pulsadores se puede optar como periféricos de entrada a unas llaves DIP como se muestran en la Fig. 2.6. La ubicación de las llaves en la placa PHR se muestra con el índice numero 11 en la Fig. 1.3. El circuito de éstas llaves puede consultarse en el Apéndice B y los pines de la FPGA que los controlan se revelan en la Tabla 2.7.

Cuando una llave se coloca en la posición de *encendido*, el pin de la FPGA correspondiente se pone a un valor lógico *alto*. En contraposición, si la llave se coloca en la posicion *apagado*, la FPGA

| Periférico | SW1 | SW2 | SW3 | SW4 | SW5 | SW6 | SW7 | SW8 |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Pin        | 85  | 88  | 90  | 94  | 97  | 4   | 6   | 9   |

Tabla 2.7: Correspondencia entre los pines de la FPGA y las llaves.

leerá un valor lógico bajo. Al igual que con el caso de los botones pulsadores, no se provee un circuito antirrebote, y debe ser tenido en cuenta en el diseño del sistema.

Figura 2.6: DIP switches.

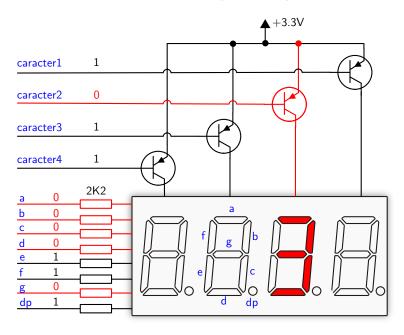

#### Displays de 7 segmentos

La placa PHR cuenta con un display de siete segmentos cuádruple de *ánado comun* indicado con el índice 14 en la Fig. 1.3. El circuito de conexión entre la FPGA y el display se muestra en la Fig. 2.7 y se resalta la denominación alfabética para los segmentos de cada display.

Ésta misma figura además muestra como ejemplo, el estado de los pines de la FPGA para indicar el numero 3 en la posición 2. Al tener ésta configuración, cada LED encenderá con un *nivel bajo* en el pin correspondiente al segmento pero además necesitará que el ánodo del caracter particular esté energizado. Éste ultimo también es activo por bajo (*active low*).

Figura 2.7: Conexionado del display de siete segmentos cuádruple.

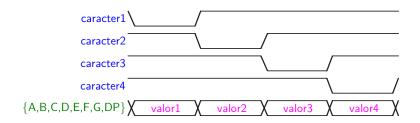

Para dar el efecto deseado de representar cuatro caracteres distintos a la vez, se recurre a la técnica de multiplexación en el dominio del tiempo. La técnica consiste en mostrar uno a uno y ciclicamente cada caracter a una frecuencia lo suficientemente alta para que el ojo humano persiva una imagen completa. Un diagrama temporal de las señales se muestra en la Fig. 2.8.

Si bien el método requiere algo mas de complejidad que la conexion directa a cada segmento de cada display, reduce el numero de pines necesarios de  $8\times 4=32$  a 8+4=12 lo cuál representa un significativo ahorro en recursos de hardware.

Figura 2.8: Diagrama temporal de la multiplexación.

La Tabla 2.8 muestra los pines de conexión de la FPGA a las distintas entradas del periférico. La Fig 2.9 muestra las representaciones de los caracteres comunes en los displays de siete segmentos. Además de los dígitos, se pueden utilizar los caracteres desde la A a la F para representar numeros en notación hexadecimal.

| Pe  | Periférico Car |  | racter1 |    | Caracter2 |    | Caracter3 |    | 3 C | Caracter4 |  |

|-----|----------------|--|---------|----|-----------|----|-----------|----|-----|-----------|--|

|     | Pin            |  | 59      |    | 57        | 7  |           | 61 |     | 60        |  |

|     | Segmento       |  | Α       | В  | С         | D  | Е         | F  | G   | DP        |  |

| Pin |                |  | 65      | 64 | 72        | 70 | 68        | 62 | 73  | 71        |  |

Tabla 2.8: Conexionado del diplay de 7 segmentos cuádruple a la FPGA.

Figura 2.9: Representación de caracteres comunes en los displays de siete segmentos.

#### Puerto serie

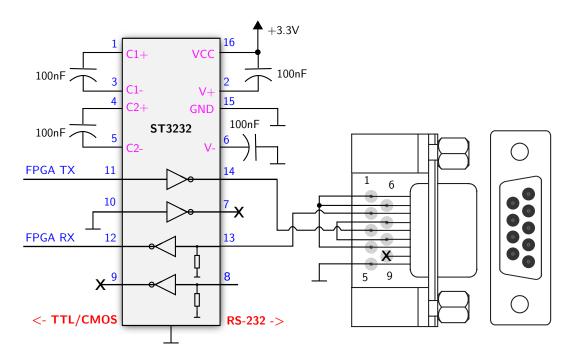

La placa PHR dispone de un puerto serial RS-232. El conector DB9 hembra/macho se señala con el numero 15 en la Fig. 1.3. La placa representa un *Data Communications Equipment* (DCE) y se puede conectar a una computadora personal con un cable serial derecho.

La Fig. 2.10 muestra el circuito de la interfaz entre la FPGA y el conector DB9. Un chip (ST3232) permite una alimentación de entre 3V y 5.5V y utiliza un conjunto de capacitores para alcanzar los niveles de tensión RS-232, garantizando tasas de transferencia de hasta 250 kbps.

El control de flujo por hardware está desabilitado. Las lineas de DCD, DTR y DSR se conectan entre sí. Analogamente para las señales RTS y CTS.

Los pines de la FPGA que controlan las señales seriales se muestran en la Tabla 2.9.

| Señal serial   | RX | TX |

|----------------|----|----|

| Pin en la FPGA | 52 | 56 |

Tabla 2.9: Correspondencia entre los pines de la FPGA y el puerto serie RS-232.

Figura 2.10: Circuito de la interfaz RS-232.

#### Entradas y salidas de propósito general

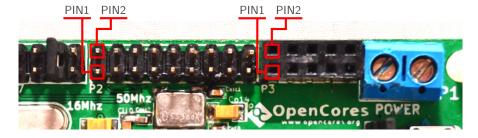

Para que el usuario realice prototipos, use placas de expansión de terceros o diseñe sus propias placas de expansión, se proveen dos conectores, uno macho y otro hembra, que pueden reconocerse respectivamente con los numeros 2 y 3 en la Fig. 1.3. Una imagen ampliada se muestra en la Fig. 2.11 indicando además la numeración de los pines. La mayoria de éstos pines estan conectados directamente al chip FPGA tal como lo muestra la Tabla 2.10. También se proveen pines de alimentación de 3.3V y GND.

Figura 2.11: Conectores para entradas y salidas de propósito general.

| Conector macho |     |     |              |  |  |

|----------------|-----|-----|--------------|--|--|

| Conectado a    | Pin | Pin | Conectado a  |  |  |

| FPGA Pin 39    | 1   | 2   | FPGA Pin 50  |  |  |

| FPGA Pin 37    | 3   | 4   | FPGA Pin 49  |  |  |

| FPGA Pin 36    | 5   | 6   | FPGA Pin 46  |  |  |

| FPGA Pin 35    | 7   | 8   | FPGA Pin 34  |  |  |

| FPGA Pin 33    | 9   | 10  | FPGA Pin 32  |  |  |

| FPGA Pin 31    | 11  | 12  | FPGA Pin 30  |  |  |

| FPGA Pin 29    | 13  | 14  | +3.3V        |  |  |

| FPGA Pin 28    | 15  | 16  | No conectado |  |  |

| FPGA Pin 27    | 17  | 18  | GND          |  |  |

| Conector hembra |     |     |             |  |  |

|-----------------|-----|-----|-------------|--|--|

| Conectado a     | Pin | Pin | Conectado a |  |  |

| FPGA Pin 21     | 1   | 2   | FPGA Pin 20 |  |  |

| FPGA Pin 19     | 3   | 4   | FPGA Pin 16 |  |  |

| FPGA Pin 15     | 5   | 6   | FPGA Pin 13 |  |  |

| FPGA Pin 12     | 7   | 8   | +3.3V       |  |  |

| FPGA Pin 10     | 9   | 10  | GND         |  |  |

Tabla 2.10: Conexión de los pines para las entradas/salidas de propósitogeneral.

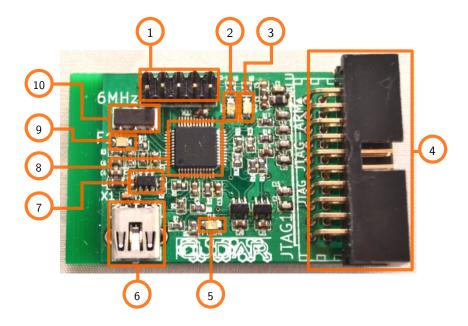

# 3. La placa OOCDLink

Ésta placa es la interfaz que permite la comunicación entre una computadora y la placa PHR. Su característica modular (o de circuito separado de la placa PHR principal) hace que su utilización no quede restringida a la FPGA y posibilita la interacción con los multiples dipositivos que soportan JTAG.

esta es una referencia a [2], otra [1], otra [3] y otra [4].

Figura 3.1: Componentes de la placa OOCDLink. 1) Conector UART, 2) LED RX, 3) LED TX, 4) Conector JTAG, 5) LED FT OK, 6) Conector USB 2.0, 7) EEPROM, 8) FT2232D, 9) LED Alimentación, 10) Oscilador de 6 MHz.

### El chip FT2232D

#### Caracteristicas

- Cumple con las especificaciones de USB 2.0 Full Speed (12 Mbits/sec).

- Simplifica la comunicación de USB con los prototolos de comunicaciones seriales JTAG, I2C y SPI.

- Tiene una tasa de transferencia de entre 300 y 3 MBaud.

- Desde el sistema operativo, la interfaz puede verse como un *puerto serie virtual* (necesita el driver que provee el fabricante sin costo adicional).

- También están disponibles librerías para facilitar el uso de JTAG, I2C y SPI (compatible con sistemas Windows y Linux).

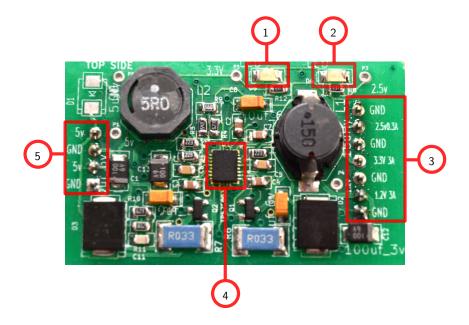

# 4. La placa S3Power

Tal como se describió en el capitulo 2, el chip FPGA tiene requerimientos de tensión que deben satisfacerse para que funcione correctamente. Para lograr las especificaciones necesarias se utiliza la placa S3Power, una placa que fue desarrollada por el *Instituto Nacional de Tecnología Industrial* (INTI) y que está disponible con licencia GNU. Una imagen de la placa se muestra en la Fig. 4.1 en donde también se señalan sus principales elementos.

Figura 4.1: Componentes de la placa S3Power. Las distintas partes resaltadas representan: 1) LED de tensión VCCO, 2) LED de tensión VCCAUX, 3) Conector de salida de la placa, 4) Chip TPS75003, 5) Conector de tensión de entrada.

La placa se alimenta con una tensión de 5V y en la salida es capaz de proporcionar tres valores de tensión regulados:

- 1.25V y 2.5A para la lógica interna.

- 3.3V y 2.5A para los bancos de pines.

- 2.4V y 200mA para el módulo de comunicación JTAG.

El componente principal de la placa es el chip TPS75003 que no solo se encarga de regular las tensiones, sino que además asegura un arranque lo suficientemente suave para las FPGA actuales y sus predecesoras con requerimientos mas exigentes. Un diagrama temporal de la repuesta en el arranque se muestra en la Fig. 4.2.

### El chip TPS75003

Éste chip es un regulador de tensiones de *Texas Instruments* especialmente diseñado para servir de fuente para las familias de FPGA de Xilinx Spartan-3, Spartan-3E y Spartan-3L. Entre las características mas importantes se pueden mencionar:

- Posee tres reguladores de tensión: Dos tipo Buck de 3A y eficiencia del 95 % y otro regulador lineal de 300 mA.

- Voltaje de entrada de entre 2.2V y 6.5 V.

- Arranque suave e independiente para cada regulador.

Figura 4.2: Tensiones de salida en el arranque.

■ Tensiones ajustables de 1.2 V a 6.5 V para los convertidores Buck y de 1.0 V a 6.5 V para el convertidor lineal.

# A. Conexiones de la FPGA

| Dı         | ITA C TAG                                             | Det            | ITAC                   |

|------------|-------------------------------------------------------|----------------|------------------------|

| P1         | JTAG TMS                                              | P51            | JTAG                   |

| P2         | JTAG TDI                                              | P52            | RS232 RX               |

| P3         | Periférico LED 6                                      | P53            | JTAG                   |

| P4         | DIP switch - Llave 6                                  | P54            | JTAG                   |

| P5         | Periférico LED 7                                      | P55            | VCCAUX (2.5V)          |

| P6         | DIP switch - Llave 7                                  | P56            | RS232 TX               |

| P7         | Periférico LED 8                                      | P57            | Display - Carácter 2   |

| P8         | Ground                                                | P58            | Ground                 |

| P9         | DIP switch - Llave 8                                  | P59            | Display - Carácter 1   |

| P10        | GPIO - Con. hembra - Pin 9                            | P60            | Display - Carácter 4   |

| P11        | VCCO 3 (3.3V)                                         | P61            | Display - Carácter 3   |

| P12        | GPIO - Con. hembra - Pin 7                            | P62            | Display - Segmento F   |

| P13        | GPIO - Con. hembra - Pin 6                            | P63            | Ground                 |

| P14        | Ground                                                | P64            | Display - Segmento B   |

| P15        | GPIO - Con. hembra - Pin 5                            | P65            | Display - Segmento A   |

| P16        | GPIO - Con. hembra - Pin 4                            | P66            | VCCINT (1.2V)          |

| P17        | VCCINT (1.2V)                                         | P67            | VCCO 1 (3.3V)          |

| P18        | Ground                                                | P68            | Display - Segmento E   |

| P19        | GPIO - Con. hembra - Pin 3                            | P69            | Ground                 |

| P20        | GPIO - Con. hembra - Pin 2                            | P70            | Display - Segmento D   |

| P21        | GPIO - Con. hembra - Pin 1                            | P71            | Display - Segmento DP  |

| P22        | VCCAUX (2.5V)                                         | P72            | Display - Segmento C   |

| P23        | JTAG                                                  | P73            | Display - Segmento G   |

| P24        | JTAG                                                  | P74            | Ground                 |

| P25        | JTAG                                                  | P75            | JTAG TDO               |

| P26        | VCCO 2 (3.3V)<br>GPIO - Con. macho - Pin 17           | P76  <br>  P77 | JTAG TCK Tact switch 1 |

| P27        | GPIO - Con. macho - Pin 17 GPIO - Con. macho - Pin 15 |                | Tact switch 2          |

| P28<br>P29 | GPIO - Con. macho - Pin 13                            | P78<br>P79     | VCCO 0 (3.3V)          |

| P30        | GPIO - Con. macho - Pin 12                            | P80            | Ground                 |

| P31        | GPIO - Con. macho - Pin 12                            | P81            | VCCINT (1.2V)          |

| P32        | GPIO - Con. macho - Pin 10                            | P82            | Tact switch 3          |

| P33        | GPIO - Con. macho - Pin 9                             | P83            | Tact switch 4          |

| P34        | GPIO - Con. macho - Pin 8                             | P84            | Periférico LED 1       |

| P35        | GPIO - Con. macho - Pin 7                             | P85            | DIP switch - Llave 1   |

| P36        | GPIO - Con. macho - Pin 5                             | P86            | Periférico LED 2       |

| P37        | GPIO - Con. macho - Pin 3                             | P87            | Ground                 |

| P38        | VCCINT (1.2V)                                         | P88            | DIP switch - Llave 2   |

| P39        | GPIO - Con. macho - Pin 1                             | P89            | Periférico LED 3       |

| P40        | Clock seleccionable 3                                 | P90            | DIP switch - Llave 3   |

| P41        | Clock selectionable 2                                 | P91            | Ground                 |

| P42        | Ground                                                | P92            | VCCAUX (2.5V)          |

| P43        | Clock 50MHz                                           | P93            | Periférico LED 4       |

| P44        | Clock seleccionable 1                                 | P94            | DIP switch - Llave 4   |

| P45        | VCCO 2 (3.3V)                                         | P95            | Ground                 |

| P46        | GPIO - Con. macho - Pin 6                             | P96            | VCCO 0 (3.3V)          |

| P47        | Ground                                                | P97            | DIP switch - Llave 5   |

| P48        | JTAG                                                  | P98            | Periférico LED 5       |

| P49        | GPIO - Con. macho - Pin 4                             | P99            | JTAG                   |

| P50        | GPIO - Con. macho - Pin 2                             | P100           | JTAG                   |

|            |                                                       | . 200          | -                      |

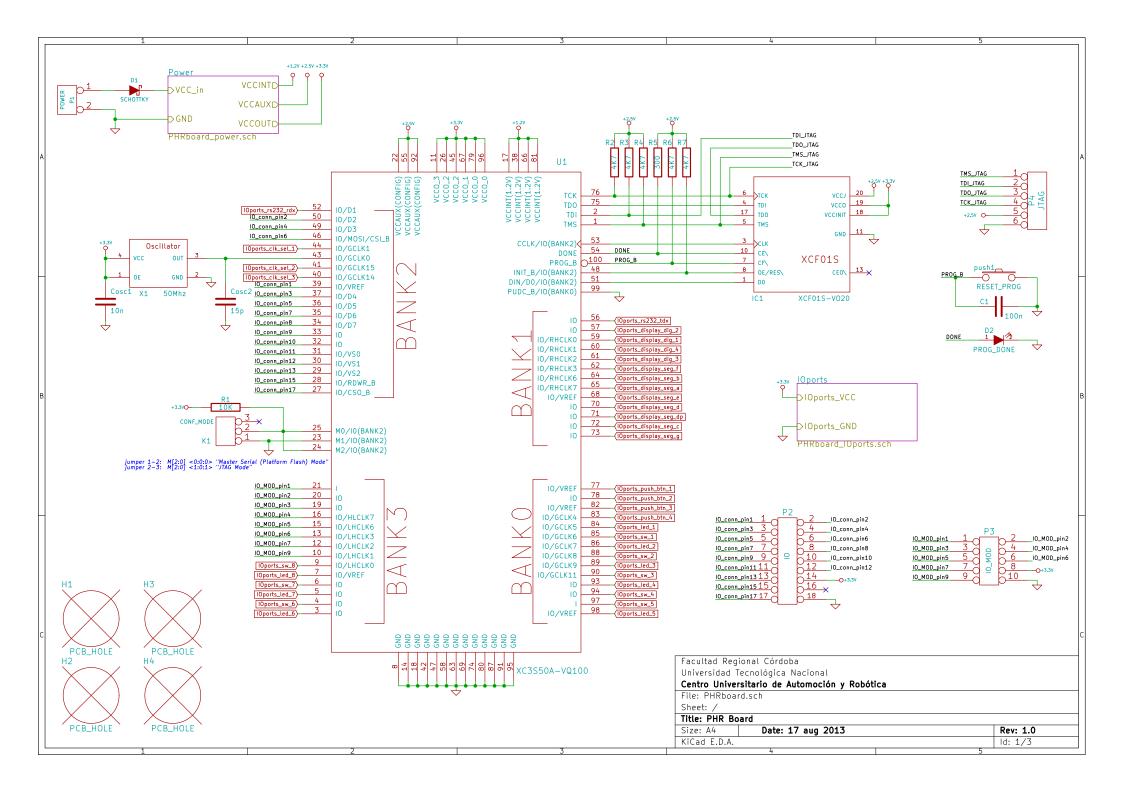

# B. Esquemáticos

# Bibliografía

- [1] Milton Abramowitz and Irene A. Stegun. *Handbook of Mathematical Functions with Formulas, Graphs, and Mathematical Tables.* Dover, New York, ninth dover printing, tenth gpo printing edition, 1964.

- [2] Nobody Jr. My article, 2006.

- [3] Maximiliano Quinteros. Manual de usuario. Texas Instruments.

- [4] Sears, Zemansky, Young, and Freedman. University Physics. Adison, 2008.

Por errores o sugerencias respecto a éste manual o alguno de los documentos complementarios no dude en comunicarse con nosotros escribiéndonos a alguna de las direcciones de correo electrónico listadas a continuación. Siempre estaremos agradecidos cualquiera sea el motivo del mensaje.

Maximiliano Quinteros: 50214@electronica.frc.utn.edu.ar Luis Guanuco:lguanuco@electronica.frc.utn.edu.ar