# Plataforma de Hardware Reconfigurable para el Diseño de Sistemas Digitales

Alexis Maximiliano Quiteros, Luis Alberto Guanuco, Sergio Daniel Olmedo Centro Universitario de Desarrollo en Automoción y Robótica Universidad Tecnológica Nacional Facultad Regional Córdoba

Email: maximiliano.quinteros@gmail.com, lguanuco@electronica.frc.utn.edu.ar, solmedo@scdt.frc.utn.edu.ar

Resumen-La contaste evolución de los sistemas electrónicos (digitales y analógicos) exige la búsqueda de nuevas herramientas para la formación académica. En el caso del diseños de sistemas digitales una excelente alternativa es el uso placas de evaluación basadas en dispositivos lógicos programables (PLDs). En función de los requerimientos y necesidades académicas que demandan recursos de hardware, y las oportunidades concretas de desarrollar una plataforma personalizada a las necesidades plateadas es que se presenta una plataforma reconfigurable con especificaciones abiertas. Este diseño cuenta con periféricos básicos con que se pueda interactuar en la implementación de sistemas digitales, pero además cuenta con una FPGA (Field Programmable Gate Array) que dispone de una gran cantidad de recursos internos para el uso en sistemas digitales avanzados que requieren gran capacidad de procesamiento. El proyecto se publica en forma libre (licencia GPL) buscando incentivar a otras grupos académicos en la modificación y adaptación de este trabajo a sus necesidades como así también proponer mejoras en versiones futuras de la plataforma.

# I. Introducción

Las áreas académicas vinculadas a la electrónica y la computación se encuentran en constante demanda de recursos educativos de hardware y software en virtud de potenciar los conocimientos de los estudiantes. En el caso de las tecnologías con poca difusión o implementación en la industria regional, la principal opción en la importación de plataformas educativas adquiridas a empresas destinadas a la manufacturación de sistemas embebidos. Estas plataformas comerciales se clasifican según su implementación por lo que no siempre cubren los requerimientos académicos. Por ejemplo, en el área de las técnicas digitales, los requerimientos de hardware para las cátedras iniciales difieren de las cátedras avanzadas. Esta situación presenta la oportunidad de desarrollar una plataforma a la medida de las necesidades de las instituciones académicas. Si se dispone de las especificaciones por parte de los docentes, la articulación de otras unidades académicas como laboratorios y grupos de investigación, es posible obtener un desarrollo que cubra las expectativas y aliente a la producción regional de plataformas educativas en un marco de transferencia de tecnología.

En el proceso de aprendizaje de las denominadas Técnicas Digitales necesariamente se debe implementar los diseños digitales. Desde el Álgebra de Bool, con operaciones digitales simples, hasta la implementación de un microprocesador son prácticas comunes de los sistemas digitales lógicos y

resulta fundamental su ejercitación para concluir el ciclo de enseñanza.

Al comienzo de la década de los 90s surgieron varios trabajos donde se planteaba la necesidad de una plataforma educativa orientada a la implementación de diseños lógicos digitales basados en PLDs. Los principales demandantes de estas plataformas eran diseñadores de arquitecturas de microprocesadores [1], desarrollos que años anteriores resultaban imposibles por el costo de la implementación en hardware. El avance en el proceso de integración de los circuitos integrados han llevado a que se desarrollen plataformas más complejas que ofrecen una gran cantidad de recursos de hardware. Al día de hoy se han generado varios proyectos desarrollados por instituciones académicas [2][3][4], otras con especificaciones abiertas [5][6] y también con fines comerciales [7]. Todos estos trabajos tienen algunas características en común:

- El dispositivo lógico programable base es una FPGA

- Memoria de programación de la FPGA

- Acceso de programación JTAG

- Software para interactuar con la plataforma desde una computadora

- Dos perfiles de diseño:

- Para la implementación de sistemas lógicos generales

- Orientado a un área específica

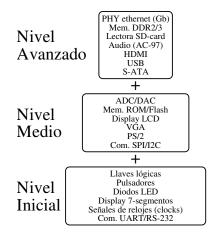

La caracterización anterior no es un intento de generalizar a todas las plataformas educativas basadas en PLDs, pero sí resulta útil para definir el perfil de la plataforma que se describe en este trabajo. Sin la especificación de a que usuarios se destina una plataforma, no se puede comenzar con el estudio de los diferentes dispositivos que se utilizarán. La Figura 1 ilustra una clasificación en bloques de los recursos que ofrecen diferentes plataformas basada en dispositivos PLDs. Donde a niveles iniciales en el estudio de la lógica digital se requieren periféricos básicos como ser llaves conmutadoras de los estados lógicos, dispositivos indicadores como diodos LED, etc. Mientras que a estudios más avanzados se requieren otros tipos de dispositivos como ser a un nivel medio controladores para display gráficos LCD/LED, comunicaciones entre varios dispositivos mediante SPI, I2C, etc. Y por últimos, en la formación de especialistas de sistemas embebidos, requieren recursos como interfaces físicos para ethernet, controladores HDMI, PS2, USB, etc.

Fig. 1. Recursos de hardware en función de los niveles de aprendizaje.

La mayoría de las plataformas de evaluación comerciales son fabricadas en el exterior del país. Se han encontrado desarrollos nacionales pero no son comercializados sino usados en laboratorios universitarios. Entre las empresas fabricantes de sistemas embebidos basados en dispositivos PLDs, se destacan: Xilix, Altera y Digilent. Los principales perfiles de sus desarrollos se encuentran orientados a,

- Sistemas de comunicaciones

- Procesamiento de Señales Digitales (DSP)

- Automovilismo

En la Figura 2 se pueden ver tres diferentes plataformas orientadas al diseño de sistemas digitales<sup>1</sup>. Los recursos de hardware que ofrecen estos desarrollos son:

- FPGA

- Memoria de programación de la FPGA

- Periféricos básicos (LEDs, display, pulsadores, llaves, etc.)

- Puerto USB

- Puerto para módulos externos

- Puerto para propósitos generales

- Varias señales de reloj (clok)

- VGA y PS/2

- Memorias ROM/RAM

- ADC/DAC

En nuestra región la tecnología PLDs se encuentra en su auge hace unos años. Instituciones gubernamentales de defensa [8], aeroespaciales, comunicaciones [9] están implementando dispositivos como FPGAs y CPLDs en sus diseños. Además existe una constante actualización por parte de las instituciones académicas en los programas analíticos de las carreras relacionadas a los sistemas embebidos [10].

Considerando la situación expuesta es que se impulsa el desarrollo de la Plataforma de Hardware Reconfigurable (PHR). Esta plataforma es un proyecto a medida de las necesidades en la enseñanza de los sistemas digitales lógicos en las cátedras

(a) BASYS2 (Digilent)

(b) DE0-Nano (Altera)

(c) Avnet Spartan-6 LX150T (Xilinx/Avnet)

Fig. 2. Plataformas comerciales de desarrollo educativas basadas en FPGAs.

iniciales. Ofrece recursos básicos para que los estudiantes interactúen con la tecnología de los dispositivos PLDs, pero también dispone de puertos para conectar otros recursos físicos permitiendo que estudiantes avanzados puedan hacer uso de ellas sin limitaciones. Además al ser publicado bajo licencia libre/abierta permitirá a que el diseño, o parte de él, sirva como referencias a otras instituciones académicas que se encuentren en búsqueda de una plataforma para implementar en sus diferentes cátedras.

#### II. DISPOSITIVOS PRINCIPALES

Son varios los dispositivos principales que se deben definir antes de comenzar a conectar algún componente electrónico. Y es que en función de estos dispositivos es que se debe seleccionar los restantes. Se podrían listar estos como:

- FPGA

- Memoria de programación

- Interfaz de programación

- Periféricos

- Sistema de potencia

#### A. FPGA

La FPGA que se utiliza pertenece a la familia Spartan-3 de Xilinx Inc. Esta familia a la vez se clasifican en

- Familia Spartan-3A extendida:

- Bajo costo

- \* Spartan-3A

- · Ideal para uso de interfaz entre dispositivos.

- \* Spartan-3A DSP

- Mayor densidad de recursos en comparación que la familia Spartan-3A

- Dispone de un dispositivo DPS (DSP48A) para el procesamiento de señales digitales

- \* Spartan-3AN

- · Dispositivos no volátiles

- Ideal para aplicaciones con restricciones de espacio

<sup>&</sup>lt;sup>1</sup>Alguna de estas plataformas disponen de módulos conversores ADC y DAC, por lo que se podría decir que también permiten la implementación de sistemas analógicos en dominio discreto.

TABLE I CARACTERÍSTICA DE LA FAMILIA SPARTAN-3A

| Devices   | System | Block RAM | Dedicated   | Maximum  |

|-----------|--------|-----------|-------------|----------|

|           | Gates  | bits      | Multipliers | User I/O |

| XC3S50A   | 50K    | 54K       | 3           | 144      |

| XC3S200A  | 200K   | 288K      | 16          | 248      |

| XC3S400A  | 400K   | 360K      | 20          | 311      |

| XC3S700A  | 700K   | 360K      | 20          | 372      |

| XC3S1400A | 1400K  | 576K      | 32          | 502      |

- Familia Spartan-3E

- Familia Spartan-3

Altara, Atmel y otros fabricantes de FPGAs también presentan familias similares a las Spartan-3. Aquí se optó por Xilinx Inc. debido a la experiencia en software/hardware con que cuenta el Centro de Investigación<sup>2</sup> donde se desarrolla el proyecto. La familia extendida Spartan-3A es la que se utiliza en el diseño de la PHR. En la comparación de recursos de hardware y precio del dispositivo FPGA, las FPGAs Spartan-3A presentan un valor aceptable. En un extremo, las Spartan-3A, permiten una gran variedad de modos de programación en contraste con la familia Spartan-3. Por otro lado, no es necesario gran capacidad de procesamiento que justifique la inclusión de un DSP, debido al perfil del usuario de la plataforma que se desarrolla. Se recuerda que la plataforma PHR se destina a la enseñanza de la tecnología descriptiva de hardware. Las principales características de las FPGAs Spartan-3A se describen en la Tabla I.

El dispositivo seleccionado, como se puede ver en la Tabla I, es el XC3S200A. Éste cuenta con una gran densidad de recursos de hardware (200K compuertas lógicas) a la vez que se puede encontrar a esta FPGA en un encapsulado de pequeñas dimensiones (VQ100) que facilita el diseño del PCB. En este encapsulado se puede contar con 68 puertos de entrada/salida (I/O) para ser utilizados externamente a diferentes tecnologías programables (LVTTL, LVCMOS33/25/18, entre otros). El perfil del diseño de la PHR no requiere de una gran cantidad de puertos de I/O debido a las aplicaciones para las que se lo diseña.

# B. Memoria de programación

La tecnología utilizada en las FPGAs Spartan-3A requieren de una memoria externa que configure al dispositivo ya que es volátil. Esta familia permite la utilización de varios tipos de memorias como modos de configuración para embeber el diseño digital en la FPGA. Xilinx comercializa memorias Flash PROM para todas sus familias de FPGA. Hay una relación directa entre la capacidad lógica de una FPGA con el tamaño de la memoria de programación, en la Tabla xxx se puede apreciar esta relación para el caso de la familia Spartan-3A.

Tanto la FPGA como la memoria de programación Flash PROM se encuentran conectadas en cadena a través de un

TABLE II Tipo de memoria para la familia Spartan-3A

| Devices   | Configuration | ISP PROM |  |

|-----------|---------------|----------|--|

| Devices   | Bits          | Solution |  |

| XC3S50A   | 437,312       | XCF01S   |  |

| XC3S200A  | 1,196,128     | XCF02S   |  |

| XC3S400A  | 1,886,560     | XCF02S   |  |

| XC3S700A  | 2,732,640     | XCF04S   |  |

| XC3S1400A | 4,755,296     | XCF08P   |  |

interfaz denominado JTAG Boundary-Scan. Xilinx Inc. implementa el estándar IEEE 1149.1 (comúnmente llamado JTAG) en sus dispositivos FPGAs, CPLDs y memorias Flash PROM para la programación mediante un software, y de esta forma transferir el diseños sintetizados en sus dispositivos.

#### C. Periféricos

Los periféricos que se implementan en este diseño permiten a los usuarios iniciales realizar prácticas sencillas. Pero también los usuarios avanzados requieren de indicadores de señales lógicas, pulsadores, etc. (Figura 1). Los periféricos que ofrece la plataforma PHR son:

- Salidas

- 8 LEDs indicadores

- Display de 7-segmentos de 4 dígitos

- Entradas

- 8 Llaves (DIP switch)

- 4 Pulsadores

- Relojes (Clocks) 50Mhz

- Divisor de reloj de 16Mhz a ∼1Mhz

- Entrada/Salida

- Puerto Serie (RS-232)

- Puerto con I/O para propósitos generales (conectores IDE)

# D. Sistema de alimentación

Por su arquitectura interna y la gran densidad de recursos lógicos que ofrecen, la necesidad de alimentar estos dispositivos en forma eficiente es una clave en el diseño de la plataforma. Los sistemas complejos como las FPGAs requieren minimizar los ruidos presentes en las fuentes de alimentación y es aquí donde las fuentes de alimentación lineal son las ideales. Pero la desventaja de estos circuitos de alimentación radica en la baja eficiencia que presentan, menor que 50%. Las fuentes de alimentación conmutadas (Switch-Mode) tienen una eficiencia mayor que el 90% pero son mas ruidosas comparada a las fuentes lineales [11]. Con esta primera observación sobre los dos principales tipos de fuentes de alimentación, se debe considerar otros aspectos sobre el tipo de regulador a utilizar,

- Secuencia de arranque

- Inicio monótona de la rampa de tensión

- Arranque suave

- Encapsulado y diseño del PCB

<sup>&</sup>lt;sup>2</sup>CUDAR - Centro Universitario de Desarrollo en Automoción y Robótica.

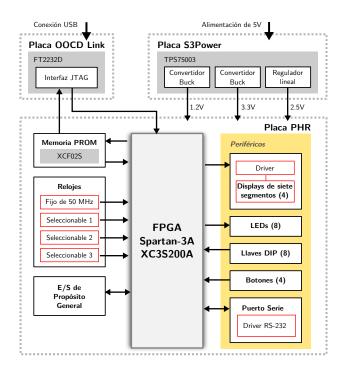

Fig. 3. Diagrama en bloque de la PHR.

El TPS75003, fabricado por Texas Instruments, es un dispositivo que integra tres reguladores de tensión en una sola pastilla. Este integrado fue diseñado para aplicaciones donde se deben alimentar a FPGAs y DSPs. En especial, el TPS75003 fue testeado con las familias Spartan-3 de Xilinx proporcionando las tensiones necesarias para estas FPGAs. Esta compuesto por dos contradores buck que logran una gran eficiencia y un regulador lineal LDO (Low-Dropout).

El Laboratorio de Desarrollo Electrónico con Software Libre, perteneciente al Instituto Nacional de Tecnología Industrial (INTI), ha realizado la implementación de un módulo de alimentación para placas con dispositivos FPGA [12]. En este desarrollo se utiliza el TPS75003 como dispositivo central y fue probado con una FPGA de la familia Spartan-3E. El diseño se encuentra disponible bajo una licencia de libre uso y modificación. Esta última aclaración no resulta un dato menor, pues la plataforma PHR persigue el mismo fin que el desarrollo realizado por el INTI. La idea de compartir y transferir desarrollos a la comunidad. Para la plataforma PHR se utiliza el módulo desarrollado por el INTI.

## III. PLACA PHR

Luego de las consideraciones sobre los dispositivos principales se presenta una diagrama en bloque de la plataforma PHR. La Figura 3 incluye no solo la placa base que contiene la FPGA, la memoria de programación de la FPGA y los periféricos sino también las placas de programación JTAG y la fuente de alimentación para todo el sistema.

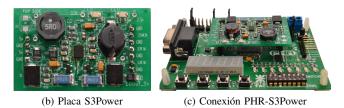

La placa de alimentación llamada S3Power es el desarrollo mencionado en la Sección II-D. Es una placa basada en el dispositivo TPS75003 que proporciona los tres niveles de tensión para la FPGA (1.2V, 2.5V y 3.3V). La S3Power se

(a) Placa PHR (base)

Fig. 4. Placas PHR y S3Power.

conecta a la placa base PHR a través de dos conectores, uno para tomar la tensión de alimentación de todo el sistema (5V) y otro conector donde entrega las correspondientes tensiones para la FPGA. La ventaja de esta implementación es la posibilidad de reutilizar la S3Power en otros diseños que requieran las mismas especificaciones de potencia que la PHR. En la Figura 4 se puede ver la placa PHR y su conexión con la placa S3Power.

# IV. INTERFAZ JTAG

La plataforma PHR requiere interactuar con una computadora personal, sobre ésta el usuario realizará su diseño lógico mediante un lenguaje descriptivo de hardware (HDL). Para obtener la síntesis del diseño se utiliza las herramientas de software proporcionadas por el fabricante de la FPGA, que luego se transferirá al dispositivo programable (ya sea directamente sobre la FPGA o almacenando la información sobre la memoria Flash PROM).

Actualmente el puerto serie y paralelo, muy utilizados antiguamente, están quedando obsoletos. Otra situación presenta el puerto USB, el cual actualmente es el interfaz cableado más utilizado para la comunicación entre una computadora y dispositivos externos.

Los requerimientos planteados para el interfaz JTAG son:

- JTAG Comunicarse con la plataforma PHR utilizando un dispositivo externo que implemente el estándar IEEE 1149.1.

- USB Comunicarse con una computadora personal a través de este puerto sin restricción al sistema operativo a utilizar (GNU/Linux, Mac OS y Microsoft Windows).

Uno de los dispositivo comerciales que presenta las características anteriormente definidas es el FT2232D fabricado

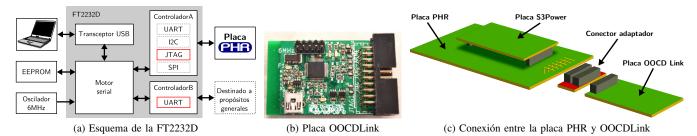

Fig. 5. Interfaz JTAG (implementación FT2232D).

por Future Technology Devices International Ltd. (FTDI). El FT2232D dispone de un interfaz llamado MPSSE (Multi-Protocol Synchronous Serial Engine). Esta tecnología proporciona un medio flexible para comunicar dispositivos seriales síncronos a un puerto USB[13]. Por ser "Multi-Protocolo", el MPSSE permite comunicar con diferentes tipos de dispositivos síncronos, los más populares son SPI, I<sup>2</sup>C y JTAG. Otra característica del FT2232D es la disponibilidad de dos canales independientes. De esta forma en uno de los canales se puede implementar JTAG y en otro una UART, funcionalidad muy útil para comunicarse por RS-232 desde una computadora sin puerto serie. El esquema de la implementación para este dispositivo se presenta en la Figura 5a, la placa se denomina OOCDLink<sup>3</sup>.

En la Figura 5b se presenta una fotografía de la placa OOCDLink. En la misma se puede ver el conector mini-USB para la PC y un conector IDE de 20 pines donde se mapean los pines JTAG. El puerto JTAG de la FPGA y la memoria Flash PROM utiliza solo cuatro pines del estándar IEEE 1149.1 (TDI, TDO, TCK y TMS). Pero la mayoría de los microcontroladores utilizan dos señales más desde el puerto JTAG para realizar debugging. Es por esta razón que la placa OOCDLink utiliza el conector IDE de 20 pines agregando las señales TRST y SRST. En la Figura 5c se puede ver como se conectarían las placas PHR y OOCDLink. El adaptador puede también ser evitado realizando un cableado simple (no recomendando, solución económica).

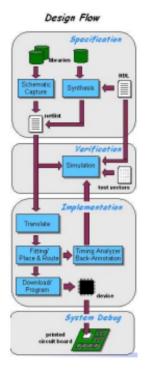

#### V. PROGRAMACIÓN DE LA PHR

Además de los desarrollos de hardware, la plataforma PHR dispone de herramientas de software necesarias para la programación/descarga del diseño lógico en la FPGA/Flash PROM. La Figura 6 representa el flujo de diseño que implementan los sistemas digitales descritos con los lenguajes HDL.

Los lenguajes descriptivos como son VHDL y Verilog se encuentran estandarizados. En el caso de VHDL el estándar ANSI/IEEE 1076-1993 lo define, mientras que para Verilog se estandarizo en la revisión IEEE 1364-1995. Esto asegura que los diseños descritos por estos lenguajes puedan ser reutilizados. Si un fabricante cambia sus librerías, solo bastará con recompilar para poder obtener la síntesis del diseño nuevamente. La implementación del diseño está vinculada con

Fig. 6. Flujo de diseño usando HDL.

el fabricante de los dispositivos sobre los cuales se piensa trabajar.

## A. PHR GUI

1) Xc3srog:

#### VI. DISCUSIÓN

Existen dos formas de solventar esta demanda, la primera opción es la adquisición de estos recursos a empresas que ofrecen plataformas educativas que cumplan con las especificaciones, pero aquí se presenta una segunda opción que es generar estas plataformas personalizadas a las necesidades de la región. Actualmente se dispone de los conocimientos necesarios para emprender un ciclo de trabajo donde las mismas unidades académicas cubren sus demandas a través de diferentes espacios como son los grupos de investigación y laboratorios

<sup>&</sup>lt;sup>3</sup>El nombre OOCDLink es tomado de un desarrollo publicado en una web de sistemas embebidos sobre el cual se baso nuestra placa.

#### VII. CONCLUSIONES

#### ACKNOWLEDGMENT

The authors would like to thank...

#### REFERENCES

- Hiroyuki Ochi, ASAver.1: An FPGA-Based Education Board for Computer Architecture/system Design, Design Automation Conference 1997.

Proceeding of the ASP-DAC'97. Asia and South Pacific. January 1997.

- [2] C. Chang, C. Huang, Y. Lin, Z. Huang and T. Hu, FPGA Platform for CPU Design and Applications, 5th. IEEE Conference on Nanotechnology. Nagoya, Japan. July 2005.

- [3] D. Kang, S. Hwang, K. Jhang, K. Yi, A Low Cost and Interactive Rapid Prototyping Platform For Digital System Design Education, IEEE International Conference on Microelectronic Systems Education, MSE'07.

- [4] J. Xing, W. Zhao and H. Hu, An FPGA-Based Experiment Platform for Multi-Cores System, 9th. International Conference for Young Computer Scientistis, ICYCS'08. 2008.

- [5] A. Cicuttin, M. Crespo, A. Shapiro, N. Abdallah, Building an Evolvable Low-Cost HW/SW Educational Platform – Application to Virtual Instrumentation, IEEE International Conference on Microelectronic Systems Education, MSE'07, 2007.

- [6] J. Lockwood, N. McKeown, G. Watson, G. Gibb, P. Hartke, J. Naous, R. Raghuraman and J. Luo, NetFPGA - An Open Platform for Gigabitrate Network Switching and Routing, IEEE International Conference on Microelectronic Systems Education, MSE'07. 2007.

- [7] Z. Qingguo, Y. Qi, L. Chanjuan, H. Bin, Port Embedded Linux to XUP Virtex-II Por Development Board, IEEE. 2009.

- [8] Instituto de Investigación Científica y Técnicas para al defensa (CITEDEF), *Radar Láser*, url: http://www.citedef.gob.ar/i-d/laser/.

- [9] J. Siman, G. Jaquenod and H. Mascialino, Fpga-Based Transmit/Receive Distributed Controller for the TR Modules of an L Band Antenna (SAR), 4th. Southern Conference on Programmable Logic, 2008.

- [10] P. Cayuela, Actualización de la currícula Incorporación de la lógica programable en ingeniería, Jornada de Investigación y Desarrollo en Ingeniería de Software (JIDIS'07). Córdoba Argentina. 2007.

- [11] D. Canny, Power-Supply Solutions for Xilinx FPGAs, 4th. Southern Conference on Programmable Logic, 2008.

- [12] C.Huy and D. Brengi, Módulo de alimentación para placas con dispositivos FPGA, Congreso de Microelectrónica Aplicada (μΕΑ2010). San Justo, Buenos Aires. 2010.

- [13] Future Technology Devices International Ltd., FTDI MPSSE Basics, (Application Notes). Document Reference No.:FT\_000208, AN\_135. December 2010.