# **APPLICATION** NOTE

# SIMPLIFY BOARD LAYOUT USING LVPECL TERMINATORS

### INTRODUCTION

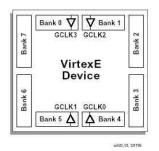

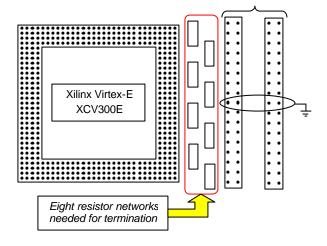

The Xilinx<sup>®</sup> Virtex-E<sup>™</sup> family of Field Programmable Gate Arrays (FPGA) offers a wide range of flexible Input/Output interfaces including Low Voltage Positive Emitter-Coupled Logic (LVPECL). The Virtex-E device is comprised of eight banks of definable I/O arranged around the perimeter of the device. See Figure 1 below.

Figure 1.

LVPECL is a differential I/O standard that requires a pair of signal lines for each channel. The differential transmission scheme is less susceptible to common-mode noise than single-ended transmission methods. LVPECL standards require external termination resistors to reduce signal reflection. The standard voltage swing for the differential pair is approximately 850mV, and the typical V<sub>cco</sub> is 3.3V.

The ClearONE Series RT1710B6/B7, RT1720B7, and RT1721B6/B7 have been designed to help the PCB Layout and Design Engineer simplify the termination for the LVPECL I/O Standards, while at the same time conserving valuable PCB real estate.

The circuits for terminating LVPECL transmitters and receivers are different. The following sections explain each.

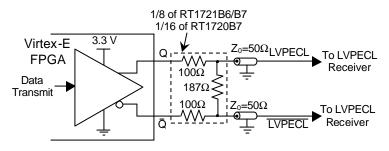

#### LVPECL TRANSMITTER TERMINATION

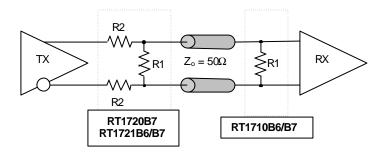

In general, the LVPECL transmitter termination consists of a series-shunt resistor combination for

each differential pair. The shunt resistor value is 187 ohms, whereas the series pair consists of 100 ohms each. See figure 2 below. Note: these values assume a 50-Ohm characteristic impedance on the transmission line.

Figure 2.

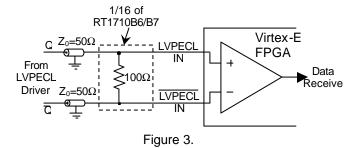

#### LVPECL RECEIVER TERMINATION

The LVPECL receiver termination consists of a shunt resistor between each differential pair. The shunt resistor value is 100 Ohms. See figure 3 below. Note: this value assumes a 50-Ohm characteristic impedance on the transmission line.

### CLEARONE BGA RESISTOR LAYOUT

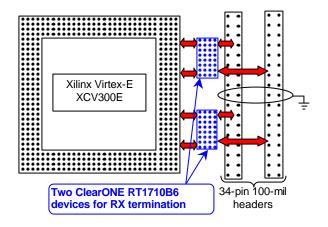

A typical application is illustrated by terminating 64 LVPECL lines from the Xilinx XCV300E device (BG432 package). As few as two ClearONE terminator packages can be used for transmitter terminations, and another two for the receiver, as opposed to up to sixteen total termination packs with other resistor termination solutions.

# Note Number AN-C1-FPGALVPECL FPGA LVPECL INTERFACE

The 32 LVPECL pairs can be routed from the 432pin BGA package through the ClearONE CBGA terminators, and then over to twin 34-pin headers with 100-mil contact spacing. Refer to the diagrams in Figure 4, which, though not to scale, accurately show the comparisons of terminating LVPECL receivers with ClearONE terminators versus terminating with standard resistor networks. The center pin pairs of each header are best connected to the ground plane, which provides a return path for any common-mode currents that may be introduced by external noise or mismatches in layout or loads.

Figure 4.

Table 1 shows the CTS ClearONE part numbers that can be used for the transmitter/receiver LVPECL resistor terminations with the Xilinx Virtex-E series FPGA's. The B6 suffix denotes a 1.27mm (50-mil) BGA pitch, and the B7 suffix denotes a 1mm (39-mil) BGA pitch.

#### CLEARONE PART NUMBER GUIDE

| Part Number | I/O Standard       | # of  | Pins |

|-------------|--------------------|-------|------|

|             | Termination for:   | Pairs |      |

| RT1720B7    | LVPECL Transmitter | 16    | 64   |

| RT1721B6/B7 | LVPECL Transmitter | 8     | 32   |

| RT1710B6/B7 | LVPECL Receiver    | 16    | 32   |

Table 1.

Refer to Figure 5 and Table 2 for details of where the ClearONE terminators are used, the part numbers available, the resistance values for each part, and the ball grid pitch.

Figure 5.

## **Detailed Information**

| Part     | R1 <b>W</b> | R2 W | Array  | Pitch |

|----------|-------------|------|--------|-------|

| Number   |             |      | Size   | (mm)  |

| RT1710B6 | 100         | N/A  | 4 x 8  | 1.27  |

| RT1710B7 | 100         | N/A  | 4 x 8  | 1.00  |

| RT1720B7 | 187         | 100  | 4 x 16 | 1.00  |

| RT1721B6 | 187         | 100  | 4 x 8  | 1.27  |

| RT1721B7 | 187         | 100  | 4 x 8  | 1.00  |

Table 2.

#### SUMMARY

The CTS ClearONE BGA terminators offer the simplest solution for board layout on LVPECL transmitter/receiver connections using the Xilinx Virtex-E series FPGA's. In addition, these offer the lowest terminators parasitic I/O capacitance and inductance in the industry. Our full line of BGA terminators have been modeled up to 1.2 GHz and the SPICE models and equivalent circuits can be found on our Web site at www.ctsclearone.com.

Xilinx and Virtex-E are registered trademarks of Xilinx Corporation.