# PITbUtils Specification

Author: Per Larsson pela.opencores@gmail.com

Rev. 1.2 March 12, 2020

This page has been intentionally left blank.

### **Revision History**

| Rev . | Date       | Author      | Description                                         |

|-------|------------|-------------|-----------------------------------------------------|

| 0.1   | 9/2/2013   | Per Larsson | First draft                                         |

| 0.2   | 11/10/2013 | Per Larsson | Added sections Acknowledgements and Language.       |

|       |            |             | Added reference section on waitsig().               |

|       |            |             | Updated reference section on print() and            |

|       |            |             | pltbutils_clkgen.                                   |

| 0.3   | 1/5/2013   | Per Larsson | Added sections User Configuration, Configuring      |

|       |            |             | Simulation Halt, Configuring Messages for           |

|       |            |             | Integration Environments.                           |

|       |            |             | In reference section added starttest, endtest,      |

|       |            |             | removed testname.                                   |

|       |            |             | Updated figures and feature bullets.                |

| 0.4   | 1/9/2013   | Per Larsson | Updates for alpha0006: Text modified in             |

|       |            |             | numerous places to reflect that PlTbUtils is now    |

|       |            |             | using the variable pltbv and the signal pltbs for   |

|       |            |             | control and status, instead of the previous shared  |

|       |            |             | variable and global signals.                        |

| 0.5   | 13/1/2014  | Per Larsson | Updates for alpha0007: added example testbench      |

|       |            |             | where the testcase process is instansiated in the   |

|       |            |             | testbench top (tb_example1). The old example        |

|       |            |             | where the testcase process is located in a VHDL     |

|       |            |             | component of its own, is now called example_tb2.    |

| 0.6   | 2/2/2015   | Per Larsson | Updates for beta0002: added description of          |

|       |            |             | to_ascending(), to_descending(), hxstr(), functions |

|       |            |             | and procedures in txt_util.vhd.                     |

| 0.7   | 23/11/2015 | Per Larsson | Updates for beta0003: added to VHDL versions        |

|       |            |             | and simulators to feature list. Added check() for   |

|       |            |             | iiioolean and for time with tolerance. In section   |

|       |            |             | User Configuration, added info on                   |

|       |            |             | pltbutils_files.lst .                               |

| 0.8   | 03/01/2016 | Per Larsson | Updates for beta0004: updated feature list, added   |

|       |            |             | Skipping tests, updated figures.                    |

| 1.0   | 26/01/2016 | Per Larsson | Updates for pltbutils v1.0: minor corrections.      |

| 1.2   | 12/04/2020 | Per Larsson | Updates for pltbutils v1.2:                         |

|       |            |             | Added waitsig() for unclocked signals.              |

|       |            |             | Added check_binfile(), check_txtfile(),             |

|       |            |             | check_datfile().                                    |

|       |            |             | Added str(), str_equal().                           |

|       |            |             | Added pltbutils_time_measure,                       |

|       |            |             | pltbutils_diff_check.                               |

1

## Introduction

### **Overview**

PITbUtils makes it easy to create automatic, self-checking simulation testbenches, and to locate bugs during a simulation. It is a collection of functions, procedures and testbench components that simplifies creation of stimuli and checking results of a device under test.

#### Features:

- Simulation status printed in transcript windows as well as in waveform window (error count, checks count, number and name of current test, etc).

- Check procedures which output meaningful information when a check fails.

- Clear SUCCESS/FAIL message at end of simulation.

- Easy to locate point in time of bugs, by studying increments of the error counter in the waveform window.

- User-defined information messages in the waveform window about what is currently going on.

- Transcript outputs prepared for parsing by scripts, e.g. in regression tests.

- Configurable status messages for use in continuous integration environments, e.g. TeamCity.

- Reduces amount of code in tests, which makes them faster to write and easier to

- Tests can easily be included or skipped in a test run.

- Supports VHDL-93 and later.

- Supports most popular VHDL simulators, including ModelSim, ISim and XSim.

It is intended that PITbUtils will constantly expand by adding more and more functions, procedures and testbench components. Comments, feedback and suggestions are welcome to <a href="mailto:pela.opencores@gmail.com">pela.opencores@gmail.com</a>.

Project web page: http://opencores.org/project,pltbutils.

Subversion repository URL: <a href="http://opencores.org/ocsvn/pltbutils/pltbutils/trunk">http://opencores.org/ocsvn/pltbutils/pltbutils/trunk</a>

Subversion export command:

svn export http://opencores.org/ocsvn/pltbutils/pltbutils/trunk pltbutils

### **Acknowledgements**

PlTbUtils contains the file txt\_util.vhd by Stefan Doll and James F. Frenzel.

Thanks to Stefan Eriksson for suggestions and feedback.

### Language

PITbUtils complies with VHDL-1993 and later, so it works with most VHDL simulators.

It is possible to configure the way a simulation stops, by taking advantage of the VHDL-2008 keywords stop and finish. If your simulator supports stop and/or finish, see Configuring Simulation Halt on page 25.

### A quick look

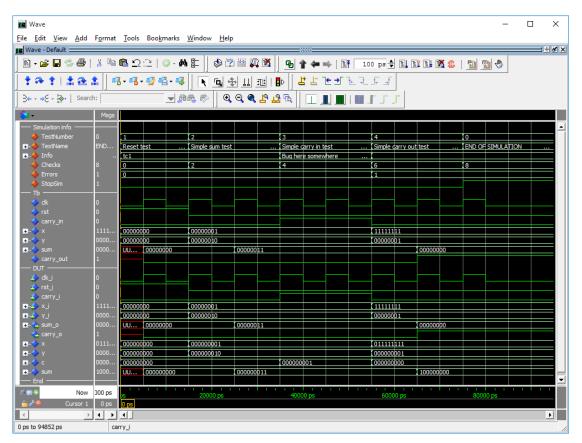

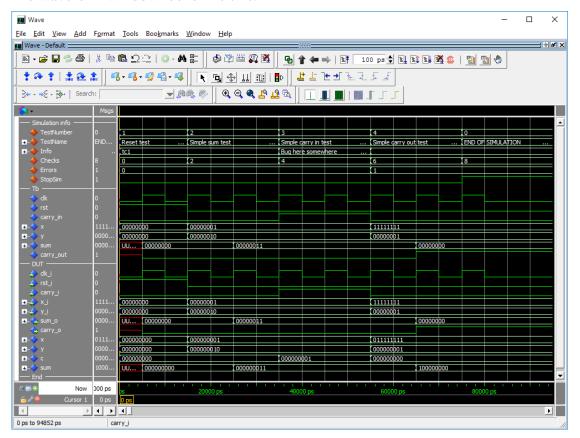

During a simulation, the waveform window shows current test number, test name, user-defined info, accumulated number of checks and errors. When the error counter increments, a bug has been found in that point in time.

The transcript window clearly shows points in time where the simulation starts, ends, and where errors are detected. The simulation stops with a clear SUCCESS/FAIL message, specifically formatted for parsing by scripts.

The testcase code is compact and to the point, which results in less code to write, and makes the code easier to read, as in the following example.

```

-- NOTE: The purpose of the following code is to demonstrate some of the

-- features in PlTbUtils, not to do a thorough verification.

p tc1 : process

variable pltbv : pltbv t := C PLTBV INIT;

startsim("tc1", "", pltbv, pltbs);

rst <= '1';</pre>

<= '0';

carry_in

<= (others => '0');

<= (others => '0');

starttest(1, "Reset test", pltbv, pltbs);

waitclks(2, clk, pltbv, pltbs);

0, pltbv, pltbs);

check("Sum during reset", sum,

check("Carry out during reset", carry_out, '0', pltbv, pltbs);

<= '0';

endtest(pltbv, pltbs);

starttest(2, "Simple sum test", pltbv, pltbs);

carry_in <= '0';

x <= std logic vector(to unsigned(1, x'length));

y <= std logic vector(to unsigned(2, x'length));

waitclks(2, clk, pltbv, pltbs);

check("Sum", sum, 3, pltbv, pltbs);

check("Carry out", carry_out, '0', pltbv, pltbs);

endtest(pltbv, pltbs);

starttest(3, "Simple carry in test", pltbv, pltbs);

print(G DISABLE BUGS=0, pltbv, pltbs, "Bug here somewhere");

carry in <= '1';

x <= std_logic_vector(to_unsigned(1, x'length));</pre>

y <= std logic vector(to unsigned(2, x'length));

waitclks(2, clk, pltbv, pltbs);

check("Sum",

check("Sum", sum, 4, pltbv, pltbs);

check("Carry out", carry_out, '0', pltbv, pltbs);

4, pltbv, pltbs);

print(G DISABLE BUGS=0, pltbv, pltbs, "");

endtest(pltbv, pltbs);

starttest(4, "Simple carry out test", pltbv, pltbs);

carry_in <= '0';

x <= std_logic_vector(to_unsigned(2**G_WIDTH-1, x'length));</pre>

y <= std_logic_vector(to_unsigned(1, x'length));</pre>

waitclks(2, clk, pltbv, pltbs);

check("Sum", sum, 0, pltbv, pltbs);

check("Carry out", carry_out, '1', pltbv, pltbs);

endtest(pltbv, pltbs);

endsim(pltbv, pltbs, true);

wait;

end process p_tc1;

```

2

# **Tutorial**

### **Basics**

We will demonstrate how to use PlTbUtils by showing an example. In this example, we have a DUT (Device Under Test / Design Under Test) with the following entity.

As you can see, it has a clock- and a reset input port (clk\_i and rst\_i), three other input ports (x\_i, y\_i, and carry\_i), and two output ports (sum\_o and carry\_o). There is also a generic, G\_WIDTH, which sets the number of bits in x\_i, y\_i and sum\_o. The second generic, G\_DISABLE\_BUGS, is very unusual in real designs, but it is useful in this example. We will reveal the purpose of this strange generic later, although some may already be able to guess what it is for.

To verify this DUT, we want the testbench to apply different stimuli to the input ports, and check the response of the output ports. The following code is an example of such a testbench. We will first show all of the code, and then explain parts of it.

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric std.all;

use work.txt util.all;

use work.pltbutils func pkg.all;

use work.pltbutils comp pkg.all;

entity tb example1 is

generic (

G WIDTH

: integer := 8;

G CLK PERIOD

: time := 10 ns;

G_DISABLE_BUGS : integer range 0 to 1 := 0

);

end entity tb_example1;

architecture bhv of tb example1 is

-- Simulation status- and control signals

-- for accessing .stop_sim and for viewing in waveform window

: pltbs t := C PLTBS INIT;

signal pltbs

-- DUT stimuli and response signals

signal clk : std_logic;

signal y : std_logic_vector(G_WIDTH-1 downto 0);

signal sum : std_logic_vector(G_WIDTH-1 downto 0);

signal carry_out : std_logic;

begin

dut0 : entity work.dut example

generic map (

=> G WIDTH,

G WIDTH

G DISABLE BUGS => G DISABLE BUGS

port map (

=> clk,

clk i

rst i

=> rst,

=> carry_in,

carry_i

хi

=> x,

y_i

=> y,

=> sum,

sum o

carry o

=> carry out

clkgen0 : pltbutils clkgen

generic map(

G PERIOD

=> G CLK PERIOD

port map(

=> clk,

clk o

=> pltbs.stop_sim

stop sim i

```

```

-- Testcase process

-- NOTE: The purpose of the following code is to demonstrate some of the

-- features of PlTbUtils, not to do a thorough verification.

p_tc1 : process

variable pltbv : pltbv t := C PLTBV INIT;

begin

startsim("tc1", "", pltbv, pltbs);

<= '1';

<= '0';

carry_in

<= (others => '0');

<= (others => '0');

starttest(1, "Reset test", pltbv, pltbs);

waitclks(2, clk, pltbv, pltbs);

check("Sum during reset", sum,

0, pltbv, pltbs);

check("Carry out during reset", carry_out, '0', pltbv, pltbs);

rst <= '0';

endtest(pltbv, pltbs);

starttest(2, "Simple sum test", pltbv, pltbs);

carry_in <= '0';</pre>

x <= std logic vector(to unsigned(1, x'length));</pre>

y <= std_logic_vector(to_unsigned(2, x'length));</pre>

waitclks(2, clk, pltbv, pltbs);

check("Sum",

3, pltbv, pltbs);

check("Sum", sum, 3, pltbv, pltbs);

check("Carry out", carry_out, '0', pltbv, pltbs);

endtest(pltbv, pltbs);

starttest(3, "Simple carry in test", pltbv, pltbs);

print(G DISABLE BUGS=0, pltbv, pltbs, "Bug here somewhere");

carry in <= '1';

x <= std_logic_vector(to_unsigned(1, x'length));</pre>

y <= std logic vector(to unsigned(2, x'length));

waitclks(2, clk, pltbv, pltbs);

check("Sum", sum, 4, pltbv, pltbs);

check("Carry out", carry_out, '0', pltbv, pltbs);

print(G_DISABLE_BUGS=0, pltbv, pltbs, "");

endtest(pltbv, pltbs);

starttest(4, "Simple carry out test", pltbv, pltbs);

carry_in <= '0';

x <= std logic vector(to unsigned(2**G WIDTH-1, x'length));

y <= std_logic_vector(to_unsigned(1, x'length));</pre>

waitclks(2, clk, pltbv, pltbs);

check("Sum", sum, 0, pltbv, pltbs);

check("Carry out", carry_out, '1', pltbv, pltbs);

endtest(pltbv, pltbs);

endsim(pltbv, pltbs, true);

wait;

end process p tc1;

```

end architecture bhv;

As the testbench example shows, the following packages are needed (in addition to the usual std\_logic\_1164, etc):

```

use work.txt_util.all;

use work.pltbutils_func_pkg.all;

use work.pltbutils comp pkg.all;

```

txt\_util contains functions and procedures for handling strings.

pltbutils\_func\_pkg contains type definitions, functions and procedures for controlling stimuli and checking response.

pltbutils\_comp\_pkg contains component declarations for testbench components.

PITbUtils uses a variable called pltbv, and a signal called pltbs, for controlling the simulation and keeping track of status. The pltbs signal is useful for viewing in the simulator's waveform window. pltbs is a record containing a number of members which show various information. Expand pltbs in the simulator's waveform window to expose the members. To make it prettier, you can make use of ModelSim's Combine Signals feature. Each member of the pltbs record can be set to be its own Combined Signal, see the waveform images in this document. Other simulators usually have similar features.

The DUT is instansiated in the testbench, as well as a clock generator component from PITbUtils.

There is also a testcase process, which feeds the DUT with stimuli, and checks the results.

The testcase process starts with calling the procedure startsim(). This procedure initializes pltbv and pltbs, and outputs a message to the transcript and to the waveform window to inform that the simulation now starts. The first argument to startsim is the name of the testcase. The second argument is an empty vector in this example. The purpose of this argument will be explained later.

The last arguments of startsim(), and to many other procedures in PlTbUtils, are pltbv and pltbs.

After initiating stimuli to the DUT, we call the procedure starttest() with the number and name for the first test. starttest() prints the test number and test name to the transcript and to the waveform window, and updates pltbv and pltbs.

Then we need to wait until the DUT has reacted to the stimuli. We do this by calling the procedure waitclks(), which waits a specified number of cycles of the specified clock.

After this, we start checking the results, by examining the outputs from the DUT. To do this, we use the check() procedure. The first argument is a text string that specifies what we check, the second argument is the signal or variable that we want to examine, and the third is the expected value of the signal or variable. If the examined signal holds the expected value, nothing is printed. But if the value is incorrect, the string in the first argument is printed, together with the actual and expected values of the signal. The number and name of the test (as specified with starttest()) is also printed. PITbUtils' check counter is incremented for every check() procedure call, and the error counter is incremented in case of error.

After the test, we call endtest().

We make a number of different tests by calling starttest(), setting stimuli, waiting for the DUT to react with waitclks() or some other means, and checking the outputs with the check() procedure, and calling endtest().

Finally, we call the endsim() procedure, which prints an end-of-simulation message to the transcript, and presents the results, including a SUCCESS or FAIL message.

The start-of-simulation message, end-of-simulation message, and SUCCESS/FAIL messages have a unique formatting with three dashes or asterisks before and after the message. This make them easy to search for by scripts, to simplify collection of simulation status of regression tests with a lot of different simulations.

Try it out in your simulator! The pltbutils files that need to be compiled are located in src/vhdl/, and they are listed in compile order in pltbutils\_files.lst . The example DUT file is located in examples/vhdl/rtl\_example/, and the example testbench files are located in examples/vhdl/example1/. The files are listed in compile order in example\_dut.lst and tb\_example1\_files.lst .

If a ModelSim .do files available you are user. there are in sim/modelsim\_tb\_example1/run/ To use them, start Start ModelSim, and in the ModelSim Gui select the menu item Filedirectory... Navigate the **PlTbUtils** >Change to directory sim/modelsim\_tb\_example1/run/ and click Ok. Then, in the transcript window, type do run.do

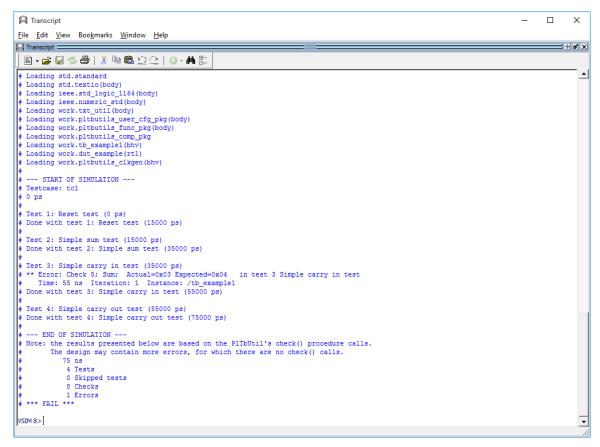

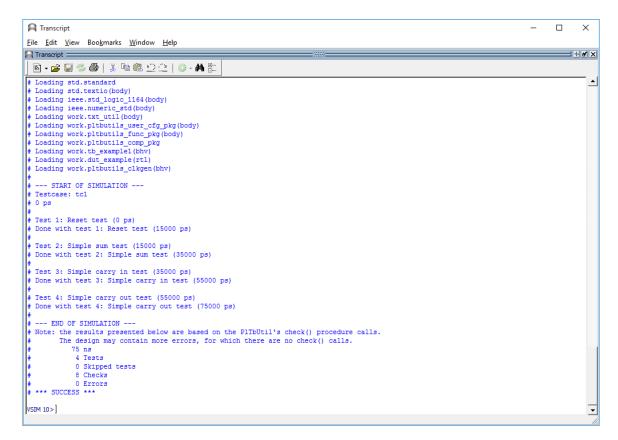

The simulation will start, and the transcript from the simulation looks as follows.

```

<u>File Edit View Bookmarks Window Help</u>

Transcript =

B · 🚅 🗑 🖏 🐠 | ¾ 🐿 🖺 № 2 | ◎ · 🗚 🖫

# Loading std.standard

# Loading std.textio(body)

# Loading ieee.std.logic_l164(body)

# Loading ieee.numeric_std(body)

# Loading work.txt_util(body)

# Loading work.txt_util(body)

Loading work.pltbutils_func_pkg(body)

Loading work.pltbutils_comp_pkg

# Loading work.tb_example1(bhv)

# Loading work.dut_example(rt1)

Loading work.pltbutils_clkgen(bhv)

--- START OF SIMULATION ---

# Testcase: tcl

# 0 ps

# Test 1: Reset test (0 ps)

# Done with test 1: Reset test (15000 ps)

Test 2: Simple sum test (15000 ps)

Done with test 2: Simple sum test (35000 ps)

# # Test 3: Simple carry in test (35000 ps)

# ** Error: Check 5; Sum; Actual=0x03 Expected=0x04 in test 3 Simple carry in test

# Time: 55 ns Iteration: 1 Instance: /tb_example1

# Done with test 3: Simple carry in test (55000 ps)

Test 4: Simple carry out test (55000 ps)

Done with test 4: Simple carry out test (75000 ps)

--- END OF SIMULATION ---

Note: the results presented below are based on the PITDUtil's check() procedure calls.

The design may contain more errors, for which there are no check() calls.

75 ns

4 Tests

0 Skipped tests

8 Checks

# 1 Errors

# *** FAIL ***

VSIM 8>]

```

The transcript says that one error has been found at 55 ns, in test 3; Simple carry in test.

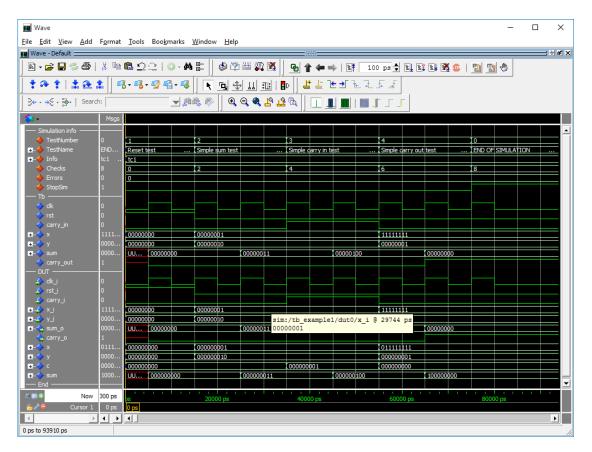

The waveform window looks like this.

Here we can see the error detected at the point in time where the error counter increments from 0 to 1. Again, we can that the error is found in test 3, the Simple carry in test.

Have a look at the DUT code in examples/vhdl/rtl\_example/dut\_example.vhd . It looks as follows.

```

x <= resize(unsigned(x_i), G_WIDTH+1);

y <= resize(unsigned(y_i), G_WIDTH+1);

c <= resize(unsigned(std_logic_vector'('0' & carry_i)), G_WIDTH+1);

p_sum : process(clk_i)

begin

if rising_edge(clk_i) then

if rst_i = '1' then

sum <= (others => '0');

else

if G_DISABLE_BUGS = 1 then

sum <= x + y + c;

else

sum <= x + y;

end if;

end if;

end if;

end process;</pre>

```

The code really looks suspicious. If the generic G\_DISABLE\_BUGS is not one, the carry input is not added to the sum. But we need the carry input to be added to the sum!

A simple way to disable this bug, is to set the generic G\_DISABLE\_BUGS to one. In this case, this can be done very easily, without any modifying of the code.

In the ModelSim transcript window, type

```

do run bugfixed.do

```

This will run the test again, but now with the generic G\_DISABLE\_BUGS set to 1.

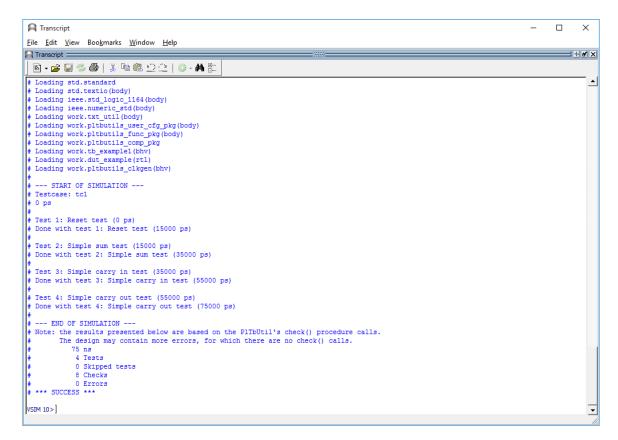

The transcript and waveform windows will now look like the following images.

This tutorial has shown some of the available procedures and testbench components in PlTbUtils. For a complete list, see the reference section.

When you want to make your own testbenches with PlTbUtils, have a look at the template files in templates/vhdl/template1/.

### Different kinds of check()

There are a number of overloaded check() procedures for different VHDL types, e.g. std\_logic, std\_logic\_vector, unsigned, signed, integer, boolean, time, etc. See the Reference section for a complete list. The check() procedures checks equality, i.e. that a signal or variable has an expected value. They have the form

```

check(rpt, actual, expected, pltbv, pltbs)

```

where rpt is the string message with info on what is being checked, actual is the signal or variable to check, and expected is the expected value. If the check fails, rpt is printed togher with actual and expected valued. There is no need to include the expected value in the rpt string, because it is printed anyway.

The is no support for comparisons other than equality, such as greater than, or not equal. But there is one check procedure that can be used for composing your own expression:

```

check(rpt, expr, pltbv, pltbs)

```

Replace expr with your own expression.

```

check("Counter after data burst", cnt o > 10, pltbv, pltbs);

```

Note that if the test fails, the actual and expected values will not be printed (because this check() procedure does not get any information on actual and expected value. You may include that information in the rpt message if you want to.

You can create specialized check procedures in a package file of your own. Your package file should begin with

```

use work.txt_util.all;

use work.pltbutils func pkg.all;

```

### and your own check procedure should call

check(rpt, expr, actual, expected, mask, pltbv, pltbs)

where actual, expected and mask are strings.

### Example:

### **Testbench with multiple testcases**

In some cases, it is more convenient to not include the testcase process in the testbench top. Instead, we can put the testcase process in its own VHDL component. Then we can have alternative architectures for this component, with different testcase processes.

This is practial for large testbenches with a lot of testbench components and other code, with a requirement for multiple testcases. Then we don't have to write a new testbench for each testcase.

The following is an example of such a testbench.

```

library ieee;

use ieee.std_logic_1164.all;

use work.pltbutils_func_pkg.all;

use work.pltbutils_comp_pkg.all;

entity tb example2 is

generic (

G WIDTH

: integer := 8;

G_CLK_PERIOD

: time := 10 ns;

: integer range 0 to 1 := 0

G DISABLE BUGS

);

end entity tb_example2;

architecture bhv of tb example2 is

-- Simulation status- and control signals

-- for accessing .stop sim and for viewing in waveform window

: pltbs_t := C_PLTBS_INIT;

signal pltbs

-- DUT stimuli and response signals

: std_logic;

: std logic;

signal clk

signal rst

signal carry_in : std_logic;

: std_logic_vector(G_WIDTH-1 downto 0);

: std_logic_vector(G_WIDTH-1 downto 0);

: std_logic_vector(G_WIDTH-1 downto 0);

: std_logic;

signal x

signal y

signal sum

signal carry out

begin

dut0 : entity work.dut example

generic map (

G WIDTH

=> G WIDTH,

=> G DISABLE BUGS

G DISABLE BUGS

port map (

clk_i

=> clk,

rst_i

=> rst,

=> carry_in,

carry_i

x_i

=> x,

=> y,

=> sum,

y_i

sum_o

=> carry_out

carry_o

);

clkgen0 : pltbutils_clkgen

generic map(

=> G CLK PERIOD

G PERIOD

port map(

clk o

=> clk,

stop_sim_i

=> pltbs.stop sim

tc0 : entity work.tc_example2

generic map (

=> G WIDTH,

G WIDTH

G DISABLE BUGS => G DISABLE BUGS

port map(

pltbs

=> pltbs,

clk

=> clk,

=> rst,

rst

=> carry_in,

carry_in

=> x,

=> y,

=> sum,

У

sum

=> carry_out

carry_out

);

```

end architecture bhv;

Instead of a testcase process, we instansiate a testcase component (tc\_example2). This testcase component has an entity defined in one file, and the architecture defined in another file. This makes it possible to have several different testcases for the same testbench. Just compile the testcase architecture that you want to use for a specific simulation run.

The entity declaration for the testcase looks as follows.

```

library ieee;

use ieee.std_logic_1164.all;

use work.pltbutils_func_pkg.all;

entity tc_example2 is

generic (

G_WIDTH : integer := 8;

G_DISABLE_BUGS : integer range 0 to 1 := 0

);

port (

pltbs : out pltbs_t;

clk : in std_logic;

rst : out std_logic;

carry_in : out std_logic;

x : out std_logic_vector(G_WIDTH-1 downto 0);

y : out std_logic_vector(G_WIDTH-1 downto 0);

sum : in std_logic_vector(G_WIDTH-1 downto 0);

carry_out : in std_logic

);

end entity tc example2;

```

The ports of the testcase components are the same as for the DUT, but the mode (direction) of the ports are the opposite, so the testcase component can drive the inputs of the DUT, and detect the values of the output of the DUT. The only exception to this rule is the clock, which is an input, just as for the DUT.

There is also an output port for pltbs, because pltbs is driven from the tc architecture.

The entity is stored in its' own file.

The architecture contains the testcase process. There can be several different architecture files. The architecture looks as follows.

```

library ieee;

use ieee.std logic 1164.all;

use ieee.numeric std.all;

use work.txt util.all;

use work.pltbutils func pkg.all;

-- NOTE: The purpose of the following code is to demonstrate some of the

-- features in PlTbUtils, not to do a thorough verification.

architecture tc1 of tc_example2 is

begin

p_tc1 : process

variable pltbv : pltbv_t := C_PLTBV_INIT;

begin

startsim("tc1", "", pltbv, pltbs);

rst <= '1';

carry_in <= '0';

<= (others => '0');

Х

<= (others => '0');

starttest(1, "Reset test", pltbv, pltbs);

waitclks(2, clk, pltbv, pltbs);

check("Sum during reset", sum,

0, pltbv, pltbs);

check("Carry out during reset", carry_out, '0', pltbv, pltbs);

<= '0';

endtest(pltbv, pltbs);

starttest(2, "Simple sum test", pltbv, pltbs);

carry_in <= '0';

x <= std logic vector(to unsigned(1, x'length));</pre>

y <= std logic vector(to unsigned(2, x'length));

waitclks(2, clk, pltbv, pltbs);

check("Sum", sum, 3, pltbv, pltbs);

check("Carry out", carry_out, '0', pltbv, pltbs);

check("Sum",

3, pltbv, pltbs);

endtest(pltbv, pltbs);

starttest(3, "Simple carry in test", pltbv, pltbs);

print(G DISABLE BUGS=0, pltbv, pltbs, "Bug here somewhere");

carry in <= '1';

x <= std logic_vector(to_unsigned(1, x'length));</pre>

y <= std logic vector(to unsigned(2, x'length));

waitclks (2, clk, pltbv, pltbs);

check("Sum", sum, 4, pltbv, pltbs);

check("Carry out", carry_out, '0', pltbv, pltbs);

4, pltbv, pltbs);

print(G DISABLE BUGS=0, pltbv, pltbs, "");

endtest(pltbv, pltbs);

starttest(4, "Simple carry out test", pltbv, pltbs);

carry_in <= '0';

x <= std logic vector(to unsigned(2**G WIDTH-1, x'length));

y <= std logic vector(to unsigned(1, x'length));

waitclks(2, clk, pltbv, pltbs);

check("Sum", sum, 0, pltbv, pltbs);

check("Carry out", carry_out, '1', pltbv, pltbs);

endtest(pltbv, pltbs);

endsim(pltbv, pltbs, true);

wait;

end process p tc1;

end architecture tc12;

```

Try this too in your simulator. The example testbench files are located in examples/vhdl/example2/. The files are listed in compile order in tb\_example2\_files.lst.

If you are a ModelSim user, there are .do files available ir sim/modelsim\_tb\_example2/run/

To use them, start Start ModelSim, and in the ModelSim Gui select the menu item

$\label{eq:file-condition} File-> Change & directory... & Navigate & to & the & PlTbUtils & directory \\ sim/modelsim\_tb\_example2/run/ & click & Ok. & Then, & in the transcript & window, & type \\ & do & run\_tcl.do & & lock & l$

### Also try

do run\_tcl\_bugfixed.do

Template files for this type of testbench is available in templates/vhdl/template2/.

### **Skipping tests**

PlTbUtils lets you skip tests, if you want to. This is useful while debugging a failure in a test. You can save simulation time by skipping the tests before and after the failing test. It is also useful while developing a test to skip the tests before.

To skip a test, add generic G\_SKIPTESTS to the testbench of type std\_logic\_vector.

If a bit in the vector is '1', the corresponding test is skipped. Bits are counted from 0 and upwards. There is usually no test with number 0, so bit 0 is usually a dummy. The length of the vector does not have to match the number of tests. If the vector is shorter, the remaining tests will not be skipped. If the vector is longer, the excessive bits will be ignored.

Feed this generic as the second argument of startsim().

```

startsim("tc1", G SKIPTESTS, pltbv, pltbs);

```

For each test, add an if-clause that calls is\_test\_active(pltbv) and executes or skips the test.

If is\_test\_active(pltbv) returns true, the test will be executed as usual. If it returns false, PlTbUtils outputs a message like the following, and skips the test.

```

Skipping Test 1: Reset test

```

Note that if you forget the if-clause, the "skipping test message" will be displayed, but the test will be executed anyway. If a check() procedure is called within a skipped test (if there is no if-clause), an error message will be displayed, and the error counter will be incremented.

The skip functionality is included in the templates in templates/vhdl/template1/ and templates/vhdl/template2/.

It is of course also possible to define the generic in the following form:

```

G_SKIPTESTS : std_logic_vector := "001";

```

This is more compact as it uses only a single line, but it is not possible to add individual comments for each test.

### **User Configuration**

It is possible to configure some aspects of PlTbUtils's behaviour, by modifying the package file pltbutils\_user\_cfg.pkg.

It is recommended NOT to modify the file directly. Instead, copy it to another directory and modify the copy. Make the simulator read the modified copy instead of the original. This makes it easier to update pltbutils to a later version without destroying the modifications. After updating, check if anything has changed in the file, and change your modified copy accordingly.

If your simulation environment (scripts, etc) uses the file pltbutils\_files.lst, then copy it too, to the other directory. Modify the contents of the file, by modifying the relative paths to point to the files from the new location.

### **Configuring Simulation Halt**

When calling endsim(), the signal stop\_sim is set to '1'. When set, all clock generators etc in the testbench and the DUT should stop, so there will be no further events in the simulation. The simulator will detect that nothing more will happen, and stops the simulation.

In some cases, it is not possible to stop clock generators, PLL models etc. In that case, endsim() can force a simulaton halt, by setting the force argument to true.

The declaration of endsim() is

```

procedure endsim(

signal pltbutils_sc : out pltbutils_sc_t;

constant show_success_fail : in boolean := false;

constant force : in boolean := false

);

```

so to force a simulation halt, call endsim with

```

endsim(pltbutils sc, true, true);

```

This stops the simulation using an assert-failure. This works in all versions of VHDL, but it is an ugly way of doing it, since it outputs a failure message for something which isn't a failure.

You can change the way the simulation stops when the force flag is set in your copy of pltbutils\_user\_cfg.vhd.

Change the constant <code>c\_pltbutils\_use\_custom\_stopsim</code> to true, and modify the behavior of the procedure <code>custom\_stopsim()</code>. In VHDL-2008 the new keywords <code>stop</code> and <code>finish</code> was introduced. Try one of them, if your simulator supports them.

### **Configuring Messages for Integration Environments**

It is possible adapt the status messages to suit various continuus integration environments, e.g. TeamCity, by specifying what the messages should look like.

You can create your own messages printed when starting and stopping a simulation, starting and stopping a test, for checking, etc.

In your copy of pltbutils\_user\_cfg\_pkg.vhd, set one or more of the message constants to true, and modify the associated procedure.

### The constants are

```

C_PLTBUTILS_USE_CUSTOM_STARTSIM_MSG

C_PLTBUTILS_USE_CUSTOM_ENDSIM_MSG

C_PLTBUTILS_USE_CUSTOM_STARTTEST_MSG

C_PLTBUTILS_USE_CUSTOM_ENDTEST_MSG

C_PLTBUTILS_USE_CUSTOM_CHECK_MSG

C_PLTBUTILS_USE_CUSTOM_ERROR_MSG

```

The corresponding procedures already contain examples for TeamCity. Modify if you use another environment.

You can disable the standard messages by setting the standard constants to false (C PLTBUTILS USE STD STARTSIM MSG etc).

### Differences between simulators

Text strings (TestName and Info text) in the waveform window look different in different simulators. In ModelSim strings look like this: Example text. In ISim it looks like this: 'E','x','a','m','p','l','e','','t','e','x','t'.

3

# Reference

### **PITbUtils files**

The PlTbUtils files are located in src/vhdl/.

The files needed to be compiled are listed in compile order in pltbutils\_files.lst .

See example testbenches using PlTbUtils in examples/vhdl/.

This code can be simulated from sim/modelsim\_tb\_example1/run/ and sim/modelsim\_tb\_example2/run/ .

Template code is available in templates/vhdl/.

### **Functions and procedures**

### startsim

```

procedure startsim(

constant testcase_name : in string;

constant skiptests : in std_logic_vector;

variable pltbv : inout pltbv_t;

signal pltbs : out pltbs_t

)

```

Displays a message at start of simulation message, and initializes PlTbUtils' status and control variable and -signal. Call startsim() only once.

### Arguments:

testcase\_name Name of the test case, e.g. "tc1".

skiptests std\_logic\_vector for marking tests that should be skipped.

The leftmost bit has position 0, and position numbers increment to the right. A '1' indicates that the test with the same number as the position should be skipped. Note that there is usually no test which has number 0, so bit zero in the vector is usually ignored. This argument is normally fed by a generic. If no tests should be skipped, a zero-length vector is

allowed, ("").

pltby, pltbs PlTbUtils' status- and control variable and -signal.

The start-of-simulation message is not only intended to be informative for humans. It is also intended to be searched for by scripts, e.g. for collecting results from a large number of regression tests.

### Examples:

```

startsim("tc1", "", pltbv, pltbs);

startsim("tc2", G SKIPTESTS, pltbv, pltbs); -- G SKIPTESTS is a generic

```

### endsim

Displays a message at end of simulation message, presents the simulation results, and stops the simulation. Call endsim() it only once.

### Arguments:

pltbv, pltbs PlTbUtils' status- and control variable and -signal.

show\_success\_fail If true, endsim() shows "\*\*\* SUCCESS \*\*\*", "\*\*\* FAIL \*\*\*",

or "\*\*\* NO CHECKS \*\*\*". Optional, default is false.

force If true, forces the simulation to stop using an assert failure

statement. Use this option only if the normal way of stopping the

simulation doesn't work (see below). Optional, default is false.

The testbench should be designed so that all clocks stop when endsim() sets the signal stop\_sim to '1'. This should stop the simulator.

In some cases, that doesn't work, then set the force argument to true, which causes a false assert failure, which should stop the simulator.

The end-of-simulation messages and success/fail messages are not only intended to be informative for humans. They are also intended to be searched for by scripts, e.g. for collecting results from a large number of regression tests.

### Examples:

```

endsim(pltbv, pltbs);

endsim(pltbv, pltbs, true);

endsim(pltbv, pltbs, true, true);

```

### starttest

Sets a number (optional) and a name for a test. The number and name will be printed to the screen, and displayed in the simulator's waveform window.

The test number and name is also included if there errors reported by the check() procedure calls.

### Arguments:

num Test number. Optional, default is to increment the current test

number.

name Test name.

pltbv, pltbs PlTbUtils' status- and control variable and -signal.

If the test number is omitted, a new test number is automatically computed by incrementing the current test number. Manually setting the test number may make it easier to find the test code in the testbench code, though.

### Examples:

```

starttest("Reset test", pltbv, pltbs);

starttest(1, "Reset test", pltbv, pltbs);

```

### is\_test\_active

```

function is_test_active(

constant pltbv : in pltbv_t

) return boolean

```

Returns true if a test is active (not skipped), otherwise false.

Arguments:

pltbv PlTbUtils' status- and control variable.

### Example:

```

starttest(3, "Example test", pltbv, pltbs);

if is_test_active(pltbv) then

... test code ...

end if;

endtest(pltbv, pltbs);

```

### endtest

```

procedure endtest(

variable pltbv : inout pltbv_t;

signal pltbs : out pltbs_t

)

```

Prints an end-of-test message to the screen.

### Arguments:

pltbv, pltbs PlTbUtils' status- and control variable and -signal.

### Example:

```

endtest(pltbv, pltbs);

```

### print printv print2

```

Defined in txt_util.vhd:

procedure print(

: in string

constant txt

)

procedure print(

constant active

: in

boolean;

: in

constant txt

string

)

Defined in pltbutils_func_pkg.vhd:

procedure print(

signal

: out string;

constant txt

: in

string

)

procedure print(

constant active

: in boolean;

signal s

: out string;

constant txt

: in

string

)

procedure print(

variable pltbv

: inout pltbv_t;

signal pltbs

: out pltbs_t;

constant txt

: in

string

)

procedure print(

constant active

: in

boolean;

variable pltbv

: inout pltbv t;

signal pltbs

: out pltbs t;

constant txt

: in

string

```

```

procedure printv(

variable s

: out string;

constant txt

: in string

)

procedure printv(

constant active

: in boolean;

variable s

: out string;

constant txt

: in string

)

procedure print2(

signal s

: out string;

constant txt

: in string

)

procedure print2(

constant active : in boolean;

signal s

: out string;

constant txt

: in string

)

procedure print2(

variable pltbv

: inout pltbv_t;

signal pltbs

: out pltbs_t;

constant txt

: in string

)

procedure print2(

: in boolean;

constant active

variable pltbv

: inout pltbv_t;

signal pltbs

: out pltbs t

constant txt

: in string

```

print() without a signal as argument prints text messages to the transcript window.

print() with a signal as argument prints text messages to that signal for viewing in the simulator's waveform window.

printv() does the same thing, but to a variable instead.

print2() prints both to a signal and to the transcript window.

The type of the output can be string or pltbv+pltbs.

#### Arguments:

s Signal or variable of type string to be printed to.

txt The text.

active The text is only printed if active is true. Useful for debug switches,

etc.

pltbv, pltbs PlTbUtils' status- and control variable and -signal. The text will be

printed to "info" in the waveform window.

If the string txt is longer than the signal s, the text will be truncated. If txt is shorter, s will be padded with spaces.

### waitclks

```

procedure waitclks(

: in

constant n

natural;

signal

: in

std logic;

variable pltbv

: inout pltbv t;

signal

pltbs

: out

pltbs t;

constant falling

: in

boolean := false;

constant timeout

:= C PLTBUTILS TIMEOUT

: in

time

)

```

Waits specified amount of clock cycles of the specified clock. Or, to be more precise, a specified number of specified clock edges of the specified clock.

#### Arguments:

n Number of rising or falling clock edges to wait.

clk The clock to wait for.

pltbv, pltbs PlTbUtils' status- and control variable and -signal.

falling If true, waits for falling edges, otherwise rising edges.

Optional, default is false.

timeout Timeout time, in case the clock is not working.

Optional, default is C\_PLTBUTILS\_TIMEOUT.

```

waitclks(5, sys_clk, pltbv, pltbs);

waitclks(5, sys_clk, pltbv, pltbs, true);

waitclks(5, sys clk, pltbv, pltbs, true, 1 ms);

```

## waitsig

```

procedure waitsig(

signal s

: in

integer|std logic|std logic vector|unsigned|signed;

constant value

: in

integer|std logic|std logic vector|unsigned|signed;

signal clk

: in std logic;

variable pltbv

: inout pltbv t;

signal pltbs

: out pltbs t;

constant falling

: in

boolean := false;

time := C PLTBUTILS TIMEOUT)

constant timeout

: in

```

Waits until a signal has reached a specified value. In clocked variants of waitsig, the signal is checked after specified clock edge (rising or falling).

Unclocked variants are currently only available for types std\_logic and std\_logic\_vector.

#### Arguments:

s The signal to test.

Supported types: integer, std\_logic, std\_logic\_vector, unsigned,

signed.

value Value to wait for.

Same type as data or integer.

clk The clock, only present in clocked variants of waitsig.

pltby, pltbs PlTbUtils' status- and control variable and -signal.

falling If true, waits for falling edges, otherwise rising edges.

Optional, default is false.

timeout Timeout time, in case the clock is not working.

Optional, default is C\_PLTBUTILS\_TIMEOUT.

```

waitsig(wr_en, '1', sys_clk, pltbv, pltbs);

waitsig(rd_en,    1, sys_clk, pltbv, pltbs, true);

waitclks(full, '1', sys_clk, pltbv, pltbs, true, 1 ms);

```

#### check

```

procedure check (

constant rpt

: in

string;

constant data

: in

integer |

std logic | std logic vector |

unsigned | signed | boolean | time |

string;

constant expected

: in

integer |

std_logic | std_logic_vector |

unsigned | signed | boolean | time |

string;

variable pltbv

: inout pltbv_t;

signal

pltbs

pltbs t

: out

)

procedure check (

constant rpt

: in

string;

constant data

: in

std_logic_vector;

constant expected

std logic vector;

: in

constant mask

std logic vector;

: in

variable pltbv

: inout pltbv t;

signal pltbs

: out

pltbs t

procedure check (

constant rpt

: in

string;

constant data

: in

time;

constant expected

: in

time;

constant tolerance

time;

: in

variable pltbv

: inout pltbv t;

signal

pltbs

: out

pltbs_t

)

procedure check (

constant rpt

: in

string;

constant expr

: in

boolean;

variable pltbv

: inout pltbv t;

signal pltbs

: out

pltbs t

)

```

Checks that the value of a signal or variable is equal to expected. If not equal, displays an error message and increments the error counter.

#### Arguments:

rpt Report message to be displayed in case of mismatch.

It is recommended that the message is unique and that it contains the name of the signal or variable being checked. The message should NOT contain the expected value, because check() prints

that automatically.

data The signal or variable to be checked.

Supported types: integer, std\_logic, std\_logic\_vector, unsigned,

signed.

expected Expected value. Same type as data, or integer.

mask Bit mask and:ed to data and expected before comparison.

Optional if data is std\_logic\_vector. Not allowed for other types.

tolerance Allowed tolerance. Checks that

expected - tolerance  $\leq$  actual  $\leq$  expected + tolerance

is true.

expr boolean expression for checking.

This makes it possible to check any kind of expresion,

not just equality.

pltbv, pltbs PlTbUtils' status- and control variable and -signal.

## check\_binfile | check\_txtfile | check\_datfile

Checks that the contents of a file is equal to expected contents, by comparing with a reference file. If not equal, displays an error message and increments the error counter.

This is useful for examining different types of files generated by testbench components during a simulation against reference files. It can be different kinds of data sequences, video image data, etc.

check\_binfile compares two binary files. It uses "file of character" to read bytes from the files. The VHDL LRM does not define how a "file of character" should be written or to/read from disk. In theory, there is a risk that a VHDL file of character is not compatible with a normal binary file, but practical tests done with some popular simulators have shown that they are compatible. This does not guarantee that this procedure works with ALL simulators, and with ALL future versions of the tested simulators. Use your own judgement.

check\_txtfile compares two text files.

check\_datfile compares two files with data formatted as follows. The files contain a sequence of data items separated by whitespace (spaces, tabs, newlines). The files can contain comments starting with a hash sign (#), and ending at next newline.

Only the data items are compared. The types of whitespace and comments are ignored. This is useful for different kinds of data dumps, including some image file formats such as

Plain PBM (Portable Bit Map - P1, http://netpbm.sourceforge.net/doc/pbm.html) Plain PGM (Portable Gray Map - P2, http://netpbm.sourceforge.net/doc/pgm.html) Plain PPM (Portable Pixel Map - P3, http://netpbm.sourceforge.net/doc/ppm.html)

#### Arguments:

rpt Report message to be displayed in case of mismatch.

It is recommended that the message is unique and that it contains

the name of the signal or variable being checked.

filename Name of first file to be compared, including relative path from the

simulator's working directory.

filename2 Name of second file to be compared, including relative path from

the simulator's working directory.

verbosity Controls amount of individual error reports when differences

between files are found, to make it possible to prevent flooding

with error messages.

0: no individual differences reported1: the first ten differences reported

2: all differences reported

pltbv, pltbs PlTbUtils' status- and control variable and -signal.

```

check_binfile("Data output file", "out_file.bin", "ref_file.bin", 0,

pltbv, pltbs);

check_txtfile("Result file", G_RESULT_FILE, G_REF_FILE,

G_CHECKFILE_VEROBOSITY, pltbv, pltbs);

check_datfile("Resulting image", "result_img.ppm", "ref_img.ppm", 2,

pltbv, pltbs);

```

## to\_ascending

Converts a vector to ascending range ("to-range"). The argument s can have ascending or descending range. E.g. an argument defined as a std\_logic\_vector(3 downto 1) will be returned as a std\_logic\_vector(1 to 3).

#### Arguments:

s Constant, signal or variable to convert

Return value: Converted value

#### Examples:

```

ascending_sig <= to_ascending(descending_sig);

ascending_var := to_ascending(descending_var);</pre>

```

## to\_descending

Converts a vector to descending range ("downto-range"). The argument s can have ascending or descending range. E.g. an argument defined as a std\_logic\_vector(1 to 3) will be returned as a std\_logic\_vector(3 downto 1).

#### Arguments:

s Constant, signal or variable to convert

Return value: Converted value

```

descending_sig <= to_descending(ascending_sig);

descending_var := to_descending(ascending_var);</pre>

```

#### hxstr

Converts a vector to a string in hexadecimal format.

An optional prefix can be specified, e.g. "0x", as well as a suffix.

The input argument can have ascending range ("to-range") or descending range ("downto-range"). There is no vector length limitation.

Arguments:

```

s Constant, signal or variable to convert

```

Return value: Converted value

print("value=" & hxstr(s));

#### Examples:

Converts integer n to a string with fixed length len and leading fillchar.

## str\_equal

) return string;

```

function str_equal (

constant s1 : STRING;

constant s2 : STRING

) return boolean;

```

Returns true if strings s1 and s2 are equal, otherwise false.

The normal VHDL string comparison s1 = s2 only works correctly if the length of the strings are equal. str\_equal works even if the lengths differ.

## More functions and procedures in txt\_util.vhd

```

-- converts std logic into a character

function chr(sl: std logic) return character;

-- converts std logic into a string (1 to 1)

function str(sl: std logic) return string;

-- converts std logic vector into a string (binary base)

function str(slv: std logic vector) return string;

-- converts boolean into a string

function str(b: boolean) return string;

-- converts an integer into a single character

-- (can also be used for hex conversion and other bases)

function chr(int: integer) return character;

-- converts integer into string using specified base

function str(int: integer; base: integer) return string;

-- converts integer to string, using base 10

function str(int: integer) return string;

-- convert std logic vector into a string in hex format

-- NOTE: Argument limited to 32 bits. Consider hxstr(), see p 43.

function hstr(slv: std logic vector) return string;

-- functions to manipulate strings

-- convert a character to upper case

function to upper(c: character) return character;

-- convert a character to lower case

function to lower(c: character) return character;

-- convert a string to upper case

function to upper(s: string) return string;

-- convert a string to lower case

function to lower(s: string) return string;

-- checks if whitespace (JFF)

function is whitespace(c: character) return boolean;

-- remove leading whitespace (JFF)

function strip_whitespace(s: string) return string;

-- return first nonwhitespace substring (JFF)

function first string(s: string) return string;

```

```

-- finds the first non-whitespace substring in a string and (JFF)

-- returns both the substring and the original with the substring

procedure chomp(variable s: inout string; variable shead:

out string);

-- functions to convert strings into other formats

-- converts a character into std logic

function to std logic(c: character) return std logic;

-- converts a hex character into std logic vector (JFF)

function chr_to_slv(c: character) return std_logic_vector;

-- converts a character into int (JFF)

function chr to int(c: character) return integer;

-- converts a binary string into std logic vector

function to std logic vector(s: string) return std logic vector;

-- converts a hex string into std logic vector (JFF)

function hstr to slv(s: string) return std logic vector;

-- converts a decimal string into an integer (JFF)

function str to int(s: string) return integer;

-- file I/O

-- read variable length string from input file

procedure str read(file in file: TEXT;

res string: out string);

-- print string to a file and start new line

procedure print(file out file: TEXT;

new string: in string);

-- print character to a file and start new line

procedure print(file out_file: TEXT;

char: in character);

```

# **Testbench components**

## pltbutils\_clkgen

Creates a clock signal for use in a testbench. The clock stops when input port stop\_sim goes '1'. This makes the simulator stop (unless there are other infinite processes running in the simulation).

| Generic     | Type<br>Width | Description                                     |

|-------------|---------------|-------------------------------------------------|

| G_PERIOD    | time          | Clock period.                                   |

| G_INITVALUE | std_logic     | Initial value of the non-inverted clock output. |

| Port       | Type<br>Width | Dir | Description                                       |

|------------|---------------|-----|---------------------------------------------------|

| clk_o      | std_logic     | Out | Non-inverted clock output.                        |

|            |               |     | Use this output for single ended or differential  |

|            |               |     | clocks.                                           |

| clk_n_o    | std_logic     | Out | Inverted clock output.                            |

|            | _             |     | Use if a differential clock is needed, leave open |

|            |               |     | if single-ended clock is needed.                  |

| stop_sim_i | std_logic     | In  | When '1', stops the clock. This will normally     |

| _          |               |     | stop the simulation.                              |

# pltbutils\_time\_measure

Measures high-time, low-time and period of a signal, usually a clock. Setting G\_VERBOSITY to at least 20 reports measures times. Set G\_RPT\_LABEL to a prefix used in reports, typically the name of the signal being measured.

| Generic     | Type<br>Width | Description                |

|-------------|---------------|----------------------------|

| G_VERBOSITY | integer       | Controls amount of reports |

| G_RPT_LABEL | string        | Prefix used in reports     |

| Port    | Type<br>Width | Dir | Description       |

|---------|---------------|-----|-------------------|

| t_hi_o  | time          | Out | High time         |

| t_lo_o  | time          | Out | Low time          |

| t_per_o | time          | Out | Period time       |

| s_i     | std_logic     | In  | Signal to measure |

## pltbutils\_diff\_check

Checks that the negative half of a diff pair is the always the complement of the positive half. Setting G\_VERBOSITY to at least 100 reports number of diff errors. Set G\_RPT\_LABEL to a prefix used in reports, typically the name of the signal being measured.

| Generic     | Type<br>Width | Description                |

|-------------|---------------|----------------------------|

| G_VERBOSITY | integer       | Controls amount of reports |

| G_RPT_LABEL | string        | Prefix used in reports     |

| Port          | TypeWi    | Dir | Description                    |

|---------------|-----------|-----|--------------------------------|

|               | dth       |     |                                |

| diff_error_o  | std_logic | Out | High when diff error detected  |

| diff_errors_o | integer   | Out | Number of diff errors detected |

| s_i           | std_logic | In  | Pos half of diff pair to check |

| s_n_i         | std_logic | In  | Neg half of diff pair to check |

| rst_errors_i  | std_logic | In  | High resets diff error counter |