# RISC-V External Debug Support Version 0.9jan27

Tim Newsome

January 27, 2016

Warning! This draft specification will change before being accepted as standard, so implementations made to this draft specification will likely not conform to the future standard.

# Contents

| 1 | Intr | roduction                                     | 3              |

|---|------|-----------------------------------------------|----------------|

|   | 1.1  | Terminology                                   | 3              |

|   | 1.2  | Background                                    | 4              |

|   | 1.3  | Supported Features                            | 4              |

| 2 | Syst | tem Overview                                  | 5              |

| 3 | Deb  | oug Transport Module                          | 6              |

|   | 3.1  | System Bus Access                             | 6              |

|   | 3.2  | Interrupt Tracking                            | $\overline{7}$ |

|   | 3.3  | Serial Ports                                  | 7              |

|   | 3.4  | Security                                      | 7              |

|   | 3.5  | Debug Transport Module Registers              | 8              |

|   |      | 3.5.1 Interrupt (dtminterrupt, at $0x0$ )     | 8              |

|   |      | 3.5.2 Control (dtmcontrol, at $0x4$ )         | 9              |

|   |      |                                               | 10             |

|   |      |                                               | 11             |

|   |      | 3.5.5 Serial Send 0 (sersend0, at $0x20$ )    | 11             |

|   |      | 3.5.6 Serial Receive 0 (serrecv0, at $0x30$ ) | 11             |

|   |      | 3.5.7 Serial Status 0 (serstat0, at $0x40$ )  | 11             |

| 4 | Dev  | vice Tree Additions                           | 12             |

| 5 | Con  | nponent Debugging                             | 12             |

|   | 5.1  | Interrupt Tracking                            | 14             |

|   | 5.2  | Security                                      | 14             |

|   | 5.3  | Component Debug Registers                     | 14             |

|   |     | 5.3.1  | Component Control and Status (ccsr, at 0x0)     | 14        |

|---|-----|--------|-------------------------------------------------|-----------|

|   |     | 5.3.2  | Authentication Data (authdata, at 0x8)          | 17        |

|   |     | 5.3.3  | DTM Interrupt Address (cdtmaddress, at $0x10$ ) | 17        |

| 6 | RIS | C-V D  | Pebug Module                                    | 18        |

|   | 6.1 | Bus In | terface                                         | 18        |

|   | 6.2 | Debug  | Mode                                            | 18        |

|   | 6.3 | Debug  | Registers                                       | 18        |

|   |     | 6.3.1  | Component Control and Status $(ccsr, at 0x0)$   | 18        |

|   |     | 6.3.2  | DTM Interrupt Address (cdtmaddress, at 0x10)    | 21        |

|   |     | 6.3.3  | Debug Control and Status (dcsr, at 0x20)        | 21        |

|   |     | 6.3.4  | PC Sample (pcsample, at 0x30)                   | 22        |

|   |     | 6.3.5  | Stuff Instruction (dstuff, at 0x100)            | 22        |

|   |     | 6.3.6  | Debug Jump ( $djump$ , at $0x110$ )             | 23        |

|   |     | 6.3.7  | PC (dpc, at 0x120)                              | 23        |

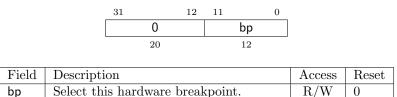

| 7 | Har | dware  | Breakpoint Module                               | 23        |

|   | 7.1 |        | are Breakpoint Registers                        | 24        |

|   |     | 7.1.1  | Breakpoint Select (bpselect, at 0x780)          | 24        |

|   |     | 7.1.2  | Breakpoint Control (bpcontrol, at 0x781)        | 24        |

|   |     | 7.1.3  | Breakpoint Low Address (bploaddr, at 0x782)     | 26        |

|   |     | 7.1.4  | Breakpoint High Address (bphiaddr, at 0x783)    | 26        |

|   |     | 7.1.5  | Breakpoint Low Data (bplodata, at 0x784)        | 27        |

|   |     | 7.1.6  | Breakpoint High Data (bphidata, at 0x785)       | 27        |

| 8 | Tra | ce Moo | dule                                            | <b>27</b> |

|   | 8.1 | Trace  | Data Format                                     | 28        |

|   | 8.2 | Trace  | Events                                          | 28        |

|   | 8.3 | Synchr | ronization                                      | 28        |

|   | 8.4 |        | Registers                                       | 28        |

|   |     | 8.4.1  | Trace (trace, at $0x788$ )                      | 28        |

|   |     | 8.4.2  | Trace Buffer Start (tbufstart, at 0x789)        | 32        |

|   |     | 8.4.3  | Trace Buffer End (tbufend, at 0x78a)            | 32        |

|   |     | 8.4.4  | Trace Buffer Write (tbufwrite, at $0x78b$ )     | 32        |

| 9 | JTA | G Deb  | bug Transport Agent                             | 32        |

|   | 9.1 |        | round                                           | 33        |

|   | 9.2 |        | Registers                                       | 33        |

|   |     | 9.2.1  | IDCODE (00001)                                  | 33        |

|   |     | 9.2.2  | DTM Control (dtmcontrol, at 10000)              | 33        |

|   |     | 9.2.3  | DTM Authentication Data (authdata, at 10001)    | 35        |

|   |     | 9.2.4  | JTAG Bus Control (jbusc, at 10010)              | 35        |

|   |     | 9.2.5  | JTAG Bus Address (jaddress, at 10011)           | 36        |

|   |     | 9.2.6  | JTAG Bus Data (jdata, at 10100)                 | 37        |

|   |     | 9.2.7  | JTAG Status (jstatus, at 10101)                 | 37        |

|   |     | 9.2.8  | JTAG Status Control (jstatc, at 10110)          | 38        |

|   |     |        |                                                 |           |

|   |            | 9.2.9  | JTAG Serial Data (jserial, at 10111)             |

|---|------------|--------|--------------------------------------------------|

|   |            | 9.2.10 | BYPASS (11111) 39                                |

| Α | Deb        | ugger  | Implementation 40                                |

|   | A.1        |        | 40                                               |

|   | A.2        | -      | ng Memory                                        |

|   | A.3        |        | g Memory 40                                      |

|   | A.4        |        | · · · · · · · · · · · · · · · · · · ·            |

|   | A.5        |        | ng Registers                                     |

|   | A.6        |        | g Registers                                      |

|   | A.7        |        | n Debug Programs 41                              |

|   | A.8        |        | ing Memory Through the Core                      |

|   |            |        | Read                                             |

|   |            |        | Write                                            |

|   | A.9        |        | ng                                               |

|   |            |        | Step                                             |

|   |            |        |                                                  |

| В | Deb        | -      | M Implementation 43                              |

|   | B.1        |        | are Changes                                      |

|   | B.2        | Debug  | ROM Registers                                    |

|   |            | B.2.1  | Bus State (busstate, at 0x770)                   |

|   |            | B.2.2  | Bus Address (busaddress, at $0x771$ ) 45         |

|   |            | B.2.3  | Bus Data (busdata, at 0x772) 45                  |

|   |            | B.2.4  | Debug PC (dpc, at 0x773)                         |

|   |            | B.2.5  | Debug Scratch 0 (dscratch0, at $0x774$ ) 45      |

|   |            | B.2.6  | Debug Scratch 1 (dscratch1, at $0x775$ ) 46      |

|   |            | B.2.7  | Debug Scratch 2 (dscratch2, at $0x776$ ) 46      |

|   |            | B.2.8  | Debug RAM Address (dramaddr, at 0x777) 46        |

|   |            | B.2.9  | Component Control and Status (ccsr, at 0x778) 46 |

|   |            |        | DTM Interrupt Address (cdtmaddress, at 0x779) 46 |

|   | <b>B.3</b> | Debug  | ROM Source                                       |

# 1 Introduction

Modern software contains bugs, and to help find these bugs it's critical to have good debugging tools. Unless you have a robust OS running on a core, and convenient access to it (eg. over a network interface), hardware support is required to provide visibility into what's going on in that core. This document outlines how that support should be provided on RISC-V cores.

# 1.1 Terminology

A platform is a single integrated circuit consisting of one or more components. Some components may be RISC-V cores, while others may have a different function. Typically they will all be connected to a single system bus.

### 1.2 Background

There are two forms of external debugging. The first is halt/freeze mode debugging, where an external debugger will halt some or all components of a platform and inspect them while everything is in stasis. Then the debugger can either let the hardware perform a single step or let it run freely. The second is run mode debugging. In this mode there is some debug agent running on a component (eg. triggered by a timer interrupt on a RISC-V core) which communicates with a debugger without halting the component. This is essential if the component is controlling some real-time system (like a hard drive) where halting the component might lead to physical damage. It requires more software support (both on the chip as well as on the debug client). For this use case the debug interface may include simple serial ports.

There's a third use for the external debug interface, which is to use it as a general transport for a component to communicate with the outside world. For instance, it could be used to implement a serial interface that firmware could use to provide a simple CLI. This can use the same serial ports used for run-mode debugging.

### **1.3 Supported Features**

The debug interface laid out here supports the following features:

- 1. Any component in the platform can be independently debugged.

- 2. Any core can be debugged just by using the system bus (unless a dedicated debug bus is used).

- 3. It's not necessary for a debugger to poll a component's state to see whether it has halted/has completed something.

- 4. More than one debug transport can be used. They all use a common system bus protocol to communicate with components being debugged.

- 5. Arbitrary instructions can be executed on a halted RISC-V core.

- 6. Data can be transferred between a RISC-V core and the debugger without relying on shared RAM.

- 7. The debug transport may implement serial ports which can be used for communication between debugger and monitor, or as a general protocol between debugger and application.

- 8. Code can be downloaded efficiently.

- 9. Each core can be debugged from very first instruction executed.

- 10. A RISC-V core can be halted when a software breakpoint instruction is executed.

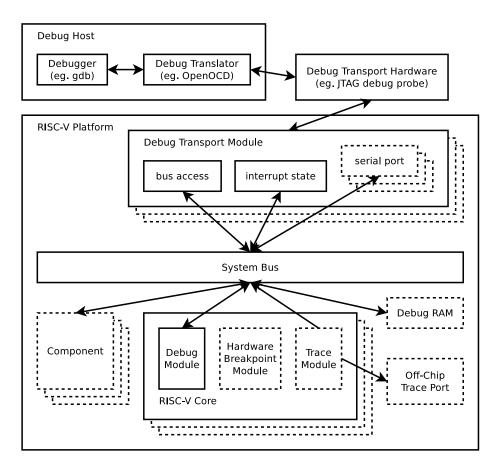

Figure 1: RISC-V Debug System Overview

- 11. A RISC-V core can be halted when a hardware breakpoint matches PC, or read/write address/data.

- 12. A RISC-V core can store an execution trace to on- or off-chip RAM.

- 13. The core can execute code while remaining in Debug Mode.

- 14. It's always possible to halt a RISC-V core, even if some other component is writing all over the system bus.

# 2 System Overview

Figure 1 shows the main components of External Debug Support. Blocks shown in dotted lines are optional.

The user interacts with the Debug Host, which is running a debugger. The debugger communicates with a Debug Translator (which may include a hard-

ware driver) to communicate with Debug Transport Hardware that's connected to the host. That hardware is also connected to the Platform, which contains a Debug Transport Module.

The Debug Transport Module provides bus access, keeps track of simple interrupts, and may implement serial ports to facilitate communication between code running on the core and the debugger. This bus could be the system bus as depicted, or a dedicated debug bus. Any component that supports some basic features may be debugged over that bus. For RISC-V cores, the Debug Module controls most debug features. Additionally there may be a Hardware Breakpoint Module and a Trace Module that can write trace information to the System Bus or an off-chip trace port.

The platform may contain a Debug RAM to be used when debugging RISC-V cores.

# 3 Debug Transport Module

Debug Transport Modules provide access to the system bus over one or more transports (eg. JTAG or USB). They also implement a simple interrupt tracking feature that helps notify debuggers of component updates without them having to poll over the system bus. Finally they may implement some serial ports.

There may be multiple DTMs in a single platform. Ideally every component that communicates with the outside world includes a DTM, allowing a platform to be debugged through every transport it supports. For instance a USB component would include a Debug Transport Module. This would trivially allow any platform where the system bus is used as the debug bus to be debugged over USB.

#### 3.1 System Bus Access

While the details are left completely to the transport-specific Debug Transport Module, every DTM must support all accesses from the following list that the system bus supports: 8-bit read/write, 16-bit read/write, 32-bit read/write, 64-bit read/write, and 128-bit read/write to arbitrary addresses on the system bus.

In addition, DTM designers should keep the following common use cases in mind:

- 1. XLEN-bit reads from consecutive addresses.

- 2. XLEN-bit writes to consecutive addresses.

- 3. Repeatedly read and write XLEN bits at addresses that are adjacent or very close.

Some implementations may decide they don't want debug accesses to use the system bus. Instead they may run a dedicated debug bus through the platform. This has the benefit that debugging does not interfere at all with other execution, and there is no need to make RISC-V cores system bus slaves. The downsides are that an extra bus needs to be run, and it's not possible to debug a component from anything but the DTM. On a small platform with a single RISC-V core it makes sense to have a dedicated debug bus (which can be very simple if there is just a single DTM and a single component to be debugged). For more complex platforms, implementers will likely choose to use the system bus.

The existence of a dedicated debug bus is transparent to the debugger. The DTM simply designates part of the address space (only when accessed by the DTM) as debug bus space. This address space should not mask a device that a debugger might conceivably want to access. If there is no address space available to fit the debug bus in, the DTM must add another address bit which is used to select the debug bus (when 1) or the system bus (when 0).

### 3.2 Interrupt Tracking

To avoid a debugger constantly polling the components it's interested in (cluttering up the system bus), very simple interrupt mechanism is supported. It consists of a single register where components can set bits by writing the bit's index to a register in the DTM. The width of this register is implementationspecific. It must be at least 1 bit wide. Sensible widths are the number of debuggable components in the platform, and the width of the data bus. When a bit becomes set, the DTM should communicate that to the debugger as soon as possible.

This mechanism exists so components can let the debugger know they are now halted (eg. because a breakpoint was hit), but may have other uses. Which interrupt each component uses is configurable by the debugger by writing the component's interrupt in ccsr.

### 3.3 Serial Ports

Each DTM may implement up to 8 serial ports. They support basic flow control and full duplex data transfer between a component and the debugger. They're intended to be used for the equivalent of printf debugging, or to provide a simple CLI without requiring any extra peripherals.

#### 3.4 Security

It may be necessary to prevent just anyone from accessing the debug interface. One option could be to add a fuse bit to the DTM that can be used to be permanently disable it. Since this is transport and technology specific, it is not further addressed in this spec.

Another option is to allow the DTM to be unlocked only by people who have the key. A simple mechanism is documented in Section 3.5. When authenticated is clear, the DTM must not perform any System Bus accesses, as well as prevent all external access to the serial ports and interrupt state.

# 3.5 Debug Transport Module Registers

| e 1: Debug       | Transport Module Regi |

|------------------|-----------------------|

| Address          | Name                  |

| 0x0              | Interrupt             |

| 0x4              | Control               |

| 0x8              | Authentication Data   |

| 0x10             | Serial Info           |

| 0x20             | Serial Send 0         |

| 0x30             | Serial Receive 0      |

| 0x40             | Serial Status 0       |

| 0x50             | Serial Send 1         |

| 0x60             | Serial Receive 1      |

| 0x70             | Serial Status 1       |

| 0x80             | Serial Send 2         |

| 0x90             | Serial Receive 2      |

| $0 \mathrm{xa0}$ | Serial Status 2       |

| 0 xb 0           | Serial Send 3         |

| 0xc0             | Serial Receive 3      |

| 0 x d0           | Serial Status 3       |

| 0xf0             | Serial Send 4         |

| 0x100            | Serial Receive 4      |

| 0x110            | Serial Status 4       |

| 0x120            | Serial Send 5         |

| 0x130            | Serial Receive 5      |

| 0x140            | Serial Status 5       |

| 0x150            | Serial Send 6         |

| 0x160            | Serial Receive 6      |

| 0x170            | Serial Status 6       |

| 0x180            | Serial Send 7         |

| 0x190            | Serial Receive 7      |

| 0x1a0            | Serial Status 7       |

|                  |                       |

Table 1: Debug Transport Module Registers

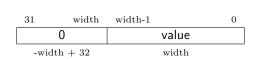

# 3.5.1 Interrupt (dtminterrupt, at 0x0)

Writes to this register set bits in the internal interrupt state.

| Field | Description                                 | Access | Reset |

|-------|---------------------------------------------|--------|-------|

| value | A write of value N sets bit N. The width    | W      | 0     |

|       | of this register depends on the width of    |        |       |

|       | the internal interrupt register. (Eg. it's  |        |       |

|       | 5 bits wide if the internal internal regis- |        |       |

|       | ter is 32 bits wide.)                       |        |       |

# 3.5.2 Control (dtmcontrol, at 0x4)

| 31         | 24 | 23 | 23 21 20 19 18 |               | 17       | 16   |          |         |           |

|------------|----|----|----------------|---------------|----------|------|----------|---------|-----------|

| abussize 0 |    | 0  | access128      | accessб4      | acce     | ss32 | access16 | access8 |           |

| 8 3        |    | 3  | 1              | 1             |          | 1    | 1        | 1       |           |

| 15 8 7 6 5 |    | 5  | 4              | 3             | 2        | 1    | 0        |         |           |

| intbits    |    | 0  | ;              | authenticated | authbusy | ′ au | thtype   | ndreset | fullreset |

| <br>8      |    | 2  |                | 1             | 1        |      | 2        | 1       | 1         |

| Field         | Description                                | Access    | Reset                  |  |  |  |  |

|---------------|--------------------------------------------|-----------|------------------------|--|--|--|--|

| abussize      | Width of the address bus in bits. (This    | R         | Preset                 |  |  |  |  |

|               | includes the extra address bit if it's re- |           |                        |  |  |  |  |

|               | quired to access the debug bus.)           |           |                        |  |  |  |  |

| access128     | 1 when 128-bit bus accesses are sup-       | R         | Preset                 |  |  |  |  |

|               | ported.                                    |           |                        |  |  |  |  |

| access64      | 1 when 64-bit bus accesses are sup-        | R         | Preset                 |  |  |  |  |

|               | ported.                                    |           |                        |  |  |  |  |

| access32      | 1 when 32-bit bus accesses are sup-        | R         | Preset                 |  |  |  |  |

|               | ported.                                    |           |                        |  |  |  |  |

| access16      | 1 when 16-bit bus accesses are sup-        | R         | Preset                 |  |  |  |  |

|               | ported.                                    |           |                        |  |  |  |  |

| access8       | 1 when 8-bit bus accesses are supported.   | R         | Preset                 |  |  |  |  |

| intbits       | The width of the internal interrupt state  | R         | Preset                 |  |  |  |  |

|               | is intbits $+1$ .                          |           |                        |  |  |  |  |

| authenticated | 0 when authentication is required before   | R         | Preset                 |  |  |  |  |

|               | using the DTM. 1 when the authenti-        |           |                        |  |  |  |  |

|               | cation check has passed. On compo-         |           |                        |  |  |  |  |

|               | nents that don't implement authentica-     |           |                        |  |  |  |  |

|               | tion, this bit must be preset as 1.        |           |                        |  |  |  |  |

|               | Contin                                     | ued on ne | Continued on next page |  |  |  |  |

| authbusy  | While 1, writes to <b>authdata</b> may be<br>ignored or may result in authentica-<br>tion failing. Authentication mecha-<br>nisms that are slow (or intentionally de-<br>layed) must set this bit when they're not<br>ready to process another write.                                                              | R | 0      |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------|

| authtype  | Defines the kind of authentication re-<br>quired to use this DTM. 0 means no au-<br>thentication is required. 1 means a pass-<br>word is required. 2 means a challenge-<br>response mechanism is in place. 3 is re-<br>served for future use.                                                                      | R | Preset |

| ndreset   | Every time this bit is written as 1, it<br>triggers a full reset of the non-debug<br>logic on the platform. This bit exists<br>so that, for debugging purposes, reset<br>behavior can be different from the stan-<br>dard behavior. For instance, a core<br>could be forced into Debug Mode right<br>out of reset. | W | 0      |

| fullreset | Every time this bit is written as 1, it<br>triggers a full reset of the platform, in-<br>cluding every component in it and the<br>debug logic for each component. It also<br>resets the DTM itself.                                                                                                                | W | 0      |

### 3.5.3 Authentication Data (authdata, at 0x8)

If authtype is 0, this register is not present.

If authtype is 1, writing a correct password to this register enables the DTM. The DTM is disabled either by writing an invalid password, or by resetting it. 0 must not be used as a password. Reading from the register returns 0.

If authtype is 2, things are a bit more complicated. Reading from the register reads the last challenge generated. Writing the correct response enables the DTM. The DTM is disabled either by writing an incorrect response, or by resetting it. Writing an incorrect response causes a new challenge to be generated. Depending on the implementation, there may not be a valid challenge until the first write to this register.

### 3.5.4 Serial Info (serinfo, at 0x10)

| 31 |    | 16    | 15 | 14     | 13 | 3      | 12    | 11  | 10     | 9    | 8    |

|----|----|-------|----|--------|----|--------|-------|-----|--------|------|------|

|    | 0  |       | S  | erial7 |    | serial | 6     | ser | ial5   | seri | ial4 |

|    | 16 |       |    | 2      |    | 2      |       |     | 2      | 2    | 2    |

|    |    | 7     | 6  | 5      | 4  | 3      | 2     | 1   | 0      |      |      |

|    |    | seria | 13 | serial | 2  | ser    | rial1 | S   | erial0 | 7    |      |

|    |    | 2     |    | 2      |    |        | 2     |     | 2      | _    |      |

| Field   | Description                               | Access | Reset  |

|---------|-------------------------------------------|--------|--------|

| serial7 | Like serial0.                             | R      | Preset |

| serial6 | Like serial0.                             | R      | Preset |

| serial5 | Like serial0.                             | R      | Preset |

| serial4 | Like serial0.                             | R      | Preset |

| serial3 | Like serial0.                             | R      | Preset |

| serial2 | Like serial0.                             | R      | Preset |

| serial1 | Like serial0.                             | R      | Preset |

| serial0 | 0 means serial interface 0 is not sup-    | R      | Preset |

|         | ported. 1 means serial interface 0 is     |        |        |

|         | supported and 32 bits wide. 2 means se-   |        |        |

|         | rial interface 0 is supported and 64 bits |        |        |

|         | wide. 3 means serial interface 0 is sup-  |        |        |

|         | ported and 128 bits wide.                 |        |        |

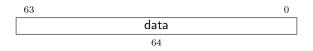

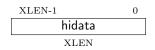

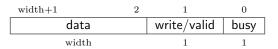

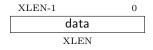

### 3.5.5 Serial Send 0 (sersend0, at 0x20)

Values written to this address are added to the send queue, unless the queue is already full.

| width-1 | 0 |

|---------|---|

| data    |   |

| width   |   |

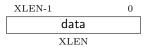

### 3.5.6 Serial Receive 0 (serrecv0, at 0x30)

This register contains the oldest value in the receive queue. Reading the register removes that value from the queue. If the queue is empty, reading this register returns an undefined value.

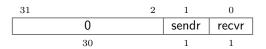

### 3.5.7 Serial Status 0 (serstat0, at 0x40)

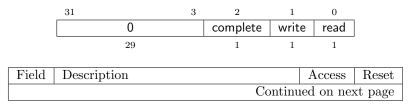

| Field | Description                             | Access | Reset |

|-------|-----------------------------------------|--------|-------|

| sendr | Send ready. 1 when the send queue is    | R      | 1     |

|       | not full. 0 otherwise.                  |        |       |

| recvr | Receive ready. 1 when the receive queue | R      | 1     |

|       | is not empty. 0 otherwise.              |        |       |

# 4 Device Tree Additions

The device tree is a data structure in ROM that all RISC-V platforms should have. It contains a variety of information about every component in the platform. (As of January 16, 2016 it is not yet part of any RISC-V spec.)

Every debuggable component should implement any applicable properties listed in Table 2 in the device tree.

|                     | 1 1                                     |          |

|---------------------|-----------------------------------------|----------|

| riscv,debug-address | Address of this component's ccsr        | Required |

|                     | register.                               |          |

| riscv,auth-type     | Defines the kind of authentication      | Optional |

|                     | required to use the debug logic on this |          |

|                     | component. 0 means no                   |          |

|                     | authentication is required. 1 means a   |          |

|                     | password is required. 2 means a         |          |

|                     | challenge-response mechanism is in      |          |

|                     | place. Other values are reserved for    |          |

|                     | future use.                             |          |

Table 2: Component Device Tree Properties

If a Debug RAM is implemented, it must be listed in the device tree with its start address and size.

Each DTM must be listed in the device tree including its base address (address of dtminterrupt).

TODO: Update this section once there is a more general RISC-V device tree spec.

# 5 Component Debugging

Every component can expose arbitrary functionality as registers visible to the Debug Transport Module on the debug/system bus. This document only specifies in detail what RISC-V cores must expose.

There are a few generic features specified that any component can implement, and that even a debugger that knows nothing else about that component can use. The simplest is to freeze a component. Freezing is the simplest form of halting, effectively the same as gating the clock to a component. It should also be possible to just let the component run for a single clock cycle. Freezing a RISC-V core might allow a debugger to inspect the state of the pipeline.

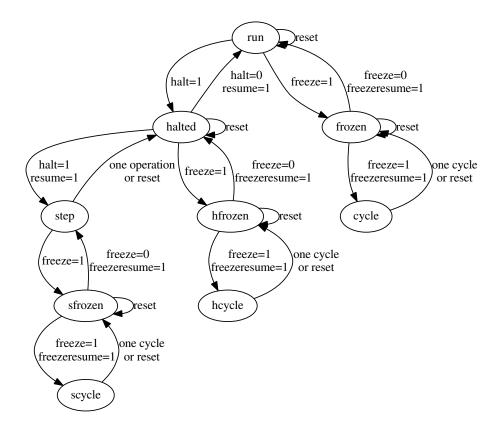

Figure 2: Component Run States

Components that support freezing must implement freeze and freezeresume in ccsr.

A more complicated alternative to freezing is halting. Halting usually happens on a boundary that is meaningful (eg. an instruction being fetched or completely executed), and may even put the component into a special Debug Mode. When a RISC-V core is halted, it's possible to let the core execute arbitrary instructions. It should also be possible to let the component take a meaningful step (eg. execute a single instruction). Components that support halting must implement halt and resume in ccsr. Their use is summarized in Figure 2.

Freezing and halting are orthogonal to each other, so a component may be both frozen and halted. In this case freezing could be used to debug halting.

In addition to freezing and halting, there are also 2 kinds of reset supported: The first is a traditional reset that resets the entire component. The second is a non-debug reset, which only resets that part of the component that are not part of the debug logic. The second is used so you can reset a component but remain halted/frozen.

### 5.1 Interrupt Tracking

When cdisable is clear, a component can send an interrupt to the DTM by writing interrupt to dtminterrupt as described in Section 3.2.

### 5.2 Security

Some components may contain intellectrual property that should not be disclosed, even to people who may debug other parts of the system. To help with this there are registers specified to support a simple authentication scheme that enables an authorized debugger to unlock the debug logic on a component.

This mechanism does not affect accesses over the system bus at all. It's up to the component designer to ensure that no IP is leaked over the system bus. This could be done by carefully designing the interface, or by only granting components that really need it the relevant system bus access. The latter option depends on the system bus to support that kind of functionality, and additionally requires that the components that have access be similarly secured.

### 5.3 Component Debug Registers

Table 3: Component Debug Registers

| Address | Name                         |

|---------|------------------------------|

| 0x0     | Component Control and Status |

| 0x8     | Authentication Data          |

|         | DTM Interrupt Address        |

#### 5.3.1 Component Control and Status (ccsr, at 0x0)

See Figure 2 for more information about how freeze, halt, and reset bits interact.

| 31          |        | 30      | 29 2   | 8  | 27      |      | 26      |       | 25        |

|-------------|--------|---------|--------|----|---------|------|---------|-------|-----------|

| authenticat | ed au  | ithbusy | 0      |    | ndreset |      | fullres | set   | stopcycle |

| 1           |        | 1       | 2      |    | 1       |      | 1       |       | 1         |

| 24          | 23     |         | 22     |    | 21      |      | 20      |       | 19        |

| stoptime    | froze  | n free  | ezesup | fr | reeze   | free | ezeresu | ime   | halted    |

| 1           | 1      |         | 1      |    | 1       |      | 1       |       | 1         |

|             | 18     | 17      | 16     |    | 15      | 8    | 7       | 0     |           |

| ha          | altsup | halt    | resume | 5  | 0       |      | inte    | rrupt |           |

|             | 1      | 1       | 1      |    | 8       |      |         | 8     |           |

| Field         | Description                               | Access    | Reset    |

|---------------|-------------------------------------------|-----------|----------|

| authenticated | 0 when authentication is required before  | R         | Preset   |

|               | talking to the debug interface on this    |           |          |

|               | component. 1 when the authentication      |           |          |

|               | check has passed. On components that      |           |          |

|               | don't implement authentication, this bit  |           |          |

|               | must be preset as 1.                      |           |          |

| authbusy      | While 1, writes to authdata may be        | R         | 0        |

| 5             | ignored or may result in authentica-      |           |          |

|               | tion failing. Authentication mecha-       |           |          |

|               | nisms that are slow (or intentionally de- |           |          |

|               | layed) must set this bit when they're not |           |          |

|               | ready to process another write.           |           |          |

| ndreset       | Every time this bit is written as 1, it   | W         | 0        |

|               | triggers a reset of the non-debug logic   |           |          |

|               | in this component.                        |           |          |

| fullreset     | Every time this bit is written as 1, it   | W         | 0        |

|               | triggers a reset of the component includ- |           |          |

|               | ing the debug logic.                      |           |          |

| stopcycle     | Controls the behavior of any counters     | R/W       | 1        |

|               | while the component is halted. When       | ,         |          |

|               | 1, counters are stopped when the com-     |           |          |

|               | ponent is halted/frozen. Otherwise, the   |           |          |

|               | counters continue to run.                 |           |          |

|               | An implementation may choose not to       |           |          |

|               | support writing to this bit. The debug-   |           |          |

|               | ger must read back the value it writes to |           |          |

|               | check whether the feature is supported.   |           |          |

|               |                                           | ued on ne | ext page |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        | -           |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|

| stoptime       | Controls the behavior of any timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W    | 0           |

|                | while the component is halted. When 1,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |             |

|                | timers are stopped when the component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |             |

|                | is halted/frozen. Otherwise, the timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |             |

|                | continue to run.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |             |

|                | An implementation may choose not to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |             |

|                | support writing to this bit. The debug-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |             |

|                | ger must read back the value it writes to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |             |

|                | check whether the feature is supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |             |

| frozen         | 1 when the component is currently                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R      | 0           |

|                | frozen.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |             |

| freezesup      | 1 when freeze and freezeresume are sup-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R      | Preset      |

|                | ported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |             |

| freeze         | When this bit is 1 and the component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W    | 0           |

|                | is not frozen, it becomes frozen.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |             |

|                | If this bit is 1 when the component is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |             |

|                | reset, the component should be frozen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |             |

|                | before it has performed any operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |             |

|                | If this bit is 1 when the freezeresume is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |             |

|                | written as 1, the component will only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |             |

|                | execute a single cycle before becoming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |             |

|                | frozen again.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |             |

|                | Setting this bit to 0 does not have an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |             |

|                | immediate effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |             |

| freezeresume   | If this bit is written as 1 while the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | W1     | 0           |

| Incereiesung   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11 I   |             |

| incezeresuille | component is frozen, the component be-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |             |

| incezeresuille | component is frozen, the component be-<br>comes unfrozen.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ** 1   |             |

| halted         | comes unfrozen.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R      | 0           |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        | 0           |

|                | comes unfrozen.1 when the component is currently                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | 0<br>Preset |

| halted         | comes unfrozen.<br>1 when the component is currently<br>halted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R      |             |

| halted         | <ul><li>comes unfrozen.</li><li>1 when the component is currently halted.</li><li>1 when halt and resume are supported.</li><li>When this bit is 1 and the component</li></ul>                                                                                                                                                                                                                                                                                                                                                                                       | R<br>R | Preset      |

| halted         | <ul><li>comes unfrozen.</li><li>1 when the component is currently halted.</li><li>1 when halt and resume are supported.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                    | R<br>R | Preset      |

| halted         | <ul> <li>comes unfrozen.</li> <li>1 when the component is currently halted.</li> <li>1 when halt and resume are supported.</li> <li>When this bit is 1 and the component is not halted, the component will enter Debug Mode.</li> </ul>                                                                                                                                                                                                                                                                                                                              | R<br>R | Preset      |

| halted         | <ul> <li>comes unfrozen.</li> <li>1 when the component is currently halted.</li> <li>1 when halt and resume are supported.</li> <li>When this bit is 1 and the component is not halted, the component will enter Debug Mode.</li> <li>If this bit is 1 when the component is</li> </ul>                                                                                                                                                                                                                                                                              | R<br>R | Preset      |

| halted         | <ul> <li>comes unfrozen.</li> <li>1 when the component is currently halted.</li> <li>1 when halt and resume are supported.</li> <li>When this bit is 1 and the component is not halted, the component will enter Debug Mode.</li> </ul>                                                                                                                                                                                                                                                                                                                              | R<br>R | Preset      |

| halted         | <ul> <li>comes unfrozen.</li> <li>1 when the component is currently halted.</li> <li>1 when halt and resume are supported.</li> <li>When this bit is 1 and the component is not halted, the component will enter Debug Mode.</li> <li>If this bit is 1 when the component is reset, the component must go directly</li> </ul>                                                                                                                                                                                                                                        | R<br>R | Preset      |

| halted         | <ul> <li>comes unfrozen.</li> <li>1 when the component is currently halted.</li> <li>1 when halt and resume are supported.</li> <li>When this bit is 1 and the component is not halted, the component will enter Debug Mode.</li> <li>If this bit is 1 when the component is reset, the component must go directly to Debug Mode.</li> </ul>                                                                                                                                                                                                                         | R<br>R | Preset      |

| halted         | <ul> <li>comes unfrozen.</li> <li>1 when the component is currently halted.</li> <li>1 when halt and resume are supported.</li> <li>When this bit is 1 and the component is not halted, the component will enter Debug Mode.</li> <li>If this bit is 1 when the component is reset, the component must go directly to Debug Mode.</li> <li>If this bit is 1 when the component</li> </ul>                                                                                                                                                                            | R<br>R | Preset      |

| halted         | <ul> <li>comes unfrozen.</li> <li>1 when the component is currently halted.</li> <li>1 when halt and resume are supported.</li> <li>When this bit is 1 and the component is not halted, the component will enter Debug Mode.</li> <li>If this bit is 1 when the component is reset, the component must go directly to Debug Mode.</li> <li>If this bit is 1 when the component leaves Debug Mode, the component will</li> </ul>                                                                                                                                      | R<br>R | Preset      |

| halted         | <ul> <li>comes unfrozen.</li> <li>1 when the component is currently halted.</li> <li>1 when halt and resume are supported.</li> <li>When this bit is 1 and the component is not halted, the component will enter Debug Mode.</li> <li>If this bit is 1 when the component is reset, the component must go directly to Debug Mode.</li> <li>If this bit is 1 when the component leaves Debug Mode, the component will perform one operation (eg. execute a</li> </ul>                                                                                                 | R<br>R | Preset      |

| halted         | <ul> <li>comes unfrozen.</li> <li>1 when the component is currently halted.</li> <li>1 when halt and resume are supported.</li> <li>When this bit is 1 and the component is not halted, the component will enter Debug Mode.</li> <li>If this bit is 1 when the component is reset, the component must go directly to Debug Mode.</li> <li>If this bit is 1 when the component leaves Debug Mode, the component will perform one operation (eg. execute a single instruction, or perform a single</li> </ul>                                                         | R<br>R | Preset      |

| halted         | <ul> <li>comes unfrozen.</li> <li>1 when the component is currently halted.</li> <li>1 when halt and resume are supported.</li> <li>When this bit is 1 and the component is not halted, the component will enter Debug Mode.</li> <li>If this bit is 1 when the component is reset, the component must go directly to Debug Mode.</li> <li>If this bit is 1 when the component leaves Debug Mode, the component will perform one operation (eg. execute a single instruction, or perform a single cycle in a state machine) before re-</li> </ul>                    | R<br>R | Preset      |

| halted         | <ul> <li>comes unfrozen.</li> <li>1 when the component is currently halted.</li> <li>1 when halt and resume are supported.</li> <li>When this bit is 1 and the component is not halted, the component will enter Debug Mode.</li> <li>If this bit is 1 when the component is reset, the component must go directly to Debug Mode.</li> <li>If this bit is 1 when the component leaves Debug Mode, the component will perform one operation (eg. execute a single instruction, or perform a single cycle in a state machine) before reentering Debug Mode.</li> </ul> | R<br>R | Preset      |

| resume    | If this bit is written as 1 while the com- | W1  | 0      |

|-----------|--------------------------------------------|-----|--------|

|           | ponent is in Debug Mode, the compo-        |     |        |

|           | nent leaves Debug Mode.                    |     |        |

| interrupt | The value this component should use        | R/W | Preset |

|           | when writing to dtminterrupt.              |     |        |

|           | Depending on intbits in the DTM, the       |     |        |

|           | top bits of this field may be hardwired    |     |        |

|           | to 0.                                      |     |        |

|           | This value may be hardcoded if there       |     |        |

|           | are few components in the system. The      |     |        |

|           | debugger must read this value back af-     |     |        |

|           | ter writing it to confirm whether it was   |     |        |

|           | written or not.                            |     |        |

#### 5.3.2 Authentication Data (authdata, at 0x8)

If authtype is 0, this register is ignored.

If authtype is 1, writing a correct password to this register enables the debug functionality. The functionality is disabled either by writing an invalid password, or by resetting it. 0 should not be used as a password. Reading from the register returns 0.

If authtype is 2, things are a bit more complicated. Reading from the register reads the last challenge generated. Writing the correct response enables the debug functionality. The functionality is disabled either by writing an incorrect response, or by resetting it. Writing an incorrect response causes a new challenge to be generated. Depending on the implementation, there may not be a valid challenge until the first write to this register.

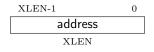

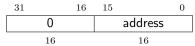

#### 5.3.3 DTM Interrupt Address (cdtmaddress, at 0x10)

On platforms with only a single DTM, this register may be read-only, pointed at that DTM.

| abussize-1   | 1 | 0        |

|--------------|---|----------|

| dtmaddress   |   | cdisable |

| abussize - 1 |   | 1        |

| Field      | Description                             | Access | Reset  |

|------------|-----------------------------------------|--------|--------|

| dtmaddress | Bits abussize-1:1 of the address of     | R/W    | Preset |

|            | dtminterrupt. On some components        |        |        |

|            | this register will be less wide than    |        |        |

|            | abussize. In order for those components |        |        |

|            | to send messages to the DTM, the DTM    |        |        |

|            | needs to be accessible to them using    |        |        |

|            | however many address bits (often 32)    |        |        |

|            | that actually fit in the register.      |        |        |

| cdisable   | When 1, the component won't write       | R/W    | Preset |

|            | anything to the DTM. Set to 0 to enable |        |        |

|            | the component writing to the DTM.       |        |        |

# 6 RISC-V Debug Module

### 6.1 Bus Interface

Each RISC-V debug module uses 17 bits of address space on the debug/system bus to provide access to debug features. The address space is divided up as show in Table 4.

### 6.2 Debug Mode

Debug Mode is a special processor mode used only when the core is halted for external debugging.

When entering Debug Mode:

1. The core should write its interrupt number to the DTM's dtminterrupt.

While in Debug Mode:

- 1. Regular program execution is suspended.

- 2. The contents of general purpose registers are accessible over the debug interface.

- 3. All operations happen in machine mode.

- 4. All interrupts are masked.

- 5. No hardware breakpoints are triggered.

- 6. Trace is disabled.

When leaving Debug Mode:

1. Regular program execution resumes at the address in dpc.

### 6.3 Debug Registers

### 6.3.1 Component Control and Status (ccsr, at 0x0)

This is the exact same register as is described in Section 5.3.1, but the description here is slightly more specific to RISC-V cores.

|                   | Table 4: Debug bus Memory Space                             |

|-------------------|-------------------------------------------------------------|

| Address           | Value                                                       |

| 0x0000 - 0x0100   | Debug registers described in Section 6.3. These are         |

|                   | always accessible.                                          |

| 0x0100 - 0x01c3   | Debug registers described in Section 6.3. These are only    |

|                   | be accessible when the core is halted.                      |

| 0x01c4 - 0x01ff   | Supported register map. This indicates which registers      |

|                   | are directly accessible to a debugger. Each register gets   |

|                   | a single bit, so each 32-bit word maps to 256 bytes of      |

|                   | address space starting at 0x100. The LSB in each word       |

|                   | maps to the first 128-bit word in its 256-byte space.       |

|                   | Since the general purpose registers must always be          |

|                   | supported, the word at 0xc4 always contains 0xfffffff.      |

|                   | These may only be accessible if the core is halted.         |

| 0x0200 - 0x03ff   | General purpose registers (x0-x31), each 16 bytes in        |

|                   | size.                                                       |

|                   | These may only be accessible if the core is halted.         |

| 0x0400 - 0x05ff   | Floating point registers (f0-f31), each 16 bytes in size.   |

|                   | (Optional, even when floating point is supported by the     |

|                   | core.)                                                      |

|                   | These may only be accessible if the core is halted.         |

| 0x0600 - 0x3fff   | Reserved for future official extensions.                    |

| 0x4000 - 0x7fff   | Reserved for future debug standards.                        |

| 0x8000 - 0xffff   | Reserved for custom use to support platform-specific        |

|                   | functions.                                                  |

| 0x10000 - 0x1ffff | CSR registers. Each CSR register gets 16 bytes of           |

|                   | space, to make it look like the registers are just laid out |

|                   | in a contiguous memory section (assuming they're all        |

|                   | 128 bits in size).                                          |

|                   | While halted, all registers must be accessible. When        |

|                   | not halted, some or all registers may not be accessible.    |

Table 4: Debug Bus Memory Space

Table 5: Debug Bus Registers

| Address | Name                         |

|---------|------------------------------|

| 0x0     | Component Control and Status |

| 0x10    | DTM Interrupt Address        |

| 0x20    | Debug Control and Status     |

| 0x30    | PC Sample                    |

| 0x100   | Stuff Instruction            |

| 0x110   | Debug Jump                   |

| 0x120   | PC                           |

| 31           | 3       | 30       | 29 28  | 3 27   |         | 26      | 25        |

|--------------|---------|----------|--------|--------|---------|---------|-----------|

| authenticate | ed auth | authbusy |        | ndres  | ndreset |         | stopcycle |

| 1            |         | 1        | 2      | 1      |         | 1       | 1         |

| 24           | 23      | 2        | 22     | 21     |         | 20      | 19        |

| stoptime     | frozen  | freez    | zesup  | freeze | free    | zeresum | e halted  |

| 1            | 1       |          | 1      | 1      |         | 1       | 1         |

|              | 18      | 17       | 16     | 15     | 8       | 7       | 0         |

| ha           | ltsup h | alt      | resume | 0      |         | interru | ıpt       |

|              | 1       | 1        | 1      | 8      |         | 8       |           |

| Field         | Description                               | Access    | Reset    |

|---------------|-------------------------------------------|-----------|----------|

| authenticated | See Section 5.3.1.                        | R         | Preset   |

| authbusy      | See Section 5.3.1.                        | R         | 0        |

| ndreset       | See Section 5.3.1.                        | W         | 0        |

| fullreset     | See Section 5.3.1.                        | W         | 0        |

| stopcycle     | Controls the behavior of any counters     | R/W       | 1        |

|               | while the component is halted. This in-   |           |          |

|               | cludes the counters read with rdcycle     |           |          |

|               | and rdinstret. When 1, counters are       |           |          |

|               | stopped when the component is halt-       |           |          |

|               | ed/frozen. Otherwise, the counters con-   |           |          |

|               | tinue to run.                             |           |          |

|               | An implementation may choose not to       |           |          |

|               | support writing to this bit. The debug-   |           |          |

|               | ger must read back the value it writes to |           |          |

|               | check whether the feature is supported.   |           |          |

| stoptime      | Controls the behavior of any timers       | R/W       | 0        |

|               | while the component is halted. This       |           |          |

|               | includes the timer read with rdcycle.     |           |          |

|               | When 1, timers are stopped when the       |           |          |

|               | component is halted/frozen. Otherwise,    |           |          |

|               | the timers continue to run.               |           |          |

|               | An implementation may choose not to       |           |          |

|               | support writing to this bit. The debug-   |           |          |

|               | ger must read back the value it writes to |           |          |

|               | check whether the feature is supported.   |           |          |

|               | Contin                                    | ued on ne | ext page |

| frozen       | See Section $5.3.1$ .                        | R   | 0      |  |  |  |  |

|--------------|----------------------------------------------|-----|--------|--|--|--|--|

| freezesup    | See Section $5.3.1$ .                        | R   | Preset |  |  |  |  |

| freeze       | See Section 5.3.1.                           | R/W | 0      |  |  |  |  |

| freezeresume | See Section 5.3.1.                           | W1  | 0      |  |  |  |  |

| halted       | See Section 5.3.1.                           | R   | 0      |  |  |  |  |

| haltsup      | See Section 5.3.1.                           | R   | Preset |  |  |  |  |

| halt         | When this bit is 1 and the core is run-      | R/W | 0      |  |  |  |  |

|              | ning, the core will enter Debug Mode,        |     |        |  |  |  |  |

|              | setting dpc to the address of the next       |     |        |  |  |  |  |

|              | instruction to be executed.                  |     |        |  |  |  |  |

|              | If this bit is 1 when the core is reset, the |     |        |  |  |  |  |

|              | core must go directly to Debug Mode.         |     |        |  |  |  |  |

|              | Do not execute any instructions. Do          |     |        |  |  |  |  |

|              | not collect \$200. When entering Debug       |     |        |  |  |  |  |

|              | Mode, dpc is set to the reset vector.        |     |        |  |  |  |  |

|              | If this bit is 1 when the core leaves De-    |     |        |  |  |  |  |

|              | bug Mode, the core will keep interrupts      |     |        |  |  |  |  |

|              | disabled and execute one instruction be-     |     |        |  |  |  |  |

|              | fore re-entering Debug Mode. dpc is set      |     |        |  |  |  |  |

|              | to the address of the next instruction to    |     |        |  |  |  |  |

|              | be executed.                                 |     |        |  |  |  |  |

|              | Setting this bit to 0 does not have an       |     |        |  |  |  |  |

|              | immediate effect.                            |     |        |  |  |  |  |

|              | Continued on next page                       |     |        |  |  |  |  |

| resume    | If this bit is written as 1 while the core is | W1  | 0      |

|-----------|-----------------------------------------------|-----|--------|

|           | in Debug Mode, the core leaves Debug          |     |        |

|           | Mode and resumes execution at dpc.            |     |        |

| interrupt | See Section 5.3.1.                            | R/W | Preset |

# 6.3.2 DTM Interrupt Address (cdtmaddress, at 0x10)

See Section 5.3.3.

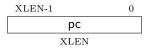

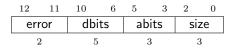

6.3.3 Debug Control and Status (dcsr, at 0x20)