# Test Bench for CCounterOprLevel

#### **Core description**

The core *CCounterOprLevel* is almost identical to the core *CCounterLevel*. The counter is clocked at each step, i.e. at FPGA clock. Instead of individual signals, the counter control is done via the signal *iOpr*, which type is:

```

enum Opr_t { cOprNone, cOprReset, cOprUp, cOprDown, cOprLoad };

```

Therefore, if *iOpr* equals *cOprUp* then the counter counts up.

#### **Test bench**

This test bench uses the *signal editor* and the *signal viewer* to test the core. The test will be done in single step simulation. Follow the instructions to:

- Create signals in the Signal Editor

- Execute with the **Single Step** function (F8)

- Use the Watch Window in single step mode

- View the result in the Signal Viewer

### **Description**

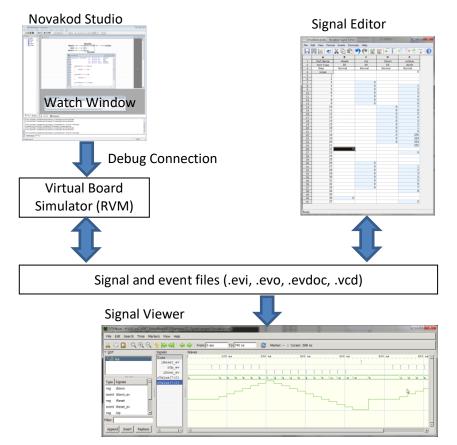

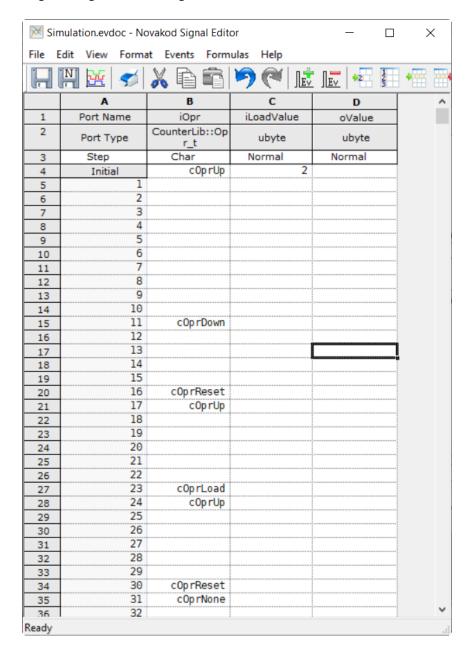

The **Signal Editor** is an Excel like spreadsheet to edit the input signals and view the output signals, including the events. The signal editor saves its information in a **.evdoc** file.

During simulation, the signals are read from an input event file (.evi) and written to an output event file (.evo). After simulation, the Signal Editor is used to view the resulting output signals. Then, the Signal Viewer will display the signal in the more common temporal view, with digital or analog representation. The signal viewer is GTK Wave and it uses .vcd (value change dump) files.

#### The psC test program

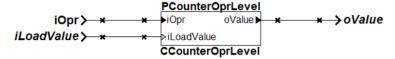

The test program consists of a single component, the core to be tested, and IO connections. The counter operation is controlled by the value of the *iOpr* input.

- 1) Double-click on *Counter.rpj* to start Novakod Studio.

- 2) Double-click on the *main* component to view the schematic.

- 3) Double-click on the *CCounterOprLevel* component to view the counter code.

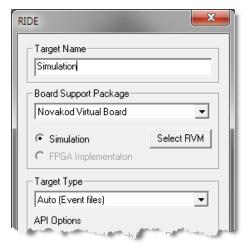

- 4) Right-click on *Targets* to view the target. The *Target Type* is *Auto (Event files)* indicating that simulation will use *.evi* and *.evo* event files.

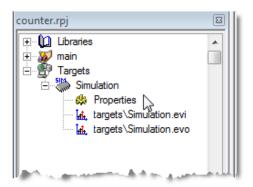

5) Expand *Targets* then *Simulation*, you should see the two event files:

## Viewing and editing input signals

The signals are already set, but you can change them as you wish.

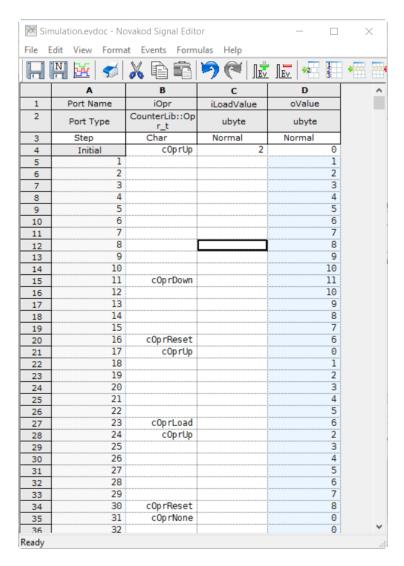

6) Double-click on targets \Simulation.evi to start the Signal Editor.

As you can see, the signal iOpr takes different values to control the counter. The values are displayed as their enum names. You can easily interpret the signal to predict the counter value. If you change the signals, don't forget to save.

## Compiling and running the test

You are now ready to run and use the **Single Step** execution mode.

- 7) Select the menu *Run* -> Start Paused to begin simulation, accept the build confirmation.

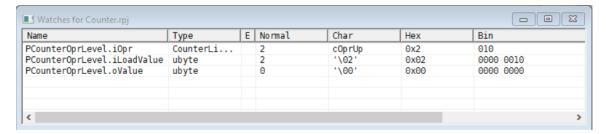

- 8) Right click on each port in the project *Inspect* tab to add them to the *Watch window*.

- 9) You should see the initial values.

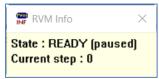

10) The RVM is in pause, and you can execute step by step.

- 11) *For single step, simply type F8.* Repeat until you reach step 30. You will see all the input signals being applied at each step.

- 12) After 30 or more steps, stop the simulation by selecting menu  $Run \rightarrow Stop$ .

## View results in signal editor

You can now view the results.

- 13) Double-click on *targets\Simulation.evo*, the *Signal Editor* window starts with the values in *oValue* column.

- 14) Verify the counter operation.

## View results in signal viewer

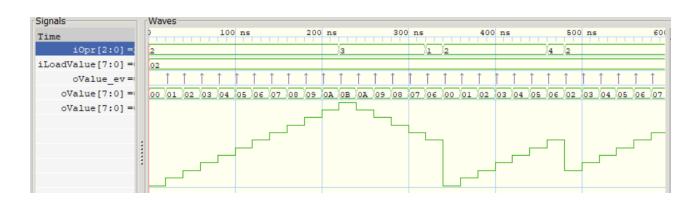

Novakod Studio integrates the well-known signal viewer called *GTK Wave*.

15) Select menu *File* → *View Signals* or click the shortcut . The GTK Wave windows appears. GTK Wave has been pre-configured to show the desired signals. You can see the inputs and the output in hexadecimal or as an analog signal.