# Theia architecture specification

Version 0.1 Last update Sunday, August 19, 2012 Diego Valverde 2012

# Table of contents

| Revision & Review                                           | .1         |  |  |

|-------------------------------------------------------------|------------|--|--|

| Table of contents                                           |            |  |  |

| Table of tables                                             | .7         |  |  |

| 1. Introduction1                                            | 1          |  |  |

| 1.1. Vector processing1                                     | 13         |  |  |

| 1.2. Combining Vector processing and out-of-order execution | 4          |  |  |

| 2. System Overview1                                         | 15         |  |  |

| 2.1. Control processor Overview1                            | L <b>7</b> |  |  |

| 1.1.1. Data block copy operations                           | 18         |  |  |

| 1.1.2. Control processor messages                           | 20         |  |  |

| 1.1.3. Mail-boxing2                                         |            |  |  |

| 1.2. Vector processors (VP)2                                | 21         |  |  |

| 2. Control FSM                                              | 23         |  |  |

| 3. Vector Processor CORE (VP CORE)                          | 24         |  |  |

| 3.1. Introduction                                           | 24         |  |  |

| 3.1.1. Single Thread execution example                      | 25         |  |  |

| 3.2. VP Architecture                                        | 28         |  |  |

| 3.3. Word size and Endianness                               | 31         |  |  |

| 3.4. Fixed point arithmetic                                 | 31         |  |  |

| 3.5. Instruction overview                                   | 32         |  |  |

| 3.5.1. Instruction operation codes                          | 33         |  |  |

| 3.5.2. Instruction destination block selector               | 35         |  |  |

| 3.5.3. Instruction source modifiers                         | 36         |  |  |

| 3.5.4. Data dependencies and source modifiers               | 39         |  |  |

| 3.5.4.1. VP Flags                                           | 13         |  |  |

| 3.5.5. Execution units and reservation stations4            | 14         |  |  |

| 3.5.6. VP Stall conditions4                                 | <b>1</b> 7 |  |  |

| 3.6. Instruction addressing modes4                          | 18         |  |  |

| 3.7. Instruction word fields5                               | 52         |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | 53                                                       |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|

| 3.9. Selecting the Arithmetic operation                                                                                                                                                                                                                                                                                                                                                                                              | 57                                                       |  |  |  |

| 0. Fixed point Square Root unit                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |  |  |  |

| 3.11. Bitwise logic operations                                                                                                                                                                                                                                                                                                                                                                                                       | 11. Bitwise logic operations                             |  |  |  |

| 3.12. Destination write channel control                                                                                                                                                                                                                                                                                                                                                                                              | 59                                                       |  |  |  |

| 3.13. Operand Scale control                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |  |  |  |

| 3.14. Operand Sign control                                                                                                                                                                                                                                                                                                                                                                                                           | 51                                                       |  |  |  |

| 3.15. Operand swizzle control                                                                                                                                                                                                                                                                                                                                                                                                        | 52                                                       |  |  |  |

| 3.16. Branching operations                                                                                                                                                                                                                                                                                                                                                                                                           | 54                                                       |  |  |  |

| 3.16.1. Unconditional branches                                                                                                                                                                                                                                                                                                                                                                                                       | 65                                                       |  |  |  |

| 3.16.2. Conditional Branches                                                                                                                                                                                                                                                                                                                                                                                                         | 56                                                       |  |  |  |

| 4. VP Data path                                                                                                                                                                                                                                                                                                                                                                                                                      | 57                                                       |  |  |  |

| 4.1.1. Instruction issue unit (IIU)                                                                                                                                                                                                                                                                                                                                                                                                  | 70                                                       |  |  |  |

| 4.1.2. Source Modification unit (SMU)                                                                                                                                                                                                                                                                                                                                                                                                | 73                                                       |  |  |  |

| 4.1.2.1. Issue Bus (IBUS)                                                                                                                                                                                                                                                                                                                                                                                                            | 74                                                       |  |  |  |

| 4.1.2.2. Commit Bus (CBUS)                                                                                                                                                                                                                                                                                                                                                                                                           | 75                                                       |  |  |  |

| 5. VP IO                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | //                                                       |  |  |  |

| 5.1. Output memory OMEM                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |  |  |  |

| 5.1.       Output memory OMEM         5.2.       Texture memory TMEM                                                                                                                                                                                                                                                                                                                                                                 | 77                                                       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | 77<br>80                                                 |  |  |  |

| 5.2. Texture memory TMEM                                                                                                                                                                                                                                                                                                                                                                                                             | 77<br>80<br>82                                           |  |  |  |

| 5.2. Texture memory TMEM   8     6. VP Register specification   8                                                                                                                                                                                                                                                                                                                                                                    | 77<br>80<br>82<br>82                                     |  |  |  |

| 5.2. Texture memory TMEM       8         6. VP Register specification       8         6.1. General purpose registers (GPRs)       8                                                                                                                                                                                                                                                                                                  | 77<br>80<br>82<br>82<br>83                               |  |  |  |

| 5.2. Texture memory TMEM    8      6. VP Register specification    8      6.1. General purpose registers (GPRs)    8      6.1.1. Zero register – R0.    8                                                                                                                                                                                                                                                                            | 77<br>80<br>82<br>82<br>83<br>83                         |  |  |  |

| 5.2. Texture memory TMEM       8         6. VP Register specification       8         6.1. General purpose registers (GPRs)       8         6.1.1. Zero register – R0.       8         6.1.2. Return address register – R2.x       8                                                                                                                                                                                                 | 77<br>80<br>82<br>82<br>83<br>83<br>84<br>84             |  |  |  |

| 5.2. Texture memory TMEM       8         6. VP Register specification       8         6.1. General purpose registers (GPRs)       8         6.1.1. Zero register – R0.       8         6.1.2. Return address register – R2.x       8         6.1.3. Offset registers – R3.x, R2.y       8                                                                                                                                            | 77<br>80<br>82<br>82<br>83<br>83<br>84<br>84<br>86       |  |  |  |

| 5.2. Texture memory TMEM       8         6. VP Register specification       8         6.1. General purpose registers (GPRs)       8         6.1.1. Zero register – R0       8         6.1.2. Return address register – R2.x       8         6.1.3. Offset registers – R3.x, R2.y       8         6.2. Shadowed GPRs       8                                                                                                          | 77<br>80<br>82<br>82<br>83<br>84<br>84<br>84<br>86<br>87 |  |  |  |

| 5.2. Texture memory TMEM       8         6. VP Register specification       8         6.1. General purpose registers (GPRs)       8         6.1.1. Zero register – R0       8         6.1.2. Return address register – R2.x       8         6.1.3. Offset registers – R3.x, R2.y       8         6.2. Shadowed GPRs       8         6.3. Special purpose registers (SPRs)       8                                                    | 77<br>80<br>82<br>82<br>83<br>84<br>84<br>86<br>87<br>90 |  |  |  |

| 5.2. Texture memory TMEM       8         6. VP Register specification       8         6.1. General purpose registers (GPRs)       8         6.1.1. Zero register – R0.       8         6.1.2. Return address register – R2.x       8         6.1.3. Offset registers – R3.x, R2.y       8         6.2. Shadowed GPRs       8         6.3. Special purpose registers (SPRs)       8         7. Control Processor architecture       9 | 77<br>80<br>82<br>82<br>83<br>84<br>84<br>86<br>87<br>90 |  |  |  |

# 4 Theia architecture specification

| 8.  | Internal Memory Controller (MCU) Architecture | .97 |

|-----|-----------------------------------------------|-----|

| 9.  | Appendix A: VP Issue unit encoding table      | .97 |

| 10. | Appendix B: VP addressing mode examples       | 0   |

| Wor | ks Cited                                      | 9   |

| Figure 1 THEIA environment overview                                                               | 12 |

|---------------------------------------------------------------------------------------------------|----|

| Figure 2 Data pipeline in an execution unit                                                       | 13 |

| Figure 3 X, Y and X data vector data lanes                                                        | 14 |

| Figure 4 Convoy chaining                                                                          | 15 |

| Figure 5 The GPU simplified block diagram                                                         | 16 |

| Figure 6 Control Processor within the system                                                      | 18 |

| Figure 7 CP "data block copy command" format                                                      | 19 |

| Figure 8 CP control processor message.                                                            | 20 |

| Figure 9 Mailboxing registers                                                                     |    |

| Figure 10 The main blocks of a CORE                                                               | 22 |

| Figure 11 The CONTROL FSM, the CP and the VP Core                                                 | 23 |

| Figure 12 Control FSM                                                                             | 24 |

| Figure 13 A sample code (single thread)                                                           | 26 |

| Figure 14 Behaviour of the execution units over time for the example from Figure 13               | 28 |

| Figure 15 VP architecture                                                                         |    |

| Figure 16 Vector word layout                                                                      |    |

| Figure 17 Storing Fixed point numbers in a 96 bit word                                            |    |

| Figure 18 Instruction Layout                                                                      | 33 |

| Figure 19 Immediate bit and the way the instruction is interpreted by the IIU                     | 33 |

| Figure 20 Modifying the individual signs of the instruction sources                               | 36 |

| Figure 21 Modifying the scale of the instruction sources                                          |    |

| Figure 22 Swizzling instruction sources                                                           | 37 |

| Figure 23 Combining several source modifiers in a single instruction                              | 38 |

| Figure 24 Example of data dependencies when using source modifiers                                |    |

| Figure 25 IIU issues a division                                                                   |    |

| Figure 26 The IIU issues an addition operation                                                    | 41 |

| Figure 27 The DIV UE commits the results to the CBUS and the SMU. The SMU presents the first data |    |

| dependency to the reservation stations                                                            | 42 |

| Figure 28 The SMU presents the second data dependency to the reservation stations. The ADD EU     |    |

| commits the result to the RF                                                                      | 43 |

| Figure 29 An example code written in T-Language                                                   | 46 |

| Figure 30 The code from Figure 29 translated into assembly language                               | 47 |

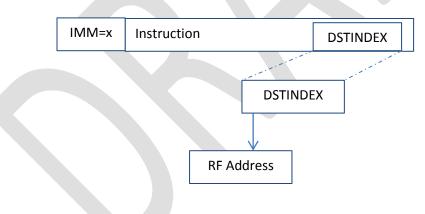

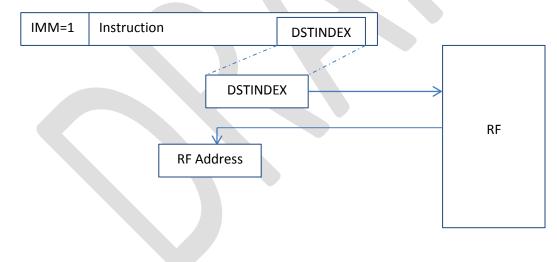

| Figure 31 Direct addressing mode                                                                  | 48 |

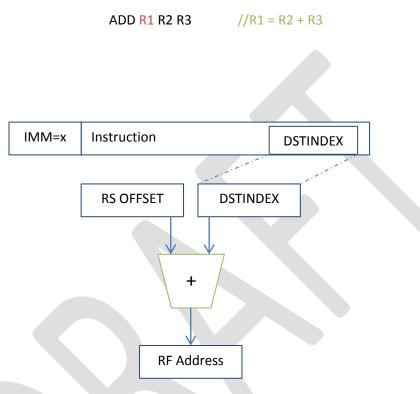

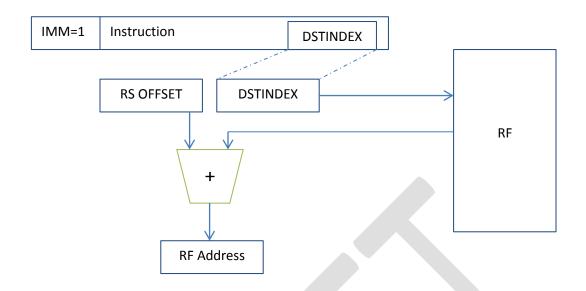

| Figure 32 Direct Addressing with displacement                                                     | 49 |

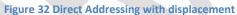

| Figure 33 direct addressing with displacement                                                     | 49 |

| Figure 34 Displacement and Index                                                                  | 50 |

| Figure 35 Indirect addressing mode                                                                | 50 |

| Figure 36 Indirect addressing with displacement                                                   | 51 |

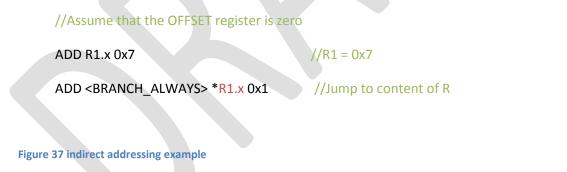

| Figure 37 indirect addressing example                                                             | 51 |

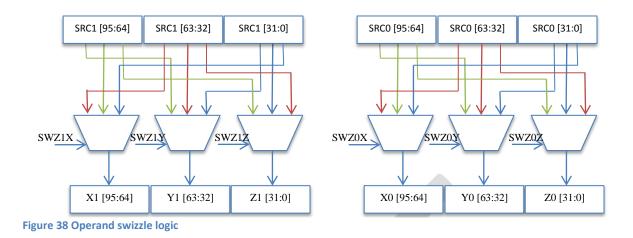

| Figure 38 Operand swizzle logic                                                                   | 64 |

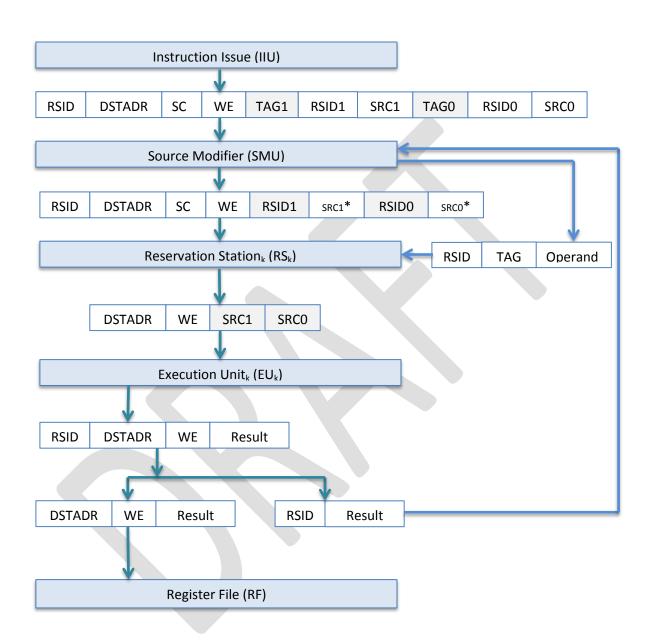

| Figure 39 VP data path Walk Through                                                           | 68 |

|-----------------------------------------------------------------------------------------------|----|

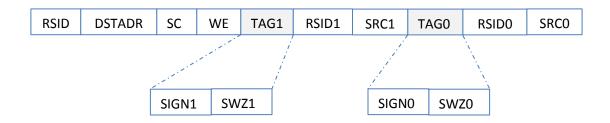

| Figure 40 The decoded instruction presented by the IIU to the SMU                             | 69 |

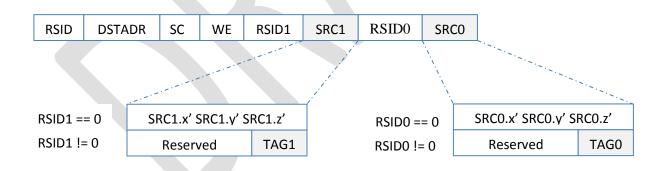

| Figure 41 The packet presented by the SMU to the reservation stations (RS)                    | 69 |

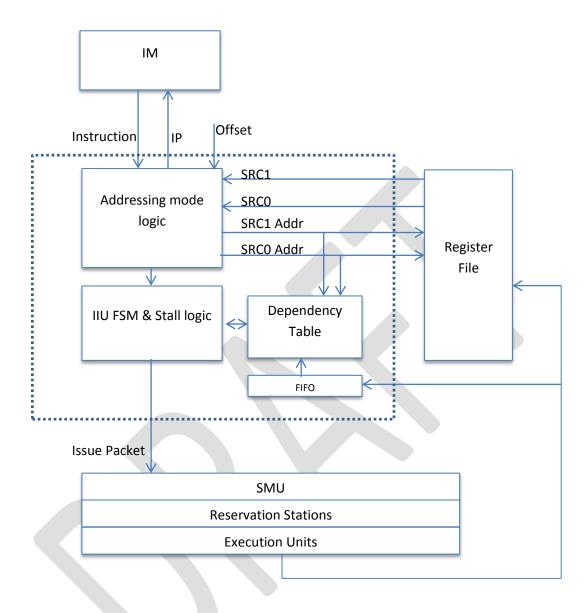

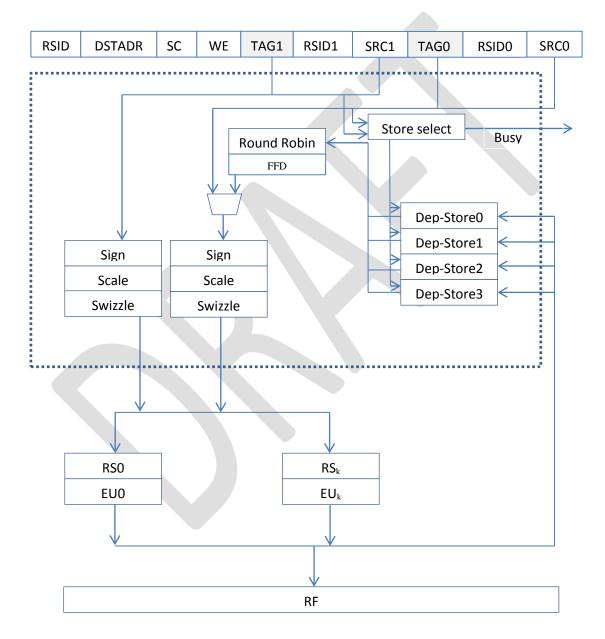

| Figure 42 Block diagram of the IIU                                                            | 71 |

| Figure 43 SMU simplified diagram                                                              | 73 |

| Figure 44 multithreading                                                                      | 76 |

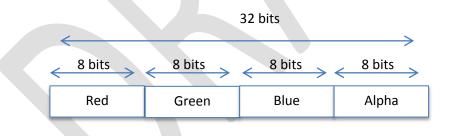

| Figure 45 A typical pixel color stored as a 32 bit value in VP's the OMEM                     | 77 |

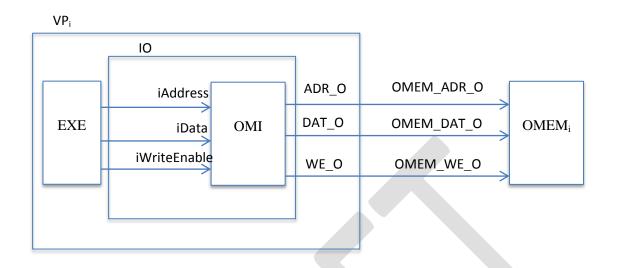

| Figure 46 The OMI inside the IO unit                                                          | 78 |

| Figure 47 EXE and OMI signals                                                                 | 78 |

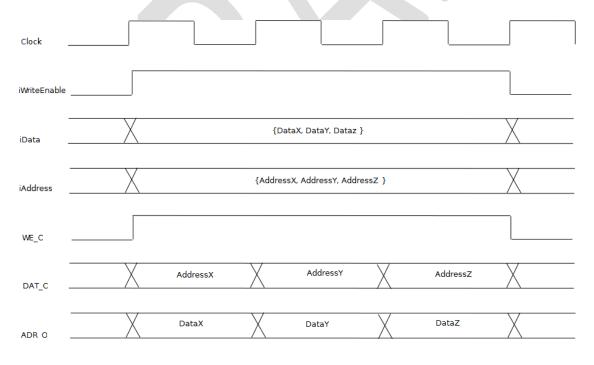

| Figure 48 - VP writing data to an OMEM                                                        |    |

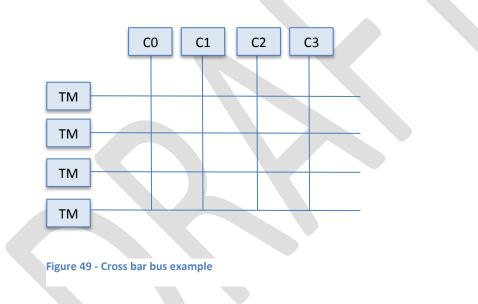

| Figure 49 - Cross bar bus example                                                             |    |

| Figure 50 - CORE reading data from TMEM                                                       |    |

| Figure 51 Using the R0 register                                                               |    |

| Figure 52 Using the R2 register                                                               | 84 |

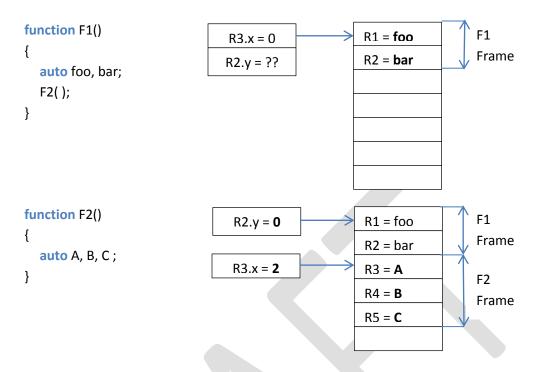

| Figure 53 Example of using the offset register R30 to allocate memory for automatic variables | 85 |

| Figure 54 Example of an SPR shadowing R30                                                     | 87 |

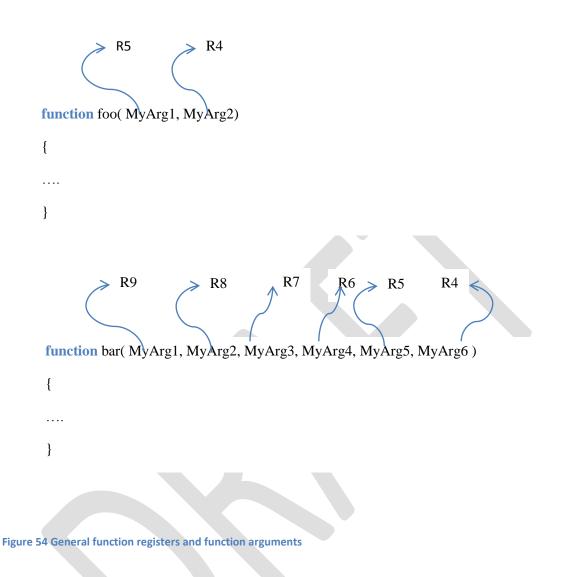

| Figure 55 Control processor CP                                                                | 90 |

| Figure 56 CP block transfer high level syntax                                                 | 94 |

| Figure 57 CP copy data block high level syntax                                                | 95 |

| Figure 58                                                                                     | 95 |

# Table of tables

| Table 1 Acronyms and Abbreviations                                              | 8  |

|---------------------------------------------------------------------------------|----|

| Table 2 Reference Documents                                                     | 8  |

| Table 3 Data copy command fields                                                | 19 |

| Table 4 Control processor messages                                              | 20 |

| Table 5 Scaling arithmetic operation for fixed point                            | 32 |

| Table 6 VP operations                                                           |    |

| Table 7 Example of destination selection                                        |    |

| Table 8 instruction operand manipulators                                        |    |

| Table 9 Execution SFLAG values                                                  |    |

| Table 10 Execution ZFLAG values                                                 |    |

| Table 11 VP Reservation Stations                                                |    |

| Table 12 IIU Stall conditions                                                   |    |

| Table 13 Instruction Operation section fields                                   | 52 |

| Table 14 Instruction Destination section fields                                 |    |

| Table 15 Addressing mode encoding IMM = 0                                       |    |

| Table 16 Addressing mode encoding IMM = 1                                       |    |

| Table 17 Addressing mode encoding                                               |    |

| Table 18 Instruction Source 1 section fields                                    | 56 |

| Table 19 Instruction Source 0 section fields                                    |    |

| Table 20 Instruction OPCODE field values                                        | 57 |

| Table 21 Write channel control bit values                                       |    |

| Table 22 input operand scale control                                            |    |

| Table 23 SRC1 Sign control                                                      |    |

| Table 24 SRC0 Sign control                                                      | 61 |

| Table 25 SRC1 Swizzle control X                                                 |    |

| Table 26 SRC1 Swizzle control Y                                                 |    |

| Table 27 SRC1 Swizzle control Z                                                 | 62 |

| Table 28 SRC0 Swizzle control X                                                 | 63 |

| Table 29 SRC0 Swizzle control Y                                                 | 63 |

| Table 30 SRC0 Swizzle control Z                                                 | 63 |

| Table 31 Branch operation BOP values                                            | 64 |

| Table 32 Branch operation predicates                                            | 64 |

| Table 33 Unconditional branch with branch destination as immediate value        | 65 |

| Table 34 Unconditional branch with branch destination stored in a register      | 66 |

| Table 35 Example of Instruction operation for a conditional branch instruction  | 66 |

| Table 36 Example of Instruction Destination for conditional branch instruction. | 67 |

| Table 37 Example of Instruction Sources for a conditional branch instruction    | 67 |

| Table 38 Data path fields.                        |    |

|---------------------------------------------------|----|

| Table 39 Issue bus fields                         | 74 |

| Table 40 Commit bus fields                        | 75 |

| Table 41 – CORE signals for OMEM write bus cycles | 79 |

| Table 4 – CORE signals for TMEM write bus cycles  | 80 |

| Table 41 Special purpose registers.               | 82 |

| Table 42 List of special purpose registers        |    |

| Table 43 Control register (CNTREG)                | 88 |

| Table 44 Arithmetic error register                | 88 |

| Table 45 CP Instruction set                       |    |

| Table 46 CP Special purpose registers             | 94 |

|                                                   |    |

| Table 1 Acronyms and Abbreviations                |    |

#### Table 1 Acronyms and Abbreviations

| Acronym | Description                                             |  |  |  |

|---------|---------------------------------------------------------|--|--|--|

| ALU     | Arithmetic and logical unit                             |  |  |  |

| IIU     | Instruction Issue Unit                                  |  |  |  |

| RF      | Register File                                           |  |  |  |

| EA      | Effective Address                                       |  |  |  |

| RTL     | Register transfer level                                 |  |  |  |

| CBUS    | Commit bus                                              |  |  |  |

| IBUS    | Issue bus                                               |  |  |  |

| IMEM    | Instruction memory                                      |  |  |  |

| RS      | Reservation Station                                     |  |  |  |

| EU      | Execution Unit                                          |  |  |  |

| IM      | Instruction Memory                                      |  |  |  |

| SPR     | Special Purpose Register                                |  |  |  |

| Qm.n    | Fixed point number with n decimal bits a m integer bits |  |  |  |

| LUT     | Lookup Table                                            |  |  |  |

| ILP     | Instruction level parallelism                           |  |  |  |

| TLP     | Thread level parallelism                                |  |  |  |

| PC      | Program counter                                         |  |  |  |

| СР      | Control Processor                                       |  |  |  |

| VP      | Vector Processor                                        |  |  |  |

| ССВ     | Control Command Bus                                     |  |  |  |

| 000     | Out of order                                            |  |  |  |

#### **Table 2 Reference Documents**

| References | Description                          |

|------------|--------------------------------------|

| TH-LS001   | T Language Specification <url></url> |

# THIS PAGE IS INTENTIONALLY LEFT BLANK

# **1. Introduction**

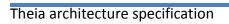

THEIA is a multi-thread, multicore, vector graphic processing unit (GPU). The idea of the THEIA project is to provide an open source environment including functional RTL, test bench environment and an open source high level programming language/compiler called T-Language.

The present document is dedicated to describe and specify the hardware architecture of the THEIA GPU system and related hardware subsystems.

The THEIA hardware is described using RTL (register transfer level), written in Verilog 2001 HDL. In order to perform a full RTL simulation, the HDL model needs a series of input files which represent the various input parameters and the binary representation of the user code (written in T-Language or in THEIA-Assembly language).

#### Figure 1 THEIA environment overview

The outputs from an RTL simulation are a series log files and the actual graphical representation of the rendered image in a format which can be opened using a standard image editor such as GNU Gimp.

Even if the hardware architecture of the THEIA GPU is designed to be efficient in 3D computer graphic related tasks, due to the flexibility of the system and the programming environment, a myriad of other applications that can benefit from vector processing and parallel processing are also possible.

# **1.1.** Vector processing

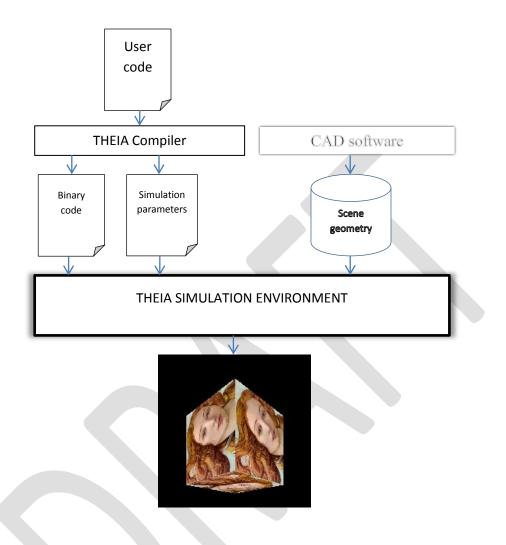

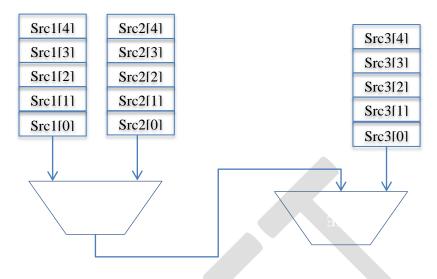

One of the interesting features of the THEIA GPU is the ability to handle vector operations. Each single instruction can operate on vectors of data. Each element of the input data vector is fetched consecutively by the corresponding execution unit in a pipelined fashion as illustrated in the next figure.

#### Figure 2 Data pipeline in an execution unit

Each vector functional unit is a separate and fully pipelined execution unit that and most execution units can start a new operation every clock cycle. Therefore, each vector functional unit is effectively a data pipeline. Furthermore each execution unit has 3 "data lanes" thus being able to simultaneously process 3 array elements every clock cycle.

| Src1.x[4] | Src2.x[2] | Src1.y[4] | Src2.y[4] | Src1.z[4] | Src2.z[4] |

|-----------|-----------|-----------|-----------|-----------|-----------|

| Src1.x[3] | Src2.x[3] | Src1.y[3] | Src2.y[3] | Src1.z[3] | Src2.z[3] |

| Src1.x[2] | Src2.x[2] | Src1.y[2] | Src2.y[2] | Src1.z[2] | Src2.z[2] |

| Src1.x[1] | Src2.x[1] | Src1.y[1] | Src2.y[1] | Src1.z[1] | Src2.z[1] |

| Src1.x[0] | Src2.x[0] | Src1.y[0] | Src2.y[0] | Src1.z[0] | Src2.z[0] |

|           |           |           |           |           |           |

#### Figure 3 X, Y and X data vector data lanes

Also each GPU core has a large register file where the data is guaranteed to be located in consecutive memory positions<sup>1</sup>.

# 1.2. Combining Vector processing and out-of-order execution.

The execution time of the vector operations primarily depends on the length of the vectors, but also depends on the structural hazards and data dependencies. In order to obtain more instruction level parallelism, the vector operations are combined with an out-out-of-order execution model. By executing the vector operations in an out-of-order fashion, the data dependencies can be minimized and a better performance is obtained.

The notion of "convoy" from [1] is defined as a series of vector instructions that can potentially execute together and the performance of a section of code can be estimated by counting the number of convoys. By introducing the OOO technique, these convoys are not limited to instructions that are sequential in the program flow therefore the performance of the program can be increased.

Vector "Chaining" allows the results from a vector functional unit to be forwarded to a second functional unit which has data dependency on the first one. By using chaining, a convoy which depends on the results from a previous convoy can be chained together into a single convoy.

<sup>&</sup>lt;sup>1</sup> This is done by software, at the Control Processor (CP) level.

Theia architecture specification

#### Figure 4 Convoy chaining

THEIA extends the data forward of execution results from the OOO model in order to implement "chaining" for the vector operations.

The details of the out-of-order engine are described later on this document.

# 2. System Overview

THEIA is a multi-thread, multicore, vector graphic processing unit (GPU). The THEIA GPU is comprised of different hardware blocks that interact with other in order to render an image frame.

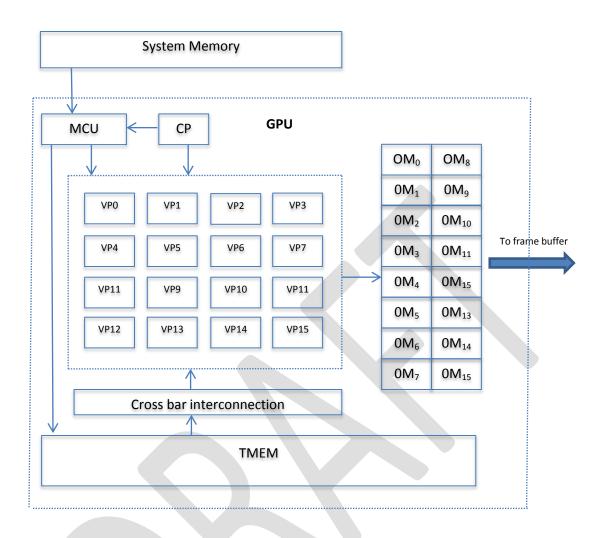

Figure 5 The GPU simplified block diagram

Figure 5 presents the GPU main functional blocks and also an external memory called "Main Memory" that is outside of the GPU. The Main memory is a large RAM that is used as a repository where the textures, code, geometry, etc. can be stored. The contents of the Main Memory are read only from the GPU stand point and can only be accessed through the internal Memory Control Unit (MCU). The MCU is controlled by the Control Processor Unit (CP).

The CP block is responsible to control and monitor the global execution of the GPU. The CP is a simple programmable unit which allows the user to programmatically control the resource allocation and the workload distribution of the GPU. The CP can command the MCU to copy execution code and data to one or more "Vector Processing Units" (VPs) at any given point in time. The CP can also request special actions from one or more VPs by sending special commands directly to the VPs using a dedicated

"Control Command Bus" (CCB). By using the MCU and the CCB, the software running on the CP effectively distributes the workload among the vector processing cores (VP).

The VPs, called V0 ... VP15<sup>2</sup> in Figure 5, are the elements in charge of the actual processing of the data. Each VP is a multi-thread out-of-order vector processor with hardware architecture and instruction set that is specially optimized to operate on 3D vectors. Section 3 gives more detail regarding the Vector processor architecture.

The THEIA GPU topology follows a "CROW PRAM" model. PRAM stands for Parallel Random Access Machine, and is a common paradigm used to describe parallel machines [tbd]. CROW stands for Concurrent-Read Owned-Write, CROW PRAMs are described by [tbd] and offer series of advantages over other types of PRAM machines as analyzed by [tbd].

Following the CROW PRAM paradigm, some of the storage blocks from Figure 5 are read-only while other blocks are write-only. The OMEMs are write-only memories (from the VP's perspective) that are "owned" by each VP, this is, each VP can only access a single and unique OMEM block, and can only perform write operations to that OMEM block.

The TMEM, on the other hand, is a read-only block (from the VP's perspective). The TMEM can be concurrently accessed for reading operations by one or more VPs at any given point in time. Together the TMEM and the OMEM blocks allow the GPU to be modeled as a CROW PRAM machine.

The next sections will further describe the various functional blocks from Figure 5.

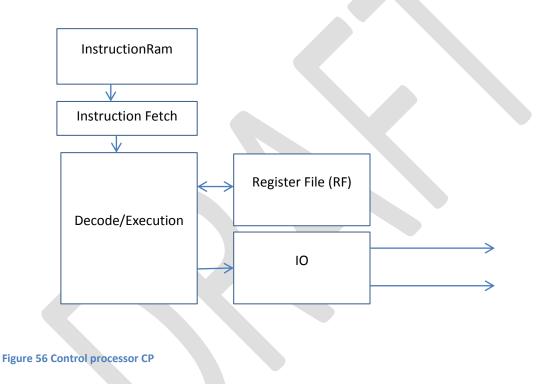

# 2.1. Control processor Overview

The main function of the Control Processor (CP) is to allow the user to programmatically control the resource allocation and the workload distribution of the GPU. In other words, instead of implementing complex dynamic hardware based scheduling algorithms, the CP allows for these algorithms to be implemented in software. This way the hardware complexity is reduced while the overall system becomes more flexible. This section will present an overview of the CP, to see a full description of the CP architecture and instruction set please see section 8.

<sup>&</sup>lt;sup>2</sup> Figure 5presents a GPU configuration with 16 VPs but this number may vary depending on the specific GPU implementation.

Theia architecture specification

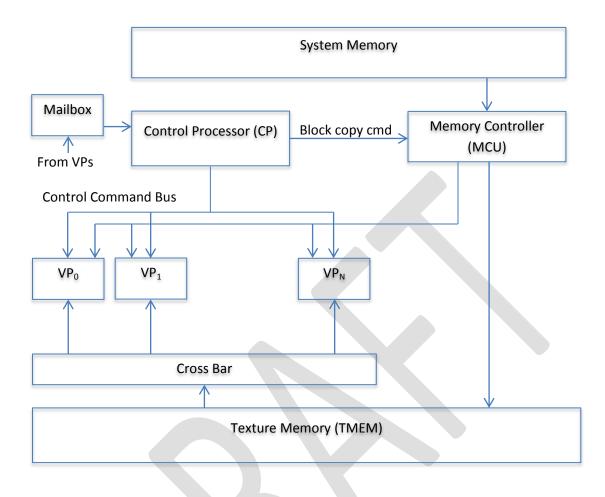

Figure 6 Control Processor within the system

The CP is a minimalistic processor. It is mainly in charge of controlling the dispatching of code, data and commands into the vector processors (VPs). There is a single control processor for the entire GPU and it is connected to the vector processors using a topology as the one depicted in Figure 6.

# **1.1.1. Data block copy operations**

As depicted in Figure 6 the control processor (CP) interfaces with an internal memory controller (MCU).

The CP issues special instructions called "data block copy commands" to the MCU, telling the MCU to copy memory blocks from the main memory into the TMEM or into the VP's internal memory locations. It is important to mention that the MCU can only copy data from the main memory and **not** into the main memory, in other words, the Main memory is read-only from the GPU perspective.

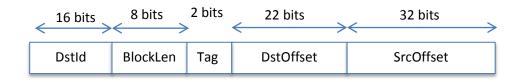

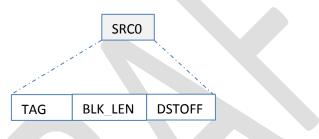

The format of the "data block copy commands" is illustrated in Figure 7

#### Figure 7 CP "data block copy command" format

The data block copy command is made of several fields as shown in the previous illustration. Table 3 describes the meaning of the various fields of the "data block copy command".

Table 3 Data copy command fields

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dstld     | <b>0: Destination NULL</b> : No data blocks are copied and no copy commands are queued in the MCU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | <b>1: Destination TMEM</b> : The data block is copied by the MCU from the main memory into the TMEM memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|           | <b>2 to N+2</b> : <b>Destination VP</b> : The data block is copied by the MCU from the main memory into the VP identified by the index <i>DstId-2</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BlockLen  | How many blocks to copy from the Main memory into the destination resource identified by <i>Dstld. Up to 1024 blocks can be copied.</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DstOffset | <ul> <li>Offset where the MCU will copy the data at the destination resource identified by Dstld.</li> <li>When the target resource is the TMEM, the offset represents the linear address where the data will start to be copied.</li> <li>When the target resource is one of the VPs, the offset is divided in address and tag: <ul> <li>DstOffset [20:0]: Linear address.</li> <li>DstOff[22:21]: Destination Tag: Can have one of the following values:</li> <li>10 -&gt; Final destination is VP Instruction Address.</li> <li>01 -&gt; Final destination is VP Data Address.</li> </ul> </li> </ul> |

| SrcOffset | Offset into the main memory from where the MCU will start coping the data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

The data block copy commands are issued by the CP to the MCU in an asynchronous way. In other words, the CP issues a data block command and then the CP can continue with the control code execution even if the MCU has not yet finished copying the data blocks. If the CP issues another data copy command to the MCU while the previous copy command has not finished, then the copy command gets queued in the MCU. The MCU presents a signal with the number of pending copy operations to the CP. This signal is mapped into the CP internal register STATUS[MCU\_OPERATION\_PENDING]<sup>3</sup>; it is the software responsibility to poll this register in order to know the number of pending memory copy operations in the MCU.

# 1.1.2. Control processor messages

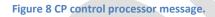

The CP has the ability to send special messages called "control processor messages" to one or more VPs using the *Control Command Bus (CBC)* from Figure 6. The control processor messages have the following format:

As depicted in Figure 8 the format of the "control processor messages" is very simple, it is made of a VP destination field, which specifies whether the CP message is targeted at a single VP or broadcasted to all the VPs, a command to specify the action that the VP has to perform and also an optional 32bit argument.

#### Table 4 Control processor messages

| CP message field | Arguments                                                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VPDST            | The destination for the CP command.<br>It has one of the following possible values:                                                                                                                  |

|                  | <ul> <li>0: NULL Message. The message has no target VPs.</li> <li>1-127: Message is targeted to one of the possible VPs.<sup>4</sup></li> <li>128: Message is broadcasted to all the VPs.</li> </ul> |

<sup>&</sup>lt;sup>3</sup> More information in section <TBD>

<sup>&</sup>lt;sup>4</sup> The number of VPs depend on the version of the GPU implementation. Currently up to 16 VPs are supported.

Theia architecture specification

| Command  | The command that the CP sends to one or more VPs to execute. It has one of the following possible values:<br>0: Start Execution |

|----------|---------------------------------------------------------------------------------------------------------------------------------|

|          | 1: Stop Execution                                                                                                               |

|          | <mark>More to be defined</mark>                                                                                                 |

| Argument | Reserved for future use                                                                                                         |

The most important use of the "control processor messages" is allowing the CP to start or to stop the VPs execution. This allows the user to program the CP in order to have full control of the resource and workload distribution.

### 1.1.3. Mail-boxing

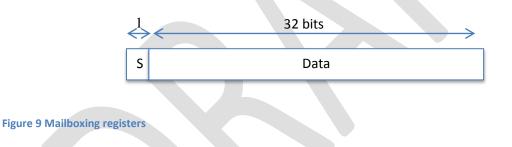

Mail-boxing is a mechanism which allows passing messages between the VPs and the CP<sup>5</sup> during code execution. Each VP has a special 33 bit register called Mailbox. Each Mailbox has 32 bits of data and a 1 bit semaphore flag.

The semaphore flag controls the write ownership of the mailbox register. If the semaphore bit is set then the CP has write ownership of the mailbox, otherwise the corresponding VP has write ownership of the mailbox. All mailboxes' semaphore bits are cleared after reset.

If the semaphore bit is set, then the CP gets notified of an incoming message delivered by the VP into the corresponding mailbox. The CP can now post a reply and then clear the semaphore flag to notify the VP that a reply has been delivered.

# 1.2. Vector processors (VP)

<sup>&</sup>lt;sup>5</sup> In the current version of the RTL, the communication can only be initiated by the VP.

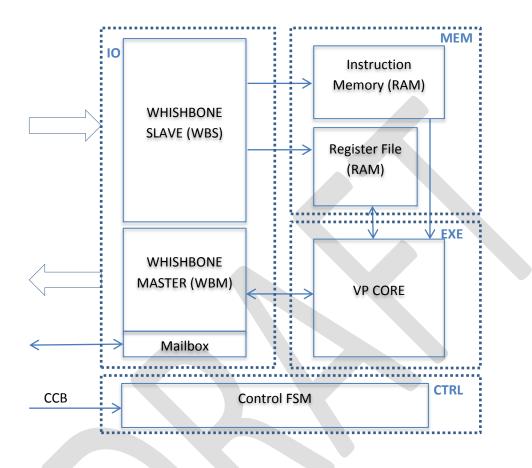

The VPs are a series of multithreaded out-of-order vector processors featuring fixed point arithmetic units and special purpose hardware to accelerate the most common 3D graphic operations. Each VP is divided into 5 main block called IO, EXE, MEM and CTRL. This is illustrated in Figure 10.

Figure 10 The main blocks of a CORE

The main building blocks shown in Figure 10 are further described later on this document.

The "VP CORE" block is where most of the complexity resides, thus section 3 of this document is dedicated exclusively to the VP CORE block.

# 2. Control FSM

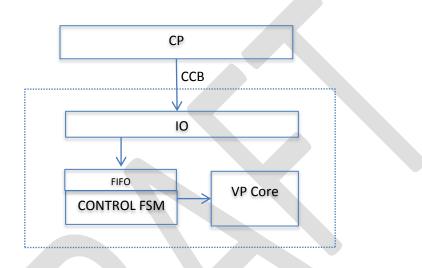

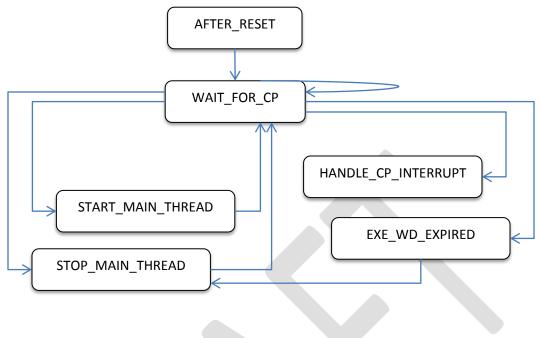

This block has the main control FSM that is in charge of orchestrating the VP operation. Each VP has a single Control FSM. The Control FSM is mainly responsible of handling commands coming from the CP through the CCB (control command bus) and guarantying that the VP Core reacts accordingly.

#### Figure 11 The CONTROL FSM, the CP and the VP Core

When the VP first comes out of reset no code in the VP gets executed by default. Instead of this, the VP first reaches a state called WAIT\_FOR\_CP where it will remain until one or more CP commands get queued into the CP command FIFO. Once a CP command becomes queued, the FSM will transition into a specific state which will take care of the CP request. If the CP command requires starting the main execution thread then the FSM transitions into the START\_MAIN\_THREAD state and then back into the WAIT\_FOR\_CP state. This means that the control FSM is not required to wait until the VP code is finished in order the handle more CP commands.

Figure 12 Control FSM

# 3. Vector Processor CORE (VP CORE)

The current section provides the architecture specification for the GPU's VPs. A detailed explanation of all the VP data structures is reviewed in the subsequent sections.

# 3.1. Introduction

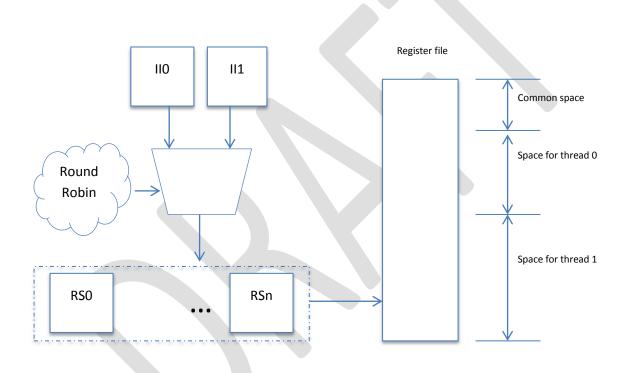

Each THEIA VP combines the features of a vector processor and a multithreaded out-of-order machine. This means that the VP is capable of sustaining various levels of instruction level parallelism (ILP) and data level parallelism. Instruction level parallelism is achieved by means of an in-order pipelined issue unit and several out-of-order execution units. The Tomasulo's algorithm [citation] is used to implement the out-of-order machine using the register renaming technique.

In order to cover for long stalls that the ILP from the out-of-execution can no longer prevent, a multithreading technique is used.

There are three main approaches to multithreading as mentioned by [1]: Fined grained multithreading, coarse-grained multithreading and simultaneous multithreading (SMT). The THEIA VP implements a simple version of SMT where up to 4 threads<sup>6</sup> can share the resources of a single VP unit.

As with most SMT implementations, all of the issues at a given point in time come from the same thread, but instructions from different threads can start executing on the same clock cycle (when dependencies are resolved at the reservation stations and so on). Since THEIA VP builds SMT on top on of an out-of-order machine, separate per-thread PC and renaming tables are maintained.

Data level parallelism is achieved by having 3 separate data lanes on each execution unit and also by means of vector processing techniques. Each THEIA VP has 256 x 32 bit registers which are divided logically across the 3 data lanes. These registers are implemented using a simple RAM memory structure divided into banks in order to provide the sufficient bandwidth for the vector operations. Each Thread is limited to access up to ¼ of the total register address<sup>7</sup> and there is no means of data sharing among the threads.

## 3.1.1. Single Thread execution example

This section will briefly describe the flow of the execution for a program running on a single thread. The next short code snippet will help clarify some of the concepts related to the VP execution and capabilities.<sup>8</sup> This code is written in a high level language called T-Language which is designed specifically to write code for the THEIA GPU. The language itself is described on separate document. Given that the T-Language closely resembles C/C++ it is assumed that an average reader can understand it.

<sup>&</sup>lt;sup>6</sup> This number may vary depending on the release of the RTL

<sup>&</sup>lt;sup>7</sup> When multithreading is disabled, the single thread has access to the entire register address space, this is in fact controlled by the software

<sup>&</sup>lt;sup>8</sup> The code snippet is written in "T-Language". For more information on the "T-Language" please refer to the <TBD> documentation.

Theia architecture specification

//Declare some variables. These variables will get stored in the internal VP register file

**vector** V1 = (1,2,3), V2=(4,5,6), V3=(7,8,9);

**vector** V4 = (10,11,12), V5=(13,14,15), V6=(16,17,18);

vector A[10], B[10], C[10];

//Some code to initialize the arrays goes in here

//Divide 2 variables. The division can take up to 32 clock cycles to complete

V1 = V2 / V3;

//Multiply two "arrays" in order to use the VP "vector" processing capabilities. //Thanks to the out of order nature of the VP this multiplications can be executed in //parallel with the previous division. Since each array has 10 element it will take the VP //10 clock cycles to complete the multiplications (each multiplication takes 1 clock cycle) C = B \* A;

//Now do a subtraction. Once more because of the out of order nature of the VP,

//this will happen in parallel with the previous two operations. Also play around with

//the "destination channel selector" and "swizzling" features

V4.**y** = V5.**yxz** – V6.**zyy**;

#### Figure 13 A sample code (single thread)

The above code is meant to give the machine the opportunity to execute several instructions in parallel as we are about to see. The code starts by declaring several variables. Each variable is called a "vector"

and consist of a single word which is divided among a 32 bit "X block", a 32 bit "Y block" and a 32 bit "Z block". Consider the following statements from the above code:

This code declares 3 variables: V1, V2 and V3. It also specifies that those variables should be initialized to the constant values (1,2,3), (4,5,6) and (7,8,9).

Each VP operation executes simultaneously on the X, Y and Z blocks of the data, meaning that the VP has 3 data lanes. In order words, each VP has 3 adders, 3 dividers, 3 multipliers and so on. Consider the division operation from Figure 13, in a single clock cycle the 3 dividers will trigger in order to start calculating the division for the X, Y and Z blocks from V2 and V3.

Since the VP runs in an out of order fashion, it doesn't need to wait until the division is complete in order to issue the next instruction. The next instruction is a multiplication; it multiplies two vector "arrays" together. A vector "array" is an array consisting of two or more vector elements (each element is a vector with an X block, a Y block and a Z block as before).

Each element from a *vector array* is internally allocated in consecutive memory positions so that the VP can perform a type of "data pipeline" using "convoys" of data<sup>9</sup>. This type of data level parallelism is typical in vector processor architectures.

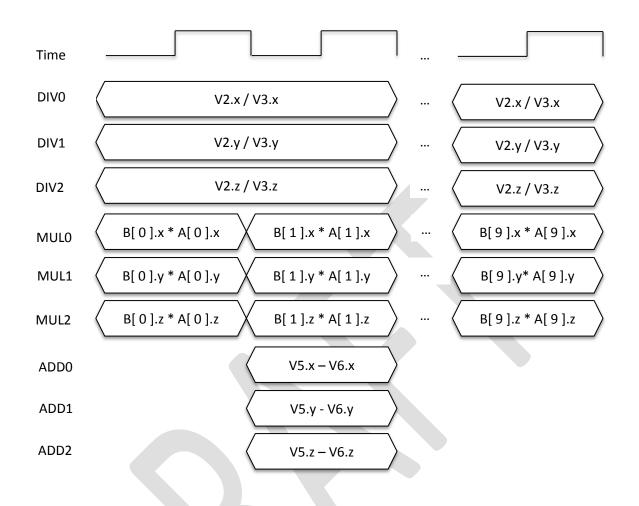

Figure 5 shows how the multiplications are executed in parallel with the division. Each clock cycle the VP's multipliers serially calculate the result of each vector array element in the data convoy. Next, the code specifies to execute a subtraction, this happens in parallel with the previous operations. Since the Additions/Subtractions take 1 clock cycle, then the subtraction is going to end before the array multiplication and the divisions are done.

<sup>&</sup>lt;sup>9</sup>See Hennesy and Paterson...

Theia architecture specification

Figure 14 Behaviour of the execution units over time for the example from Figure 13

Figure 14 shows the overlapping execution of the various execution units involved in the code from Figure 13. As it was mentioned before, the Division algorithm takes 32 clock cycles to complete (worst case). It is also interesting to observe how the multiplying units are kept busy working on the array elements with no need of a new instruction being issued. Also, since the addition units are free, those can handle additional operation over time as shown in Figure 14. The Architectural features allowing this kind of parallelism are described in the next sections.

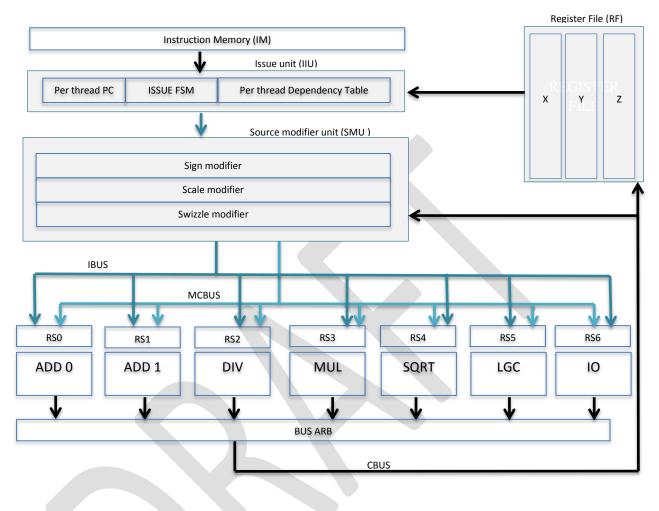

# 3.2. VP Architecture

The VP is the logic block responsible to perform the Arithmetic and Logic operations within each CORE. The VP can operate on vectors of data, each vector consisting of 3 32-bits words as explained in section 3.3. The VP features an in-order fetch and out-of-order execution following the classic Tomasulo's

#### <sup>10</sup>algorithm for register renaming.

Figure 15 shows the main building blocks of the VP. The instructions are initially fetched from the instruction memory (IM) by the IIU. Each instruction is a 64 bit word and the layout of the instruction is discussed in section 3.5.

Once the instruction is fetched, the IIU chooses a free reservation station (RS1 to RS6) to issue the instruction, according to the instruction OPCODE. If there are no reservation stations available to execute the instruction, then there is a structural hazard condition and the IIU stalls until an appropriate reservation station becomes available.

<sup>&</sup>lt;sup>10</sup> Note: with some modifications as that are specified in s subsequent sections.

If there are reservation stations available to execute the instruction, then the IIU determines the reservation station number and data dependencies that will be added into the *Issue packet* using the dependency table from Figure 1. The *issue packet* is a special data structure that is broadcasted to all the reservation stations connected to the Issue Bus. The format of the issue packet is discussed in section 4.1.2.1.

While the dependencies are established, the IIU also reads the instruction operand values from the register file RF. Each instruction operand value is a 96 bit word, and the layout of these words is discussed in section 3.3.

Once the operand values are retrieved from the RF, the operand manipulators (section 3.5.3) are applied in the following sequence:

First the sign control does a 2 complement on the individual X, Y and Z components of each operand source, as described in section 3.14.

Next the source operands are scaled according to the rules in section 3.13 and swizzled according to the rules in section 3.15.

Finally the source operands are presented to the issue bus, together with reservation station number and the dependency fields. The instruction is finally issued to the reservation stations, the dependency table gets updated with the current instruction and the Issue packet is broadcasted to the Reservation stations.

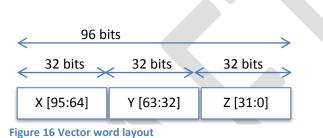

# 3.3. Word size and Endianness

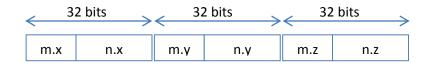

THEIA words are little endian, meaning that the least significant bit goes into the lowest address. Each word is 96 bits long and usually represents a 3D vector<sup>11</sup>; thus it is divided among three 32 bits value slots called X, Y and Z as depicted in Figure 16. Depending on the VP operation, the X, Y and Z components of the word can be individually accessed or the entire 96 bits can be accessed simultaneously.

# **3.4.** Fixed point arithmetic.

The VP has the ability to work with integer arithmetic or with fixed point arithmetic.

When working with integer arithmetic, the entire 32 bits from the X, Y or Z blocks of a word are used to store the integer value.

When working with fixed point arithmetic (Qm.n), the 'n' least significant bits of the X, Y or Z blocks are used to store the decimal part of the number, while the 'm' more significant bits of the X, Y or Z blocks are used to store the integer part of the number.

Theia architecture specification

<sup>&</sup>lt;sup>11</sup> 4D/Homogenous-coordinates are not natively supported at the hardware level.

Figure 17 Storing Fixed point numbers in a 96 bit word

The length of the 'n' bits of a Qm.n number is called the fixed point SCALE. The SCALE is used to transform numbers from fixed point to integer and vice versa and is also used as part of the fixed point multiplication and division operations<sup>12</sup>. Table 5 shows the way in which the arithmetic operations are performed when using integer arithmetic and when using fixed point arithmetic.

| <b>Table 5 Scaling</b> | arithmetic | operation | for fixed | point |

|------------------------|------------|-----------|-----------|-------|

|------------------------|------------|-----------|-----------|-------|

| Operation       | Integer        | Fixed Point           |

|-----------------|----------------|-----------------------|

| Addition        | R = A + B      | R = A + B             |

| Subtraction     | R=A-B          | R=A-B                 |

| Multiplication  | R = A * B      | R = (A * B) >> SCALE  |

| Division        | R = A / B      | R = ( A << SCALE) / B |

| Logic operation | See section <> | n/a                   |

It is important to mention that it is the compiler's responsibility to appropriately manage the SCALE in the operations to either use fixed point or integer arithmetic. In other words, the VP has no knowledge if a particular instruction should use fixed point or integer arithmetic; the VP only executes the operation after applying the SCALE to the input arguments according to Table 23. The logic operations are not affected by the SCALE.

## 3.5. Instruction overview

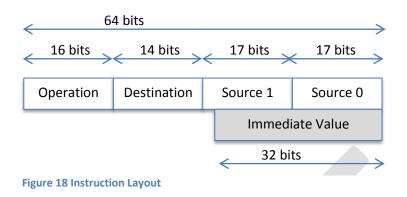

THEIA instructions are 64 bits wide. Each instruction is divided into various *"sections"* as depicted in Figure 18: operation section, destination section, source 1 and source 0 sections or immediate value section. The source 0 and source 1 sections are mutually exclusive with the immediate value section.

<sup>&</sup>lt;sup>12</sup> The square root operation is a special case which always assumes fixed point input arguments. See section 3.9 for details.

Theia architecture specification

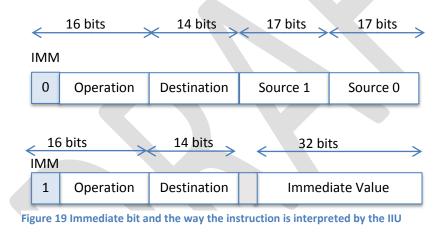

Each instruction section has special *fields* that modify the VP behavior in various ways. A very important field is the IMM field. The IMM field tells the VP whether it has to interpret the lowest 32 bits of the instruction as an immediate (literal) value, called IMMV, or as part of the register source sections. The IMM field also takes part in the addressing mode as discussed in section 3.6. Figure 19 illustrates how the VP interprets the instruction depending on the IMM bit.

Other instruction fields specify different behaviors such as which blocks of the resulting word to write back into the RF, how to handle the sign of the input operands, how to handle branches, etc. Table 13, Table 14, Table 18 and Table 19 show the various Instruction section fields and their meaning.

# **3.5.1.** Instruction operation codes

The instruction operation codes or OPCODEs are the set of all the possible arithmetic or logic operations that the VP is capable of doing. The VP is actually able to do a small number of different OPCODES:

Theia architecture specification

addition, multiplication, division, square root, IO and logic operations. This may seem as a small set of possible operations at first, but when combined with the instruction source modifiers from section 3.5.3, it becomes capable of doing a wide variety of operations.

Also, each of the possible OPCODES is executed simultaneously on the x, y and z blocks of the instruction sources. In other words, the VP has 3 adders, 3 multipliers, 3 dividers and so  $on^{13}$ . Table 6 lists the possible arithmetic operations the VP can do.

| Operation      | Description                                                                                                                    |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Addition       | $\begin{pmatrix} Rx \\ Ry \\ Rz \end{pmatrix} = \begin{pmatrix} Ax + Bx \\ Ay + By \\ Az + Bz \end{pmatrix}$                   |  |

| Multiplication | $\begin{pmatrix} Rx \\ Ry \\ Rz \end{pmatrix} = \begin{pmatrix} Ax * Bx \\ Ay * By \\ Az * Bz \end{pmatrix}$                   |  |

| Division       | $\begin{pmatrix} Rx \\ Ry \\ Rz \end{pmatrix} = \begin{pmatrix} Ax/Bx \\ Ay/By \\ Az/Bz \end{pmatrix}$                         |  |

| Square root    | $\begin{pmatrix} Rx \\ Ry \\ Rz \end{pmatrix} = \begin{pmatrix} \sqrt{Ax} \\ \sqrt{Ax} \\ \sqrt{Ax} \end{pmatrix}$             |  |

| Bitwise AND    | $\begin{pmatrix} Rx \\ Ry \\ Rz \end{pmatrix} = \begin{pmatrix} Ax \ AND \ Bx \\ Ay \ AND \ By \\ Az \ AND \ Bz \end{pmatrix}$ |  |

| Bitwise OR     | $\begin{pmatrix} Rx \\ Ry \\ Rz \end{pmatrix} = \begin{pmatrix} Ax \ OR \ Bx \\ Ay \ OR \ By \\ Az \ OR \ Bz \end{pmatrix}$    |  |

| Bitwise NOT    | $\begin{pmatrix} Rx \\ Ry \\ Rz \end{pmatrix} = \begin{pmatrix} NOT \ Ax \\ NOT \ Ay \\ NOT \ Az \end{pmatrix}$                |  |

| SHIFT LEFT     |                                                                                                                                |  |

Table 6 VP operations

<sup>&</sup>lt;sup>13</sup> The exception to this is the SQRT which has a single execution unit

Theia architecture specification

|             | $\begin{pmatrix} Rx \\ Ry \\ Rz \end{pmatrix} = \begin{pmatrix} Ax \ll Bx \\ Ay \ll By \\ Az \ll Bz \end{pmatrix}$ |

|-------------|--------------------------------------------------------------------------------------------------------------------|

| SHIFT RIGHT | $\begin{pmatrix} Rx \\ Ry \\ Rz \end{pmatrix} = \begin{pmatrix} Ax \gg Bx \\ Ay \gg By \\ Az \gg Bz \end{pmatrix}$ |

Note from Table 6 how each operation is simultaneously executed on the x, y and z blocks of the source data. Again, it is important to mention that the VP makes no distinction between fixed point numbers and integer numbers; it is the compiler that needs to apply the corresponding SCALE using the techniques from the next sections in order to obtain the proper result for integer numbers or fixed point numbers.

# 3.5.2. Instruction destination block selector

As mentioned in section 3.3, each THEIA word has 3 32 bit blocks called x, y and z. Each instruction has the ability to write the results simultaneously into the three destination blocks, or it can also choose to store the results into only some of the x, y and z blocks leaving the other blocks un-changed.

| Operation     | Description                                                                                                  |

|---------------|--------------------------------------------------------------------------------------------------------------|

| R = A + B     | $\begin{pmatrix} Rx \\ Ry \\ Rz \end{pmatrix} = \begin{pmatrix} Ax + Bx \\ Ay + By \\ Az + Bz \end{pmatrix}$ |

| R.y = A + B   | $\left(Ry\right) = \left(Ay + By\right)$                                                                     |

| R.xnz = A + B | $\binom{Rx}{Rz} = \binom{Ax + Bx}{Az + Bz}$                                                                  |

Table 7 Example of destination selection

Note from Table 7 that the 'n' symbol stands for no-write, so for example R1.xnz means to write the results into the x and z blocks but not into the 'y' block. Section 3.13 will list all of the possible combinations of destination blocks; from Table 7 it becomes clear that destination can be all of the

blocks, one single block or any two blocks.

# **3.5.3.** Instruction source modifiers

Instruction source modifiers are special ways in which the VP can modify the input source data (Source 0 (SRC0) and Source 1 (SRC1)) before they reach the execution units (EU).

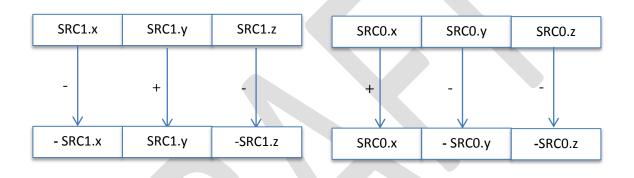

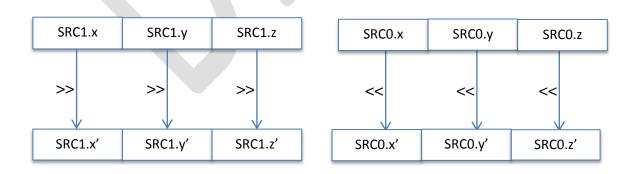

There are 3 ways in which the SRC0 and SRC1 data can be modified before they reach the EU: modifying the signs, modifying the scale or "*swizzling*" the data blocks. Each of these three modifications can be individually applied into the x, y or z blocks of SRC1 or SRC0. The next series of figures represent examples of possible source modifications.

#### Figure 20 Modifying the individual signs of the instruction sources

Figure 20 shows an example of how the signs of the individual x, y and z blocks of the data sources can be modified. The sign modification can be used for vector operations such as cross products. Furthermore, the VP does not have a subtraction operation *per se*, but instead the compiler is required to negate the SRC0 from an addition in order to perform a subtraction.

Figure 21 Modifying the scale of the instruction sources

Figure 21 illustrates a source scaling. Each x, y and z block can be shifted left or shifted right SCALE number of bits. The value of SCALE can be controlled by the setting the appropriate value in the configuration registers as will be detailed later on this document. The scale operations are used to transform numbers between the integer and fixed point numerical representations, and are also used to perform fixed point multiplications and divisions as it is specified on Table 5.

The last of the three possible source modifications is what is called "swizzling". Swizzling allows replacing the x, y or z blocks of a source register by any other x, y or z block from that same source register. This concept is illustrated in the next figure.

## Figure 22 Swizzling instruction sources

Register swizzle is a very powerful technique which allows the VP to perform a variety of operations. An example of the usefulness of operand swizzling is matrix multiplication. Let's take for instance the following 3x3 matrix multiplication:

$$\begin{pmatrix} 1 & 2 & 3 \\ 4 & 5 & 6 \\ 7 & 8 & 9 \end{pmatrix} * \begin{pmatrix} a \\ b \\ c \end{pmatrix} = \begin{pmatrix} 1a + 2b + 3c \\ 4a + 5b + 6c \\ 7a + 8b + 9c \end{pmatrix}$$

(1)

Let's assume that R1 has been loaded with the value (1,4,7), that R2 has been loaded with the value (2,5,8), that R3 has been loaded with the value (3,6,9), and that R4 has been loaded with the value (a,b,c). Equation (1) can be represented as series of swizzled operations in *T-language* like this:

The previous code shows that it would take the VP 5 operations to complete the 3x3 matrix

## multiplication.

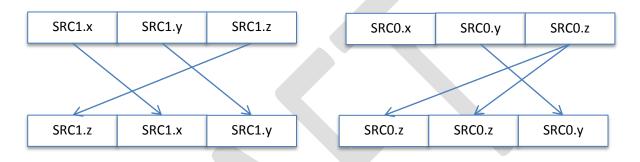

Finally it also possible to simultaneously combine the 3 types of source modifiers in a single instruction as illustrated in the next figure.

Figure 23 Combining several source modifiers in a single instruction

Figure 23 shows how it is possible to combine sign modifications, scaling and swizzling in the same instruction. To illustrate this, let's take for example a cross product vector operation. The cross product can be written as the following column of vectors:

$$\begin{pmatrix} Ax \\ Ay \\ Az \end{pmatrix} * \begin{pmatrix} Bx \\ By \\ Bz \end{pmatrix} = \begin{pmatrix} AyBz - AzBy \\ AzBx - AxBz \\ AxBy - AyBx \end{pmatrix}$$

(2)

You can see from (2) that the cross product needs to perform a series of subtractions (the VP uses sign control to negate the second argument for subtractions) and also needs to organize the sources in a special way in order to obtain the desired result. Let's assume that R1 has been loaded with the value (Ax, Ay, Az) and R2 has been loaded with the value (Bx, By, Bz). Equation (2) can be represented as series of swizzled operations in T-language<sup>14</sup> like this:

So the previous code shows that the VP can perform a cross product using only three instructions.

It is important to mention that the source modifiers are implemented as pure combinatorial blocks, this means that they add no extract latency to the operations.

<sup>&</sup>lt;sup>14</sup> This a special 'middle level' language specially designed for the THEIA GPU, more details on section <TBD> Theia architecture specification

Table 8 summarizes the three possible instruction source modifiers and the document section where more information can be found.

Table 8 instruction operand manipulators

| Instruction source<br>modifier | Document section | Description                          |

|--------------------------------|------------------|--------------------------------------|

| Swizzle control                | 3.15             | Input operand Swizzle control logic. |

| Sign control                   | 3.14             | Input operand Sign control logic.    |

| Scale control                  | 3.13             | Input operand Scale control logic.   |

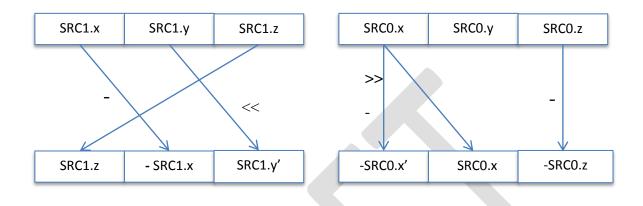

# 3.5.4. Data dependencies and source modifiers

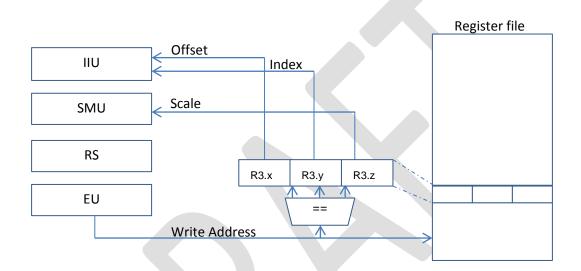

Looking back at Figure 15, it must be noted how the Source modifier unit (SMU) is connected to the issue unit (IIU) and is also connected to the commit bus (CBUS). This is because the SMU needs to apply the source modifiers to the data sources coming from the issue stage and it may also potentially need to apply source modifiers to the results from the execution units (EU) when the data dependencies get resolved. Let's illustrate this concept with an example.

R2 = (10,20,30);R3 = (2,0,0);

R1 = R2 / R3.xxx;

R2.y = R1.zzz + R1;

## Figure 24 Example of data dependencies when using source modifiers

In the example from Figure 24, the addition operation depends upon the result from the division operation. Because of the out-of-order execution, the addition instruction will be issued into the reservation stations regardless of the division result not being yet committed into the RF. Once the divider EU finishes calculating the result of the division, this result is written back into the RF and also forwarded into the SMU. The SMU needs to apply to proper modifiers to the result from the division EU and then present this modified result into the reservation stations so that the data dependencies can be properly resolved. This concept is illustrated in the next series of figures.

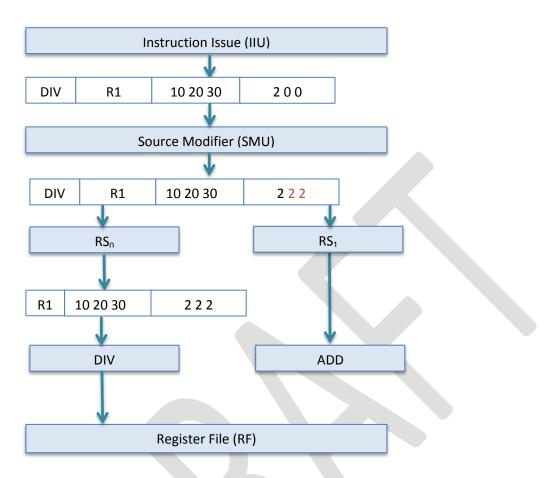

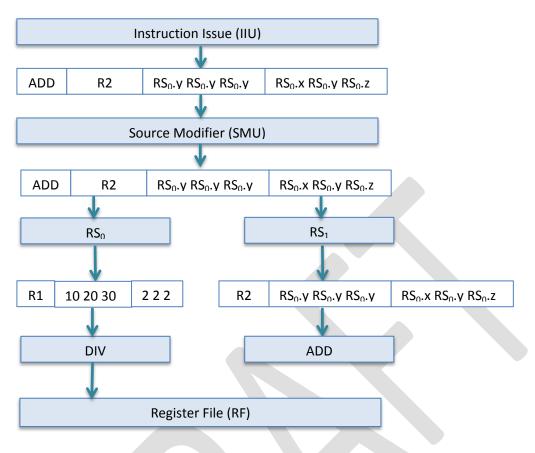

#### Figure 25 IIU issues a division

Figure 25 depicts the IIU is issuing the division instruction from Figure 24. The IIU retrieves the value of R2 (10, 20, 30) and the value of R3 (2, 0, 0) from the RF and then sends these vectors to the SMU. The SMU swizzles the values of R2 so that it becomes R2.xxx (2, 2, 2) and then broadcasts these values to the reservation stations along with the reservation station index (RSID)<sup>15</sup>. The reservation station whose index matches with the RSID broadcasted by the SMU latches the value, since no data dependencies where found, the RS triggers the corresponding EU (the divider for this example) using these input values from the SMU.

<sup>&</sup>lt;sup>15</sup> Not shown in the picture.

## Figure 26 The IIU issues an addition operation

While the Divider EU is busy calculating the result of DIV operation, the IIU issues the next instruction which is an addition. Since the addition source operands depends on the result from the division instruction, the IIU uses the register renaming technique to specify the reservation station that will resolve the data dependencies, this is illustrated in Figure 26. The RS<sub>1</sub> will not start the addition EU until it receives the result from RS<sub>0</sub>.

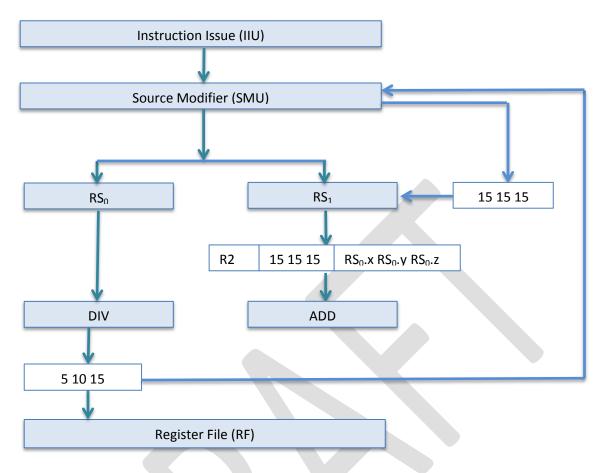

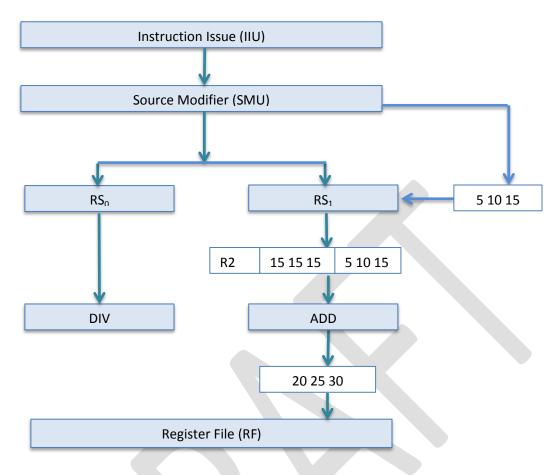

A number of clock cycles after issuing the DIV instruction, the divider EU is finally done calculating the result; this is shown in Figure 27. Figure 27 depicts the DIV EU committing the division results into the shared commit bus (CBUS). These results are also forwarded into the SMU, the SMU has a series of internal registers that store the various data dependencies that need to be scaled<sup>16</sup>, signed changed or swizzled. In this example, the SMU knows that it needs to propagate two result values from RS<sub>0</sub> back to the reservation stations. One value would be the division result using the "yyy" swizzle combination and the other value would be the division result with no modifiers. Figure 27 shows when the SMU issues the "yyy" swizzled value (15, 15, 15) back into the reservation stations<sup>17</sup>.

<sup>&</sup>lt;sup>16</sup> More detail on this on section 4.1.2

<sup>&</sup>lt;sup>17</sup> The order in which the dependencies values are presented by the SMU into the RSs is not deterministic. See section xxx for details.

Theia architecture specification