# Xgate Co-Processor (xgate) Specification

Author: Robert Hayes rehayes@opencores.org

> Rev. 0.1 November 9, 2009

This page has been intentionally left blank.

# **Revision History**

| Rev. | Date     | Author          | Description |

|------|----------|-----------------|-------------|

| 0.1  | 09/29/09 | Robert<br>Hayes |             |

|      |          |                 |             |

|      |          |                 |             |

# Contents

| INTRODUCTION                                   | 1 |

|------------------------------------------------|---|

| FEATURES                                       | 1 |

| ARCHITECTURE                                   |   |

| 2.1 WISHBONE SLAVE INTERFACE                   |   |

| 2.2 Control Registers                          |   |

| 2.3 INTERRUPT INTERFACE                        |   |

| 2.4 WISHBONE MASTER INTERFACE.                 |   |

| 2.5 RISC PROCESSOR CORE                        |   |

| OPERATION                                      | 9 |

| 3.1 Software Example                           | 9 |

| 3.2 Software Triggers                          |   |

| 3.3 PROGRAM MEMORY CONNECTION OPTIONS          |   |

| 3.4 INSTRUCTION SET SUMMARY                    |   |

| 3.4 INCONSISTENT INSTRUCTION SET DOCUMENTATION |   |

| REGISTERS                                      |   |

| LIST OF REGISTERS                              |   |

| 4.1 XGATE MODULE CONTROL REGISTER (XGMCTL)     |   |

| 4.2 XGATE CHANNEL ID REGISTER (XGCHID)         |   |

| 4.3 XGATE STACK POINTER REGISTER (XGISPHI)     |   |

| 4.4 XGATE STACK POINTER REGISTER (XGISPLO)     |   |

| 4.5 XGATE VECTOR BASE ADDRESS REGISTER (XGVBR) |   |

| 4.6 XGATE INTERRUPT FLAG REGISTER 7 (XGIFR_7)  |   |

| 4.6 XGATE SOFTWARE TRIGGER REGISTER (XGSWT)    |   |

| 4.6 XGATE SEMAPHORE REGISTER (XGSEM)           |   |

| 4.6 XGATE CONDITION CODE REGISTER (XGCCR)      |   |

| 4.6 XGATE PROGRAM COUNTER REGISTER (XGPC)      |   |

| 4.6 XGATE REGISTER 1 (XGR1)                    |   |

| CLOCKS                                         |   |

| IO PORTS                                       |   |

| 6.1 WISHBONE INTERFACE                         |   |

| 6.2 XGATE SIGNALS.                             |   |

| 6.3 XGATE CORE PARAMETERS                      |   |

| APPENDIX A                                     |   |

| INDEX                                          |   |

|                                                |   |

# 1

# Introduction

The Xgate Co-processor Module, Xgate, is a 16 bit programmable RISC processor that is managed by a host CPU to reduce the host load in handling interrupts. Because the Xgate is user programmable there is a great deal of user control in how to preprocess data from peripheral modules. This module may be configured as a simple DMA controller to organize data such that the host only operates with whole messages and not individual words or bytes. The Xgate may also handle higher levels of messaging protocols than the peripheral hardware recognizes. Encryption algorithms are also supported by the instruction set.

The ideal application for the Xgate co-processor is in an ASIC environment where a specific host processor is required but the host as a standalone processor lacks sufficient computational resources to service the target application. Such a situation might occur in an existing application that has an extensive software base or the host processor has a significant history in similar applications. In this environment the Xgate provides the additional resources needed for the application while also providing the user programmability that may allow the ASIC to be used in other applications.

The use of an Xgate co-processor in an FPGA may not be as advantageous as in an ASIC environment because of the reprogramability of the FPGA hardware. Because the Xgate co-processor offers a generic solution to a variety of problems and the functionality can be changed by upgrading user software without changing the FPGA hardware implementation it may still be a valuable solution to certain problems. The use of the Xgate module may also reduce development time since the application can begin debug sooner and changes can be prototyped in user software.

# FEATURES

- Instruction set compatible with Freescale XGATE co-processor

- Handles up to 127 interrupt inputs

- Eight software triggerable interrupt channels.

- Eight semaphore registers to coordinate host/Xgate shared memory.

- Static synchronous designFully synthesizable

# 2

# Architecture

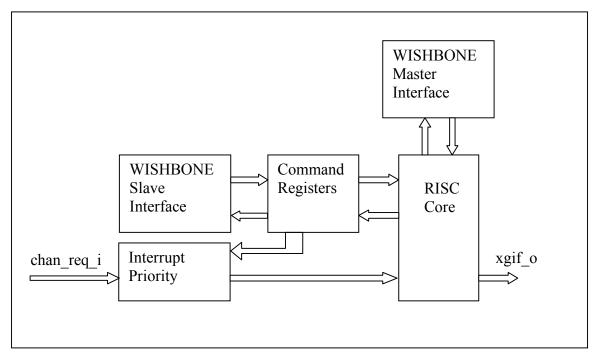

The Xgate core is built around five primary blocks; the WISHBONE Slave Interface, WISHBONE Master Interface, the Control Registers, Interrupt Priority, and RISC Processor Core.

Fig. 2.1 Internal structure Xgate Core

## 2.1 WISHBONE Slave Interface

The host processor uses this bus to access the Xgate control and status registers. The WISHBONE Slave Interface isolates the Xgate functionality from the WISHBONE bus. This interface takes the bus specific signals and generates a generic set of control signals to drive the Xgate control registers. Isolating the WISHBONE bus should help promote Xgate module reusability by localizing the scope of changes needed to retarget the Xgate module to another bus environment.

# 2.2 Control Registers

This module receives the generic write signals from the WISHBONE Slave Interface and applies these signals to the registers that the host processor uses to control Xgate operation.

# 2.3 Interrupt Interface

The Interrupt Interface takes the input interrupts from other slave peripheral modules and prioritizes them for processing by the Xgate RISC Processor Core.

#### 2.3.1 Simple Interrupt Interface

The current implementation uses the simplest interrupt interface with the least hardware and least functionality. This module takes the 127 interrupt inputs and does a simple encoding to generate the six bit bus that becomes the active channel select signal. The active interrupt input with the highest index number becomes the chosen channel select enable.

Because the Xgate module is in the signal path from the interrupt sources to the host CPU there must always be always be some code running in the Xgate module to activate the appropriate interrupt output to the CPU.

#### 2.3.2 Bypass Interrupt Interface

This is a proposed functional improvement and is not currently implemented. This module will do the same basic interrupt encoding as the "Simple Interrupt Interface" except it will include the additional functionality to allow an interrupt input to be bypassed around the Xgate module and connected directly to the host CPU. This will eliminate the latency and software overhead when it is required for the host CPU to process some interrupts directly while still reserving the option to enable the Xgate module to preprocess those same interrupt sources at some other time. To implement this functionality additional control registers will need to be added to the WISHBONE slave interface.

#### 2.3.3 Programmable Interrupt Interface

This is a proposed functional improvement and is not currently implemented. This module will include the functionality of the "Bypass Interrupt Interface" with additional functionality to allow interrupt priorities to be set by the host CPU. This will eliminate the latency and software overhead when it is required for the host CPU to process some interrupts directly while still reserving the option to enable the Xgate module to preprocess those same interrupt sources at some other time. To implement this functionality additional control registers will need to be added to the WISHBONE slave interface.

## 2.4 WISHBONE Master Interface

The Xgate module uses the WISHBONE Master Interface to access the shared memory space where it's software code, data, and other slave peripheral registers may be accessed. The WISHBONE Master Interface isolates the Xgate functionality from the WISHBONE bus. This interface takes the bus specific signals and generates a generic set of control signals to drive the Xgate RISC Processor. Isolating the WISHBONE bus should help promote Xgate module reusability by localizing the scope of changes needed to retarget the Xgate module to another bus environment.

## 2.5 RISC Processor Core

The RISC Processor Core is the key element of the Xgate module. This module implements the Xgate instruction set.

#### 2.5.1 Hardware Model

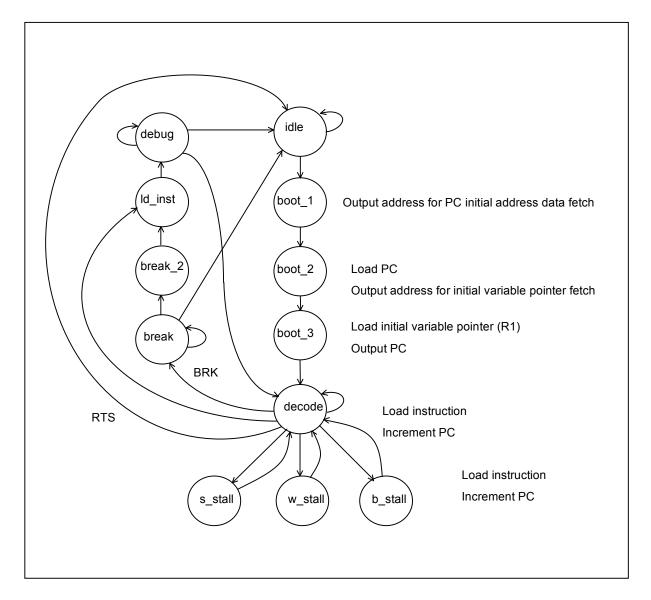

#### 2.5.2 State Machine

- Idle: The idle state is the condition where the xgate RISC processor waits to be enabled and an interrupt input to be activated.

- Boot\_1: State entered after an input interrupt is detected. Output the address stored in XGVBR + 2\*XGCHID to fetch PC (Program Counter).

- Boot\_2: State entered after Boot\_1. Load the PC and output the address of the variable pointer, XGVBR + 2\*XGCHID + 2.

- Boot\_3: State entered after Boot\_2. Load the variable pointer. Output the PC and prepare to load the first instruction.

- Decode: In normal user operation this is the state entered after Boot\_3 and the instruction is decoded and executed. For single cycle instructions, if Debug Mode is not active, then the Program Counter is incremented and the next instruction is loaded. For multi-cycle instructions one of the three instruction continue states is selected. If an RTS instruction is decoded then the state machine is returned to the Idle state to wait for the next change in XGCHID.

- S\_stall: Simple stall is the state that branch instructions use to change the PC when a change of flow is required. This state is also used for Store instructions.

- W\_stall: Word stall is the state Load instructions use to retrieve a word of RAM memory data.

- B\_stall: Byte stall is the state Load instructions use to retrieve a byte of RAM memory data.

- Break: If the Decode state detects a BRK command then the Break state is entered. The RISC processor remains in the Break state till:

Single Step Command

XGEN is set to zero

XGCHID is set to zero

- Break\_2: After a Single Step Command is issued in the Break state the PC is incremented in this state.

- Ld\_inst: The Load Instruction state is used in debug mode to load the next instruction to be executed into the RISC instruction register.

- Debug: debug is the state where the RISC processor waits for an input to execute the next command Exit conditions for this state are:

Single Step Command

XGEN is set to zero

XGCHID is set to zero

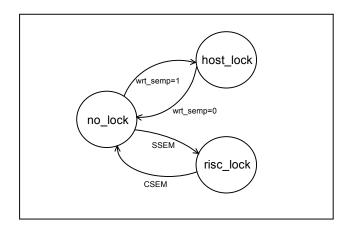

#### 2.5.3 Semaphore Bit

Each semaphore bit is a simple state machine that is controlled by write commands from either the host or RISC processor. The first write command to set a semaphore bit takes control of the semaphore state until the bit is cleared by the setting processor. The host has priority if the host and RISC processor attempt to write the semaphore bit in the same clock cycle. Each processor has a different read view of the semaphore bit so it can determine if it has successfully set the bit.

// Semaphore states

NO\_LOCK = 2'b00 RISC\_LOCK = 2'b10 HOST\_LOCK = 2'b11

These are the states for the semaphore bits. Only three of the four possible states are required to cover all the real things that can happen. For decoding the state of a semaphore bit the MSB is equivalent to "locked" and the LSB is equivalent to which processor is the one that owns the lock. Therefore state 2'b01 doesn't make sense because it implies there is no "lock" but the bit is owned by the host. In terms of the actual logic it probably makes little if any difference how the states are encoded but from the mental perspective it maybe helpful in understanding and debug to have the individual bits of the state be connected to a unique meaning.

# 3

# Operation

The Xgate Module is a simple RISC CPU with an instruction set ..... then the cop\_rst\_o will become active to force a system reset.

The COP module also has the capability to generate an interrupt at a programmed number of cycles before the cop\_rst\_o initiates a system reset. This functionality is primarily intended as a debug feature.

| General Purpose Registers | Program Counter                                      |

|---------------------------|------------------------------------------------------|

| R1 Variable Address       | 15 PC 0                                              |

| R2                        | Condition Code Desister                              |

| R3                        | Condition Code Register $15$ $N^3$ $v^2$ $z^1$ $c^0$ |

| R4                        | N V Z C                                              |

| R5                        |                                                      |

| R6                        |                                                      |

| R7                        |                                                      |

|                           | Programmers Model                                    |

A very readable article about watchdog timers and their use:

# 3.1 Software Example

The recommended software procedure for using the Xgate Module:

- 1. Initialize Xgate

- a) Load RAM with Xgate software.

- b) Set XGVBR register to base address of input interrupt vectors.

- c) Enable Xgate by setting the XGE bit.

- d) Enable host to accept interrupts.

- e) Enable peripheral modules to output interrupts as required.

- 2. Normal Operation

- a) Service Xgate interrupt requests as they are received by the host.

### 3.2 Software Triggers

## 3.3 Semaphore Bits

### **3.4 Program Memory Connection Options**

### 3.5 Debug Mode

#### **3.6 Instruction Set Summary**

The RISC Processor Core is the key element of the Xgate module. This module implements the Xgate instruction set.

| Function                            | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------------------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Return to<br>Scheduler and<br>other |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| BRK                                 | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| NOP                                 | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

# **3.7 Inconsistent Instruction Set Documentation**

The following instructions have problems in the Freescale documentation.

#### 3.4.1 SUBL

Freescale Documentation:

V: Set if a two's complement overflow resulted from the 8-bit operation; cleared otherwise.

RD[15]old & !RD[15]new

C: Set if there is a carry from the bit 7 to bit 8 of the result; cleared otherwise. !RD[15]old & RD[15]new

Xgate implementation:

For signed subtraction the rules for overflow are:

Negative number minus Positive number creates a Positive number OR

Positive number minus Negative number creates a Negative number

So the overflow calculation should be:

V = RD[7] & !IMM8[7] & !result[7] | !RD[7] & IMM8[7] & result[7]

The Carry calculation should be:

C = !RD[7] & IMM8[7] | !RD[7] & result[7] | IMM8[7] & result[7]

These calculations for setting the Carry and Overflow bits are also consistent with the calculations used to set the Carry and Overflow bits using the CMPL instruction.

#### 3.4.2 ADDL

Freescale Documentation:

V: Set if a two's complement overflow resulted from the 8-bit operation; cleared otherwise. RD[15]old & RD[15]new C: Set if there is a carry from the bit 7 to bit 8 of the result; cleared otherwise. RD[15]old & RD[15]new

Xgate implementation:

For signed addition the rules for overflow are:

Positive number plus Positive number creates a Negative number OR

Negative number plus Negative number creates a Positive number

So the overflow calculation should be:

V = !RD[7] & !IMM8[7] & result[7] | RD[7] & IMM8[7] & !result[7]

The Carry calculation should be:

C = !RD[7] & IMM8[7] | RD[7] & !result[7] | IMM8[7] & !result[7]

# 4

# Registers

The Xgate Module has a WISHBONE bus interface configured for a 16-bit bus width 16-bit granularity.

This module address map will probably change to a byte addressable to be consistent with the byte addressable functionality of the Xgate RISC processor.

| Name    | Address | Width | Access | Description                        |

|---------|---------|-------|--------|------------------------------------|

| XGMCTL  | 0x00    | 16    | RW     | Xgate Module Control Register      |

| XGCHID  | 0x01    | 16    | RW     | Xgate Channel ID Register          |

| XGISPHI | 0x02    | 16    | RW     | Xgate Interrupt Stack Pointer High |

| XGISPLO | 0x03    | 16    | RW     | Xgate Interrupt Stack Pointer Low  |

| XGVBR   | 0x04    | 16    | RW     | Xgate Vector Base Address          |

| XGIF_7  | 0x05    | 16    | RW     | Xgate Interrupt Flag Register #7   |

| XGIF_6  | 0x06    | 16    | RW     | Xgate Interrupt Flag Register #6   |

| XGIF_5  | 0x07    | 16    | RW     | Xgate Interrupt Flag Register #5   |

| XGIF_4  | 0x08    | 16    | RW     | Xgate Interrupt Flag Register #4   |

| XGIF_3  | 0x09    | 16    | RW     | Xgate Interrupt Flag Register #3   |

| XGIF_2  | 0x0A    | 16    | RW     | Xgate Interrupt Flag Register #2   |

| XGIF_1  | 0x0B    | 16    | RW     | Xgate Interrupt Flag Register #1   |

| XGIF_0  | 0x0C    | 16    | RW     | Xgate Interrupt Flag Register #0   |

| XGSWT   | 0x0D    | 16    | RW     | Xgate Software Trigger Register    |

| XGSEM   | 0x0E    | 16    | RW     | Xgate Semaphore Register           |

|         | 0x0F    | 16    | R      | Reserved                           |

| XGCCR   | 0x10    | 16    | RW     | Xgate Condition Code Register      |

## List of Registers

| Name | Address | Width | Access | Description           |

|------|---------|-------|--------|-----------------------|

| XGPC | 0x11    | 16    | RW     | Xgate Program Counter |

|      | 0x12    | 16    | R      | Reserved              |

| XGR1 | 0x13    | 16    | RW     | Xgate Register 1      |

| XGR2 | 0x14    | 16    | RW     | Xgate Register 2      |

| XGR3 | 0x15    | 16    | RW     | Xgate Register 3      |

| XGR4 | 0x16    | 16    | RW     | Xgate Register 4      |

| XGR5 | 0x17    | 16    | RW     | Xgate Register 5      |

| XGR6 | 0x18    | 16    | RW     | Xgate Register 6      |

| XGR7 | 0x19    | 16    | RW     | Xgate Register 7      |

Table 1: List of registers

# 4.1 Xgate Module Control Register (XGMCTL)

| Bit # | Access | Description                                                                                                    |

|-------|--------|----------------------------------------------------------------------------------------------------------------|

| 15    | W      | XGEM, XGE Mask – The XGE bit can only be changed when the XGEM bit is set in the same register access.         |

|       |        | <ul><li>'0' No change allowed to XGE control bit.</li><li>'1' Change allowed to XGE control bit.</li></ul>     |

|       |        | Always reads as '0'.                                                                                           |

| 14    | W      | XGFRZM, XGFRZ Mask – The XGFRZ bit can only be changed when the XGEM bit is set in the same register access.   |

|       |        | <ul><li>'0' No change allowed to XGFRZ control bit.</li><li>'1' Change allowed XGFRZ control bit.</li></ul>    |

|       |        | Always reads as '0'.                                                                                           |

| 13    | W      | XGDGBM, XGDGB Mask – The XGDGB bit can only be changed when the XGDGBM bit is set in the same register access. |

|       |        | " " " " " " " " " " " " " " " " " " "                                                                          |

|       |        | Always reads as '0'.                                                                                           |

| 12    | W      | XGSSM, XGSS Mask – The XGSS bit can only be changed when the XGSSM bit is set in the same register access.     |

|       |        | '0' No change allowed to XGSS control bit.                                                                     |

| Bit # | Access | Description                                                                                                                                                                                                                                      |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |        | '1' Change allowed to XGSS control bit.                                                                                                                                                                                                          |

|       |        | Always reads as '0'.                                                                                                                                                                                                                             |

| 11    | W      | XGFACTM, XGFACT Mask – The XGFACT bit can only be changed when the XGFACTM bit is set in the same register access.                                                                                                                               |

|       |        | <ul><li>'0' No change allowed to XGFACT control bit.</li><li>'1' Change allowed to XGFACT control bit.</li></ul>                                                                                                                                 |

|       |        | Always reads as '0'.                                                                                                                                                                                                                             |

| 10    |        | BRK_IRQ_ENM, BRK_IRQ_EN Mask – The BRK_IRQ_EN bit can only be changed when the BRK_IRQ_ENM bit is set in the same register access.                                                                                                               |

|       |        | <ul><li>'0' No change allowed to BRK_IRQ_EN control bit.</li><li>'1' Change allowed to BRK_IRQ_EN control bit.</li></ul>                                                                                                                         |

|       |        | Always reads as '0'.                                                                                                                                                                                                                             |

| 9     | RW     | XGSWEIFM, XGSWEIF Mask – The XGSWEIF bit can only<br>be changed when the XGSWEIFM bit is set in the same<br>register access.                                                                                                                     |

|       |        | <ul><li>'0' No change allowed to XGSWEIF control bit.</li><li>'1' Change allowed to XGSWEIF control bit.</li></ul>                                                                                                                               |

|       |        | Always reads as '0'.                                                                                                                                                                                                                             |

| 8     | RW     | XGIEM, XGIE Mask – The XGIE bit can only be changed when the XGIEM bit is set in the same register access.                                                                                                                                       |

|       |        | '0' No change allowed to XGIE control bit.                                                                                                                                                                                                       |

|       |        | '1' Change allowed to XGIE control bit.                                                                                                                                                                                                          |

|       |        | Always reads as '0'.                                                                                                                                                                                                                             |

| 7     | RW     | XGE, XG Enable – The XGE bit can only be changed when the XGEM bit is set in the same register access.                                                                                                                                           |

|       |        | <ul><li>'0' The Xgate module is disabled. The currently active interrupt request will be completed and then no new interrupt processing requests will be accepted.</li><li>'1' The Xgate module is enabled to start processing channel</li></ul> |

|       |        | interrupts.                                                                                                                                                                                                                                      |

| 6     | RW     | XGFRZ, XG Freeze Mode – The XGE bit can only be changed<br>when the XGEM bit is set in the same register access.                                                                                                                                 |

|       |        | '0' The Xgate module is disabled. The currently active channel interrupt will be completed and then no new interrupt channel processing requests will be accepted.                                                                               |

| Bit # | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |        | '1' The Xgate module is enabled to start processing channel interrupts.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5     | RW     | <ul> <li>XGDBG, XG Debug Mode – The XGDBG bit can only be changed when the XGDBGM bit is set in the same register access.</li> <li>'0' The Xgate module is not in DEBUG Mode.</li> <li>'1' The Xgate module is in DEBUG Mode. Along with writing to the XGGBG bit from the host interface DEBUG Mode can also be entered by executing the 'BRK' instruction by the RISC Processor Core.</li> </ul>                                                                                                                           |

| 4     | RW     | XGSS, XG Single Step – The XGSS bit can only be changed<br>when the XGSSM bit is set in the same register access.<br>'0' The Xgate module is disabled. The currently active<br>channel interrupt will be completed and then no new interrupt<br>channel processing requests will be accepted.<br>'1' Write - Xgate module should execute a single RISC<br>instruction. Read – A RISC instruction is being processed.                                                                                                         |

| 3     | RW     | XGFACT, XG Fake Activity – The XGFACT bit can only be<br>changed when the XGFACTM bit is set in the same register<br>access.<br>'0' The Xgate module is disabled. The currently active<br>channel interrupt will be completed and then no new interrupt<br>channel processing requests will be accepted.<br>'1' The Xgate module is enabled to start processing channel<br>interrupts.                                                                                                                                       |

| 2     | RW     | <ul> <li>BRK_IRQ_EN, Break Interrupt Enable – The BRK_IRQ_EN bit can only be changed when the BRK_IRQ_EN M bit is set in the same register access.</li> <li>'0' The Xgate module is operating in a mode compatible with the Freescale XGATE module. BRK instructions do not generate an Xgate error interrupt output.</li> <li>'1' The Xgate module is enabled to output an error interrupt whenever a BRK command is encountered. Set this bit whenever no BRK commands are expected to be used in the software.</li> </ul> |

| 1     | RW     | XGSWEIF, XG Software Error Interrupt Flag – The XGSWEIF bit can only be changed when the XGSWEIFM bit is set in the same register access.<br>'0' The Xgate module is operating correctly. Writing '0' has                                                                                                                                                                                                                                                                                                                    |

| Bit # | Access | Description                                                                                                                                                                                                                                                   |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |        | no effect.<br>'1' The Xgate RISC processor has detected an error condition.<br>Writing '1' will clear a set XGSWEIF bit and terminate the<br>current interrupt process. The Xgate module will go to an<br>IDLE state if no other interrupt inputs are active. |

| 0     | RW     | XGIE, XG Interrupt Enable – The XGIE bit can only be<br>changed when the XGEM bit is set in the same register access.<br>'0' All Xgate module interrupt outputs are disabled.<br>'1' All Xgate module interrupt outputs are enabled.                          |

Reset Value:

#### XGMCTL: 0004h

#### Table 2: CNTRL Register Bits

# 4.2 Xgate Channel ID Register (XGCHID)

| Bit # | Access | Description                                                                                                                                                                                    |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:7  | R      | Reserved, write zeros for future compatibility.                                                                                                                                                |

| 6:0   | RW     | XGCHID, XG Channel ID – The XGCHID register reflects the value of the current interrupt channel being processed.                                                                               |

|       |        | <ul><li>'0' No interrupt currently being processed.</li><li>'1' The encoded value of the input interrupt currently being processed.</li></ul>                                                  |

|       |        | The XGCHID can only be written in DEBUG Mode. When a value<br>is written to the XGCHID register the RISC Processor Core will<br>start executing the code associated with that interrupt input. |

Reset Value: XGCHID: 0000h

Table 4: Channel ID Register Bits

# 4.3 Xgate Stack Pointer Register (XGISPHI)

| Bit # | Access | Description |

|-------|--------|-------------|

|-------|--------|-------------|

| Bit # | Access | Description                                                                                                                                                                                                       |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0  | RW     | XGISPHI, Read returns the current state of the COP Watchdog Counter.                                                                                                                                              |

|       |        | Writes to the CNT register access the COP service words. To reset<br>the COP Watchdog Counter to the TOUT_VAL state two specific<br>service words must be written in the correct order to prevent a COP<br>reset. |

Reset Value:

XGISP74: 0000h

Table 5: XGIPS74 Register Bits

# 4.4 Xgate Stack Pointer Register (XGISPLO)

| Bit # | Access | Description                                                                                                                                                                                                       |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0  | RW     | XGISPLO, Read returns the current state of the COP Watchdog Counter.                                                                                                                                              |

|       |        | Writes to the CNT register access the COP service words. To reset<br>the COP Watchdog Counter to the TOUT_VAL state two specific<br>service words must be written in the correct order to prevent a COP<br>reset. |

Reset Value:

XGISP31: 0000h

Table 5: XGIPS31 Register Bits

# 4.5 Xgate Vector Base Address Register (XGVBR)

| Bit # | Access | Description                                                                                                                                                                   |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:1  | RW     | XGVBR, Sets the vector base address that the Xgate RISC Core<br>uses to determine where in the memory map the code and data<br>space is for a specific interrupt is reserved. |

Reset Value:

XGVBR: FE00h

Table 5: XGVBR Register Bits

# 4.6 Xgate Interrupt Flag Register 7 (XGIFR 7)

The bits in this register reflect the state of interrupts that are being output from the Xgate module to the host CPU. A bit is set by the Xgate module with the "SIF" instruction usually at the end of a process and the host CPU clears the XGIF bit as part of its interrupt service routine.

Clear the interrupt output by writing a '1' to the corresponding XGIF register bit.

The highest numbered interrupt is in the MSB position of the register bank.

Some bits in this register may be unimplemented in a specific hardware design based on the setting of the "MAX CHANNEL" parameter and will always read as "0".

| Bit # | Access | Description                  |

|-------|--------|------------------------------|

| 15:0  | RW     | XGIF_127 – XGIF_112          |

|       |        | '0' No interrupt.            |

|       |        | '1' Interrupt output active. |

Reset Value:

XGIFR 7: 0000h

| Table 5: XGIF | _7 Register Bits |

|---------------|------------------|

|---------------|------------------|

# 4.6 Xgate Software Trigger Register (XGSWT)

| Bit # | Access | Description                                                                                                                                                                                                   |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8  | W      | XGSWTM[7:0], Read always returns zero.                                                                                                                                                                        |

|       |        | XGSWTM, XGSWT Mask – The XGSWT bits can only be<br>changed when the XGSWTM bit is set in the same register access.<br>'0' No change allowed to XGSWT control bit.<br>'1' Change allowed to XGSWT control bit. |

|       |        | Always reads as '0'.                                                                                                                                                                                          |

| 7:0   | RW     | XGSWT[7:0], XG Software Trigger – The XGSWT bit can only be changed when the XGSWTM bit is set in the same register access.                                                                                   |

|       |        | '0' The Xgate module is disabled. The currently active interrupt request will be completed and then no new interrupt processing requests will be accepted.                                                    |

|       |        | '1' The Xgate module is enabled to start processing channel                                                                                                                                                   |

| Bit # | Access | Description |

|-------|--------|-------------|

|       |        | interrupts. |

Reset Value:

XGSWT: 0000h

Table 5: XGSWT Register Bits

# 4.6 Xgate Semaphore Register (XGSEM)

| Bit # | Access | Description                                                                                                                                                                                                        |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8  | W      | XGSEMM, XGSEM Mask – The XGSEM bit can only be changed when the XGSEMM bit is set in the same register access.                                                                                                     |

|       |        | '0' No change allowed to XGSEM control bit.                                                                                                                                                                        |

|       |        | '1' Change allowed to XGSEM control bit.                                                                                                                                                                           |

|       |        | Always reads as '0'.                                                                                                                                                                                               |

| 7:0   | RW     | XGSWT[7:0], XG Software Trigger – The XGSWT bit can only be changed when the XGSWTM bit is set in the same register access.                                                                                        |

|       |        | '0' The semaphore bit is either unlocked or locked by the Xgate module. If the host attempts to set the bit by writing a '1' and a subsequent read of the bit returns a '0' the bit is locked by the Xgate module. |

|       |        | '1' The semaphore bit is locked by the host processor. The host writes a '0' to clear the bit and unlock the semaphore.                                                                                            |

Reset Value: XGSEM: 0000h

Table 5: XGSEM Register Bits

# 4.6 Xgate Condition Code Register (XGCCR)

| Bit # | Access | Description                                                                                                  |

|-------|--------|--------------------------------------------------------------------------------------------------------------|

| 15:4  | R      | Reserved, write zeros for future compatibility.                                                              |

| 3     | RW     | XGN, Xgate Negative – Reflects the current state of the "Negative" bit of the Xgate condition code register. |

| Bit # | Access | Description                                                                                                  |

|-------|--------|--------------------------------------------------------------------------------------------------------------|

| 2     | RW     | XGZ, Xgate Zero – Reflects the current state of the "Zero" bit of the Xgate condition code register.         |

| 1     | RW     | XGV, Xgate Overflow – Reflects the current state of the "Overflow" bit of the Xgate condition code register. |

| 0     | RW     | XGC, Xgate Carry – Reflects the current state of the "Carry" bit of the Xgate condition code register.       |

Reset Value:

XGCCR: 0000h

Table 5: XGCCR Register Bits

# 4.6 Xgate Program Counter Register (XGPC)

| Bit # | Access | Description                                                        |

|-------|--------|--------------------------------------------------------------------|

| 15:0  | RW     | XGPC, Read returns the current state of the Xgate Program Counter. |

|       |        | Writes to the XGPC register can only be done in Debug Mode.        |

Reset Value:

XGPC: 0000h

Table 5: XGPC Register Bits

# 4.6 Xgate Register 1 (XGR1)

| Bit # | Access | Description                                                                   |

|-------|--------|-------------------------------------------------------------------------------|

| 15:0  | RW     | XGR1, Read returns the current state of the Xgate General Purpose Register 1. |

|       |        | Writes to the XGR1 register can only be done in Debug Mode.                   |

Reset Value:

XGR1: 0000h

Table 5: XGR1 Register Bits

# 5

# Clocks

| Name          | Source | Rates (MHz) |     |            | Remarks                                                                  | Description                |

|---------------|--------|-------------|-----|------------|--------------------------------------------------------------------------|----------------------------|

|               |        | Max         | Min | Resolution |                                                                          |                            |

| wbs_clk_<br>i | System | 200         | -   | -          | Master clock for all<br>Xgate bus registers.<br>Positive edge<br>active. | System clock.              |

| risc_clk_i    | System |             |     |            |                                                                          | RISC<br>Processor<br>clock |

#### Table 3: List of clocks

The wbs\_clk\_i has no timing constraints based on the RTL implementation although there may be constrains applied for synthesis results to be compatible with the target physical implementation. If the Xgate is targeted for an ASIC implementation then [wbs\_clk\_i] should be used as the scan clock, any clock multiplexing required to make [wbs\_clk\_i] the scan clock should be done at the system level external to the Xgate Module.

The risc\_clk\_i is the clock used to run the Xgate RISC processor submodule. The frequency of this clock should be the same as or 2X the frequency of the wbs\_clk\_i input. The risc\_clk\_i input is assumed to be in phase with the wbs\_clk\_i input.

# 6 IO Ports

| Port      | Width | Direction | Description                               |

|-----------|-------|-----------|-------------------------------------------|

| wbs_clk_i | 1     | Input     | WISHBONE Bus Clock Input, Master Clock    |

| wbs_rst_i | 1     | Input     | WISHBONE Slave Synchronous Reset          |

| wbs_adr_i | 5     | Input     | WISHBONE Slave Lower address bits         |

| wbs_dat_i | 16    | Input     | WISHBONE Slave Bus Data                   |

| wbs_dat_o | 16    | Output    | WISHBONE Slave Bus Data                   |

| wbs_we_i  | 1     | Input     | WISHBONE Slave Write enable               |

| wbs_stb_i | 1     | Input     | WISHBONE Slave Strobe signal/Core select  |

| wbs_cyc_i | 1     | Input     | WISHBONE Slave Valid bus cycle            |

| wbs_sel_i | 2     | Input     | WISHBONE Slave Data Bus Byte Select       |

| wbs_ack_o | 1     | Output    | WISHBONE Slave Bus cycle acknowledge      |

|           |       |           |                                           |

| wbm_adr_o | 16    | Output    | WISHBONE Master address bits              |

| wbm_dat_i | 16    | Input     | WISHBONE Master Bus Data                  |

| wbm_dat_o | 16    | Output    | WISHBONE Master Bus Data                  |

| wbm_we_o  | 1     | Output    | WISHBONE Master Write enable              |

| wbm_stb_o | 1     | Output    | WISHBONE Master Strobe signal/Core select |

| wbm_cyc_o | 1     | Output    | WISHBONE Master Valid bus cycle           |

| wbm_sel_o | 2     | Output    | WISHBONE Master Data Bus Byte Select      |

| wbm ack i | 1     | Input     | WISHBONE Master Bus cycle acknowledge     |

| Port               | Width | Direction | Description                              |

|--------------------|-------|-----------|------------------------------------------|

| arst_i 1           |       | Input     | Asynchronous Reset                       |

| risc_clk_i         | 1     | Input     | Clock signal for the RISC Core Processor |

| chan_req_i         | 127   | Input     | Xgate Interrupt Request                  |

| xgif_o             | 127   | Output    | Xgate Interrupt Requext                  |

| xg_sw_irq          | 1     | Output    | Xgate Software Error Interrupt           |

| xgswt              | 8     | Output    | Xgate Software Trigger                   |

| debug_mode_ 1<br>i |       | Input     | Force Xgate into debug mode              |

| secure_mode_ 1     |       | Input     | Limit host access to RISC core registers |

| scantestmode_ 1 I  |       | Input     | Scan Test Mode Enable                    |

Table 4: List of IO ports

## 6.1 WISHBONE Slave Interface

The core features a WISHBONE RevB.3 compliant WISHBONE Classic interface that operates in SLAVE mode. All output signals are registered. Each access takes 2 clock cycles. To limit a WISHBONE access to just two clock cycles the following synthesis rules should be used:

- Single cycle timing for wbs\_cyc\_i and wbs\_stb\_i

- Two cycle timing for wbs\_adr\_i, wbs\_data\_i, and wbs\_data\_o. (Single cycle timing could be used but it would be a waste of resources to meet an over constrained timing path.)

Note: Use the "SINGLE\_CYCLE" parameter to do a WISHBONE bus access in one clock cycle.

| WISHBONE DATASHEET   |                   |  |  |

|----------------------|-------------------|--|--|

| Description          | Specification     |  |  |

| General description: | 8-bit SLAVE       |  |  |

| Supported Cycles:    | SLAVE, READ/WRITE |  |  |

| Data port, size:                             | Default: 16, option 8 bit                    |                 |

|----------------------------------------------|----------------------------------------------|-----------------|

| Data port, granularity:                      | Default: 16, option to match 8 bit port size |                 |

| Data port, maximum operand size:             |                                              |                 |

| Data transfer ordering:                      |                                              |                 |

| Data transfer sequencing:                    |                                              |                 |

| Supported signal list and cross reference to | Signal Name                                  | WISHBONE Equiv. |

| equivalent WISHBONE signals:                 | wbs_clk_i                                    | CLK_I           |

|                                              | wbs_rst_i                                    | RST_I           |

|                                              | wbs_adr_i                                    | ADR_I()         |

|                                              | wbs_dat_i                                    | DAT_I()         |

|                                              | wbs_dat_o                                    | DAT_O()         |

|                                              | wbs_we_i                                     | WE_I            |

|                                              | wbs_stb_i                                    | STB_I           |

|                                              | wbs_cyc_i                                    | CYC_I           |

|                                              | wbs_sel_i                                    | SEL_I()         |

|                                              | wbs_ack_o                                    | ACK_O           |

#### 6.1.1 wbs\_rst\_i

The synchronous reset signal has a minimum pulse width requirement of one [wbs\_clk\_i] clock period. It will take two [wbs\_clk\_i] clock cycles for all registers in the Xgate Module to initialize. Also see information on pin [arst\_i].

#### 6.1.2 wbs\_adr\_i

Connections to the WISHBONE address pins will depend on the size of the WISHBONE data bus that is set by the DWIDTH parameter. If DWIDTH=8 the all address pins should be connected, if DWIDTH=16 then [wbs\_adr\_i(2)] should be tied low.

#### 6.1.3 wbs\_sel\_i

The [wbs\_sel\_i] is the WISHBONE byte lane select signal. It is currently unimplemented in the Xgate module and should be tied hi.

# 6.2 Xgate signals

## 6.2.1 xgif\_o[127:0]

The Xgate output signal. This output is the result of executing the SIF command by the Xgate RISC processor. The normal connection is to the interrupt inputs of the host processor.

### 6.2.2 chan\_req\_i[127:0]

These signals are the interrupt inputs from the prepherial modules that the Xgate services. The eight outputs of the xgswt\_o bus may also connect to some subset these inputs.

#### 6.2.3 xgswt\_o[7:0]

The [xgswt\_o] signal is active low. These signals are activated by the host processor writing to the XGSWT register. These signals are connected to a user selected subset of the [chan\_req\_i] inputs to trigger the Xgate coprocessor to execute a software routine associated with the selected XGSWT register bit. The host should respond the the setting of one of the [xgif\_o] outputs by clearing the set bit in the XGSWT register. Priority of the software routine executed is determined by which [chan\_req\_i] input the [xgswt\_o] signal is connected to.

### 6.2.4 arst\_i

The signal [arst\_i] is an asynchronous reset signal that goes to all flops in the COP. It is provided for FPGA implementations and test methodologies that require this function for initialization. Using [arst\_i] instead of [wb\_rst\_i] can result in lower cell-usage and higher performance for a FPGAs implementation because the standard FPGA cell already provides a dedicated asynchronous reset path. Using [wb\_rst\_i] for an ASIC implementation might synthesize to a smaller module because smaller non\_reset flops can be used. Use either [arst\_i] or [wb\_rst\_i], tie the other to a negated state. The active level of [arst\_i] is determined by the parameter ARST\_LVL that defaults to active low.

### 6.2.6 xg\_sw\_irq\_o

This output signal is activated whenever the Xgate is activated whenever the encounters a software error. These errors are:

- 1. Instruction error

- 2. Instruction Address error

- 3. Load/Store Word Address error

#### 6.2.7 risc\_clk\_i

The [risc\_clk\_i] is the clock input signal used by the RISC core processor.

#### 6.2.8 debug\_mode\_i

The [debug\_mode\_i] input can be used by an external source such as a debug module to force the Xgate RISC core processor into debug mode. The exact number of clock cycles between the [debug\_mode\_i] signal going active and the RISC core stopping instruction execution may vary between one and several clock cycles. If no external debug activation is required then the [debug\_mode\_i] signal should be tied low.

#### 6.2.9 secure\_mode\_i

The [secure\_mode\_i] input is used to limit host read access to the RISC core registers for software security reasons. In an ASIC implementation this pin would be tied to a non-volatile memory bit that is only cleared when all of the Xgate program memory is also cleared. In an FPGA implementation the signal may be tied to a level consistent with the desired application security level. If no software security is required then the [secure\_mode\_i] signal should be tied low.

#### 6.2.10 scantestmode\_i

The [scantestmode\_i] input is an optional signal used to put the module into scan test mode. When [scantestmode\_i] is active the [startup\_osc\_clk\_i] is replaced by the [wb\_clk\_i] clock so all register are clocked by a common clock source.

| Parameter    | Туре    | Default | Description                          |

|--------------|---------|---------|--------------------------------------|

| ARST_LVL     | Bit     | 1'b0    | Asynchronous reset level             |

| MAX_CHANNEL  | Integer | 127     | Number of input an output interrupts |

| SINGLE_CYCLE | Bit     | 1'b0    | WISHBONE wait state                  |

### 6.3 Xgate Core Parameters

#### 6.3.1 ARST\_LVL

The asynchronous reset level can be set to either active high (1'b1) or active low (1'b0).

Allowed values: 1'b0, 1'b1

#### 6.3.2 MAX\_CHANNEL

The maximun index value for chan\_req\_i and xgif.

Allowed values: any integer value between 1 and 127

#### 6.3.3 SINGLE\_CYCLE

The default operation of the Xgate WISHBONE bus interface is to insert one wait state by delaying the assertion of the wb\_ack\_o by one wb\_clk\_i period. Setting the SINGLE\_CYCLE parameter generates the wb\_ack\_o combinationaly so a WISHBONE bus cycle can be completed in one wb\_clk\_i period.

Allowed values: 1'b0, 1'b1

# Appendix A Name

[This section may be added to outline different specifications.]

[This section contains an alphabetical list of helpful document entries with their corresponding page numbers.]