**Ethernet Switch on Configurable Logic**

# ESoCL

## **Ethernet Switch on Configurable Logic**

**Product Brief**

Copyright (C) LogiXA and OPENCORES.ORG

This source file may be used and distributed without restriction provided that this copyright statement is not Removed from the file and that any derivative work contains the original copyright notice and the associated disclaimer. This source file belongs to free software; you can redistribute it and/or modify it under the terms of the GNU Lesser General Public License as published by the Free Software Foundation; either version 2.1 of the License, or (at your option) any later version. This source is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU Lesser General Public License for more details. You should have received a copy of the GNU Lesser General Public License along with this source; if not, download it from http://www.opencores.org/lgpl.shtml

### Ethernet Switch on Configurable Logic

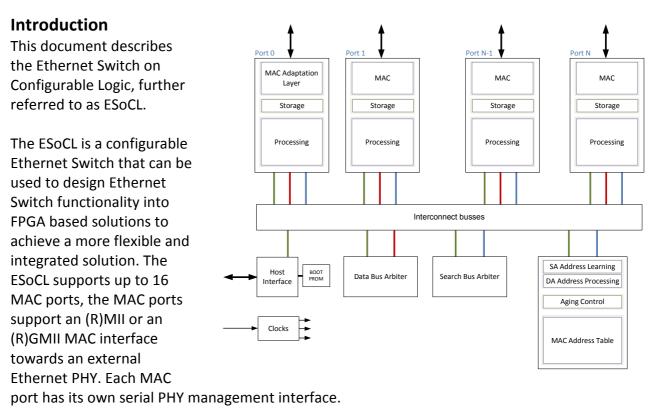

The ESoC is a VLAN capable Ethernet Switch. Untagged packets received by a port are tagged by the port default VLAN ID before they are processed. After switching an untagged packet to the destination port(s) the default tag is removed. Tagged packets can be re-tagged by the port default VLAN ID before or after they are processed further.

The ESoCL is a self-learning Ethernet Switch, the source address of incoming packets are stored or renewed in the internal MAC Address table, together with the associated VLAN ID. The MAC address table is monitored by an aging mechanism that removes expired MAC addresses.

The ESoCL can operate in unmanaged and managed mode. For unmanaged applications the ESoCL has an integrated boot ROM that can be used to configure the Ethernet Switch after reset is de- asserted. For managed applications the ESoCL has a generic, asynchronous, memory mapped interface that can be used by a processor platform to configure the Ethernet Switch. Managed applications with challenging start-up requirements related to the Ethernet Switch functionality can use the boot ROM as well.

#### **Main Features**

- Ethernet Switch with up to 16 ports

- Shared total switching capacity of 6-9 Gbps<sup>1</sup>

- Serial PHY management on each port

- Integrated Ethernet MACs with (R)MII or (R)GMII interface from Altera<sup>2</sup>

- MAC address table with up to 8192 entries

- Configurable address learning and aging mechanism

- VLAN tagged frames, according to IEEE 802.1Q, up to 4096 VLAN ID's

- Generic host interface<sup>3</sup>

- Unmanaged and managed operation

- Initialization by boot ROM

- Extensive set of counters

#### Sources

- Synthesizable VHDL for FPGA targets<sup>2</sup>

- Semi-automated functional test bench

#### **Target resources**

| Resources: 8 port ESoCL Target: EP3CLS100F484I7 (Altera Cyclone 3LS) |             |                |                                          |

|----------------------------------------------------------------------|-------------|----------------|------------------------------------------|

| Units                                                                | Logic cells | Memory bits    | Fmax                                     |

| Generic                                                              | 1217        | 8192 bits      |                                          |

| (Arbiters, Control)                                                  |             | 1 M9K Block    |                                          |

| RGMII Port                                                           | 5904        | 337328 bits    |                                          |

| (MAC, MAL, Storage, Processing)                                      |             | 51 M9K Blocks  | CLK_CTRL ≤ 50MHz                         |

| Search engine                                                        | 945         | 582400 bits    | CLK_DATA ≤ 140MHz<br>CLK SEARCH ≤ 100MHz |

|                                                                      |             | 72 M9K Blocks  | CLK_SEARCH S 100MHz                      |

| Total                                                                | 49394       | 337328 bits    |                                          |

|                                                                      |             | 481 M9K Blocks |                                          |

#### Documentation

- Product Brief

- Design Description

- Release Bulletin

<sup>&</sup>lt;sup>1</sup> Depends on target device and average packet size

<sup>&</sup>lt;sup>2</sup> Altera is supported, a Xilinx and/or a full Open Cores version upon request

<sup>&</sup>lt;sup>3</sup> Open Cores Wish Bone upon request