# Ethernet IP Core Specification

Author: Igor Mohor

IgorM@opencores.org

Rev. 1.19

November 27, 2002

November 27, 2002 Ethernet IP Core Specification

This page has been intentionally left blank.

## **Revision History**

| Rev. | Date     | Author               | Description                                                                                                                                                                                                  |  |  |

|------|----------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0.1  | 13/03/01 | Igor Mohor           | First Draft                                                                                                                                                                                                  |  |  |

| 0.2  | 17/03/01 | Igor Mohor           | MDC clock divider changed. Instead of the clock select bits CLKS[2:0] the clock divider bits CLKDIV[7:0] are used.                                                                                           |  |  |

| 1.0  | 21/03/01 | Igor Mohor           | MII module completed. Revision changed to 1.0 due to cvs demands.                                                                                                                                            |  |  |

| 1.1  | 16/04/01 | IM                   | DMA support and buffer descriptors added.                                                                                                                                                                    |  |  |

| 1.2  | 24/05/01 | IM                   | Registers revised.                                                                                                                                                                                           |  |  |

| 1.3  | 05/06/01 | IM                   | Status is written to the status registers. DMA channels 2 and 3 are not used any more. Figures that are implementation specific removed from the document.                                                   |  |  |

| 1.4  | 03/07/01 | IM                   | COLLCONF register changed bit width. BCKPRESS<br>and BCKPNBEN bit removed from MODER.<br>LOOPBCK added.                                                                                                      |  |  |

| 1.5  | 21/07/01 | IM                   | Signal RD0_O (Restart Descriptor for channel 0) added. Per packet CRC, BD changed.                                                                                                                           |  |  |

| 1.6  | 03/12/01 | IM                   | BD section rewritten.                                                                                                                                                                                        |  |  |

| 1.7  | 05/12/01 | IM                   | TX_BD_NUM register used instead of RX_BD_BASE_ADDR register.                                                                                                                                                 |  |  |

| 1.8  | 07/01/02 | IM                   | Minor typos fixed                                                                                                                                                                                            |  |  |

| 1.9  | 30/01/02 | IM                   | RST bit in MODER register is 1 after reset, initial collision window changed.                                                                                                                                |  |  |

| 1.10 | 18/02/02 | IM                   | Address recognition system added. Buffer Descriptors changed. DMA section changed. Ports changed.                                                                                                            |  |  |

| 1.11 | 02/03/02 | IM                   | Typos fixed, INT_SOURCE and INT_MASK registers changed.                                                                                                                                                      |  |  |

| 1.12 | 15/03/02 | IM                   | TX_BD_NUM, MAC_ADDR0 and MAC_ADDR1 register description changed.                                                                                                                                             |  |  |

| 1.13 | 15/04/02 | Jeanne<br>Wiegelmann | Document revised.                                                                                                                                                                                            |  |  |

| 1.14 | 14/05/02 | IM                   | Minor typos fixed.                                                                                                                                                                                           |  |  |

| 1.15 | 14/08/02 | IM                   | LINKFAIL and NVALID bit description changed in the<br>MIISTATUS register. TX_BD_NUM changed. External<br>DMA support removed from the document.                                                              |  |  |

| 1.16 | 04/09/02 | IM                   | RX_BD_NUM changed to TX_BD_NUM in the register<br>table. MIIRX_DATA bits changed to read only.<br>MIIMRST bit in MIIMODER register moved from bit[10]<br>to bit[9]. Description of the RXEN and TXEN bits in |  |  |

| Rev. | Date     | Author | Description                                                                                                                                                                                                                                                                              |  |  |

|------|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|      |          |        | MODER register is modified. Description of the CTRLMODER and INT_SOURCE register changed.                                                                                                                                                                                                |  |  |

| 1.17 | 14/11/02 | IM     | Few minor changes in the Tx BD, Rx BD and Host<br>Interface sections. Bit description in the INT_SOURCE<br>register improved. Frame reception section fixed.<br>Minimum tx and rx length defined in the Frame<br>Transmission and Frame Reception sections. RST bit<br>in MODER removed. |  |  |

| 1.18 | 22/11/02 | IM     | MIIMRST (Reset of the MIIM module) not used any<br>more in the MIIMODER register. Control Frame bit (CF)<br>added to the RX buffer descriptor. Control frame<br>detection section updated.                                                                                               |  |  |

| 1.19 | 27/11/02 | IM     | Control frame detection section improved.                                                                                                                                                                                                                                                |  |  |

## **List of Contents**

| 1                                                                                                    | 1    |

|------------------------------------------------------------------------------------------------------|------|

| INTRODUCTION                                                                                         | 1    |

| 2                                                                                                    | 2    |

| IO PORTS                                                                                             | 2    |

| 2.1 ETHERNET CORE IO PORTS                                                                           |      |

| 2.1.1 Host Interface Ports                                                                           |      |

| 2.1.2 PHY Interface ports                                                                            |      |

| 3                                                                                                    | 6    |

| REGISTERS                                                                                            | 6    |

| 3.1 MODER (MODE REGISTER)                                                                            | 8    |

| 3.2 INT SOURCE (INTERRUPT SOURCE REGISTER)                                                           | 10   |

| 3.3 INT_MASK (INTERRUPT MASK REGISTER)                                                               | 11   |

| 3.4 IPGT (BACK TO BACK INTER PACKET GAP REGISTER)                                                    | 12   |

| 3.5 IPGR1 (NON BACK TO BACK INTER PACKET GAP REGISTER 1)                                             |      |

| 3.6 IPGR2 (NON BACK TO BACK INTER PACKET GAP REGISTER 2)                                             |      |

| 3.7 PACKETLEN (PACKET LENGTH REGISTER)                                                               | 13   |

| 3.8 COLLCONF (COLLISION AND RETRY CONFIGURATION REGISTER)<br>3.9 TX_BD_NUM (TRANSMIT BD NUMBER REG.) |      |

| 3.10 CTRLMODER (CONTROL MODULE MODE REGISTER)                                                        | . 14 |

| 3.11 MIIMODER (MII MODE REGISTER)                                                                    | 16   |

| 3.12 MIICOMMAND (MII COMMAND REGISTER)                                                               |      |

| 3.13 MIIADDRESS (MII ADDRESS REGISTER)                                                               |      |

| 3.14 MIITX_DATA (MII TRANSMIT DATA)                                                                  |      |

| 3.15 MIIRX_DATA (MII RECEIVE DATA)                                                                   |      |

| 3.16 MIISTATUS (MII STATUS REGISTER)                                                                 |      |

| 3.17 MAC_ADDR0 (MAC ADDRESS REGISTER 0)                                                              | 18   |

| 3.18 MAC_ADDR1 (MAC ADDRESS REGISTER 1)                                                              |      |

| 3.19 HASH0 (HASH REGISTER 0)                                                                         |      |

| 3.20 HASH1 (HASH REGISTER 1)<br>3.21 TXCTRL (TX CONTROL REGISTER)                                    |      |

|                                                                                                      |      |

| 4                                                                                                    | 21   |

| OPERATION                                                                                            | 21   |

| 4.1 RESETTING ETHERNET CORE                                                                          |      |

| 4.2 HOST INTERFACE OPERATION                                                                         |      |

| 4.2.1 Configuration Registers                                                                        |      |

| 4.2.2 Buffer Descriptors (BD)                                                                        |      |

| 4.2.3 Frame Transmission                                                                             |      |

| 4.3 TX ETHERNET MAC                                                                                  |      |

|                                                                                                      | 30   |

| 4.4 RX ETHERNET MAC                   |    |

|---------------------------------------|----|

| 4.5 MAC CONTROL MODULE                |    |

| 4.5.1 Control Frame Detection         |    |

| 4.5.2 Control Frame Generation        |    |

| 4.5.3 TX/RX MAC Interface             |    |

| 4.5.4 PAUSE Timer                     |    |

| 4.5.5 Slot Timer                      |    |

| 4.6 MII MANAGEMENT MODULE             |    |

| 4.6.1 Operation Controller            |    |

| 4.6.2 Shift Registers Operation       |    |

| 4.6.3 Output Control Module Operation |    |

| 4.6.4 Clock Generator Operation       |    |

| 5                                     | 38 |

|                                       |    |

| ARCHITECTURE                          |    |

| 5.1 HOST INTERFACE                    |    |

| 5.2 TX ETHERNET MAC                   |    |

| 5.3 RX ETHERNET MAC                   |    |

| 5.4 MAC CONTROL MODULE                |    |

| 5.4.1 Control Frame Detector          |    |

| 5.4.2 Control Frame Generator         |    |

| 5.4.3 TX/RX Ethernet MAC Interface    |    |

| 5.4.4 PAUSE Timer                     |    |

| 5.4.5 Slot Timer                      |    |

| 5.5 MII MANAGEMENT MODULE             |    |

| 5.5.1 Operation Control Module        |    |

| 5.5.2 Output Control Module           |    |

| 5.5.3 Shift Register                  |    |

| 5.5.4 Clock Generator                 |    |

|                                       |    |

## **List of Tables**

| Table 1: Host Interface Ports          |

|----------------------------------------|

| Table 2: PHY Interface Ports   5       |

| Table 3: Register List    7            |

| Table 4: MODER Register                |

| Table 5: INT_SOURCE Register           |

| Table 6: INT_MASK Register11           |

| Table 7: IPGT Register                 |

| Table 8: IPGR1 Register                |

| Table 9: IPGR2 Register                |

| Table 10: PACKETLEN Register           |

| Table 11: COLLCONF Register            |

| Table 12: TX_BD_NUM Register    14     |

| Table 13: CTRLMODER Register           |

| Table 14: PASSALL and RXFLOW operation |

| Table 15: MIIMODER Register16          |

| Table 16: MIICOMMAND Register16        |

| Table 17: MIIADDRESS Register          |

| Table 18: MIITX_DATA Register17        |

| Table 19: MIIRX_DATA Register    17    |

| Table 20: MIISTATUS Register    18     |

| Table 21: MAC_ADDR0 Register    18     |

| Table 22: MAC_ADDR1 Register    19     |

| Table 23: HASH0 Register               |

| Table 24: HASH1 Register               |

| Table 25: HASH1 Register               |

| Table 26: Tx Buffer Descriptor         |

| Table 27: Tx Buffer Pointer   25       |

| Table 28: Rx Buffer Descriptor |  |

|--------------------------------|--|

| Table 29: Rx Buffer pointer    |  |

## **List of Figures**

| Figure 1: Tx Buffer Descriptor                 | 24 |

|------------------------------------------------|----|

| Figure 2: Rx Buffer Descriptor                 | 26 |

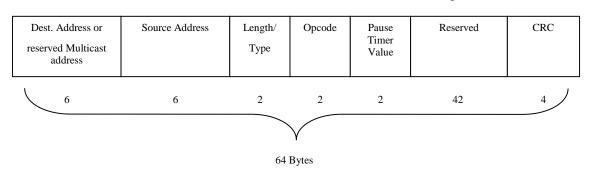

| Figure 3: Structure of the PAUSE control frame |    |

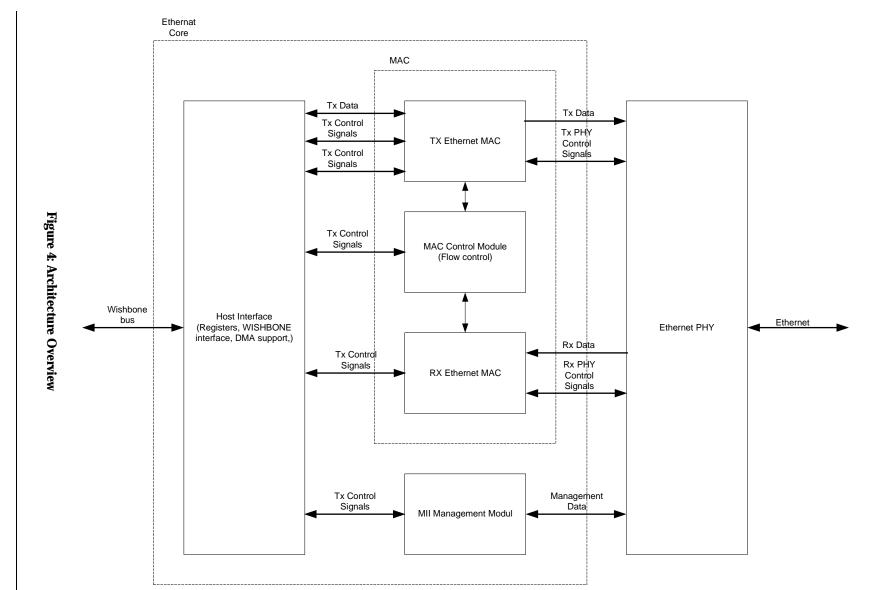

| Figure 4: Architecture Overview                |    |

# 1

## Introduction

The Ethernet IP Core consists of five modules:

- ✓ The MAC (Media Access Control) module, formed by transmit, receive, and control module

- ✓ The MII (Media Independent Interface) Management module

- ✓ The Host Interface

The Ethernet IP Core is capable of operating at 10 or 100 Mbps for Ethernet and Fast Ethernet applications. An external PHY is needed for the complete Ethernet solution.

# 2

## **IO Ports**

## 2.1 Ethernet Core IO ports

The Ethernet IP Core uses three types of signals to connect to media:

- ✓ WISHBONE signals to connect to the Host Interface.

- ✓ MII Management signals to connect to the PHY

- ✓ Reset signals (for resetting different parts of the Ethernet IP Core

#### 2.1.1 Host Interface Ports

The table below contains the common ports connecting the Ethernet IP Core to the Host Interface. The Host Interface is WISHBONE Rev. B compliant.

All signals listed below are active HIGH, unless otherwise noted. Signal direction is with respect to the Ethernet IP Core.

| Port                     | Width | Directi<br>on                         | Description                                                                                                                      |  |

|--------------------------|-------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| CLK_I                    | 1     | I                                     | Clock Input                                                                                                                      |  |

| RST_I                    | 1     | 1                                     | Reset Input                                                                                                                      |  |

| ADDR_I                   | 32    | I                                     | Address Input                                                                                                                    |  |

| DATA_I                   | 32    | I                                     | Data Input                                                                                                                       |  |

| DATA_O                   | 32    | 0                                     | Data Output                                                                                                                      |  |

| SEL_I                    | 4     | I                                     | Select Input Array                                                                                                               |  |

|                          |       |                                       | Indicates which bytes are valid on the data bus. Whenever this signal is not 1111b during a valid access, the ERR_O is asserted. |  |

| WE_I                     | 1     | 1                                     | Write Input                                                                                                                      |  |

|                          |       |                                       | Indicates a Write Cycle when asserted high or a Read Cycle when asserted low.                                                    |  |

| STB_I                    | 1     | I                                     | Strobe Input                                                                                                                     |  |

|                          |       |                                       | Indicates the beginning of a valid transfer cycle.                                                                               |  |

| CYC_I                    | 1     | I                                     | Cycle Input                                                                                                                      |  |

|                          |       |                                       | Indicates that a valid bus cycle is in progress.                                                                                 |  |

| ACK_O                    | 1     | 0                                     | Acknowledgment Output                                                                                                            |  |

|                          |       |                                       | Indicates a normal Cycle termination.                                                                                            |  |

| ERR_O                    | 1     | 0                                     | Error Acknowledgment Output                                                                                                      |  |

|                          |       |                                       | Indicates an abnormal cycle termination.                                                                                         |  |

| INTA_O                   | 1     | 0                                     | Interrupt Output A.                                                                                                              |  |

| M_ADDR_O                 | 32    | 0                                     | Address Output                                                                                                                   |  |

| M_DATA_I                 | 32    | I                                     | Data Input                                                                                                                       |  |

| M_DATA_O                 | 32    | 0                                     | Data Output                                                                                                                      |  |

| M_SEL_O                  | 4     | I                                     | Select Output Array                                                                                                              |  |

|                          |       |                                       | Indicates which bytes are valid on the data bus. Whenever this signal is not 1111b during a valid access, the ERR_I is asserted. |  |

| M_WE_O                   | 1     | 0                                     | Write Output                                                                                                                     |  |

|                          |       |                                       | Indicates a Write Cycle when asserted high or a Read Cycle when asserted low.                                                    |  |

| M_STB_O                  | 1     | 0                                     | Strobe Output                                                                                                                    |  |

|                          |       |                                       | Indicates the beginning of a valid transfer cycle.                                                                               |  |

| M_CYC_O                  | 1     | 0                                     | Cycle Output                                                                                                                     |  |

|                          |       |                                       | Indicates that a valid bus cycle is in progress.                                                                                 |  |

| M_ACK_I                  | 1     | I Acknowledgment Input                |                                                                                                                                  |  |

| Indicates a normal cycle |       | Indicates a normal cycle termination. |                                                                                                                                  |  |

| Port    | Width | Directi<br>on | Description                                                            |  |

|---------|-------|---------------|------------------------------------------------------------------------|--|

| M_ERR_I | 1     | I             | Error Acknowledgment Input<br>Indicates an abnormal cycle termination. |  |

#### **Table 1: Host Interface Ports**

#### 2.1.2 PHY Interface ports

The table below contains the ports connecting the Ethernet IP Core to the PHY Interface. All signals listed below are active HIGH, unless otherwise noted. Signal direction is with respect to the Ethernet IP Core.

| Port      | Width | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-----------|-------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MTxClk    | 1     |           | Transmit Nibble or Symbol Clock. The PHY provides the MTxClk signal. It operates at a frequency of 25 MHz (100 Mbps) or 2.5 MHz (10 Mbps). The clock is used as a timing reference for the transfer of MTxD[3:0], MtxEn, and MTxErr.                                                                                                                                                            |  |  |

| MTxD[3:0] | 4     | 0         | Transmit Data Nibble. Signals are the transmit data<br>nibbles. They are synchronized to the rising edge of<br>MTxClk. When MTxEn is asserted, PHY accepts the<br>MTxD.                                                                                                                                                                                                                         |  |  |

| MTxEn     | 1     | 0         | Transmit Enable. When asserted, this signal indicates to<br>the PHY that the data MTxD[3:0] is valid and the<br>transmission can start. The transmission starts with the<br>first nibble of the preamble. The signal remains asserted<br>until all nibbles to be transmitted are presented to the<br>PHY. It is deasserted prior to the first MTxClk, following<br>the final nibble of a frame. |  |  |

| MTxErr    | 1     | 0         | Transmit Coding Error. When asserted for one MTxClk clock period while MTxEn is also asserted, this signal causes the PHY to transmit one or more symbols that are not part of the valid data or delimiter set somewhere in the frame being transmitted to indicate that there has been a transmit coding error.                                                                                |  |  |

| MRxClk    | 1     | 1         | Receive Nibble or Symbol Clock. The PHY provides the MRxClk signal. It operates at a frequency of 25 MHz (100 Mbps) or 2.5 MHz (10 Mbps). The clock is used as a timing reference for the reception of MRxD[3:0], MRxDV, and MRxErr.                                                                                                                                                            |  |  |

| MRxDV     | 1     | I         | Receive Data Valid. The PHY asserts this signal to indicate to the Rx MAC that it is presenting the valid                                                                                                                                                                                                                                                                                       |  |  |

| Port          | Width | Direction | Description                                                                                                                                                                                                                                                                                                                         |  |  |

|---------------|-------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|               |       |           | nibbles on the MRxD[3:0] signals. The signal is asserted<br>synchronously to the MRxClk. MRxDV is asserted from<br>the first recovered nibble of the frame to the final<br>recovered nibble. It is then deasserted prior to the first<br>MRxClk that follows the final nibble.                                                      |  |  |

| MRxD<br>[3:0] | 4     | Ι         | Receive Data Nibble. These signals are the receive data<br>nibble. They are synchronized to the rising edge of<br>MRxClk. When MRxDV is asserted, the PHY sends a data<br>nibble to the Rx MAC. For a correctly interpreted frame,<br>seven bytes of a preamble and a completely formed SFD<br>must be passed across the interface. |  |  |

| MRxErr        | 1     | 1         | Receive Error. The PHY asserts this signal to indicate to<br>the Rx MAC that a media error was detected during the<br>transmission of the current frame. MRxErr is synchronous<br>to the MRxClk and is asserted for one or more MRxClk<br>clock periods and then deasserted.                                                        |  |  |

| MColl         | 1     | I         | Collision Detected. The PHY asynchronously asserts the collision signal MColl after the collision has been detected on the media. When deasserted, no collision is detected on the media.                                                                                                                                           |  |  |

| MCrS          | 1     | 1         | Carrier Sense. The PHY asynchronously asserts the carrier sense MCrS signal after the medium is detected in a non-idle state. When deasserted, this signal indicates that the media is in an idle state (and the transmission can start).                                                                                           |  |  |

| MDC           | 1     | 0         | Management Data Clock. This is a clock for the MDIO serial data channel.                                                                                                                                                                                                                                                            |  |  |

| MDIO          | 1     | I/O       | Management Data Input/Output. Bi-directional serial data channel for PHY/STA communication.                                                                                                                                                                                                                                         |  |  |

Table 2: PHY Interface Ports

# 3

## Registers

This section describes all base, control, and status registers inside the Ethernet IP Core. The Address field indicates a relative address in hexadecimal. Width specifies the number of bits in the register, and Access specifies the valid access types to that register. RW stands for read and write access, R for read-only access.

| Name       | Address | Width | Access | Description                                                      |

|------------|---------|-------|--------|------------------------------------------------------------------|

| MODER      | 0x00    | 32    | RW     | Mode Register                                                    |

| INT_SOURCE | 0x04    | 32    | RW     | Interrupt Source Register                                        |

| INT_MASK   | 0x08    | 32    | RW     | Interrupt Mask Register                                          |

| IPGT       | 0x0C    | 32    | RW     | Back to Back Inter Packet Gap<br>Register                        |

| IPGR1      | 0x10    | 32    | RW     | Non Back to Back Inter Packet Gap<br>Register 1                  |

| IPGR2      | 0x14    | 32    | RW     | Non Back to Back Inter Packet Gap<br>Register 2                  |

| PACKETLEN  | 0x18    | 32    | RW     | Packet Length (minimum and maximum) Register                     |

| COLLCONF   | 0x1C    | 32    | RW     | Collision and Retry Configuration                                |

| TX_BD_NUM  | 0x20    | 32    | RW     | Transmit Buffer Descriptor Number                                |

| CTRLMODER  | 0x24    | 32    | RW     | Control Module Mode Register                                     |

| MIIMODER   | 0x28    | 32    | RW     | MII Mode Register                                                |

| MIICOMMAND | 0x2C    | 32    | RW     | MII Commend Register                                             |

|            |         |       |        | MII Address Register                                             |

| MIIADDRESS | 0x30    | 32    | RW     | Contains the PHY address and the register within the PHY address |

| Name          | Address | Width | Access | Description                                                                |

|---------------|---------|-------|--------|----------------------------------------------------------------------------|

| MIITX DATA    | 0x34    | 32    | RW     | MII Transmit Data                                                          |

|               | 0,34    | 32    |        | The data to be transmitted to the PHY                                      |

| MIIRX_DATA    | 0x38    | 32    | RW     | MII Receive Data                                                           |

|               | 0X30    | 32    |        | The data received from the PHY                                             |

| MIISTATUS     | 0x3C    | 32    | RW     | MII Status Register                                                        |

| MAC_ADDR0     |         |       |        | MAC Individual Address0                                                    |

|               | 0x40    | 32    | RW     | The LSB four bytes of the individual address are written to this register. |

| MAC_ADDR1     |         |       |        | MAC Individual Address1                                                    |

|               | 0x44    | 32    | RW     | The MSB two bytes of the individual address are written to this register.  |

| ETH_HASH0_ADR | 0x48    | 32    | RW     | HASH0 Register                                                             |

| ETH_HASH1_ADR | 0x4C    | 32    | RW     | HASH1 Register                                                             |

| ETH_TXCTRL    | 0x50    | 32    | RW     | Transmit Control Register                                                  |

Table 3: Register List

http://www.opencores.org

## 3.1 MODER (Mode Register)

| Bit #     | Access | Description                                                                      |

|-----------|--------|----------------------------------------------------------------------------------|

| 31-<br>17 |        | Reserved                                                                         |

| 16        | RW     | RECSMALL – Receive Small Packets                                                 |

|           |        | 0 = Packets smaller than MINFL are ignored.                                      |

|           |        | 1 = Packets smaller than MINFL are accepted.                                     |

| 15        | RW     | PAD – Padding enabled                                                            |

|           |        | 0 = Do not add pads to short frames.                                             |

|           |        | 1 = Add pads to short frames (until the minimum frame length is equal to MINFL). |

| 14        | RW     | HUGEN – Huge Packets Enable                                                      |

|           |        | 0 = The maximum frame length is MAXFL. All additional bytes are discarded.       |

|           |        | 1 = Frames up 64 KB are transmitted.                                             |

| 13        | RW     | CRCEN – CRC Enable                                                               |

|           |        | 0 = Tx MAC does not append the CRC (passed frames already contain the CRC.       |

|           |        | 1 = Tx MAC appends the CRC to every frame.                                       |

| 12        | RW     | DLYCRCEN – Delayed CRC Enabled                                                   |

|           |        | 0 = Normal operation (CRC calculation starts immediately after the SFD).         |

|           |        | 1 = CRC calculation starts 4 bytes after the SFD.                                |

| 11        |        | Reserved                                                                         |

| 10        | RW     | FULLD – Full Duplex                                                              |

|           |        | 0 = Half duplex mode.                                                            |

|           |        | 1 = Full duplex mode.                                                            |

| 9         | RW     | EXDFREN – Excess Defer Enabled                                                   |

|           |        | 0 = When the excessive deferral limit is reached, a packet is aborted.           |

|           |        | 1 = MAC waits for the carrier indefinitely.                                      |

| 8         | RW     | NOBCKOF – No Backoff                                                             |

|           |        | 0 = Normal operation (a binary exponential backoff algorithm is used).           |

|           |        | 1 = Tx MAC starts retransmitting immediately after the collision.                |

| 7         | RW     | LOOPBCK – Loop Back                                                              |

|           |        | 0 = Normal operation.                                                            |

|           |        | 1 = TX is looped back to the RX.                                                 |

| 6         | RW     | IFG – Interframe Gap for Incoming frames                                         |

| Bit # | Access | Description                                                                                                                                                                                                                         |  |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|       |        | 0 = Normal operation (minimum IFG is required for a frame to be accepted).                                                                                                                                                          |  |

|       |        | 1 = All frames are accepted regardless to the IFG.                                                                                                                                                                                  |  |

| 5     | RW     | PRO – Promiscuous                                                                                                                                                                                                                   |  |

|       |        | 0 = Check the destination address of the incoming frames.                                                                                                                                                                           |  |

|       |        | 1 = Receive the frame regardless of its address.                                                                                                                                                                                    |  |

| 4     | RW     | IAM – Individual Address Mode                                                                                                                                                                                                       |  |

|       |        | 0 = Normal operation (physical address is checked when the frame is received.                                                                                                                                                       |  |

|       |        | 1 = The individual hash table is used to check all individual addresses received.                                                                                                                                                   |  |

| 3     | RW     | BRO – Broadcast Address                                                                                                                                                                                                             |  |

|       |        | 0 = Receive all frames containing the broadcast address.                                                                                                                                                                            |  |

|       |        | 1 = Reject all frames containing the broadcast address unless the PRO bit = 1.                                                                                                                                                      |  |

| 2     | RW     | NOPRE – No Preamble                                                                                                                                                                                                                 |  |

|       |        | 0 = Normal operation (7-byte preamble).                                                                                                                                                                                             |  |

|       |        | 1 = No preamble is sent.                                                                                                                                                                                                            |  |

| 1     | RW     | TXEN – Transmit Enable                                                                                                                                                                                                              |  |

|       |        | 0 = Transmit is disabled.                                                                                                                                                                                                           |  |

|       |        | 1 = Transmit is enabled.                                                                                                                                                                                                            |  |

|       |        | If the value, written to the TX_BD_NUM register, is equal to 0x0 (zero buffer descriptors are used), then the transmitter is automatically disabled regardless of the TXEN bit.                                                     |  |

| 0     | RW     | RXEN – Receive Enable                                                                                                                                                                                                               |  |

|       |        | 0 = Receive is disabled.                                                                                                                                                                                                            |  |

|       |        | 1 = Receive is enabled.                                                                                                                                                                                                             |  |

|       |        | If the value, written to the TX_BD_NUM register, is equal to 0x80 (all buffer descriptors are used for transmit buffer descriptors, so there is no receive BD), then receiver is automatically disabled regardless of the RXEN bit. |  |

#### Table 4: MODER Register

Reset Value:

MODER: 0000A000h

#### **NOTE:** Registers should not be changed after the TXEN or RXEN bits is set.

## 3.2 INT\_SOURCE (Interrupt Source Register)

| Bit # | Access | Description                                                                                                                                                                                                                                                                                                                           |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-7  |        | Reserved                                                                                                                                                                                                                                                                                                                              |

| 6     | RW     | RXC – Receive Control Frame                                                                                                                                                                                                                                                                                                           |

|       |        | This bit indicates that the control frame was received. It is cleared by writing 1 to it. Bit RXFLOW (CTRLMODER register) must be set to 1 in order to get the RXC bit set.                                                                                                                                                           |

| 5     | RW     | TXC – Transmit Control Frame                                                                                                                                                                                                                                                                                                          |

|       |        | This bit indicates that a control frame was transmitted. It is cleared by writing 1 to it. Bit TXFLOW (CTRLMODER register) must be set to 1 in order to get the TXC bit set.                                                                                                                                                          |

| 4     | RW     | BUSY – Busy                                                                                                                                                                                                                                                                                                                           |

|       |        | This bit indicates that a buffer was received and discarded due to a lack of buffers. It is cleared by writing 1 to it. This bit appears regardless to the IRQ bits in the Receive or Transmit Buffer Descriptors.                                                                                                                    |

| 3     | RW     | RXE - Receive Error                                                                                                                                                                                                                                                                                                                   |

|       |        | This bit indicates that an error occurred while receiving data. It is cleared by writing 1 to it. This bit appears only when IRQ bit is set in the Receive Buffer Descriptor.                                                                                                                                                         |

| 2     | RW     | RXB - Receive Frame                                                                                                                                                                                                                                                                                                                   |

|       |        | This bit indicates that a frame was received. It is cleared by writing 1 to it.<br>This bit appears only when IRQ bit is set in the Receive Buffer Descriptor.<br>If a control frame is received, then RXC bit is set instead of the RXB bit.<br>(See 3.10 CTRLMODER (Control Module Mode Register) description for<br>more details.) |

| 1     | RW     | TXE - Transmit Error                                                                                                                                                                                                                                                                                                                  |

|       |        | This bit indicates that a buffer was not transmitted due to a transmit error.<br>It is cleared by writing 1 to it. This bit appears only when IRQ bit is set in<br>the Receive Buffer Descriptor. This bit appears only when IRQ bit is set in<br>the Transmit Buffer Descriptor.                                                     |

| 0     | RW     | TXB – Transmit Buffer                                                                                                                                                                                                                                                                                                                 |

|       |        | This bit indicates that a buffer has been transmitted. It is cleared by writing 1 to it. This bit appears only when IRQ bit is set in the Transmit Buffer Descriptor.                                                                                                                                                                 |

#### Table 5: INT\_SOURCE Register

Reset Value:

#### INT\_SOURCE: 0000000h

## 3.3 INT\_MASK (Interrupt Mask Register)

| Bit # | Access | Description                         |

|-------|--------|-------------------------------------|

| 31-7  |        | Reserved                            |

| 6     | RW     | RXC_M – Receive Control Frame Mask  |

|       |        | 0 = Event masked                    |

|       |        | 1 = Event causes an interrupt       |

| 5     | RW     | TXC_M – Transmit Control Frame Mask |

|       |        | 0 = Event masked                    |

|       |        | 1 = Event causes an interrupt       |

| 4     | RW     | BUSY_M – Busy Mask                  |

|       |        | 0 = Event masked                    |

|       |        | 1 = Event causes an interrupt       |

| 3     | RW     | RXE_M – Receive Error Mask          |

|       |        | 0 = Event masked                    |

|       |        | 1 = Event causes an interrupt       |

| 2     | RW     | RXF_M – Receive Frame Mask          |

|       |        | 0 = Event masked                    |

|       |        | 1 = Event causes an interrupt       |

| 1     | RW     | TXE_M – Transmit Error Mask         |

|       |        | 0 = Event masked                    |

|       |        | 1 = Event causes an interrupt       |

| 0     | RW     | TXB_M – Transmit Buffer Mask        |

|       |        | 0 = Event masked                    |

|       |        | 1 = Event causes an interrupt       |

#### Table 6: INT\_MASK Register

Reset Value:

INT\_MASK: 0000000h

### 3.4 IPGT (Back to Back Inter Packet Gap Register)

| Bit # | Access | Description                                                                                                                                                                                              |

|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-7  |        | Reserved                                                                                                                                                                                                 |

| 6-0   | RW     | IPGT – Back to Back Inter Packet Gap                                                                                                                                                                     |

|       |        | Full Duplex: The recommended value is 0x15, which equals 0.96 $\mu$ s IPG (100 Mbps) or 9.6 $\mu$ s (10 Mbps). The desired period in nibble times minus 6 should be written to the register.             |

|       |        | Half Duplex: The recommended value and default is 0x12, which equals 0.96 $\mu$ s IPG (100 Mbps) or 9.6 $\mu$ s (10 Mbps). The desired period in nibble times minus 3 should be written to the register. |

#### Table 7: IPGT Register

Reset Value:

IPGT: 00000012h

## 3.5 IPGR1 (Non Back to Back Inter Packet Gap Register 1)

| Bit # | Access | Description                                                                                                                                                                                       |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-7  |        | Reserved                                                                                                                                                                                          |

| 6-0   | RW     | IPGR1 – Non Back to Back Inter Packet Gap 1                                                                                                                                                       |

|       |        | When a carrier sense appears within the IPGR1 window, Tx MAC defers and the IPGR counter is reset.                                                                                                |

|       |        | When a carrier sense appears later than the IPGR1 window, the IPGR counter continues counting. The recommended and default value for this register is 0xC. It must be within the range [0,IPGR2]. |

#### Table 8: IPGR1 Register

Reset Value:

IPGR1: 000000Ch

## 3.6 IPGR2 (Non Back to Back Inter Packet Gap Register 2)

| Bit # | Access | Description                                                                                                          |

|-------|--------|----------------------------------------------------------------------------------------------------------------------|

| 31-7  |        | Reserved                                                                                                             |

| 6-0   | RW     | IPGR2 – Non Back to Back Inter Packet Gap 2                                                                          |

|       |        | The recommended and default value is 0x12, which equals to 0.96 $\mu s$ IPG (100 Mbit/s) or 9.6 $\mu s$ (10 Mbit/s). |

Table 9: IPGR2 Register

Reset Value:

IPGR2: 00000012h

### 3.7 PACKETLEN (Packet Length Register)

| Bit # | Access | Description                                                                                                                                                                                                                                                                                                                                    |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-   | RW     | MINFL – Minimum Frame Length                                                                                                                                                                                                                                                                                                                   |

| 16    |        | The minimum Ethernet packet is 64 bytes long. If a reception of smaller frames is needed, assert the RECSMALL bit (in the mode register MODER) or change the value of this register.                                                                                                                                                           |

|       |        | To transmit small packets, assert the PAD bit or the MINFL value (see the PAD bit description in the MODER register).                                                                                                                                                                                                                          |

| 15-0  | RW     | MAXFL – Maximum Frame Length                                                                                                                                                                                                                                                                                                                   |

|       |        | The maximum Ethernet packet is 1518 bytes long. To support this and to leave some additional space for the tags, a default maximum packet length equals 1536 bytes (0x0600). If there is a need to support bigger packets, you can assert the HUGEN bit or increase the value of the MAXFL field (see the HUGEN bit description in the MODER). |

#### Table 10: PACKETLEN Register

Reset Value:

PACKETLEN: 00400600h

## 3.8 COLLCONF (Collision and Retry Configuration Register)

| Bit #     | Access | Description                                                                                                                                                                                                                                                                                                                                                     |

|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-<br>20 |        | Reserved                                                                                                                                                                                                                                                                                                                                                        |

| 19-<br>16 | RW     | MAXRET – Maximum Retry<br>This field specifies the maximum number of consequential retransmission<br>attempts after the collision is detected. When the maximum number has<br>been reached, the Tx MAC reports an error and stops transmitting the<br>current packet. According to the Ethernet standard, the MAXRET default<br>value is set to 0xf (15).       |

| 15-6      |        | Reserved                                                                                                                                                                                                                                                                                                                                                        |

| 5-0       | RW     | COLLVALID – Collision Valid<br>This field specifies a collision time window. A collision that occurs later than<br>the time window is reported as a »Late Collisions« and transmission of the<br>current packet is aborted. The default value equals 0x3f (by default, a late<br>collision is every collision that occurs 64 bytes (63 + 1) from the preamble). |

#### Table 11: COLLCONF Register

Reset Value:

COLLCONF: 000F003fh

## 3.9 TX\_BD\_NUM (Transmit BD Number Reg.)

| Bit # | Access | Description                                                                                                                                                                                  |

|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8  |        | Reserved                                                                                                                                                                                     |

| 7:0   | RW     | Transmit Buffer Descriptor (Tx BD) Number                                                                                                                                                    |

|       |        | Number of the Tx BD. Number of the Rx BD equals to the $(0x80 - Tx BD number)$ . Maximum number of the Tx BD is 0x80. Values greater then 0x80 cannot be written to this register (ignored). |

#### Table 12: TX\_BD\_NUM Register

Reset Value:

#### TX\_BD\_NUM: 0000040h

http://www.opencores.org

## 3.10 CTRLMODER (Control Module Mode Register)

| Bit # | Access | Description                                                                                                                                    |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-3  |        | Reserved                                                                                                                                       |

| 2     | RW     | TXFLOW – Transmit Flow Control                                                                                                                 |

|       |        | 0 = PAUSE control frames are blocked.                                                                                                          |

|       |        | 1 = PAUSE control frames are allowed to be sent. This bit enables the TXC bit in the INT_SOURCE register.                                      |

| 1     | RW     | RXFLOW – Receive Flow Control                                                                                                                  |

|       |        | 0 = Received PAUSE control frames are ignored.                                                                                                 |

|       |        | 1 = The transmit function (Tx MAC) is blocked when a PAUSE control frame is received. This bit enables the RXC bit in the INT_SOURCE register. |

| 0     | RW     | PASSALL – Pass All Receive Frames                                                                                                              |

|       |        | 0 = Control frames are not passed to the host. RXFLOW must be set to 1 in order to use PAUSE control frames.                                   |

|       |        | 1 = All received frames are passed to the host.                                                                                                |

#### Table 13: CTRLMODER Register

Reset Value:

CTRLMODER: 0000000h

| PASSALL | RXFLOW | Description                                                                                                                                                                                                                          |

|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | 0      | When a PAUSE control frame is received, nothing happens. The control frame is not stored to the memory.                                                                                                                              |

| 0       | 1      | When a PAUSE control frame is received, RXC interrupt is set and pause timer is updated. The control frame is not stored to the memory.                                                                                              |

| 1       | 0      | When a PAUSE control frame is received, it is stored to the memory as a normal data frame. RXB interrupt is set (if the related buffer descriptor has an IRQ bit set to 1). RXC interrupt is not set and pause timer is not updated. |

| 1       | 1      | When a PAUSE control frame is received, RXC interrupt is set and pause timer is updated. Besides that the control frame is also stored to the memory as a normal data frame.                                                         |

#### Table 14: PASSALL and RXFLOW operation

http://www.opencores.org

### 3.11 MIIMODER (MII Mode Register)

| Bit # | Access | Description                                                                                                                                 |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 31-9  |        | Reserved                                                                                                                                    |

| 8     | RW     | MIINOPRE – No Preamble                                                                                                                      |

|       |        | 0 = 32-bit preamble sent                                                                                                                    |

|       |        | 1 = No preamble send                                                                                                                        |

| 7-0   | RW     | CLKDIV – Clock Divider                                                                                                                      |

|       |        | The field is a host clock divider factor. The host clock can be divided by an even number, greater then 1. The default value is 0x64 (100). |

#### Table 15: MIIMODER Register

Reset Value:

MIIMODER: 0000064h

### 3.12 MIICOMMAND (MII Command Register)

| Bit # | Access | Description                    |

|-------|--------|--------------------------------|

| 31-3  |        | Reserved                       |

| 2     | RW     | WCTRLDATA – Write Control Data |

| 1     | RW     | RSTAT – Read Status            |

| 0     | RW     | SCANSTAT – Scan Status         |

#### Table 16: MIICOMMAND Register

Reset Value:

MIICOMMAND: 0000000h

**NOTE:** While one operation is in progress, BUSY signal (3.16 MIISTATUS (MII Status Register) register) is set. Next operation can be started after the previous one is finished (and BUSY signal cleared to zero).

### 3.13 MIIADDRESS (MII Address Register)

| Bit #     | Access | Description                                                        |

|-----------|--------|--------------------------------------------------------------------|

| 31-<br>13 |        | Reserved                                                           |

| 12-8      | RW     | RGAD – Register Address (within the PHY selected by the FIAD[4:0]) |

| 7-5       |        | Reserved                                                           |

| 4-0       | RW     | FIAD – PHY Address                                                 |

**Table 17: MIIADDRESS Register**

Reset Value:

MIIADDRESS: 0000000h

## 3.14 MIITX\_DATA (MII Transmit Data)

| Bit #     | Access | Description                                             |

|-----------|--------|---------------------------------------------------------|

| 31-<br>16 |        | Reserved                                                |

| 15-0      | RW     | CTRLDATA – Control Data (data to be written to the PHY) |

Table 18: MIITX\_DATA Register

Reset Value:

MIITX\_DATA: 0000000h

### 3.15 MIIRX\_DATA (MII Receive Data)

| Bit #     | Access | Description                                   |

|-----------|--------|-----------------------------------------------|

| 31-<br>16 |        | Reserved                                      |

| 15-0      | R      | PRSD – Received Data (data read from the PHY) |

#### Table 19: MIIRX\_DATA Register

Reset Value:

MIIRX\_DATA: 0000000h

## 3.16 MIISTATUS (MII Status Register)

| Bit # | Access | Description                                                                                         |

|-------|--------|-----------------------------------------------------------------------------------------------------|

| 31-3  |        | Reserved                                                                                            |

| 2     | R      | NVALID – Invalid                                                                                    |

|       |        | 0 = The data in the MSTATUS register is valid.                                                      |

|       |        | 1 = The data in the MSTATUS register is invalid.                                                    |

|       |        | This bit is only valid when the scan status operation is active.                                    |

| 1     | R      | BUSY                                                                                                |

|       |        | 0 = The MII is ready.                                                                               |

|       |        | 1 = The MII is busy (operation in progress).                                                        |

| 0     | R      | LINKFAIL:                                                                                           |

|       |        | 0 = The link is OK.                                                                                 |

|       |        | 1 = The link failed.                                                                                |

|       |        | The Link fail condition occurred (now the link might be OK). Another status read gets a new status. |

Table 20: MIISTATUS Register

Reset Value:

MIISTATUS: 0000000h

## 3.17 MAC\_ADDR0 (MAC Address Register 0)

| Bit #     | Access | Description                                             |

|-----------|--------|---------------------------------------------------------|

| 31-<br>24 | RW     | Byte 2 of the Ethernet MAC address (individual address) |

| 23-<br>16 | RW     | Byte 3 of the Ethernet MAC address (individual address) |

| 15-8      | RW     | Byte 4 of the Ethernet MAC address (individual address) |

| 7-0       | RW     | Byte 5 of the Ethernet MAC address (individual address) |

#### Table 21: MAC\_ADDR0 Register

Reset Value:

MAC\_ADDR0: 0000000h

Note: When an address is transmitted, byte 0 is sent first and byte 5 last.

http://www.opencores.org

### 3.18 MAC\_ADDR1 (MAC Address Register 1)

| Bit #     | Access | Description                                             |

|-----------|--------|---------------------------------------------------------|

| 31-<br>16 |        | Reserved                                                |

| 15-8      | RW     | Byte 0 of the Ethernet MAC address (individual address) |

| 7-0       | RW     | Byte 1 of the Ethernet MAC address (individual address) |

Table 22: MAC\_ADDR1 Register

Reset Value:

MAC\_ADDR1: 0000000h

Note: When an address is transmitted, byte 0 is sent first and byte 5 last.

### 3.19 HASH0 (HASH Register 0)

| Bit # | Access | Description |

|-------|--------|-------------|

| 31-0  | RW     | Hash0 value |

Table 23: HASH0 Register

Reset Value:

HASH0: 0000000h

### 3.20 HASH1 (HASH Register 1)

| Bit # | Access | Description |

|-------|--------|-------------|

| 31-0  | RW     | Hash1 value |

Table 24: HASH1 Register

Reset Value:

HASH1: 0000000h

http://www.opencores.org

## 3.21 TXCTRL (Tx Control Register)

| Bit # | Access | Description                                                                                         |

|-------|--------|-----------------------------------------------------------------------------------------------------|

| 31-17 |        | Reserved                                                                                            |

| 16    | RW     | TXPAUSERQ – Tx Pause Request                                                                        |

|       |        | Writing 1 to this bit starts sending control frame procedure. Bit is automatically cleared to zero. |

| 15:0  | RW     | TXPAUSETV – Tx Pause Timer Value                                                                    |

|       |        | The value that is send in the pause control frame.                                                  |

#### Table 25: HASH1 Register

Reset Value:

TXCTRL: 0000000h

# 4

## Operation

This section describes the Ethernet IP Core operation.

The core consists of five modules:

- ✓ The host interface connects the Ethernet Core to the rest of the system via the WISHBONE (using DMA transfers). Registers are also part of the host interface.

- ✓ The TX Ethernet MAC performs transmit functions.

- ✓ The RX Ethernet MAC performs receive functions.

- ✓ The MAC Control Module performs full duplex flow control functions.

- ✓ The MII Management Module performs PHY control and gathers the status information from it.

All modules combined deliver full-function 10/100 Mbps Media Access Control. The Ethernet IP Core can operate in half- or full-duplex mode and is based on the CSMA/CD (Carrier Sense Multiple Access / Collision Detection) protocol..

When a station wants to transmit in half-duplex mode, it must observe the activity on the media (Carrier Sense). As soon as the media is idle (no transmission), any station can start transmitting (Multiple Access). If two or more stations are transmitting at the same time, a collision on the media is detected. All stations stop transmitting and back off for some random time. After the back-off time, the station checks the activity on the media again. If the media is idle, it starts transmitting. All other stations wait for the current transmission to end.

In full-duplex mode, the Carrier Sense and the Collision Detect signals are ignored. The MAC Control module takes care of sending and receiving the PAUSE control frame to achieve Flow control (see the TXFLOW and RXFLOW bit description in the CTRLMODER register for more information).

The MII Management module provides a media independent interface (MII) to the external PHY. This way, the configuration and status registers of the PHY can be read from/written to.

### **4.1 Resetting Ethernet Core**

The RST\_I signal is used for resetting all sub-modules except the MIIM module. Setting the MIIMRST bit in the MIIMODER register to 1 resets the MIIM module. To reset the PHY, assert its RESET signal either through the boars system control register or by writing an appropriate bit in the PHY register.

### **4.2 Host Interface Operation**

The host interface connects the Ethernet IP Core to the rest of the system (RISC, memory) via the WISHBONE bus. The WISHBONE serves to access the configuration registers and the memory. Currently, only DMA transfers are supported for transferring the data from/to the memory.

#### 4.2.1 Configuration Registers

The function of the configuration registers is transparent and can be easily understood by reading the Registers section (Chapter 3).

#### 4.2.2 Buffer Descriptors (BD)

The transmission and the reception processes are based on the descriptors. The Transmit Descriptors (TxD) are used for transmission while the Receive Descriptors (RxD) are used for reception.

The buffer descriptors are 64 bits long. The first 32 bits are reserved for length and status while the last 32 bits contain the pointer to the associated buffer (where data is stored). The Ethernet MAC core has an internal RAM that can store up to 128 BDs (for both Rx and Tx).

The internal memory saves all descriptors at addresses from 0x400 to 0x7ff (128 64bit descriptors). The transmit descriptors are located between the start address (0x400) and

http://www.opencores.org

the address that equals the value written in the TX\_BD\_NUM register (page 14) multiplied by 8. This register holds the number of the used Tx buffer descriptors. The receive descriptors are located between the start address (0x400), plus the address number written in the TX\_BD\_NUM multiplied by 8, and the descriptor end address (0x7ff).

The transmit and receive status of the packet is written to the associated buffer descriptor once its transmission/reception is finished.