An www.OpenCores.org

Project

ghuber@opencores.org

# **Revision History**

| Revision | Date         | Author    | Description                                        |  |  |  |  |  |  |  |  |

|----------|--------------|-----------|----------------------------------------------------|--|--|--|--|--|--|--|--|

| 1.0      | 3 Sept 2005  | G Huber   | Initial Revision                                   |  |  |  |  |  |  |  |  |

| 1.1      | 10 Sept 2005 | G Huber   | Add parts, fix some typo's                         |  |  |  |  |  |  |  |  |

| 2.0      | 17 Sept 2005 | H LeFevre | 1. Add LFSR's                                      |  |  |  |  |  |  |  |  |

|          |              |           | 2. Add gh_ prefix to the name of some parts.       |  |  |  |  |  |  |  |  |

|          |              |           | (See chapter 4 for explanation on this change)     |  |  |  |  |  |  |  |  |

|          |              |           | 3 Mod parts to use gh_ parts (where required)      |  |  |  |  |  |  |  |  |

| 2.1      | 18 Sept 2005 | G Huber   | Add decoder/mux, clock divider, and NCO            |  |  |  |  |  |  |  |  |

| 2.2      | 24 Sept 2005 | S A Dodd  | Add pulse generator                                |  |  |  |  |  |  |  |  |

| 2.3      | 1 Oct 2005   | G Huber   | Add sweep generator                                |  |  |  |  |  |  |  |  |

| 2.4      | 4 Oct 2005   | H LeFevre | Add Random Number Generator/CASR                   |  |  |  |  |  |  |  |  |

| 3.0      | 8 Oct 2005   | G Huber   | Reorganize library,                                |  |  |  |  |  |  |  |  |

|          |              |           | add a couple of shift registers                    |  |  |  |  |  |  |  |  |

| 3.1      | 15 Oct 2005  | S A Dodd  | Add parity generator, FIFO's, integer counters     |  |  |  |  |  |  |  |  |

| 3.2      | 23 Oct 2005  | G Huber   | Add programmable LFSR's                            |  |  |  |  |  |  |  |  |

| 3.3      | 29 Oct 2005  | G Huber   | Add Configuration Registers                        |  |  |  |  |  |  |  |  |

| 3.4      | 13 Nov 2005  | S A Dodd, | Add some memory parts                              |  |  |  |  |  |  |  |  |

|          |              | G Huber   |                                                    |  |  |  |  |  |  |  |  |

| 3.5      | 14 Jan 2006  | G Huber   | Add delay lines                                    |  |  |  |  |  |  |  |  |

| 3.6      | 21 Jan 2006  | S A Dodd  | Add Control Registers                              |  |  |  |  |  |  |  |  |

|          |              | G Huber   | Add a fixed delay line for a bus                   |  |  |  |  |  |  |  |  |

| 3.7      | 28 Jan 2006  | H LeFevre | Add a baud rate generator                          |  |  |  |  |  |  |  |  |

| 3.8      | 4 Feb 2006   | S A Dodd  | Add FIFO with sync clear                           |  |  |  |  |  |  |  |  |

|          |              | H LeFevre | Add an In Place Multiplier                         |  |  |  |  |  |  |  |  |

| 3.9      | 11 Feb 2006  | H LeFevre | Add two more In Place Multipliers (one has both    |  |  |  |  |  |  |  |  |

|          |              |           | inputs unsigned and the other both inputs are      |  |  |  |  |  |  |  |  |

|          |              |           | signed)                                            |  |  |  |  |  |  |  |  |

|          |              | G Huber   | Add another shift register (shifts left)           |  |  |  |  |  |  |  |  |

| 3.10     | 18 Feb 2006  | G Huber   | Add another shift register (also shifts left)      |  |  |  |  |  |  |  |  |

|          |              |           | Finished adding the gh_ prefix to all parts        |  |  |  |  |  |  |  |  |

| 3.11     | 25 Mar 2006  | H LeFevre | Add one more In Place Multiplier                   |  |  |  |  |  |  |  |  |

|          |              | S A Dodd  | Mod gh_sincos to use Cordic ± 45                   |  |  |  |  |  |  |  |  |

| 3.12     | 13 May 2006  | S A Dodd  | Add FIR Filter                                     |  |  |  |  |  |  |  |  |

| 3.13     | 26 May 1006  | G Huber   | Add debounce, stretch low                          |  |  |  |  |  |  |  |  |

| 3.14     | 16 Sept 2006 | G Huber   | Add a counter, 18 bit multipliers                  |  |  |  |  |  |  |  |  |

| 3.15     | 23 Sept 2006 | SA Dodd   | Add complex math parts                             |  |  |  |  |  |  |  |  |

| 3.16     | 23 Dec 2006  | H LeFevre | Replace async FIFO (to use gray code)              |  |  |  |  |  |  |  |  |

| 3.17     | 27 Dec 2006  | G Huber   | Add Gray code converters                           |  |  |  |  |  |  |  |  |

|          |              | HL/SD     | Update FIFO's                                      |  |  |  |  |  |  |  |  |

| 3.18     | 13 Jan 2007  | H LeFevre | add async FIFO's with 1/4. 1/2, and 3/4 full flags |  |  |  |  |  |  |  |  |

| 3.19     | 27 Jan 2007  | SA Dodd   | add digital attenuator                             |  |  |  |  |  |  |  |  |

| 3.20     | 3 Feb 2007   | H LeFevre | add parallel FIR Filter                            |  |  |  |  |  |  |  |  |

| 3.21     | 10 Feb 2007  | H LeFevre | add FIR Filters of odd order, negative symmetry    |  |  |  |  |  |  |  |  |

| 3.22  | 9 June 2007  | G Huber<br>SA Dodd | add programmable delay bus, FASM dual port Ram with reset, 3 multipliers with generics |

|-------|--------------|--------------------|----------------------------------------------------------------------------------------|

| 2.22  | 30 June 2007 |                    |                                                                                        |

| 3.23  | 30 June 2007 | H LeFevre          | add 2 in-place multipliers, with all data bits out                                     |

|       |              | G Huber            | add MAC with full generics and an unsigned array                                       |

| 2.24  | 15.1.1.2005  | G A D 11           | divider                                                                                |

| 3.24  | 15 July 2007 | S A Dodd           | add a FIR filter and Pulse time/width module                                           |

| 3.25  | 12 Aug 2007  | S A Dodd           | mod/add filter                                                                         |

| 3.26  | 16 Aug 2007  | S A Dodd           | add (two clock multiply) complex multipliers                                           |

| 3.27  | 14 Oct 2007  | H LeFevre          | add some filters w/o multipliers                                                       |

| 3.28  | 21 Oct 2007  | S A Dodd           | Add rev A of rectangular to polar (CORDIC                                              |

|       |              |                    | application) – increases pipelining                                                    |

|       |              | G Huber            | add 4 byte memory                                                                      |

| 3.29  | 22 Nov 2007  | H LeFevre          | add VMEbus Slave Interface Module parts                                                |

| 3.30  | 25 Nov 2007  | H LeFevre          | add FIR filter, rev A for NCO                                                          |

| 3.31  | 8 Dec 2007   | G Huber            | add VME read Modules                                                                   |

| 3.32  | 30 Dec 2007  | H LeFevre          | add 3 multiplier complex multipliers                                                   |

| 3.33  | 3 May 2008   | H LeFevre          | Add random number scalar (serial multiplier)                                           |

| 3.33a | 4 May 2008   |                    | Add random number scalar (parallel multiplier)                                         |

| 3.34  | 24 May 2008  | H LeFevre          | Add two asynchronous fifo's (with UART style                                           |

|       |              |                    | flags)                                                                                 |

| 3.35  | 27 May 2008  | G Huber            | Add programmable delay line using generics                                             |

| 3.36  | 1 June 2008  | S A Dodd           | 3 complex multipliers, with an extra register                                          |

|       |              |                    | delay for higher operating frequency                                                   |

|       |              |                    | Data Mux(2:1) /DeMux (1:2) set                                                         |

| 3.37  | 4 July 2008  | G Huber            | Add some NCO type accumulators                                                         |

| 3.38  | 1 Sept 2008  | H LeFevre          | Add versions of a couple frequency syntheses parts                                     |

| 3.39  | 20 Sept 2008 | H LeFevre          | Add programmable Stretch parts, add init to some                                       |

|       | _            |                    | of the memory parts                                                                    |

| 3.40  | 27 Sept 2008 | H LeFevre          | Add 4 byte GPIO                                                                        |

| 3.41  | 04 Oct 2008  | H LeFevre          | Add Burst Generator                                                                    |

| 3.42  | 11 Oct 2008  | H LeFevre          | Add CORDIC's with 28 bit atan functions                                                |

| 3.43  | 26 Oct 2008  | H LeFevre          | Add Sin Cos ROM's                                                                      |

| 3.44  | 1 Nov 2008   | H LeFevre          | Add Sin Cos ROM's with quarter size tables                                             |

| 3.45  | 8 Nov 2008   | H LeFevre          | Add config registers (3072, 4096 bits), fix notes                                      |

| 3.46  | 25 Jan 2009  | H LeFevre          | Add watch dog timers                                                                   |

| 3.47  | 28 Feb 2009  | H LeFevre          | Add Pulse Width Modulator                                                              |

# **Table of Contents**

| 1 | Intro | duction                                     | 1    |

|---|-------|---------------------------------------------|------|

|   | 1.1   | Purpose                                     | 1    |

|   | 1.2   | What the Library is Not                     | 1    |

|   | 1.3   | GH VHDL License                             | 1    |

| 2 | Basi  | c Registers and Gates                       | 3    |

|   | 2.1   | D Flip Flop                                 |      |

|   | 2.2   | JK Flip Flop                                |      |

|   | 2.3   | Basic Register and Latch                    |      |

|   | 2.4   | XOR Bus                                     |      |

|   | 2.5   | Comparators                                 | 5    |

|   | 2.6   | Decoders                                    | 6    |

|   | 2.7   | Multiplexers                                | 6    |

|   | 2.8   | Shift Registers                             | 7    |

|   | 2.9   | Four Byte Configuration Registers           | 8    |

| 3 | Cou   | nters                                       |      |

|   | 3.1   | Binary Counters                             | 9    |

|   | 3.2   | Modulo Counter                              | . 10 |

|   | 3.3   | Integer Counters                            |      |

| 4 | Cust  | om MSI Parts                                |      |

|   | 4.1   | Pulse Stretcher                             |      |

|   | 4.2   | Edge Detector                               |      |

|   | 4.3   | Clock Divider                               |      |

|   | 4.4   | Pulse Generator                             | . 13 |

|   | 4.5   | Parity Generator                            |      |

|   | 4.6   | Delay Lines                                 |      |

|   | 4.7   | Baud Rate Generator                         |      |

|   | 4.8   | Control Registers                           |      |

|   | 4.9   | A Switch de-bouncer                         |      |

|   | 4.10  | An Edge Detector for changing Clock Domains |      |

|   | 4.11  | Gray code converters                        |      |

|   |       | Pulse Width/Time Measurement                |      |

|   | 4.13  | Lower Rate Clock Mirror                     |      |

|   | 4.14  | Data DeMux 1 to 2                           | . 19 |

|   | 4.15  | Data Mux 2 to 1                             |      |

|   |       | Four Byte GPIO                              |      |

|   | 4.17  | Burst Generator                             |      |

|   | 4.18  | Watch Dog Timers                            |      |

|   | 4.19  | Pulse Width Modulator                       |      |

| 5 |       | n Functions                                 |      |

| ٠ | 5.1   | Accumulator                                 |      |

|   | 5.2   | Multipliers                                 |      |

|   | 5.3   | Multipliers using Generics                  |      |

|   | 5.4   | Multiplier Accumulator                      |      |

|   |       | Random Number Generation                    |      |

|    | 5.5.1 | 1 The Linear Feedback Shift Register (LFSR) | 26 |

|----|-------|---------------------------------------------|----|

|    | 5.5.2 | 2 CASR and Random Number Generator          | 27 |

|    | 5.5.3 | 3 Programmable LFSR's                       | 28 |

|    | 5.5.4 | 4 Random Number Scalars                     | 29 |

|    | 5.6   | In Place Multipliers                        | 30 |

|    | 5.7   | Unsigned Array Divider                      |    |

|    | 5.8   | Complex Math                                |    |

|    | 5.9   | Digital Attenuator                          |    |

| 6  | Men   | mory                                        | 35 |

|    | 6.1   | Synchronous RAM                             | 35 |

|    | 6.2   | FIFO's                                      | 36 |

|    | 6.2.1 | 1 Synchronous FIFO                          | 36 |

|    | 6.2.2 | 2 Asynchronous FIFO                         | 37 |

|    | 6.2.3 | 3 Asynchronous FIFO's with UART Style Flags | 38 |

|    | 6.3   | Four Byte Dual Port RAM                     |    |

| 7  | Freq  | quency Synthesis                            | 40 |

|    | 7.1   | The DDS (also known as the NCO, or DCO)     | 40 |

|    | 7.1.1 | 1 NCO Style Accumulators                    | 41 |

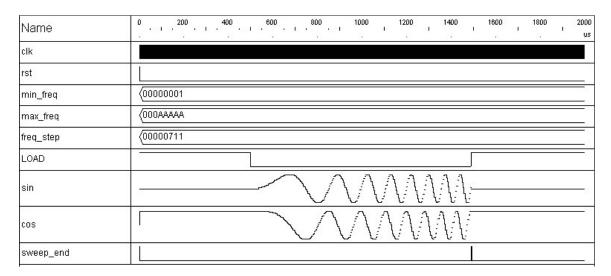

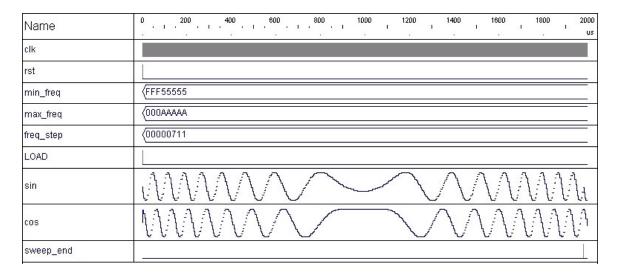

|    | 7.2   | Sweep Generator                             | 42 |

|    | 7.2.1 | Simulation of the Sweep Generator           | 45 |

|    | 7.3   | CORDIC Rotation Algorithm                   | 46 |

|    | 7.3.1 |                                             |    |

|    | 7.3.2 | 2 Applications for the CORDIC               | 49 |

|    | 7.4   | Sin Cos ROM Lookup Tables                   |    |

| 8  | Filte | ers                                         | 51 |

|    | 8.1   | CIC Filter                                  | 51 |

|    | 8.2   | Time-Varying Fractional Delay Filters       | 54 |

|    | 8.2.1 | 1 The Lagrange Interpolator                 | 54 |

|    | 8.2.2 | 2 Time–Varying Control                      | 55 |

|    | 8.2.3 | 3 TVFD Application Notes                    | 55 |

|    | 8.3   | A single MAC FIR Filter                     | 56 |

|    | 8.4   | Symmetrical, parallel FIR Filters           | 57 |

|    | 8.4.1 | 1 FIR Filter Architecture                   | 58 |

|    | 8.5   | FIR Filters Without Multipliers             | 59 |

| 9  | VMI   | IEbus [VXIbus] Interface Modules            | 60 |

|    | 9.1   | VME Slave Modules                           | 61 |

|    | 9.2   | VME Chip Select Modules                     | 63 |

|    | 9.3   | VME Read Modules                            | 63 |

| 10 | ) Ii  | ibrary Notes                                | 64 |

### 1 Introduction

The GH VHDL Standard Parts Library is a collection of basic VHDL parts that may be included in larger designs. There is nothing wrong with modifying library parts so that they will meet the system requirements.

### 1.1 Purpose

- Educational this is a set of design examples that demonstrate some of the more important language constructs.

- To have a set of building blocks to aid in the building of a VHDL design Large designs can be broken up into smaller blocks. When there are common functions in these blocks, time can be saved when these common functions can be designed once and reused many times.

Note: The library is setup as a collection of design files – this makes it easy to examine the design of each part. Some may want to put them together as a "proper" VHDL library.

### 1.2 What the Library is Not

- A VHDL language reference.

- Complete Contributions are encouraged, which may be added the library (or ignored) at our discretion.

- Perfect. Look for ways to improve it even if we do not like your "improvements," if they make your life easier, use them anyway.

#### 1.3 GH VHDL License

Copyright (c) 2005, 2006, 2007, 2008, 2009 by George Huber

Permission is hereby granted, free of charge, to any person obtaining a copy of this OpenCores Project and associated documentation (the "lesser IP"), to use it in the in larger designs (the "greater IP") without restriction, subject to the following conditions:

- 1. The copyright notice is retained in the source files, and if they are modified, the Revision block must updated to identify the changes.

- 2. The lesser IP itself may not be sold, but this restriction is limited to the lesser IP itself, not to any greater IP that it may be used in. (Inclusion on a distribution CD of, for example, OpenSource Projects is not considered a "sale")

- 3. Any greater IP which uses the lesser IP, when distributed as source code or synthesized net list, must include in the documentation an acknowledgement of using the GH VHDL Library (This acknowledgement is not required for the

- distribution of a fuse map or other hardware implementation in CPLD, FPGA, ASIC or other form of custom IC).

- 4. THE LESSER IP IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED.

- 5. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY ARISING FROM, OR IN CONNECTION WITH THE USE OF THE LESSER IP.

# 2 Basic Registers and Gates

Here are the basic parts that make up many larger systems. For some of these, it may be argued that it is more work to instantiate them than it is to rewrite the function. However, a number of design entry tools allow the use of Block diagrams. When using block diagrams, it is useful to have these parts available.

# 2.1 D Flip Flop

The D Flip Flop is almost too simple to be in the library, but it is here anyway.

| I/O |   | Function                        |

|-----|---|---------------------------------|

| CLK | I | Clock, rising edge is used      |

| rst | I | Asynchronous Reset, active high |

| D   | I | Input Data                      |

| Q   | О | Output Data                     |

File name: gh\_DFF.vhd

# 2.2 JK Flip Flop

| I/O |   | Function                        |

|-----|---|---------------------------------|

| CLK | I | Clock, rising edge is used      |

| rst | I | Asynchronous Reset, active high |

| J   | I | J Input                         |

| K   | I | K Input                         |

| Q   | О | Output Data                     |

File name: gh\_JKFF.vhd

Truth Table for the JKFF

| CLK        | rst | J | K | Q         |

|------------|-----|---|---|-----------|

| X          | 1   | X | X | 0         |

| <b>↑</b>   | 0   | 1 | 0 | 1         |

| <b>↑</b>   | 0   | 0 | 1 | 0         |

| <b>1</b>   | 0   | 1 | 1 | toggle    |

| $\uparrow$ | 0   | 0 | 0 | no change |

# 2.3 Basic Register and Latch

These parts have the generic "size" which sets the data width.

| I/O                |   | Function                             |

|--------------------|---|--------------------------------------|

| CLK                | I | Clock, rising edge is used           |

| rst                | I | Asynchronous Reset, active high      |

| LE                 | I | Latch enable (1 = transparent D to Q |

|                    |   | 0 = hold  Q)                         |

| CE                 | I | Clock enable                         |

| D(size-1 downto 0) | I | Input Data                           |

| Q(size-1 downto 0) | О | Output Data                          |

| Parts              | С | r | L | С | D | Q | comments |

|--------------------|---|---|---|---|---|---|----------|

|                    | L | S | Е | Е |   |   |          |

|                    | K | t |   |   |   |   |          |

| gh_latch.vhd       |   |   | X |   | X | X |          |

| gh_register.vhd    | X | X |   |   | X | X |          |

| gh_register_ce.vhd | X | X |   | X | X | X |          |

### 2.4 XOR Bus

This is just a XOR gate with a programmable length (using the generic "size"). Its purpose is to make it easier to combine two LFSR's (of different length), or a LFSR with a CASR (Cellular Automata Shift Register), to improve the characteristics of the generated random numbers.

| I/O              | Function |                                 |  |  |  |  |

|------------------|----------|---------------------------------|--|--|--|--|

| A(size downto 1) | I        | Size number of bits from LFSR A |  |  |  |  |

| B(size downto 1) | I        | Size number of bits from LFSR B |  |  |  |  |

| Q(size downto 1) | О        | output                          |  |  |  |  |

File name: gh\_xor\_bus.vhd

# 2.5 Comparators

While Comparators are not strictly gates, they are included here because they are simple enough that some people will find it easier to rewrite the code, than it is to instantiate a component.

| I/O                    |   | Function                                        |

|------------------------|---|-------------------------------------------------|

| A (size-1 downto 0)    | I | A input vector                                  |

| B (size-1 downto 0)    | I | B input vector                                  |

| min (size-1 downto 0)  | I |                                                 |

| max (size-1 downto 0)  | I |                                                 |

| D (size-1 downto 0)    | I |                                                 |

| AGB                    | О | ABS of A is greater than the ABS of B when high |

| AEB                    | О | ABS of A is equal to the ABS of B when high     |

| ALB                    | O | ABS of A is less than the ABS of B when high    |

| AS                     | О | A sign bit                                      |

| BS                     | О | B sign bit                                      |

| ABS_A(size-1 downto 0) | О | ABS of A                                        |

| ABS_B(size-1 downto 0) | О | ABS of B                                        |

| Y                      | O | Y = '1' when D is between min and max           |

| Parts                      | A | В | m | m | D | A | A | A | A | В | A      | A      | Y | Comments   |

|----------------------------|---|---|---|---|---|---|---|---|---|---|--------|--------|---|------------|

|                            |   |   | i | a |   | G | E | L | S | S | В      | В      |   |            |

|                            |   |   | n | X |   | В | В | В |   |   | S      | S      |   |            |

|                            |   |   |   |   |   |   |   |   |   |   | –<br>A | -<br>B |   |            |

| gh_compare.vhd             | X | X |   |   |   | X | X | X |   |   |        |        |   | Unsigned   |

|                            |   |   |   |   |   |   |   |   |   |   |        |        |   | data       |

| gh_compare_ABS.vhd         | X | X |   |   |   | X | X | X | X | X | X      | X      |   | Signed     |

|                            |   |   |   |   |   |   |   |   |   |   |        |        |   | data       |

| gh_compare_BMM.vhd         |   |   | X | X | X |   |   |   |   |   |        |        | X | Unsigned   |

|                            |   |   |   |   |   |   |   |   |   |   |        |        |   | data       |

| gh_compare_BMM_s.vhd       |   |   | X | X | X |   |   |   |   |   |        |        | X | signed     |

|                            |   |   |   |   |   |   |   |   |   |   |        |        |   | data       |

| gh_compare_ABS_reg.vhd     | X | X |   |   |   | X | X | X | X | X | X      | X      |   | Signed     |

| (clk and rst inputs added) |   |   |   |   |   |   |   |   |   |   |        |        |   | data- adds |

|                            |   |   |   |   |   |   |   |   |   |   |        |        |   | pipeline   |

|                            |   |   |   |   |   |   |   |   |   |   |        |        |   | registers  |

# 2.6 Decoders

The design of the decoders is based on the 75LS138, except that the outputs, when active, are high.

| I/O                 |   | Function                                      |

|---------------------|---|-----------------------------------------------|

| A                   | I | Address/select input                          |

| G1                  | I | Output enable, active high                    |

| G2n                 | I | Output enable, active low                     |

| G2n                 | I | Output enable, active low                     |

| Y(8 or 16 downto 0) | О | Output bus, only 1 output is active (high) at |

|                     |   | a time- when all enables are active           |

| Parts                | A | G | G | G | Y       | Comments                      |

|----------------------|---|---|---|---|---------|-------------------------------|

|                      |   | 1 | 2 | 3 |         |                               |

|                      |   |   | n | n |         |                               |

| gh_decoder_2to4.vhd  | X | X | X | X | 4 bits  | Output bit, which corresponds |

|                      |   |   |   |   |         | with value of A, is high      |

| gh_decoder_3to8.vhd  | X | X | X | X | 8 bits  | Output bit, which corresponds |

|                      |   |   |   |   |         | with value of A, is high      |

| gh_decoder_4to16.vhd | X | X | X | X | 16 bits | Output bit, which corresponds |

|                      |   |   |   |   |         | with value of A, is high      |

# 2.7 Multiplexers

| I/O   |   | Function                                |

|-------|---|-----------------------------------------|

| sel   | I | Selects which input becomes the output  |

| A - P | I | Data inputs                             |

|       |   | A input sel = $0$ , B input sel = $1$ , |

|       |   | C input sel = 2, D input sel =3 etc     |

| Y     | О | Output                                  |

| Parts                | sel    | Data  | Y | Comments                          |

|----------------------|--------|-------|---|-----------------------------------|

| gh_mux_2to1.vhd      | 1 bit  | A, B  | X |                                   |

| gh_mux_2to1_bus.vhd  | 1 bit  | A, B  | X | Uses generic size to set width of |

|                      |        |       |   | data bus                          |

| gh_mux_4to1.vhd      | 2 bits | A – D | X |                                   |

| gh_mux_4to1_bus.vhd  | 2 bits | A – D | X | Uses generic size to set width of |

| gh_mux_8to1_bus.vhd  | 3 bits | A – H | X | data bus                          |

| gh_mux_16to1_bus.vhd | 4 bits | A - P | X |                                   |

# 2.8 Shift Registers

These are just a simple shift registers – the input D is loaded into Q(0) [when shifting right] with each clock edge. The data Q(n) is shifted to Q(n+1) at the same time [or Q(n+1) is shifted to Q(n) when shifting left]. The Shift Register's have the generic "size" which sets the number of bits to be shifted.

It should be noted the "shift left" and "shift right" refers to shifting the data as if it is lined up: q0 q1 q2 q3 q4...qn. Default for this library is shift right (\_sl in the name means it shifts left, \_slr means it can shift either left or righ).

| I/O                     |   | Function                                |

|-------------------------|---|-----------------------------------------|

| CLK                     | I | Clock, rising edge is used              |

| rst                     | I | Asynchronous Reset, active high         |

| srst                    | I | Synchronous reset, active high          |

| LOAD                    | I | Parallel Load command                   |

| SE                      | I | Shift enable                            |

| MODE                    | I | Mode Bits: 00 hold (do nothing)         |

|                         |   | 01 shit right ( $Q_i = Q_{i-1}$ )       |

|                         |   | 10 shift left $(Q_i = Q_{i+1})$         |

|                         |   | 11 Parallel Load                        |

| DSL                     | I | Serial data in for shift left           |

| DSR                     | I | Serial data in for shift right          |

| D or D(size-1 downto 0) | I | Data bit(s) to be shifted and/or loaded |

| Q(size-1 downto 0)      | О | Shifted bits out                        |

| Parts                   | С | r | S | L | S | M | D | D | D | Q | Comments             |

|-------------------------|---|---|---|---|---|---|---|---|---|---|----------------------|

|                         | L | S | r | О | Е | О | S | S |   |   |                      |

|                         | K | t | S | Α |   | D | L | R |   |   |                      |

|                         |   |   | t | D |   | Ε |   |   |   |   |                      |

| gh_shift_reg.vhd        | X | X |   |   |   |   |   |   | X | X |                      |

| gh_shift_reg_rs.vhd     | X | X | X |   |   |   |   |   | X | X | Reset can be changed |

|                         |   |   |   |   |   |   |   |   |   |   | to Preset w/generic  |

| gh_shift_reg_PL.vhd     | X | X |   | X | X |   |   |   | X | X | Parallel Load, shift |

|                         |   |   |   |   |   |   |   |   |   |   | right                |

| gh_shift_reg_PL_sl.vhd  | X | X |   | X | X |   |   |   | X | X | Parallel Load, shift |

|                         |   |   |   |   |   |   |   |   |   |   | left                 |

| gh_shift_reg_PL_SLR.vhd | X | X |   |   |   | X | X | X | X | X | Parallel Load, shift |

|                         |   |   |   |   |   |   |   |   |   |   | left or right        |

| gh_shift_reg_se_sl.vhd  | X | X | X |   | X |   |   |   | X | X |                      |

# 2.9 Four Byte Configuration Registers

Here is a collection of registers intended for use as configuration/control - set up so that they may be initialized by byte, word, or long word access on a 32 bit data buss.

With FPGA gate counts of over 3 million, how many configuration bits are required?

| I/O             |   | Function                            |

|-----------------|---|-------------------------------------|

| clk             | I | Clock, rising edge is used          |

| rst             | I | Asynchronous Reset, active high     |

| CSn             | I | Chip Select, active low             |

| WR              | I | Write strobe, active high           |

| BE(3 downto 0)  | I | Byte enable bits                    |

| A               | I | Address bits (Long Word addressing, |

|                 |   | BE is used to identify which byte)  |

| D(31 downto 0)  | I | Data buss in                        |

| RD(31 downto 0) | О | Read Configuration Data             |

| Q               | О | Configuration Bits                  |

| Parts                 | С | r | С | W | В | Α | D | R | Q | Comments             |

|-----------------------|---|---|---|---|---|---|---|---|---|----------------------|

|                       | L | S | S | R | Е |   |   | D |   |                      |

|                       | K | t | n |   |   |   |   |   |   |                      |

| gh_4byte_reg_32.vhd   | X | X |   | X | X |   | X |   | X | Used on larger parts |

| gh_4byte_reg_64.vhd   | X | X | X | X | X | X | X | X | X |                      |

| gh_4byte_reg_128.vhd  | X | X | X | X | X | X | X | X | X |                      |

| gh_4byte_reg_256.vhd  | X | X | X | X | X | X | X | X | X | Used on larger parts |

| gh_4byte_reg_512.vhd  | X | X | X | X | X | X | X | X | X |                      |

| gh_4byte_reg_768.vhd  | X | X | X | X | X | X | X | X | X |                      |

| gh_4byte_reg_1024.vhd | X | X | X | X | X | X | X | X | X | Used on larger parts |

|                       |   |   |   |   |   |   |   |   |   | (3072,4096)          |

| gh_4byte_reg_1536.vhd | X | X | X | X | X | X | X | X | X |                      |

| gh_4byte_reg_2048.vhd | X | X | X | X | X | X | X | X | X |                      |

| gh_4byte_reg_3072.vhd | X | X | X | X | X | X | X | X | X |                      |

| gh_4byte_reg_4096.vhd | X | X | X | X | X | X | X | X | X |                      |

# 3 Counters

# 3.1 Binary Counters

All of these counters use standard logic vectors and use the generic "size" to set the number of bits used in the counter.

| I/O                |   | Function                        |

|--------------------|---|---------------------------------|

|                    |   |                                 |

| CLK                | I | Clock, rising edge is used      |

| rst                | I | Asynchronous Reset, active high |

| srst               | I | Synchronous Reset, active high  |

| CE                 | I | Count enable, active high       |

| LOAD               | I | Parallel load control           |

| UP_D               | I | Up/down control                 |

| D(size-1 downto 0) | I | Parallel load Data              |

| TC                 | О | Terminal Count                  |

| one                | О | Active when Count = 1           |

| Q(size-1 downto 0) | О | Count value out                 |

| Parts                        | С | r | S | С | L | U | D | T | o | Q | comments           |

|------------------------------|---|---|---|---|---|---|---|---|---|---|--------------------|

|                              | L | S | r | Е | О | P |   | C | n |   |                    |

|                              | K | t | S |   | A | _ |   |   | e |   |                    |

|                              |   |   | t |   | D | D |   |   |   |   |                    |

| gh_counter.vhd               | X | X |   | X | X | X | X | X |   | X | Universal          |

|                              |   |   |   |   |   |   |   |   |   |   | Up/down counter    |

| gh_counter_up_sr_ce.vhd      | X | X | X | X |   |   |   |   |   | X | Up counter         |

| gh_counter_up_ce.vhd         | X | X |   | X |   |   |   |   |   | X | Up counter         |

| gh_counter_up_ce_tc.vhd      | X | X |   | X |   |   |   | X |   | X | Up counter         |

| gh_counter_up_ce_ld.vhd      | X | X |   | X | X |   | X |   |   | X | Up counter         |

| gh_counter_up_ce_ld_tc.vhd   | X | X |   | X | X |   | X | X |   | X | Up counter         |

| gh_counter_down_ce_ld.vhd    | X | X |   | X | X |   | X |   |   | X | Down counter       |

| gh_counter_down_ce_ld_tc.vhd | X | X |   | X | X |   | X | X |   | X | Down counter       |

| gh_counter_down_one.vhd      | X | X |   | X | X |   | X | X | X | X | Useful as an event |

|                              |   |   |   |   |   |   |   |   |   |   | counter            |

| gh_counter_fr.vhd            | X | X |   |   |   |   |   |   |   |   | A free running     |

|                              |   |   |   |   |   |   |   |   |   |   | binary counter     |

Why have so many counters in the library, when the first one is a super set of (most) the rest? After all, the synthesis tools will remove the excess logic. Logic verification is the answer. If a code coverage (and/or toggle coverage) tool is used to verify the design, some of the excess logic will show up as untested.

#### 3.2 Modulo Counter

The Modulo counter is a specialized counter. It is incremented by the input N, and will roll over at the generic modulo. It will increment by the specified value even as it rolls over. The terminal count will go active the clock period before the roll over, for all values of N.

| I/O                |   | Function                        |

|--------------------|---|---------------------------------|

|                    |   |                                 |

| CLK                | I | Clock, rising edge is used      |

| Rst                | I | Asynchronous Reset, active high |

| CE                 | I | Count enable, active high       |

| N(size-1 downto 0) | I | Increments by this value        |

| TC                 | О | Terminal Count                  |

| Q(size-1 downto 0) | О | Count value out                 |

| Parts                 | С | r | С | N | T | Q | comments                        |

|-----------------------|---|---|---|---|---|---|---------------------------------|

|                       | L | s | Е |   | C |   |                                 |

|                       | K | t |   |   |   |   |                                 |

| gh_counter_modulo.vhd | X | X | X | X | X | X | Note: size must be large enough |

|                       |   |   |   |   |   |   | to count up to modulo           |

# 3.3 Integer Counters

The Integer Counters us integers, rather than standard logic vectors for holding the count values. They have one generic, max\_count. The chief advantage this counter have is that they can be set to count to any value, without having a vector size to set.

| I/O  |   | Function                        |

|------|---|---------------------------------|

|      |   |                                 |

| clk  | I | Clock, rising edge is used      |

| rst  | I | Asynchronous Reset, active high |

| LOAD | I | Parallel load control           |

| CE   | I | Count enable, active high       |

| D    | I | Parallel load Data              |

| Q    | О | Count value out                 |

| Parts                       | С | r | С | L | D | Q | comments                           |

|-----------------------------|---|---|---|---|---|---|------------------------------------|

|                             | L | s | Е | О |   |   |                                    |

|                             | K | t |   | A |   |   |                                    |

|                             |   |   |   | D |   |   |                                    |

| gh_counter_integer_up.vhd   | X | X | X | X | X | X | Counts up to max _count            |

| gh_counter_integer_down.vhd | X | X | X | X | X | X | Counts down to zero, rolls over to |

|                             |   |   |   |   |   |   | max_count                          |

# 4 Custom MSI Parts

This is a collection of parts that have functions that are not normally found in Standard MSI parts, but are not particularly complex in design.

#### 4.1 Pulse Stretcher

The fixed Pulse Stretchers have the generic "stretch\_count" which sets the number of clock periods that the pulse will be stretched. The programmable Pulse Stretches use the generic "size" the set the number of bits used to control the stretch count.

| I/O                       |   | Function                             |

|---------------------------|---|--------------------------------------|

| CLK                       | I | Clock, rising edge is used           |

| rst                       | I | Asynchronous Reset, active high      |

| D (Dn)                    | I | Input pulse to be stretched          |

| stretch(size -1 downto 0) | I | Number of clocks to stretch pulse by |

| Q (Qn)                    | О | Stretched pulse out                  |

For the fixed Pulse Stretchers, an integer Variable is used to control the pulse stretching. This means only one generic is needed to be control the stretch time. If a STD\_LOGIC\_VECTOR had been used, the number of bits in the vector would also need to be adjustable.

| Parts                           | С | r | D(n) | stretch | Q | Comments               |

|---------------------------------|---|---|------|---------|---|------------------------|

|                                 | L | s |      |         |   |                        |

|                                 | K | t |      |         |   |                        |

| gh_stretch.vhd                  | X | X | X    |         | X | stretches a high pulse |

| gh_stretch_low.vhd              | X | X | X    |         | X | stretches a low pulse  |

| gh_stretch_programmable.vhd     | X | X | X    | X       | X | stretches a high pulse |

| gh_stretch_programmable_low.vhd | X | X | X    | X       | X | stretches a low pulse  |

# 4.2 Edge Detector

This part will detect edges on the data input. When the input is asynchronous, the "s" outputs should be used to avoid missing edges. With synchronous inputs, the "s" outputs will add a clock delay the non "s" outputs, without a gain in reliability.

| I/O |   | Function                                              |

|-----|---|-------------------------------------------------------|

| clk | I | Clock, rising edge is used                            |

| rst | I | Asynchronous Reset, active high                       |

| D   | I | Input data bit                                        |

| re  | О | Rising edge detected (needs a synchronous input)      |

| fe  | О | Falling edge detected (needs a synchronous input)     |

| sre | О | Rising edge detected (Data sampled before detection)  |

| sfe | О | Falling edge detected (Data sampled before detection) |

File name: gh\_edge\_det.vhd

#### 4.3 Clock Divider

This uses a generic to set the dived ratio, the number of high speed clocks per low speed clock. The output is one clock period wide, designed to drive a clock enable pin on the parts running at the lower clock rate.

| I/O |   | Function                         |

|-----|---|----------------------------------|

| CLK | I | Higher rate Clock                |

| rst | I | Asynchronous Reset, active high  |

| Q   | О | Lower rate "clock enable" output |

File name: gh\_clk\_ce\_div.vhd

This part was designed specifically to be used by the TVFD\_filter, the CIC\_filter and any other part that requires two related clocks, where the lower rate "clock" is a clock enable pulse with the correct period.

For the TVFD\_filter, the Q output drives the START input. For the CIC filtes, the Q output drives the ND input.

#### 4.4 Pulse Generator

Does this belong here? Well, where else?? The Pulse Generator it is a simple application of two counters. If the Pulse Width is set to be equal to or larger than the Period, the output pulse will be a constant high.

| I/O                                  |   |                                     |  |

|--------------------------------------|---|-------------------------------------|--|

| clk                                  | I | Clock, rising edge is used          |  |

| rst                                  | I | Asynchronous Reset, active high     |  |

| Period (size_Period-1 DOWNTO 0)      | I | The number of clocks between pulses |  |

| Pulse_Width (size_Period-1 DOWNTO 0) | I | The Pulse width, in clock periods   |  |

| ENABLE                               | I | Enable, active high                 |  |

| Pulse                                | О | The Output Pulse                    |  |

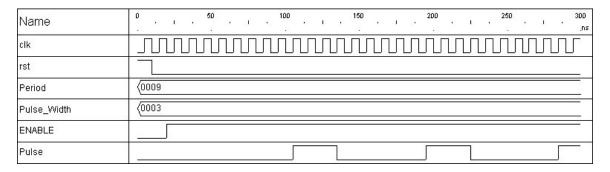

Here is a simulation of the Pulse generator with the period set to 9 and the pulse width set to 3. File name: gh\_pulse\_generator.vhd

# 4.5 Parity Generator

This is a serial parity generator. It needs to be before the start of a data word. The SD (sample data command) is included so that it is easy to use a clock that is greater that the data rate.

| I/O  |   | Function                        |

|------|---|---------------------------------|

| clk  | I | Clock, rising edge is used      |

| rst  | I | Asynchronous Reset, active high |

| srst | I | Synchronous Reset, active high  |

| SD   | I | Sample Data control             |

| D    | I | Serial data in                  |

| Q    | О | Parity Bit                      |

File name: gh\_parity\_gen\_Serial.vhd

# 4.6 Delay Lines

Here is a collection of registered delay lines. All of the delay lines use shift registers, so it is not just an edge that is delayed, it will delay the entire serial data string.

The fixed length delay line uses the generic "clock\_delays" to set the number of register delays.

The programmable delay lines use a number of fixed delay lines, each with a multiplexer at the input to select the source of the input, also a multiplexer is used to select the source for the output. This avoids the need for a single large multiplexer to select the delay tap.

**Note**: For the programmable delay lines- when the delay changes, any data in the shift registers may be at the "wrong delay." If it is not cleared, it will take the DELAY (or ½ max delay, which ever is less) number of clocks to shift out the "bad" data.

| I/O                               |   | Function                        |

|-----------------------------------|---|---------------------------------|

| clk                               | I | Clock, rising edge is used      |

| rst                               | I | Asynchronous Reset, active high |

| srst                              | I | Synchronous Reset, active high  |

| D                                 | I | Data input                      |

| DELAY (7, 6, 5, 4, or 3 downto 0) | I | Sets the programmable delay     |

| Q                                 | О | Output data                     |

| Parts                         | С | r | S | D | D | Q | Comments                       |

|-------------------------------|---|---|---|---|---|---|--------------------------------|

|                               | L | s | r |   | E |   |                                |

|                               | K | t | S |   | L |   |                                |

|                               |   |   | t |   | A |   |                                |

|                               |   |   |   |   | Y |   |                                |

| gh_delay.vhd                  | X | X | X | X |   | X | Uses generic "clock_delays" to |

|                               |   |   |   |   |   |   | set number of clock delays     |

| gh_delay_bus.vhd              | X | X | X | X |   | X | Uses generic "clock_delays" to |

|                               |   |   |   |   |   |   | set number of clock delays and |

|                               |   |   |   |   |   |   | the generic "size" to set bus  |

|                               |   |   |   |   |   |   | width                          |

| gh_delay_programmable_15.vhd  | X | X | X | X | X | X |                                |

| gh_delay_programmable_31.vhd  | X | X | X | X | X | X |                                |

| gh_delay_programmable_63.vhd  | X | X | X | X | X | X |                                |

| gh_delay_programmable_127.vhd | X | X | X | X | X | X |                                |

| gh_delay_programmable_255.vhd | X | X | X | X | X | X |                                |

| gh_delay_programmable_255_bus | X | X | X | X | X | X |                                |

| .vhd                          |   |   |   |   |   |   |                                |

| gh_delay_programmable_bus.vhd | X | X |   | X | X | X | Uses generics for data width   |

|                               |   |   |   |   |   |   | and size of possible delay     |

|                               |   |   |   |   |   |   | (address size of internal RAM) |

#### 4.7 Baud Rate Generator

This 16 bit baud rate generator is designed to be a building block in UART's. It has separate clocks for loading the baud rate register and for the generating baud rate. Valid baud rate divide ratio's are from 2-65535. Divide values of 1 or 0 will disable the generator. The counter will be reloaded with a write to either byte.

| I/O             |   | Function                          |

|-----------------|---|-----------------------------------|

| clk             | I | Clock, rising edge is used        |

| BR_clk          | I | Baud rate counter clock           |

| rst             | I | Asynchronous Reset, active high   |

| WR              | I | Write, active high                |

| BE(1 downto 0)  | I | Byte enable, active high          |

|                 |   | bit 1 for bits 15 downto 8        |

|                 |   | bit 0 for bits 7 downto 0         |

| D(15 downto 0)  | I | data in                           |

| RD(15 downto 0) | O | The baud rate register            |

| rCE             | О | Baud rate clock (Typically 16x of |

|                 |   | UART's baud rate- one BR_clk      |

|                 |   | period wide)                      |

| rCLK            | O | Baud rate clock (duty cycle about |

|                 |   | 50%)                              |

File name: gh\_baud\_rate\_gen.vhd

# 4.8 Control Registers

Embedded Systems often have Control Registers, where the software folks would like to be able to set or clear individual bits. If they can not do this, they may need to do a Read-Modify-Write, or use a shadow register so that only the desired bits are changed.

These Control Registers allow individual bits to be set, reset, or inverted. This is done by setting the MODE bits. The four operations are to write entire register, set any number of individual bits, clear any number of bits, or invert any number of bits.

One easy way of controlling the MODE bits is to tie them the to lower address bits.

| I/O                                 |   | Function                            |

|-------------------------------------|---|-------------------------------------|

| clk                                 | I | Clock, rising edge is used          |

| rst                                 | I | Asynchronous Reset, active high     |

| CE                                  | I | Clock enable, active high           |

|                                     |   | Note: this signal must by           |

|                                     |   | synchronous with clk, and must go   |

|                                     |   | low between data writes             |

| CSn                                 | I | Chip Select, active low             |

| WE                                  | I | Write strobe                        |

| BE(3 downto 0)                      | I | Byte enable bits                    |

| MODE(1 downto 0)                    | I | Mode bits                           |

|                                     |   | "00" writes D into Q                |

|                                     |   | "01" sets bits that are '1' in Q    |

|                                     |   | "10" clears bits that are '1' in Q  |

|                                     |   | "11" inverts bits that are '1' in Q |

| A                                   | I | Address (Long Word addressing, BE   |

|                                     |   | is used to identify which byte)     |

| D(size-1 downto 0) or (31 downto 0) | I | Data input                          |

| Q(size-1 downto 0) or (31 downto 0) | O | Output data                         |

| Parts                        | С | r | С | С | W | В | M | A | D | Q | Comments            |

|------------------------------|---|---|---|---|---|---|---|---|---|---|---------------------|

|                              | L | S | Е | S | Е | Е | О |   |   |   |                     |

|                              | K | t |   | n |   |   | D |   |   |   |                     |

|                              |   |   |   |   |   |   | Е |   |   |   |                     |

| gh_register_control_ce.vhd   | X | X | X |   |   |   | X |   |   | X | Uses generic "size" |

|                              |   |   |   |   |   |   |   |   |   |   | to set bit width of |

|                              |   |   |   |   |   |   |   |   |   |   | the register        |

| gh_4byte_control_reg_32.vhd  | X | X |   | X | X | X | X |   |   | X |                     |

| gh_4byte_control_reg_64.vhd  | X | X |   | X | X | X | X | X | X | X |                     |

| gh_4byte_control_reg_128.vhd | X | X |   | X | X | X | X | X | X | X |                     |

| gh_4byte_control_reg_256.vhd | X | X |   | X | X | X | X | X | X | X |                     |

#### 4.9 A Switch de-bouncer

Here is a logic module that will help in de-bouncing a switch. It has two generics that affect how it works:

min\_pw (an integer) number of clocks wide a pulse needs to be to change states hold (an integer) number of clocks to hold the output level

The check for minimum pulse width can help in filtering out noise that may be on the line, while the hold time should wide enough to allow any ringing (or switch bouncing) to settle out. It is setup to work the same way on signals that are active high as active low.

| I/O |   | Function                        |

|-----|---|---------------------------------|

| clk | I | Clock, rising edge is used      |

| rst | I | Asynchronous Reset, active high |

| D   | I | data in                         |

| Q   | О | De-bounced output               |

File name: gh\_debounce.vhd

### 4.10 An Edge Detector for changing Clock Domains

This part is designed so that the edges of a pulse generated in one clock domain, can be sampled in a different clock domain. Although either clock may have a higher frequency than the other, if the output clock has the higher frequency, the gh\_edge\_detector.vhd will use fewer resources.

**Note:** the period of the input D (rising to rising edge, or falling edge to falling edge) should be at lest three times the slower clock frequency for proper operation. Also, a narrow input pulse may cause both outputs to be active at the same time (the greater the difference in clock frequencies, the higher probability this will happen).

| I/O  |   | Function                                      |

|------|---|-----------------------------------------------|

| iclk | I | Input clock for sampling D                    |

| oclk | I | Clock which will be synchronous with          |

|      |   | outputs re and fe                             |

| rst  | I | Asynchronous Reset, active high               |

| D    | I | Input data bit, if not synchronous with iclk, |

|      |   | should be as lest as wide as an iclk period + |

|      |   | (a register) setup time + hold time           |

| re   | О | Rising edge detected                          |

| fe   | 0 | Falling edge detected                         |

File name: gh\_edge\_det\_XCD.vhd

### 4.11 Gray code converters

In a standard binary sequence, multiple bits may change at the same time (for example, in going from 2 to 3, two bits change at the same time). In contrast, Gray codes have only one bit change at a time.

Gray code counters offer a major advantage in Asynchronous FIFO design. For example, when the write count value is sampled by the read clock (for generating the EMPTY flag), with only one bit changing at a time, the worst that will happen is that the EMPTY flag will be high for one clock period longer than "ideal."

The two converters use combinational logic, and the generic "size" to set the data width.

File Names: gh\_binary2gray.vhd gh\_gray2binary.vhd

Reference

1. Clive "Max" Maxfield, *Bebop to the Boolean Boogie, Second Edition*, Newnes 2003 – page 361

#### 4.12 Pulse Width/Time Measurement

This module will measure the pulse width, and provide a relative time of arrival (TOA), for a series of pulses. The "current" time is also available. There are separate generics for the pulse width and time measurements.

For best operation,  $T_{size} >= pw_{size}$

| I/O                       |   | Function                                      |

|---------------------------|---|-----------------------------------------------|

| clk                       | I | Input clock for sampling D                    |

| rst                       | I | Asynchronous Reset, active high               |

| Pulse(pw_size-1 DOWNTO 0) | I | Pulse to measure                              |

| NEW_PULSE                 | О | New Pulse detected, PW & TOA valid            |

| PW                        | О | Pulse Width measurement                       |

| TOA(T_size-1 DOWNTO 0)    | О | Time of Arrival for pulse, relative to TTIME  |

| TTIME(T_size-1 DOWNTO 0)  | O | Free running counter to provide relative time |

| ACTIVE                    | О | goes high with a pulse input, goes low when   |

|                           |   | there is no new pulse in the wrap around time |

|                           |   | of the free running counter.                  |

File name: gh\_pw\_wTOA.vhd

#### 4.13 Lower Rate Clock Mirror

This module, in systems that have a 1x clock and a 2x clock, will generate a logic mirror of the 1x clock. Works with the Data DeMux and Data Mux modules.

In systems that use multiple, related clocks (multi-rate systems), the higher rate clock may need to sample the lower rate clock so that their phase relationship is known. When using FPGA's, it is highly recommended to avoid using clocks as anything other than a clock input for a register.

| I/O    |   | Function                              |

|--------|---|---------------------------------------|

| clk_2x | I | Clock, rising edge used - higher rate |

| clk_1x | I | Clock, rising edge used – lower rate  |

| rst    | I | Asynchronous Reset, active high       |

| mirror | O | Logical mirror of 1x clock            |

File name: gh\_clk\_mirror.vhd

#### 4.14 Data DeMux 1 to 2

This module will split a stream of data into two – at half the data rate of the input stream.

| I/O                 |   | Function                                               |

|---------------------|---|--------------------------------------------------------|

| clk_2x              | I | Clock, rising edge used - higher rate                  |

| clk_1x              | I | Clock, rising edge used – lower rate                   |

| rst                 | I | Asynchronous Reset, active high                        |

| mux_cnt             | I | Controls demux timing (use mirror output               |

|                     |   | of gh_clk_mirror.vhd module)                           |

| D(size-1 downto 0)  | I | Input data, sync to 2x clock                           |

| Qa(size-1 downto 0) | О | Output data, sync to 1x clock (1 <sup>st</sup> sample) |

| Qb(size-1 downto 0) | О | Output data, sync to 1x clock (2 <sup>nd</sup> sample) |

File name: gh\_de\_mux.vhd

#### 4.15 Data Mux 2 to 1

This module will split a combine of two data streams into one – at twice the data rate of the input stream. It does not use the lower rate clock.

| I/O                 |   | Function                                               |

|---------------------|---|--------------------------------------------------------|

| clk_2x              | I | Clock, rising edge used - higher rate                  |

| rst                 | I | Asynchronous Reset, active high                        |

| mux_cnt             | I | Controls mux timing (use mirror output of              |

|                     |   | gh_clk_mirror.vhd module)                              |

| Da(size-1 downto 0) | I | Input data, sync to 1x clock (1 <sup>st</sup> sample)  |

| Da(size-1 downto 0) | I | Output data, sync to 1x clock (2 <sup>nd</sup> sample) |

| Q(size-1 downto 0)  | О | Output data, sync to 2x clock                          |

File name: gh\_mux.vhd

# 4.16 Four Byte GPIO

The four byte GPIO module is a modification of the four byte control register (see paragraph 4.8) to include tri-state IO.

This Module allows flexible chip IO – the direction is controllable on a byte (8 bits) basis. Each bit (for the bytes that are driving) can be controlled on an individually.

| I/O               |    | Function                          |

|-------------------|----|-----------------------------------|

| clk               | I  | Clock, rising edge is used        |

| rst               | I  | Asynchronous Reset, active high   |

| CSn               | I  | Chip Select, active low           |

| WE                | I  | Write strobe                      |

| DRIVE(3 downto 0) | I  | Per byte direction control        |

|                   |    | (1 = drive, 0 = receive)          |

| BE(3 downto 0)    | I  | Byte enable bits                  |

| MODE(1 downto 0)  | I  | Mode bits                         |

|                   |    | (see paragraph 4.8 for operation) |

| D (31 downto 0)   | I  | Data input                        |

| RD(31 downto 0)   | О  | Read back Data                    |

| Q(31 downto 0)    | IO | Input/Output data                 |

File name: gh\_4byte\_gpio\_32.vhd

#### 4.17 Burst Generator

The Burst Generator it is a simple application of three counters. A fourth counter can be used to create the trigger signal, making the bust periodic (an exercise left to the user).

| I/O                                  |   | Function                                          |

|--------------------------------------|---|---------------------------------------------------|

| clk                                  | I | Clock, rising edge is used                        |

| rst                                  | I | Asynchronous Reset, active high                   |

| Period (size_Period-1 DOWNTO 0)      | I | The number of clocks between pulses               |

| Pulse_Width (size_Period-1 DOWNTO 0) | I | The Pulse width, in clock periods                 |

| P_Count (size_pcount-1 downto 0)     | I | The number of pulses in a burst                   |

| trigger                              | I | Starts burst, active high                         |

| Pulse                                | О | The Output Pulse                                  |

| busy                                 | О | Active high between 1 <sup>st</sup> pulse through |

|                                      |   | the end of the last pulse                         |

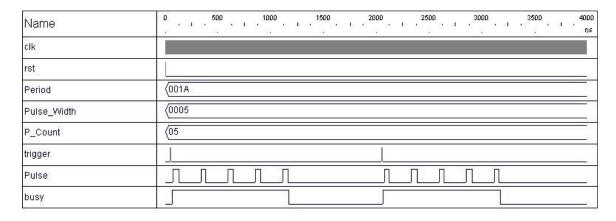

Below is a simulation of the gh\_Burst\_Generator.vhd file:

# 4.18 Watch Dog Timers

A Watch Dog Timer is a free running counter- which, if the system fails to reset before it times out, will (typically) re-start a system (reset, re-boot, or interrupt). A generic, ticks, sets the number of clock ticks for the time out period in the fixed length version. The programmable version uses a generic size that sets the maximum time out.

| I/O                      |   | Function                               |

|--------------------------|---|----------------------------------------|

| clk                      | I | Clock, rising edge is used             |

| rst                      | I | Asynchronous Reset, active high        |

| T_en                     | I | Timer enable                           |

| t                        | I | Toggle input to reset counter          |

| t_time (size-1 downto 0) | I | Timer time out clocks                  |

| Q                        | О | High after time out period has elapsed |

| Parts                   | clk | rst | T_en | t | t_time | Q | Comments |

|-------------------------|-----|-----|------|---|--------|---|----------|

| gh_wdt.vhd              | X   | X   |      | X | X      | X |          |

| gh_wdt_programmable.vhd | X   | X   | X    |   | X      | X |          |

#### 4.19 Pulse Width Modulator

A pulse width modulator is one way of converting digital data to analog. The output is a series of pulses with the pulse widths (or duty cycle) that are proportional to the input digital value.

| I/O                   |   | Function                        |

|-----------------------|---|---------------------------------|

| clk                   | I | Clock, rising edge is used      |

| rst                   | I | Asynchronous Reset, active high |

| d_format              | I | Input Data format $0 = 2$ 's    |

|                       |   | complement, 1 = offset binary   |

| DATA(size-1 downto 0) | I | Input data                      |

| PWMo                  | О | Pulse Width Modulator output    |

| ND                    | О | New Data Sample strobe          |

The minimum recommended clock frequency for the pulse width modulator module is:

$$F_{PWM} = 2 \times F_{range} \times R$$

$F_{PWM}$  = PWM module clock frequency

$F_{range}$  = maximum frequency of input data stream

R = resolution (typically a multiple of 2N, where N is the number of bits)

| Parts      | c | r | d_format | D | PWMo | N | Comments |

|------------|---|---|----------|---|------|---|----------|

|            | 1 | s |          | A |      | D |          |

|            | k | t |          | T |      |   |          |

|            |   |   |          | A |      |   |          |

| gh_PWM.vhd | X | X | X        | X | X    | X |          |

|            |   |   |          |   |      |   |          |

Pulse width modulators can be used to control the intensity of LED's, audio play back, and motor control. The reference (listed below) is highly recommended reading.

### Reference:

1. Rafael Camarota, *How to control analog output from a CPLD using a pulse width modulator*, Programmable Logic Design Line, February 24, 2009 <a href="http://www.industrialcontroldesignline.com/howto/motorcontrol/214502805">http://www.industrialcontroldesignline.com/howto/motorcontrol/214502805</a>

# 5 Math Functions

#### 5.1 Accumulator

The Accumulator has the generic "size" which sets the number of bits to be accumulated. When CE is high, the value of D is added to the value of Q. No provision is made for overflow or underflow.

| I/O                 |   | Function                        |

|---------------------|---|---------------------------------|

| CLK                 | I | Clock, rising edge is used      |

| rst                 | I | Asynchronous Reset, active high |

| srst                | I | Synchronous Reset, active high  |

| LOAD                | I | Load data w/o accumulate        |

| CE                  | I | Clock enable, active high       |

| D (size-1 downto 0) | I | Input Data                      |

| Q(size-1 downto 0)  | Q | Shifted bits out                |

| Parts         | С | r | S | L | C | D | Q | Comments                       |

|---------------|---|---|---|---|---|---|---|--------------------------------|

|               | L | S | r | O | Е |   |   |                                |

|               | K | t | S | A |   |   |   |                                |

|               |   |   | t | D |   |   |   |                                |

| gh_acc.vhd    | X | X | X |   | X | X | X |                                |

| gh_acc_ld.vhd | X | X |   | X | X | X | X | Loads Data with out accumulate |

|               |   |   |   |   |   |   |   | (has priority over CE)         |

# 5.2 Multipliers

The multipliers will be recognized, at lest by the Xilinx ISE synthesis tool, and placed into one of the multiplier blocks. The two clock delay Multipliers are expected to operate at higher clock rates than the single clock delay multipliers.

| I/O             | Function |                                           |  |  |

|-----------------|----------|-------------------------------------------|--|--|

| clk             | I        | Clocks, rising edge is used for A/B ports |  |  |

| DA(15 downto 0) | I        | A input data port                         |  |  |

| DB(15 downto 0) | I        | B input data port                         |  |  |

| Q(15 downto 0)  | О        | Output data                               |  |  |

| Parts              | CLK | DA/DB | Q | Comments                              |

|--------------------|-----|-------|---|---------------------------------------|

| gh_mult_g16.vhd    | X   | X     | X | Has two clock delay, signed data      |

| gh_mult_g18.vhd    | X   | X     | X | Has two clock delay, signed data      |

| gh_mult_g18_sc.vhd | X   | X     | X | Has a single clock delay, signed data |

# 5.3 Multipliers using Generics

The multipliers will be recognized, at lest by the Xilinx ISE synthesis tool, and placed into one of the multiplier blocks. These use generics for the size of the input ports – the output port size is the sum of the size of the two input ports.

| I/O                                      |   | Function                            |

|------------------------------------------|---|-------------------------------------|

| clk                                      | I | Clocks, rising edge is used for A/B |

|                                          |   | ports                               |

| I(size-1 downto 0)                       | I | signed input data                   |

| Scale(ssize-1 downto 0)                  | I | unsigned input data                 |

| A(asize-1 downto 0), B(bsize-1 downto 0) | I | input data                          |

| Q                                        | О | Output data                         |

| Parts               | CLK | I | Scale | A/B | Q | Comments            |

|---------------------|-----|---|-------|-----|---|---------------------|

| gh_scaling_mult.vhd | X   | X | X     |     | X | Has one clock delay |

| gh_mult_gs.vhd      | X   |   |       | X   | X | Has one clock delay |

| gh_mult_gus_sc.vhd  | X   |   |       | X   | X | Has one clock delay |

# 5.4 Multiplier Accumulator

The Multiplier Accumulator is a basic building block used in digital filters.

| I/O             |   | Function                                  |

|-----------------|---|-------------------------------------------|

| clk             | I | Clocks, rising edge is used for A/B ports |

| rst             | I | Asynchronous Reset, active high           |

| srst            | I | Synchronous Reset, active high            |

| LOAD            | I | Load data w/o accumulate                  |

| ce              | I | Clock enable                              |

| DA(15 downto 0) | I | A input data port                         |

| DB(15 downto 0) | I | B input data port                         |

| Q(15 downto 0)  | О | Output data                               |

| Parts               | С | r | s | L | С | D | Q | Comments                         |

|---------------------|---|---|---|---|---|---|---|----------------------------------|

|                     | L | s | r | О | Е | A |   |                                  |

|                     | K | t | s | A |   | / |   |                                  |

|                     |   |   | t | D |   | D |   |                                  |

|                     |   |   |   |   |   | В |   |                                  |

| gh_MAC_16bit.vhd    | X | X | X |   | X | X | X |                                  |

| gh_MAC_16bit_ld.vhd | X | X |   | X | X | X | X | Loads Data with out accumulate   |

|                     |   |   |   |   |   |   |   | (has priority over CE)           |

| gh_MAC_ld.vhd       | X | X |   | X | X | X | X | includes generics to set size    |

|                     |   |   |   |   |   |   |   | (separate for DA/DB) and for bit |

|                     |   |   |   |   |   |   |   | expansion to avoid accumulator   |

|                     |   |   |   |   |   |   |   | overflow                         |

### 5.5 Random Number Generation

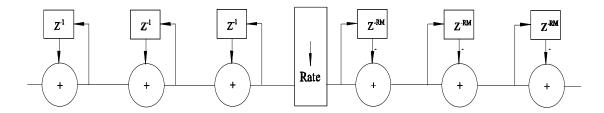

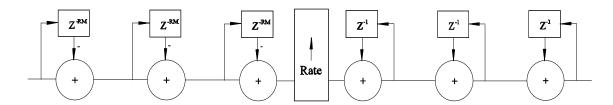

There are a number of was to generate pseudo random numbers in hardware. The LFSR may be the one most used, but a CASR is also included.

# 5.5.1 The Linear Feedback Shift Register (LFSR)

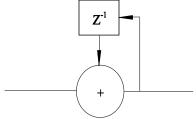

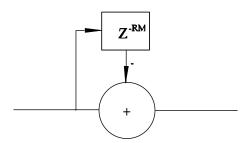

The Linear Feedback Shift Register (LFSR) is used for generating pseudo random numbers. These use the Fibonacci implementation, where the output from some of the registers are exclusive ORed together and feedback to the input of the beginning of the shift register.

| I/O                         |   | Function                        |

|-----------------------------|---|---------------------------------|

| CLK                         | I | Clock, rising edge is used      |

| rst                         | I | Asynchronous Reset, active high |

| LOAD                        | I | Load the seed value             |

| seed(size of LFSR downto 1) | I | LFSR seed (initial value)       |

| Q(size of LFSR downto 1)    | О | output                          |

| Parts               | С | r | L | S | Q | Approximant time pattern runs before repeating                   |

|---------------------|---|---|---|---|---|------------------------------------------------------------------|

|                     | L | s | O | e |   | (when the clock rate is 100MHz)                                  |

|                     | K | t | A | e |   |                                                                  |

|                     |   |   | D | d |   |                                                                  |

| gh_lfsr_24.vhd      | X | X |   |   | X | 167.8ms                                                          |

| gh_lfsr_36.vhd      | X | X |   |   | X | 11.45 minutes                                                    |

| gh_lfsr_48.vhd      | X | X |   |   | X | 32.578 days                                                      |

| gh_lfsr_64.vhd      | X | X |   |   | X | 5,849 years                                                      |

| gh_lfsr_gfb4.vhd    | X | X |   |   | X | Has generics for size (first feedback tap) and three             |

|                     |   |   |   |   |   | more feedback taps (these taps may be set to zero                |

|                     |   |   |   |   |   | to have tap ignored). If Taps are picked that give a             |

|                     |   |   |   |   |   | maximum sequence length: $(2^{\text{size}} - 1) * 10 \text{ ns}$ |

| gh_lfsr_gfb4_ld.vhd | X | X | X | X | X | Adds Load / Seed inputs                                          |

| Bits | Taps       | Bits | Taps     | Bits | Taps        | Bits | Taps        |

|------|------------|------|----------|------|-------------|------|-------------|

| 9    | 9,5        | 19   | 19,6,2,1 | 32   | 32,22,2,1   | 67   | 67,66,58,57 |

| 10   | 10,7       | 21   | 21,19    | 33   | 33,20       | 72   | 72,66,25,19 |

| 11   | 11,9       | 23   | 23,18    | 38   | 38,6,5,1    | 77   | 77,76,47,46 |

| 12   | 12,6,4,1   | 25   | 25,22    | 43   | 43,42,38,37 | 81   | 81,77       |

| 13   | 13,4,3,1   | 26   | 26,6,2,1 | 47   | 47,42       | 89   | 89,51       |

| 15   | 15,14      | 28   | 28,25    | 51   | 51,50,36,35 | 96   | 96,94,49,47 |

| 16   | 16,15,13,4 | 29   | 29,27    | 55   | 55,31       | 97   | 97,91       |

| 17   | 17,14      | 30   | 30,6,4,1 | 57   | 57,50       | 99   | 99,97,54,52 |

| 18   | 18,11      | 31   | 31,28    | 61   | 61,60,46,45 | 100  | 100,63      |

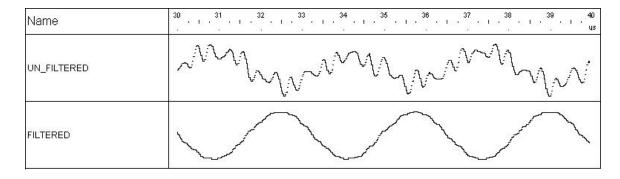

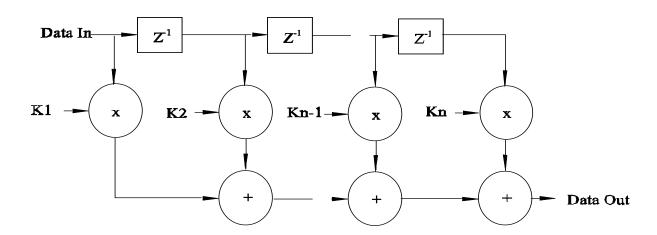

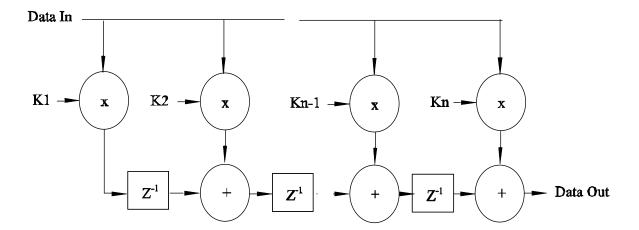

A selection of different length LFSR feedback taps. For those who are interested in LFSR's of different lengths should consult one of the references listed.