# openMSP430

Author: Olivier GIRARD olgirard@gmail.com

Rev. 1.15 May 19, 2015

# **Revision History**

| Rev. | Date                             | Author | Description                                           |

|------|----------------------------------|--------|-------------------------------------------------------|

| 1.0  | August 4th, 2009                 | GIRARD | First version.                                        |

| 1.1  | August 30th, 2009                | GIRARD | Replaced "openMSP430.inc" with                        |

|      |                                  |        | "openMSP430_defines.v"                                |

| 1.2  | December 27 <sup>th</sup> , 2009 | GIRARD | - Update file and directory description for hte FPGA  |

|      |                                  |        | projects (in particular, add the Altera project).     |

|      |                                  |        | - Diverse minor updates.                              |

| 1.3  | December 29 <sup>th</sup> , 2009 | GIRARD | - Renamed the "rom_*" ports to "pmem_*".              |

|      |                                  |        | - Renamed the "ram_*" ports to "dmem_*".              |

|      |                                  |        | - Renamed the "ROM_AWIDTH" Verilog define to          |

|      |                                  |        | "PMEM_AWIDTH".                                        |

|      |                                  |        | - Renamed the "RAM_AWIDTH" Verilog define to          |

|      |                                  |        | "DMEM_AWIDTH".                                        |

|      |                                  |        | - Prefixed all the verilog sub-modules of the         |

|      |                                  |        | openMSP430 core with "omsp_".                         |

|      |                                  |        | - Diverse minor updates                               |

| 1.4  | January 12 <sup>th</sup> , 2010  | GIRARD | - Added the "Integration and Connectivity" section.   |

| 1.5  | March 7 <sup>th</sup> , 2010     | GIRARD | - Add Hardware multiplier info.                       |

|      |                                  |        | - Added the "Area and Speed Analysis" section.        |

| 1.6  | August 1st, 2010                 | GIRARD | - Update core configuration section.                  |

|      |                                  |        | - Expand the CPU selection table for msp430-gcc.      |

| 1.7  | August 18th, 2010                | GIRARD | - Update CPU_ID description in the serial debug       |

|      |                                  |        | interface chapter                                     |

| 1.8  | March 1 <sup>st</sup> , 2011     | GIRARD | - Update openmsp430-minidebug tool section.           |

|      |                                  |        | - Add. Actel ProASIC3 example to the file and         |

|      |                                  |        | directory description section.                        |

| 1.9  | June 6 <sup>th</sup> , 2011      | GIRARD | - General update to reflect the latest RTL            |

|      |                                  |        | implementation (cpu_en/dbg_en ports, configurable     |

|      |                                  |        | peripheral address space, software development tools  |

|      |                                  |        | update)                                               |

| 1.10 | March 20 <sup>th</sup> , 2012    | GIRARD | - Global update reflecting the ASIC support and       |

|      |                                  |        | corresponding configuration options.                  |

| 1.11 | July 15 <sup>th</sup> , 2012     | GIRARD | - Add benchmark results                               |

|      | 4                                |        | - Add custom memory size configuration                |

| 1.12 | November 27 <sup>th</sup> , 2012 | GIRARD | - Global update reflecting the I2C based serial debug |

|      |                                  |        | interface update.                                     |

| 1.13 | February 24 <sup>th</sup> , 2013 | GIRARD | - Minor update to reflect new ASIC_CLOCKING           |

|      |                                  |        | option.                                               |

| 1.14 | December 17 <sup>th</sup> , 2013 | GIRARD | - Update with number of IRQs configuration option     |

|      |                                  |        | - Move peripherals documentation to a dedicated       |

|      |                                  |        | chapter.                                              |

| 1.15 | May 19 <sup>th</sup> , 2015      | GIRARD | - Overall update to document the DMA interface.       |

# **Contents**

| 1. OVERVIEW                        | <u>1</u>  |

|------------------------------------|-----------|

| 2. CORE                            | <u>4</u>  |

| 3. PERIPHERALS                     | <u>22</u> |

| 4. DMA INTERFACE                   | <u>33</u> |

| 5. SERIAL DEBUG INTERFACE          | <u>43</u> |

| 6. INTEGRATION AND CONNECTIVITY    | <u>59</u> |

| 7. ASIC IMPLEMENTATION             | <u>77</u> |

| 8. AREA AND SPEED ANALYSIS         | <u>94</u> |

| 9. SOFTWARE DEVELOPMENT TOOLS      | <u>98</u> |

| 10. FILE AND DIRECTORY DESCRIPTION | 111       |

# **Overview**

% 8 € % 16 €

# Introduction

The openMSP430 is a synthesizable 16bit microcontroller core written in Verilog. It is compatible with Texas Instruments' MSP430 microcontroller family and can execute the code generated by an MSP430 toolchain in a near cycle accurate way.

The core comes with some peripherals (16x16 Hardware Multiplier, Watchdog, GPIO, TimerA, generic templates), with a DMA interface, and most notably with a two-wire **Serial Debug Interface** supporting the <u>MSPGCC</u> GNU Debugger (GDB) for in-system software debugging.

While being fully FPGA friendly, this design is also particularly suited for ASIC implementations (typically mixed signal ICs with strong area and low-power requirements).

In a nutshell, the openMSP430 brings with it:

- Low area (8k-Gates), without hidden extra infrastructure overhead (memory backbone, IRQ controller and watchdog timer are already included).

- Excellent code density.

- Good performances.

- Build-in power and clock management options.

- Multiple times Silicon Proven.

## **Download**

## Design

The complete tar archive of the project can be downloaded <u>here</u> (OpenCores account required).

The following SVN command can be run from a console (or <u>GUI</u>):

svn export http://opencores.org/ocsvn/openmsp430/openmsp430/trunk/ openmsp430

## Changelog

- The <u>Core's ChangeLog</u> lists the CPU updates

- The <u>Tools' ChangeLog</u> lists the Software development tools updates.

- Subscribe to the following <u>RSS</u> feed to keep yourself informed about ALL updates.

### **Documentation**

Being fully compatible with the original MSP430 architecture, TI's official documentation is applicable: <u>SLAU49F.PDF</u>

In addition, the openMSP430 online documentation is also available in pdf.

# **Features & Limitations**

### **Features**

- Core:

- Full instruction set support.

- Interrupts: IRQs (x14, x30 or x62), NMI (x1).

- Low Power Modes (LPMx).

- Configurable memory size for both program and data.

- Scalable peripheral address space.

- DMA interface.

- Two-wire Serial Debug Interface (I<sup>2</sup>C or UART based) with GDB support (Nexus class 3, w/o trace).

- FPGA friendly (option for single clock domain, no clock gate).

- ASIC friendly (options for full power & clock management support).

- Small size (Xilinx: 1650 LUTs / Altera: 1550 LEs / ASIC: 8k gates).

- · Peripherals:

- 16x16 Hardware Multiplier.

- Basic Clock Module.

- Watchdog.

- Timer A (FPGA only).

- GPIO (FPGA only).

- Templates for 8 and 16 bit peripherals.

### Limitations

- Core:

- Instructions can't be executed from the data memory.

# Links

Development has been performed using the following freely available (excellent) tools:

- <u>Icarus Verilog</u>: Verilog simulator.

- GTKWave Analyzer: Waveform viewer.

- MSPGCC: GCC toolchain for the Texas Instruments MSP430 MCUs.

- <u>ISE WebPACK</u>: Xilinx's free FPGA synthesis tool.

#### A few MSP430 links:

- Wikipedia: MSP430

- TI: MSP430x1xx Family User's Guide

- TI: MSP430 Competitive Benchmarking

- TI: a list of available MSP430 Open Source projects out there on the web today.

# Legal information

MSP430 is a trademark of Texas Instruments, Inc. This project is not affiliated in any way with Texas Instruments. All other product names are trademarks or registered trademarks of their respective owners.

# 2.

# Core

### **Table of content**

- 1. Introduction

- <u>2. Core</u>

- <u>2.1 Design structure</u>

- 2.2 Limitations

- 2.3 Configuration

- 2.3.1 Basic System Configuration

- 2.3.2 Advanced System Configuration

- 2.3.3 Expert System Configuration

- 2.3.4 Parameters For Multi-Core Systems

- 2.4 Memory mapping

- 2.5 Interrupt mapping

- 2.6 Pinout

- 2.7 Instruction Cycles and Lengths

- 2.8 Serial Debug Interface

- 2.9 Benchmark results

- 2.9.1 Dhrystone

- 2.9.2 CoreMark

# 1. Introduction

The openMSP430 is a 16-bit microcontroller core compatible with <u>TI's MSP430 family</u> (note that the extended version of the architecture, the MSP430X, isn't supported by this IP). It is based on a Von Neumann architecture, with a single address space for instructions and data.

Depending on the selected configuration, this design can either be:

- **FPGA friendly**: the core doesn't contain any clock gate and has only a single clock domain. As a consequence, in this mode, the *Basic Clock Module* peripheral has a few limitations.

- **ASIC friendly**: the core contains up to all clock management options (clock muxes & low-power modes, fine grained clock gating, ...) and is also ready for scan insertion. In this mode, the *Basic Clock Module* offers all features listed in the official documentation.

It is to be noted that this IP doesn't contain the instruction and data memory blocks internally (these are technology dependent hard macros which are connected to the IP during chip integration). However the core is fully configurable in regard to the supported RAM and/or ROM sizes.

# 2. Core

# 2.1 Design structure

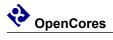

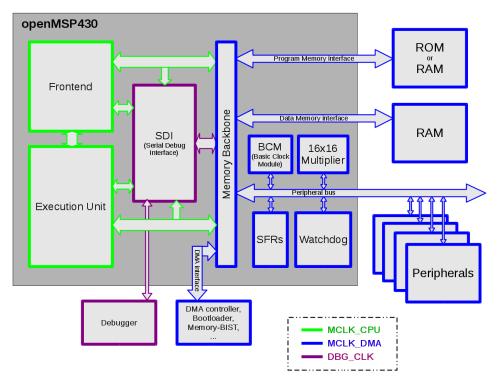

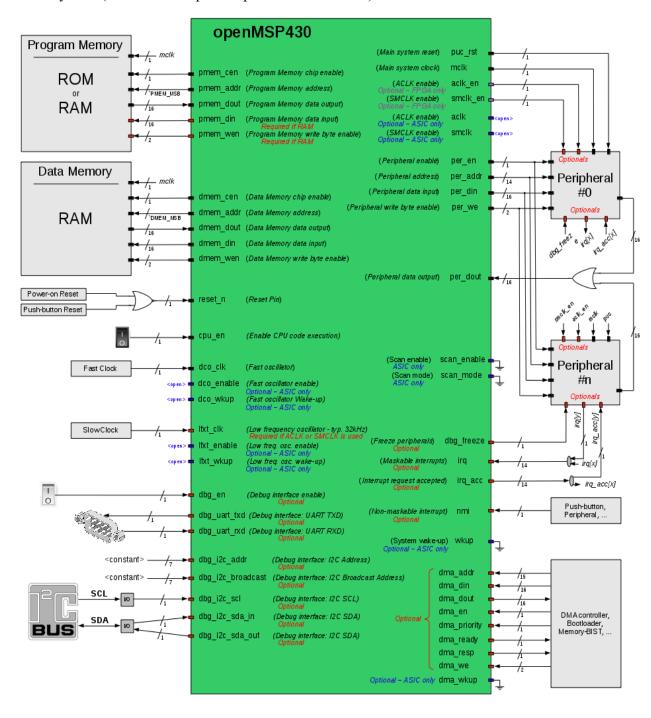

The following diagram shows the openMSP430 design structure:

- **Frontend**: This module performs the instruction Fetch and Decode tasks. It also contains the execution state machine.

- **Execution unit**: Containing the ALU and the register file, this module executes the current decoded instruction according to the execution state.

- **Serial Debug Interface**: Contains all the required logic for a Nexus class 3 debugging unit (without trace). Communication with the host is done with a standard two-wire interface following either the UART 8N1 or I<sup>2</sup>C serial protocol.

- **Memory backbone**: This block performs a simple arbitration between the frontend, execution-unit, DMA and Serial-Debug interfaces for program, data and peripheral memory accesses.

- **Basic Clock Module**: Generates MCLK, ACLK, SMCLK and manage the low power modes.

- SFRs: The Special Function Registers block contains diverse configuration registers (NMI, Watchdog, ...).

- Watchdog: Although it is a peripheral, the watchdog is directly included in the core because of its tight links with the NMI interrupts and the PUC reset generation.

- **16x16 Multiplier**: The hardware multiplier peripheral is transparently supported by the GCC compiler and is therefore located in the core. It can be included or excluded at will through a Verilog define.

## 2.2 Limitations

The known core limitations are the following:

• Instructions can't be executed from the data memory.

## 2.3 Configuration

It is possible to configure the openMSP430 core through the *openMSP430\_defines.v* file located in the *rtl* directory (see <u>file and directory description</u>).

In this section, three sets of adjustable user parameters are discussed in order to customize the core. A fourth set is available for ASIC specific options and will be discussed in the <u>ASIC implementation</u> section.

### 2.3.1 Basic System Configuration

The basic system can be adjusted with the following set of defines in order to match the target system requirements.

```

//BASIC SYSTEM CONFIGURATION

// Note: the sum of program, data and peripheral memory spaces must not

// exceed 64 kB

// Program Memory Size:

Uncomment the required memory size

//`define PMEM SIZE CUSTOM

//`define PMEM_SIZE_59_KB

//`define PMEM_SIZE_55_KB

//`define PMEM_SIZE_54_KB

//`define PMEM SIZE 51 KB

//`define PMEM_SIZE_48_KB

//`define PMEM SIZE 41 KB

//`define PMEM SIZE 32 KB

//`define PMEM SIZE 24 KB

```

```

//`define PMEM_SIZE_16_KB

//`define PMEM SIZE 12 KB

//`define PMEM_SIZE_8_KB

//`define PMEM_SIZE_4_KB

`define PMEM SIZE 2 KB

//`define PMEM_SIZE_1_KB

// Data Memory Size:

Uncomment the required memory size

//`define DMEM SIZE CUSTOM

//`define DMEM SIZE 32 KB

//`define DMEM SIZE 24 KB

//`define DMEM SIZE 16 KB

//`define DMEM SIZE 10 KB

//`define DMEM_SIZE_8_KB

//`define DMEM_SIZE_5_KB

//`define DMEM_SIZE_4_KB

//`define DMEM_SIZE_2p5_KB

//`define DMEM SIZE 2 KB

//`define DMEM_SIZE_1_KB

//`define DMEM SIZE 512 B

//`define DMEM_SIZE_256_B

`define DMEM SIZE 128 B

// Include/Exclude Hardware Multiplier

`define MULTIPLIER

// Include/Exclude Serial Debug interface

`define DBG EN

```

The only design considerations at this stage are:

- Make sure that the program and data memories have the correct size :-P

- The sum of program, data and peripheral memory space MUST NOT exceed 64kB.

**Note:** when selected, full custom memory sizes can be specified in the "Expert System Configuration" section.

### 2.3.2 Advanced System Configuration

In this section, some additional features are available in order to match the needs of more experienced users.

```

// interface.

// (see CPU_ID.USER_VERSION field in the documentation)

//-----

`define USER_VERSION 5'b00000

//-----

// Include/Exclude Watchdog timer

//-----

// When excluded, the following functionality will be

// lost:

//

- Watchog (both interval and watchdog modes)

//

- NMI interrupt edge selection

//

- Possibility to generate a software PUC reset

//-----

`define WATCHDOG

//-----

// Include/Exclude DMA interface support

//----

//`define DMA IF EN

//-----

// Include/Exclude Non-Maskable-Interrupt support

`define NMI

//----

// Number of available IRQs

//-----

// Indicates the number of interrupt vectors supported

// (16 ,32 or 64).

//----

`define IRQ 16

//`define IRQ 32

//`define IRQ_64

//-----

// Input synchronizers

//-----

// In some cases, the asynchronous input ports might

// already be synchronized externally.

// If an extensive CDC design review showed that this

// is really the case, the individual synchronizers

// can be disabled with the following defines.

//

// Notes:

//

- all three signals are all sampled in the MCLK domain

//

//

- the dbg_en signal reset the debug interface

//

when 0. Therefore make sure it is glitch free.

//

//-----

`define SYNC NMI

//`define SYNC_CPU_EN

//`define SYNC_DBG_EN

//-----

// Peripheral Memory Space:

```

```

// The original MSP430 architecture map the peripherals

// from 0x0000 to 0x01FF (i.e. 512B of the memory space).

// The following defines allow you to expand this space

// up to 32 kB (i.e. from 0x0000 to 0x7fff).

// As a consequence, the data memory mapping will be

// shifted up and a custom linker script will therefore

// be required by the GCC compiler.

//`define PER SIZE CUSTOM

//`define PER SIZE 32 KB

//`define PER SIZE 16 KB

//`define PER SIZE 8 KB

//`define PER SIZE 4 KB

//`define PER SIZE 2 KB

//`define PER SIZE 1 KB

`define PER SIZE 512 B

// Defines the debugger CPU_CTL.RST_BRK_EN reset value

// (CPU break on PUC reset)

// When defined, the CPU will automatically break after

// a PUC occurrence by default. This is typically useful

// when the program memory can only be initialized through

// the serial debug interface.

//-----

`define DBG_RST_BRK_EN

```

Design consideration at this stage are:

- Setting a peripheral memory space to something else than 512B will shift the data memory mapping up, which in turn will require the use of a custom linker script. If you don't know what a linker script is and if you don't want to know what it is, you should probably not modify this section.

- The sum of program, data and peripheral memory space MUST NOT exceed 64kB.

**Note:** when selected, full custom peripheral memory space can be specified in the "Expert System Configuration" section.

### 2.3.3 Expert System Configuration

In this section, you will find configuration options which will be relevant for roughly 0.1% of the users (according to a highly reliable market analysis;-)).

```

// IMPORTANT NOTE: Please update following configuration options ONLY if

//

you have a good reason to do so... and if you know what

//

you are doing :-P

//

//-----

// Select serial debug interface protocol

//-----

DBG UART -> Enable UART (8N1) debug interface

//

DBG_I2C -> Enable I2C debug interface

//

//-----

`define DBG UART

//`define DBG I2C

//----

// Enable the I2C broadcast address

//-----

// For multicore systems, a common I2C broadcast address

// can be given to all oMSP cores in order to

// synchronously RESET, START, STOP, or STEP all CPUs

// at once with a single I2C command.

// If you have a single openMSP430 in your system,

// this option can stay commented-out.

//`define DBG I2C BROADCAST

//-----

// Number of hardware breakpoint units (each unit contains

// two hardware address breakpoints):

// - DBG HWBRK 0 -> Include hardware breakpoints unit 0

// - DBG HWBRK 1 -> Include hardware breakpoints unit 1

// - DBG_HWBRK_2 -> Include hardware breakpoints unit 2

// - DBG_HWBRK_3 -> Include hardware breakpoints unit 3

//-----

// Please keep in mind that hardware breakpoints only

// make sense whenever the program memory is not an SRAM

// (i.e. Flash/OTP/ROM/...) or when you are interested

// in data breakpoints (btw. not supported by GDB).

//----

//`define DBG_HWBRK_0

//`define DBG HWBRK 1

//`define DBG HWBRK 2

//`define DBG HWBRK 3

//-----

// Enable/Disable the hardware breakpoint RANGE mode

// When enabled this feature allows the hardware breakpoint

// units to stop the cpu whenever an instruction or data

// access lays within an address range.

// Note that this feature is not supported by GDB.

//`define DBG_HWBRK_RANGE

//-----

// Custom Program/Data and Peripheral Memory Spaces

```

```

// The following values are valid only if the

// corresponding * SIZE CUSTOM defines are uncommented:

// - *_{SIZE} : size of the section in bytes.

// - *_AWIDTH : address port width, this value must allow

to address all WORDS of the section

//

(i.e. the *_{SIZE} divided by 2)

//-----

// Custom Program memory (enabled with PMEM_SIZE_CUSTOM)

`define PMEM CUSTOM AWIDTH

10

`define PMEM_CUSTOM_SIZE

2048

// Custom Data memory (enabled with DMEM SIZE CUSTOM)

`define DMEM_CUSTOM_AWIDTH 6

`define DMEM CUSTOM SIZE

128

// Custom Peripheral memory (enabled with PER_SIZE_CUSTOM)

define PER_CUSTOM_AWIDTH 8

`define PER_CUSTOM_SIZE

512

//-----

// ASIC version

// When uncommented, this define will enable the

// ASIC system configuration section (see below) and

// will activate scan support for production test.

// WARNING: if you target an FPGA, leave this define

commented.

//`define ASIC

```

Design consideration at this stage are:

• This is the expert section... so you know what your are doing, right ;-)

All remaining defines located after the ASIC section in the *openMSP430\_defines.v* file are system constants and MUST NOT be edited.

### 2.3.4 Parameters For Multi-Core Systems

In addition to the define file, two Verilog parmaeters are available to facilitate software development on multi-core systems.

For example, in a dual-core openMSP430 system, the cores can be instantiated as following:

The values of these parameters are then directly accessible by software through the CPU NR register of the SFR peripheral.

For example, if both cores share the same program memory, the software can take advantage of this information as following:

```

"...

int main(void) {

if (CPU_NR==0x0100) {

main_core_0(); // Main routine call for core 0

}

if (CPU_NR==0x0101) {

main_core_1(); // Main routine call for core 1

}

}

..."

```

# 2.4 Memory mapping

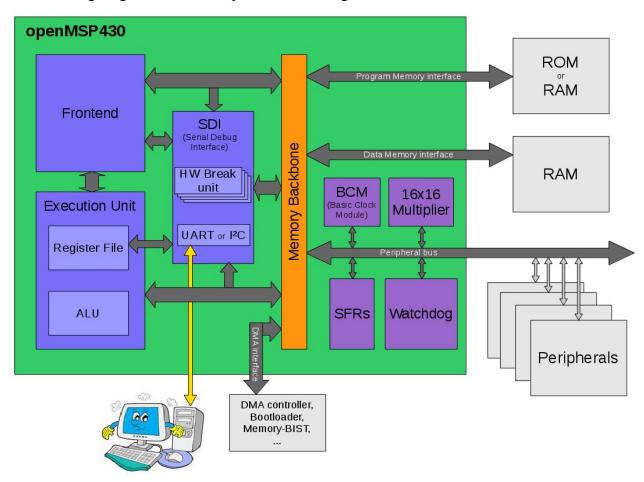

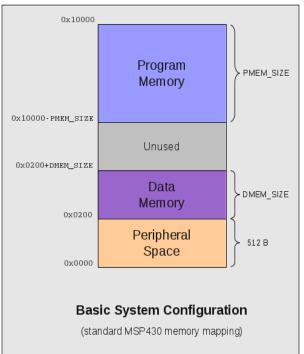

As discussed earlier, the openMSP430 memory mapping is fully configurable.

The basic system configuration section allows to adjust program and data memory sizes while keeping 100% compatibility with the pre-existing linker scripts provided by MSPGCC (or any other toolchain for that matter).

However, an increasing number of users saw the 512B space available for peripherals in the standard MSP430 architecture as a limitation. Therefore, the advanced system configuration section gives the possibility to up-scale the reserved peripheral address space anywhere between 512B and 32kB. As a consequence, the data memory space will be shifted up, which means that the linker script of your favorite toolchain will have to be modified accordingly.

The following schematic should hopefully summarize this:

## 2.5 Interrupt mapping

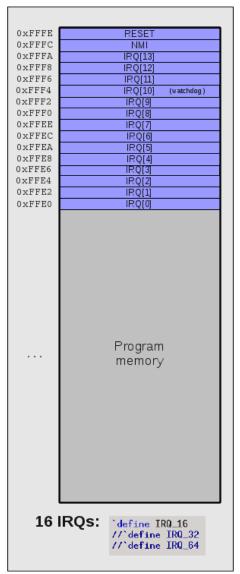

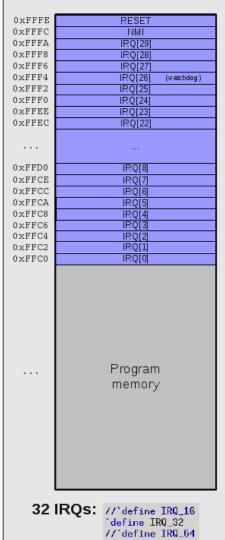

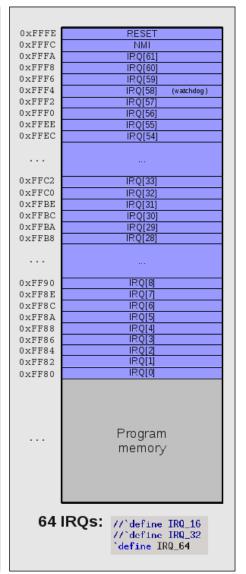

The number of supported interrupts is configurable with the IRQ xx macros.

The interrupt vectors are then mapped as following:

# 2.6 Pinout

The full pinout of the openMSP430 core is provided in the following table:

| Port Name   | Direct<br>ion | Width          | Clock<br>Domain                     | Description                                                                   |

|-------------|---------------|----------------|-------------------------------------|-------------------------------------------------------------------------------|

|             |               |                | Cloca                               | ks                                                                            |

| cpu_en      | Input         | 1              | <async> or mclk<sup>4</sup></async> | Enable CPU code execution (asynchronous and non-glitchy). Set to 1 if unused. |

| dco_clk     | Input         | 1              | -                                   | Fast oscillator (fast clock)                                                  |

| lfxt_clk    | Input         | 1              | -                                   | Low frequency oscillator (typ. 32kHz)<br>Set to 0 if unused.                  |

| mclk        | Output        | 1              | -                                   | Main system clock                                                             |

| aclk_en     | Output        | 1              | mclk                                | FPGA ONLY: ACLK enable                                                        |

| smclk_en    | Output        | 1              | mclk                                | FPGA ONLY: SMCLK enable                                                       |

| dco_enable  | Output        | 1              | dco_clk                             | ASIC ONLY: Fast oscillator enable                                             |

| dco_wkup    | Output        | 1              | <async></async>                     | ASIC ONLY: Fast oscillator wakeup (asynchronous)                              |

| lfxt_enable | Output        | 1              | lfxt_clk                            | ASIC ONLY: Low frequency oscillator enable                                    |

| lfxt_wkup   | Output        | 1              | <async></async>                     | ASIC ONLY: Low frequency oscillator wakeup (asynchronous)                     |

| aclk        | Output        | 1              | -                                   | ASIC ONLY: ACLK                                                               |

| smclk       | Output        | 1              | -                                   | ASIC ONLY: SMCLK                                                              |

| wkup        | Input         | 1              | <async></async>                     | ASIC ONLY: System Wake-up (asynchronous and non-glitchy) Set 0 if unused.     |

|             |               |                | Rese                                | ts                                                                            |

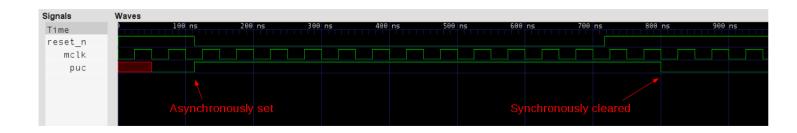

| puc_rst     | Output        | 1              | mclk                                | Main system reset                                                             |

| reset_n     | Input         | 1              | <async></async>                     | Reset Pin (active low, asynchronous and non-glitchy)                          |

|             |               |                | Interru                             | ıpts                                                                          |

| irq         | Input         | `IRQ_NR-2<br>1 | mclk                                | Maskable interrupts (one-hot signal)                                          |

| nmi                          | Input                        | 1                             | <async> or mclk<sup>4</sup></async>        | Non-maskable interrupt (asynchronous and non-glitchy) Set to 0 if unused. |  |

|------------------------------|------------------------------|-------------------------------|--------------------------------------------|---------------------------------------------------------------------------|--|

| irq_acc                      | Output                       | IRQ_NR-2                      | mclk                                       | Interrupt request accepted (one-hot signal)                               |  |

|                              |                              | Progr                         | am Memo                                    | ory interface                                                             |  |

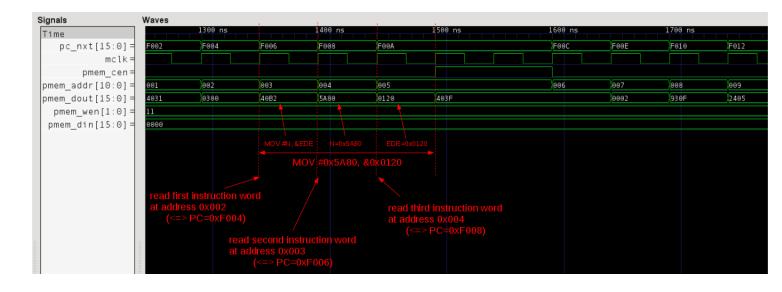

| pmem_addr Output AWIDTH mclk |                              |                               | Program Memory address                     |                                                                           |  |

| pmem_cen                     | Output                       | 1                             | mclk                                       | Program Memory chip enable (low active)                                   |  |

| pmem_din                     | Output                       | 16                            | mclk                                       | Program Memory data input (optional <sup>2</sup> )                        |  |

| pmem_dout                    | Input                        | 16                            | mclk                                       | Program Memory data output                                                |  |

| pmem_wen                     | Output                       | 2                             | melk                                       | Program Memory write byte enable (low active) (optional <sup>2</sup> )    |  |

|                              |                              | Dat                           | a Memory                                   | v interface                                                               |  |

| dmem_addr                    | Output                       | `DMEM_<br>AWIDTH <sup>1</sup> | mclk                                       | Data Memory address                                                       |  |

| dmem_cen                     | Output                       | 1                             | mclk                                       | Data Memory chip enable (low active)                                      |  |

| dmem_din                     | Output                       | 16                            | mclk                                       | Data Memory data input                                                    |  |

| dmem_dout                    | Input                        | 16                            | mclk                                       | Data Memory data output                                                   |  |

| dmem_wen                     | lamem wen "Chimit / I meik I |                               | Data Memory write byte enable (low active) |                                                                           |  |

|                              |                              | Extern                        | al Periphe                                 | erals interface                                                           |  |

| per_addr                     | Output                       | 14                            | mclk                                       | Peripheral address                                                        |  |

| per_din                      | Output                       | 16                            | mclk                                       | Peripheral data input                                                     |  |

| per_dout                     | Input                        | 16                            | mclk                                       | Peripheral data output                                                    |  |

| per_en                       | Output                       | 1                             | mclk                                       | Peripheral enable (high active)                                           |  |

| per_we                       | Output                       | 2                             | mclk                                       | Peripheral write enable (high active)                                     |  |

|                              |                              | Direct 1                      | Memory A                                   | ccess interface                                                           |  |

| dma_addr                     | Input                        | 15                            | mclk                                       | Direct Memory Access address                                              |  |

| dma_din                      | Input                        | 16                            | mclk                                       | Direct Memory Access data input                                           |  |

| dma_dout                     | Output                       | 16                            | mclk                                       | Direct Memory Access data output                                          |  |

| dma_en                       | Input                        | 1                             | mclk                                       | Direct Memory Access enable (high active)                                 |  |

| dma_priority                 | Input                        | 1                             | melk                                       | Direct Memory Access priority (0:low / 1:high)                            |  |

| dma_ready                    | Output                       | 1                             | mclk                                       | Direct Memory Access is complete                                          |  |

| dma_resp                     | Output                       | 1                             | mclk                                       | Direct Memory Access response                                             |  |

|                              | Carput                       |                               | I IIIOIK                                   | Z TOO MENTON TOO CONTROL TO TOO TOO TOO TOO TOO TOO TOO TOO TO            |  |

|        |                                                                                 |                                                                                                                        | (0:Okay / 1: Error)                                                                                                                                                                                                                     |  |  |

|--------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Input  | 2                                                                               | mclk Direct Memory Access write byte ena (high active)                                                                 |                                                                                                                                                                                                                                         |  |  |

| Input  | 1                                                                               | <async> ASIC ONLY: DMA Wake-up (asynchronous and non-glitchy)</async>                                                  |                                                                                                                                                                                                                                         |  |  |

|        | Ser                                                                             | ial Debug                                                                                                              | interface                                                                                                                                                                                                                               |  |  |

| Input  | 1                                                                               | <async> or mclk<sup>4</sup></async>                                                                                    | Debug interface enable (asynchronous) <sup>3</sup>                                                                                                                                                                                      |  |  |

| Output | 1                                                                               | mclk                                                                                                                   | Freeze peripherals                                                                                                                                                                                                                      |  |  |

| Output | 1                                                                               | mclk                                                                                                                   | Debug interface: UART TXD                                                                                                                                                                                                               |  |  |

| Input  | 1                                                                               | <async></async>                                                                                                        | Debug interface: UART RXD (asynchronous)                                                                                                                                                                                                |  |  |

| Input  | 7                                                                               | mclk                                                                                                                   | Debug interface: I2C Address                                                                                                                                                                                                            |  |  |

| Input  | 7                                                                               | mclk                                                                                                                   | Debug interface: I2C Broadcast Address (for multicore systems)                                                                                                                                                                          |  |  |

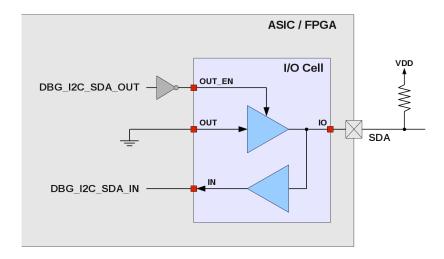

| Input  | 1                                                                               | <async></async>                                                                                                        | Debug interface: I2C SCL (asynchronous)                                                                                                                                                                                                 |  |  |

| Input  | 1                                                                               | <async></async>                                                                                                        | Debug interface: I2C SDA IN (asynchronous)                                                                                                                                                                                              |  |  |

| Output | 1                                                                               | mclk                                                                                                                   | Debug interface: I2C SDA OUT                                                                                                                                                                                                            |  |  |

| Scan   |                                                                                 |                                                                                                                        |                                                                                                                                                                                                                                         |  |  |

| Input  | 1                                                                               | dco_clk                                                                                                                | ASIC ONLY: Scan enable (active during scan shifting)                                                                                                                                                                                    |  |  |

| Input  | 1                                                                               | <stable></stable>                                                                                                      | ASIC ONLY: Scan mode                                                                                                                                                                                                                    |  |  |

|        | Input Output Output Input | Input 1  Ser Input 1 Output 1 Output 1 Input 1 Input 7 Input 7 Input 7 Input 1 Input 1 Input 1 Input 1 Input 1 Input 1 | Input 1 <async> Serial Debug Input 1 <async>or mclk⁴ Output 1 mclk Output 1 mclk Input 1 <async> Input 7 mclk Input 7 mclk Input 7 mclk Input 1 <async> Input 1 casync&gt; Input 1 mclk Input 1 dco_clk</async></async></async></async> |  |  |

<sup>1:</sup> This parameter is declared in the "openMSP430\_defines.v" file and defines the RAM/ROM size or the number of interrupts vectors (16, 32 or 64).

**Note:** in the FPGA configuration, the ASIC ONLY signals must be left unconnected (for the outputs) and tied low (for the inputs).

<sup>&</sup>lt;sup>2</sup>: These two optional ports can be connected whenever the program memory is a RAM. This will allow the user to load a program through the serial debug interface and to use software breakpoints.

<sup>3:</sup> When disabled, the debug interface is hold into reset (and clock gated in ASIC mode). As a consequence, the *dbg\_en* port can be used to reset the debug interface without disrupting the CPU execution.

<sup>4:</sup> Clock domain is selectable through configuration in the "openMSP430\_defines.v" file (see Advanced System Configuration).

# 2.7 Instruction Cycles and Lengths

Please note that a detailed description of the instruction and addressing modes can be found in the MSP430x1xx Family User's Guide (Chapter 3).

The number of CPU clock cycles required for an instruction depends on the instruction format and the addressing modes used, not the instruction itself.

In the following tables, the number of cycles refers to the main clock (*MCLK*). Differences with the original MSP430 are highlighted in green (the original value being red).

### • Interrupt and Reset Cycles

| Action                       | No. of Cycles | Length of Instruction |

|------------------------------|---------------|-----------------------|

| Return from interrupt (RETI) | 5             | 1                     |

| Interrupt accepted           | 6             | -                     |

| WDT reset                    | 4             | -                     |

| Reset (!RST/NMI)             | 4             | -                     |

### • Format-II (Single Operand) Instruction Cycles and Lengths

| Addressing Mode | No. of Cycle        | I anoth of Instruction |       |                       |

|-----------------|---------------------|------------------------|-------|-----------------------|

| Addressing Mode | RRA, RRC, SWPB, SXT | PUSH                   | CALL  | Length of Instruction |

| Rn              | 1                   | 3                      | 3 (4) | 1                     |

| @Rn             | 3                   | 4                      | 4     | 1                     |

| @Rn+            | 3                   | 4 (5)                  | 4 (5) | 1                     |

| #N              | N/A                 | 4                      | 5     | 2                     |

| X(Rn)           | 4                   | 5                      | 5     | 2                     |

| EDE             | 4                   | 5                      | 5     | 2                     |

| &EDE            | 4                   | 5                      | 5     | 2                     |

#### • Format-III (Jump) Instruction Cycles and Lengths

All jump instructions require one code word, and take two CPU cycles to execute, regardless of whether the jump is taken or not.

# • Format-I (Double Operand) Instruction Cycles and Lengths

| Addressi | ng Mode | No of Cyalor  | I anoth of Instruction |  |  |

|----------|---------|---------------|------------------------|--|--|

| Src      | Dst     | No. of Cycles | Length of Instruction  |  |  |

|          | Rm      | 1             | 1                      |  |  |

|          | PC      | 2             | 1                      |  |  |

| Rn       | x(Rm)   | 4             | 2                      |  |  |

|          | EDE     | 4             | 2                      |  |  |

|          | &EDE    | 4             | 2                      |  |  |

|          | Rm      | 2             | 1                      |  |  |

|          | PC      | 3 (2)         | 1                      |  |  |

| @Rn      | x(Rm)   | 5             | 2                      |  |  |

|          | EDE     | 5             | 2                      |  |  |

|          | &EDE    | 5             | 2                      |  |  |

|          | Rm      | 2             | 1                      |  |  |

|          | PC      | 3             | 1                      |  |  |

| @Rn+     | x(Rm)   | 5             | 2                      |  |  |

|          | EDE     | 5             | 2                      |  |  |

|          | &EDE    | 5             | 2                      |  |  |

|          | Rm      | 2             | 2                      |  |  |

|          | PC      | 3             | 2                      |  |  |

| #N       | x(Rm)   | 5             | 3                      |  |  |

|          | EDE     | 5             | 3                      |  |  |

|          | &EDE    | 5             | 3                      |  |  |

|          | Rm      | 3             | 2                      |  |  |

|          | PC      | 3 (4)         | 2                      |  |  |

| x(Rn)    | x(Rm)   | 6             | 3                      |  |  |

|          | EDE     | 6             | 3                      |  |  |

|          | &EDE    | 6             | 3                      |  |  |

|          | Rm      | 3             | 2                      |  |  |

|          | PC      | 3 (4)         | 2                      |  |  |

| EDE      | x(Rm)   | 6             | 3                      |  |  |

|          | EDE     | 6             | 3                      |  |  |

|          | &EDE    | 6             | 3                      |  |  |

|      | Rm    | 3 | 2 |

|------|-------|---|---|

| &EDE | PC    | 3 | 2 |

|      | x(Rm) | 6 | 3 |

|      | EDE   | 6 | 3 |

|      | &EDE  | 6 | 3 |

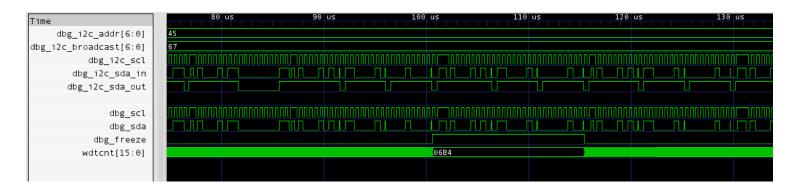

# 2.8 Serial Debug Interface

All the details about the Serial Debug Interface are located here.

### 2.9 Benchmark results

### 2.9.1 Dhrystone (DMIPS/MHz)

Dhrystone is known for being susceptible to compiler optimizations (among other issues). However, as it is still quite a popular metric, some results are provided here (ranging from 0.30 to 0.45 DMIPS/MHz depending on the compiler version and options).

Note that the used C-code is available in the repository <u>here</u> and <u>here</u>.

| Dhrystone flavor | Compiler option   | ons<br>-Os | -02  | -03  |

|------------------|-------------------|------------|------|------|

| Diffystone navoi | Compiler version  | -03        | -02  | -05  |

|                  | mspgcc v4.4.5     | 0.30       | 0.32 | 0.33 |

| Dhrystone v2.1   | mspgcc v4.6.3     | 0.37       | 0.39 | 0.40 |

| (common version) | mspgcc v4.7.2     | 0.37       | 0.37 | 0.37 |

|                  | msp430-elf v4.9.1 | 0.26       | 0.36 | 0.37 |

|                  | mspgcc v4.4.5     | 0.30       | 0.30 | 0.31 |

| Dhrystone v2.1   | mspgcc v4.6.3     | 0.37       | 0.44 | 0.45 |

| (MCU adapted)    | mspgcc v4.7.2     | 0.37       | 0.44 | 0.45 |

|                  | msp430-elf v4.9.1 | 0.26       | 0.36 | 0.37 |

## 2.9.2 CoreMark (Coremark/MHz)

CoreMark tries to address most of Dhrystone's pitfall by preventing the compiler to optimize some code away and using "real-life" algorithm.

Note that the used C-code is available in the repository <u>here</u>.

|                    | Compiler options  | -Os  | -O2  | -03  |

|--------------------|-------------------|------|------|------|

|                    | Compiler version  |      |      |      |

|                    | mspgcc v4.4.5     | 0.78 | 0.85 | 0.83 |

| CoreMark v1.0      | mspgcc v4.6.3     | 0.74 | 0.91 | 0.87 |

| (official version) | mspgcc v4.7.2     | 0.67 | 0.93 | 0.90 |

|                    | msp430-elf v4.9.1 | 0.58 | 0.67 | n.a. |

# **Peripherals**

### **Table of content**

- 1. Introduction

- 2. Peripherals

- 2.1 System Peripherals

- 2.1.1 Basic Clock Module: FPGA

- 2.1.2 Basic Clock Module: ASIC

- 2.1.3 SFR

- 2.1.4 Watchdog Timer

- 2.1.5 16x16 Hardware Multiplier

- 2.2 External Peripherals

- 2.2.1 Digital I/O (FPGA ONLY)

- 2.3.2 Timer A (FPGA ONLY)

# 1. Introduction

In addition to the CPU core itself, several peripherals are also provided and can be easily connected to the core during integration.

# 2. Peripherals

# 2.1 System Peripherals

In addition to the CPU core itself, several peripherals are also provided and can be easily connected to the core during integration. The followings are directly integrated within the core because of their tight links with the CPU.

It is to be noted that **ALL** system peripherals support both ASIC and FPGA versions.

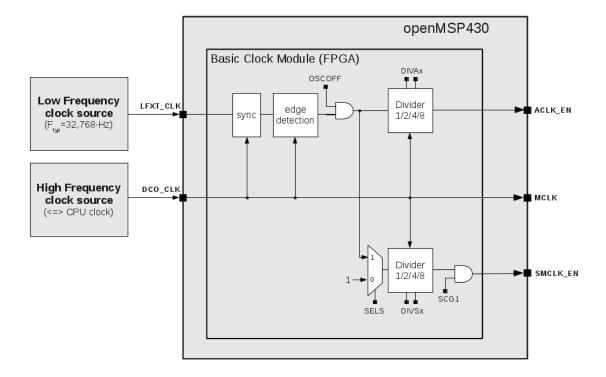

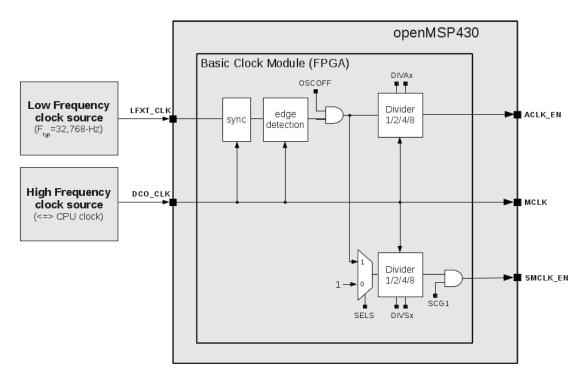

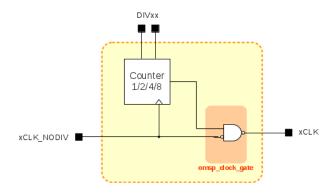

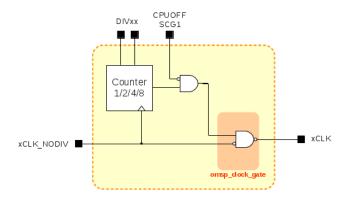

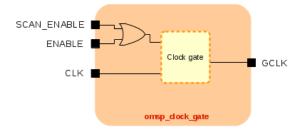

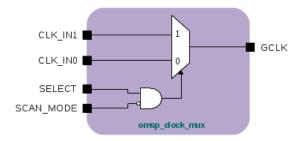

#### 2.1.1 Basic Clock Module: FPGA

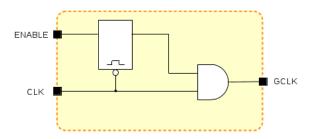

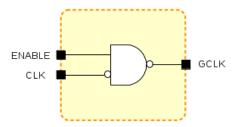

In order to make an FPGA implementation as simple as possible (ideally, a non-professional designer should be able to do it), clock gates are not used in the design configuration and neither are clock muxes.

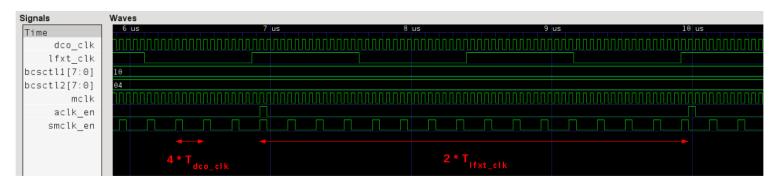

With these constrains, the Basic Clock Module is implemented as following:

**Note**: CPUOFF doesn't switch MCLK off and will instead bring the CPU state machines in an IDLE state while MCLK will still be running.

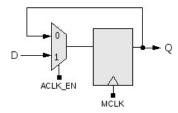

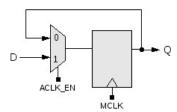

In order to 'clock' a register with ACLK or SMCLK, the following structure needs to be implemented:

For example, the following Verilog code would implement a counter clocked with SMCLK:

#### **Register Description (FPGA)**

| Register | Address | Bit Fields      |                     |   |      |    |     |        |   |

|----------|---------|-----------------|---------------------|---|------|----|-----|--------|---|

| Name     | Audress | 7               | 6                   | 5 | 4    | 3  | 2   | 1      | 0 |

| DCOCTL   | 0x0004  | not implemented |                     |   |      |    |     |        |   |

| BCSTL1   | 0x0006  | unu             | unused DIVAx unused |   |      |    |     |        |   |

| BCSTL2   | 0x0008  | unused          |                     |   | SELS | DI | VSx | unused |   |

• BCSCTL1.**DIVAx** : ACLK EN divider (1/2/4/8)

• BCSCTL2.**SELS** : SMCLK EN clock selection (0:DCO CLK / 1:LFXT CLK)

• BCSCTL2.**DIVSx** : SMCLK EN divider (1/2/4/8)

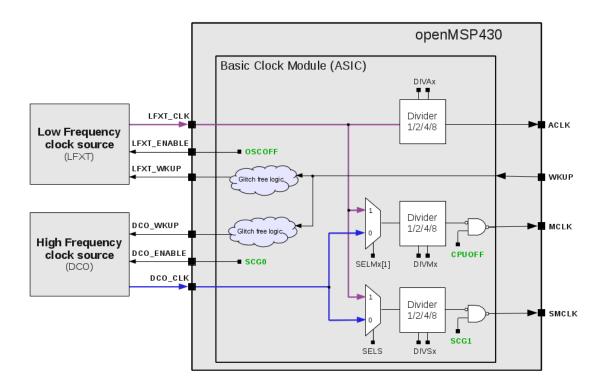

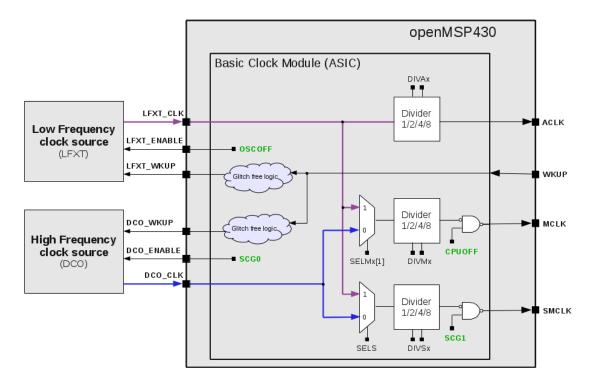

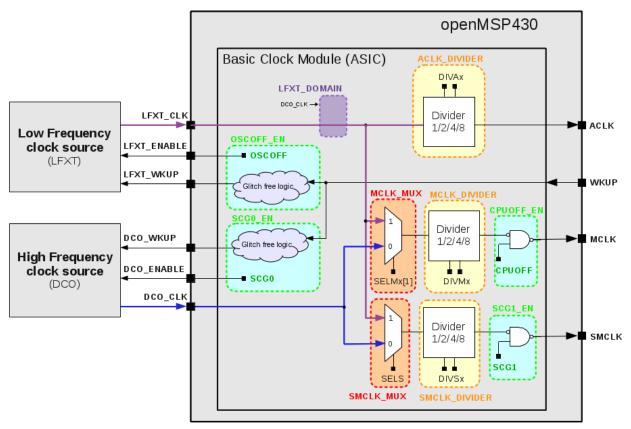

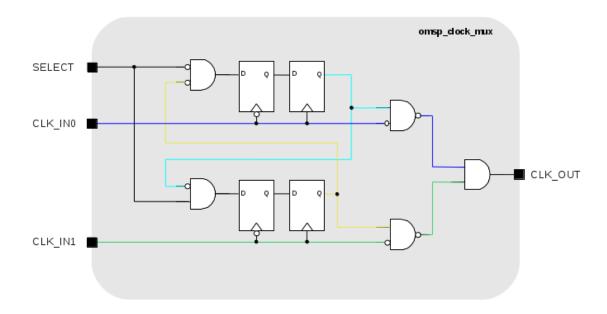

### 2.1.2 Basic Clock Module: ASIC

When targeting an ASIC, up to all clock management options available in the MSP430x1xx Family User's Guide (Chapter 4) can be included:

Additional info can be found in the <u>ASIC implementation</u> section.

### **Register Description (ASIC)**

| Register | Address |              | Bit Fields |       |                 |              |                |                |        |  |  |  |  |

|----------|---------|--------------|------------|-------|-----------------|--------------|----------------|----------------|--------|--|--|--|--|

| Name     | Address | 7            | 6          | 5     | 4               | 3            | 2              | 1              | 0      |  |  |  |  |

| DCOCTL   | 0x0004  |              | ~          |       | not implemented |              |                |                |        |  |  |  |  |

| BCSTL1   | 0x0006  | unus         | DIV        | /Ax   | DMA_<br>SCG1    | DMA_<br>SCG0 | DMA_<br>OSCOFF | DMA_<br>CPUOFF |        |  |  |  |  |

| BCSTL2   | 0x0008  | SELMx unused |            | DIVMx |                 | SELS         | DIV            | /Sx            | unused |  |  |  |  |

• BCSCTL1.**DIVAx** : ACLK divider (1/2/4/8)

• BCSCTL1.**DMA SCG1** : Restore SMCLK with DMA wakeup

BCSCTL1.DMA\_SCG0 : Restore DCO oscillator with DMA wakeup

BCSCTL1.DMA\_OSCOFF : Restore LFXT oscillator with DMA wakeup

• BCSCTL1.**DMA CPUOFF** : Restore MCLK with DMA wakeup

• BCSCTL2.**SELMx** : MCLK clock selection (0:DCO\_CLK / 1:LFXT\_CLK)

• BCSCTL2.**DIVMx** : MCLK clock divider (1/2/4/8)

• BCSCTL2.SELS : SMCLK clock selection (0:DCO\_CLK / 1:LFXT\_CLK)

• BCSCTL2.**DIVS**x : SMCLK clock divider (1/2/4/8)

#### 2.1.3 SFR

Following the MSP430x1xx Family User's Guide, this peripheral implements flags and interrupt enable bits for the Watchdog Timer and NMI:

| Register | Adduss  | Address Bit Fields |   |   |          |          |   |                      |                    |                     |  |

|----------|---------|--------------------|---|---|----------|----------|---|----------------------|--------------------|---------------------|--|

| Name     | Address | 7                  | 6 | 5 | 4        | 3        | 2 | 1                    | 0                  |                     |  |

| IE1      | 0x0000  | Reserved           |   |   | NMIIE 1  | Reserved |   | ed                   | WDTIE <sup>2</sup> |                     |  |

| IFG1     | 0x0002  | Reserved           |   |   | NMIIFG 1 | Reserved |   | FG 1 Reserved WDTIFG |                    | WDTIFG <sup>2</sup> |  |

<sup>1:</sup> These fields are not available if the NMI is excluded (see *openMSP430 defines.v*)

In addition, two 16-bit read-only registers have been added in order to let the software know with which version of the openMSP430 it is running:

| Register  | Address | Bit field |              |    |    |    |    |    |            |     |     |      |             |      |       |   |   |

|-----------|---------|-----------|--------------|----|----|----|----|----|------------|-----|-----|------|-------------|------|-------|---|---|

| Name      | Auuress | 15        | 14           | 13 | 12 | 11 | 10 | 9  | 8          | 7   | 6   | 5    | 4           | 3    | 2     | 1 | 0 |

| CPU_ID_LO | 0x0004  |           | PER_SPACE    |    |    |    |    | US | ER_VERSION |     |     | ASIC | CPU_VERSION |      | RSION |   |   |

| CPU_ID_HI | 0x0006  |           | PMEM_SIZE    |    |    |    |    |    | D          | MEI | M_S | IZE  |             |      | MPY   |   |   |

| CPU_NR    | 0x0008  |           | CPU_TOTAL_NR |    |    |    |    |    |            |     |     | CP   | U_INS       | T_NR |       |   |   |

• CPU VERSION: Current CPU version.

• ASIC : Defines if the ASIC specific features are enabled in the

current openMSP430 implementation.

• USER\_VERSION : Reflects the value defined in the *openMSP430\_defines.v*

file

• PER\_SPACE : Peripheral address space for the current implementation

(byte size = PER SPACE\*512)

• **MPY** : This bit is set if the hardware multiplier is inclued in the

current implementation.

• **DMEM\_SIZE** : Data memory size for the current implementation

(byte size = DMEM SIZE\*128)

• **PMEM SIZE** : Program memory size for the current implementation

(byte size = PMEM SIZE\*1024)

• CPU INST NR : Current oMSP instance number (for multicore systems)

• CPU TOTAL NR : Total number of oMSP instances-1 (for multicore systems)

<sup>&</sup>lt;sup>2</sup>: These fields are not available if the Watchdog is excluded (see *openMSP430\_defines.v* )

<u>Note:</u> attentive readers will have noted that *CPU\_ID\_LO*, *CPU\_ID\_HI* and *CPU\_NR* are identical to the Serial Debug Interface register counterparts.

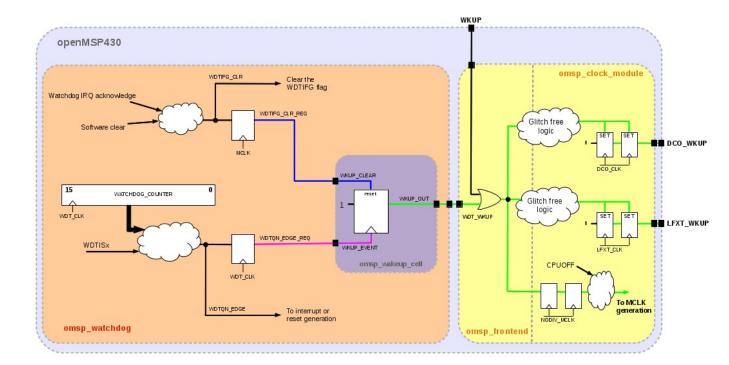

### 2.1.4 Watchdog Timer

100% of the features advertised in the MSP430x1xx Family User's Guide (Chapter 10) have been implemented.

The following parameter in the *openMSP430\_defines.v* file controls if the watchdog timer should be included or not:

### 2.1.5 16x16 Hardware Multiplier

100% of the features advertised in the MSP430x1xx Family User's Guide (Chapter 7) have been implemented.

The following parameter in the *openMSP430\_defines.v* file controls if the hardware multiplier should be included or not:

```

// Include/Exclude Hardware Multiplier

`define MULTIPLIER

```

### 2.2 External Peripherals

The external peripherals labeled with the "FPGA ONLY" tag do not contain any clock gate nor clock muxes and are clocked with MCLK only. This mean that they don't support any of the low power modes and therefore are most likely not suited for an ASIC implementation.

### 2.2.1 Digital I/O (FPGA ONLY)

100% of the features advertised in the MSP430x1xx Family User's Guide (Chapter 9) have been implemented.

The following Verilog parameters will enable or disable the corresponding ports in order to save area (i.e. FPGA utilization):

```

parameter P1_EN = 1'b1; // Enable Port 1

parameter P2_EN = 1'b1; // Enable Port 2

parameter P3_EN = 1'b0; // Enable Port 3

parameter P4_EN = 1'b0; // Enable Port 4

parameter P5_EN = 1'b0; // Enable Port 5

parameter P6_EN = 1'b0; // Enable Port 6

```

They can be updated as following during the module instantiation (here port 1, 2 and 3 are enabled):

The full pinout of the GPIO module is provided in the following table:

| Port Name       | Direction | Width | Description       |  |  |  |  |  |

|-----------------|-----------|-------|-------------------|--|--|--|--|--|

| Clocks & Resets |           |       |                   |  |  |  |  |  |

| mclk            | Input     | 1     | Main system clock |  |  |  |  |  |

| puc_rst         | Input     | 1     | Main system reset |  |  |  |  |  |

| Interrupts      |           |       |                   |  |  |  |  |  |

| irq_port1       | Output    | 1     | Port 1 interrupt  |  |  |  |  |  |

| irq_port2       | Output    | 1     | Port 2 interrupt  |  |  |  |  |  |

| External Peripherals interface |        |    |                                       |  |  |  |  |  |

|--------------------------------|--------|----|---------------------------------------|--|--|--|--|--|

| per_addr                       | Input  | 8  | Peripheral address                    |  |  |  |  |  |

| per_din                        | Input  | 16 | Peripheral data input                 |  |  |  |  |  |

| per_dout                       | Output | 16 | Peripheral data output                |  |  |  |  |  |

| per_en                         | Input  | 1  | Peripheral enable (high active)       |  |  |  |  |  |

| per_wen                        | Input  | 2  | Peripheral write enable (high active) |  |  |  |  |  |

| Port 1                         |        |    |                                       |  |  |  |  |  |

| p1_din                         | Input  | 8  | Port 1 data input                     |  |  |  |  |  |

| p1_dout                        | Output | 8  | Port 1 data output                    |  |  |  |  |  |

| p1_dout_en                     | Output | 8  | Port 1 data output enable             |  |  |  |  |  |

| p1_sel                         | Output | 8  | Port 1 function select                |  |  |  |  |  |

| Port 2                         |        |    |                                       |  |  |  |  |  |

| p2_din                         | Input  | 8  | Port 2 data input                     |  |  |  |  |  |

| p2_dout                        | Output | 8  | Port 2 data output                    |  |  |  |  |  |

| p2_dout_en                     | Output | 8  | Port 2 data output enable             |  |  |  |  |  |

| p2_sel                         | Output | 8  | Port 2 function select                |  |  |  |  |  |

|                                |        |    | Port 3                                |  |  |  |  |  |

| p3_din                         | Input  | 8  | Port 3 data input                     |  |  |  |  |  |

| p3_dout                        | Output | 8  | Port 3 data output                    |  |  |  |  |  |

| p3_dout_en                     | Output | 8  | Port 3 data output enable             |  |  |  |  |  |

| p3_sel                         | Output | 8  | Port 3 function select                |  |  |  |  |  |

|                                |        |    | Port 4                                |  |  |  |  |  |

| p4_din                         | Input  | 8  | Port 4 data input                     |  |  |  |  |  |

| p4_dout                        | Output | 8  | Port 4 data output                    |  |  |  |  |  |

| p4_dout_en                     | Output | 8  | Port 4 data output enable             |  |  |  |  |  |

| p4_sel                         | Output | 8  | Port 4 function select                |  |  |  |  |  |

|                                |        |    | Port 5                                |  |  |  |  |  |

| p5_din                         | Input  | 8  | Port 5 data input                     |  |  |  |  |  |

| p5_dout                        | Output | 8  | Port 5 data output                    |  |  |  |  |  |

| p5_dout_en                     | Output | 8  | Port 5 data output enable             |  |  |  |  |  |

| p5_sel                         | Output | 8  | Port 5 function select                |  |  |  |  |  |

|                                |        |    | Port 6                                |  |  |  |  |  |

| p6_din                         | Input  | 8  | Port 6 data input                     |  |  |  |  |  |

| p6_dout                        | Output | 8  | Port 6 data output                    |  |  |  |  |  |

| p6_dout_en | Output | 8 | Port 6 data output enable |

|------------|--------|---|---------------------------|

| p6_sel     | Output | 8 | Port 6 function select    |

## 2.2.2 Timer A (FPGA ONLY)

100% of the features advertised in the MSP430x1xx Family User's Guide (Chapter 11) have been implemented.

The full pinout of the Timer A module is provided in the following table:

| Port Name   | Direction | Width   | Description                             |  |  |  |  |

|-------------|-----------|---------|-----------------------------------------|--|--|--|--|

|             |           | Cloc    | cks, Resets & Debug                     |  |  |  |  |

| mclk        | Input     | 1       | Main system clock                       |  |  |  |  |

| aclk_en     | Input     | 1       | ACLK enable (from CPU)                  |  |  |  |  |

| smclk_en    | Input     | 1       | SMCLK enable (from CPU)                 |  |  |  |  |

| inclk       | Input     | 1       | INCLK external timer clock (SLOW)       |  |  |  |  |

| taclk       | Input     | 1       | TACLK external timer clock (SLOW)       |  |  |  |  |

| puc_rst     | Input     | 1       | Main system reset                       |  |  |  |  |

| dbg_freeze  | Input     | 1       | Freeze Timer A counter                  |  |  |  |  |

| Interrupts  |           |         |                                         |  |  |  |  |

| irq_ta0     | Output    | 1       | Timer A interrupt: TACCR0               |  |  |  |  |

| irq_ta1     | Output    | 1       | Timer A interrupt: TAIV, TACCR1, TACCR2 |  |  |  |  |

| irq_ta0_acc | Input     | 1       | Interrupt request TACCR0 accepted       |  |  |  |  |

|             |           | Externo | al Peripherals interface                |  |  |  |  |

| per_addr    | Input     | 8       | Peripheral address                      |  |  |  |  |

| per_din     | Input     | 16      | Peripheral data input                   |  |  |  |  |

| per_dout    | Output    | 16      | Peripheral data output                  |  |  |  |  |

| per_en      | Input     | 1       | Peripheral enable (high active)         |  |  |  |  |

| per_wen     | Input     | 2       | Peripheral write enable (high active)   |  |  |  |  |

|             |           | Сарі    | ture/Compare Unit 0                     |  |  |  |  |

| ta_cci0a    | Input     | 1       | Timer A capture 0 input A               |  |  |  |  |

| ta_cci0b    | Input     | 1       | Timer A capture 0 input B               |  |  |  |  |

| ta_out0     | Output    | 1       | Timer A output 0                        |  |  |  |  |

| ta_out0_en  | Output    | 1       | Timer A output 0 enable                 |  |  |  |  |

|             |           | Capi    | ture/Compare Unit 1                     |  |  |  |  |

| ta_cci1a    | Input     | 1       | Timer A capture 1 input A               |  |  |  |  |

| ta_cci1b               | Input  | 1 | Timer A capture 1 input B |  |  |  |  |

|------------------------|--------|---|---------------------------|--|--|--|--|

| ta_out1                | Output | 1 | Timer A output 1          |  |  |  |  |

| ta_out1_en             | Output | 1 | Timer A output 1 enable   |  |  |  |  |

| Capture/Compare Unit 2 |        |   |                           |  |  |  |  |

| ta_cci2a               | Input  | 1 | Timer A capture 2 input A |  |  |  |  |

| ta_cci2b               | Input  | 1 | Timer A capture 2 input B |  |  |  |  |

| ta_out2                | Output | 1 | Timer A output 2          |  |  |  |  |

| ta_out2_en             | Output | 1 | Timer A output 2 enable   |  |  |  |  |

**Note**: for the same reason as with the Basic Clock Module FPGA version, the two additional clock inputs (TACLK and INCLK) are internally synchronized with the MCLK domain. As a consequence, TACLK and INCLK should be at least 2 times slowlier than MCLK, and if these clock are used toghether with the Timer A output unit, some jitter might be observed on the generated output. If this jitter is critical for the application, ACLK and INCLK should idealy be derivated from DCO CLK.

# **DMA** Interface

#### **Table of content**

- 1. Introduction

- 2. Signal list

- 3. Protocol

- 3.1 Simple transfer

- 3.2 Transfer with wait states

- 3.3 Multiple transfers

- 3.4 Transfer response

- 3.5 Priority control

- 3.5.1 Data rate control

- 3.5.2 Bootloader case

- 4 ASIC Implementation

- 4.1 Clock domains

- 4.2 DMA wakeup

# 1. Introduction

The openMSP430 Direct-Memory-Access interface acts as a gateway to the whole logical 64kB memory space and can be enabled be uncommenting the DMA\_IF\_EN macro in the "openMSP430 defines.sv" file:

```

//----

// Include/Exclude DMA interface support

//-----

//`define DMA_IF_EN

```

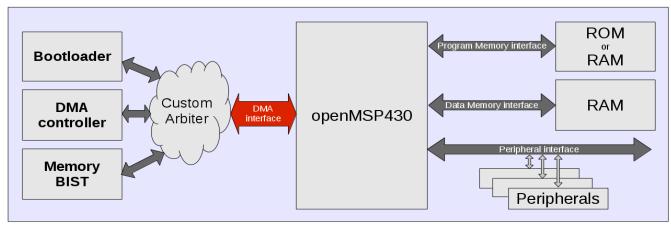

It supports the efficient connection of Bootloader, DMA controller, Memory-BIST or any other hardware unit requiring direct read/write access to the CPU memory space.

The interface is also designed as to reuse the existing arbitration logic within the memory-backbone and thus minimize to timing costs of its physical implementation (i.e. no additional muxing layer on an already critical timing path).

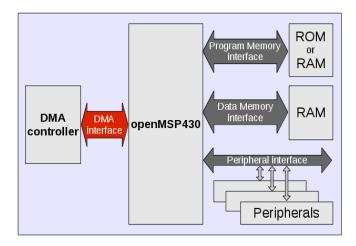

An simple system using the DMA interface typically consists of a DMA master directly connected to openMSP430 core:

However, it is also possible to combine different DMA masters using a custom arbitration logic:

# 2. Signal list

| Name                         | Source                       | Type    | Description                                                                                                                                   |

|------------------------------|------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| MCLK<br>System clock         | openMSP430                   | System  | This clock times all DMA transfers. All signal timings are related to the rising edge of MCLK.                                                |

| PUC_RST<br>System reset      | openMSP430                   | System  | The system reset is active HIGH and is used to reset the sytem, including the DMA master(s).                                                  |

| DMA_WKUP Wakeup              | DMA Master<br>(Asynchronous) | System  | When HIGH in a Low-Power-Mode, the wakeup signal restores the clocks necessary for the DMA transfer (see <u>ASIC Implementation</u> section). |

| DMA_ADDR[15:1] Address bus   | DMA Master                   | Adress  | This is the 15-bit address bus allowing to access the 64kB address space (16b words).                                                         |

| DMA_DIN[15:0] Write data bus | DMA Master                   | Data    | The write data bus is used to transfer data from the DMA master to openMSP430 system during write operations.                                 |

| DMA_DOUT[15:0] Read data bus | openMSP430                   | Data    | The read data bus is used to transfer data from the openMSP430 system to the DMA master during read operations.                               |

| DMA_EN Transfer enable       | DMA Master                   | Control | Indicates that the current DMA transfer is active.                                                                                            |

| DMA_WE[1:0] Transfer direction | DMA Master | Control  | When HIGH, this signal indicates a write transfer on the selected byte, and a read transfer when LOW.                                                                             |

|--------------------------------|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA_PRIORITY Transfer priority | DMA Master | Control  | When HIGH, this signal indicates a high priority DMA transfer (i.e. CPU is stopped). When LOW, low priority DMA transfer have to wait for the CPU to free the accessed ressource. |

| DMA_READY Transfer done        | openMSP430 | Response | When HIGH the DMA_READY signal indicates that a transfer has finished on the bus. This signal may be driven LOW to add wait states to the transfer.                               |

| DMA_RESP<br>Transfer response  | openMSP430 | Response | The transfer response provides additional information on the status of a transfer (OKAY if LOW, ERROR when HIGH).                                                                 |

# 3. Protocol

# 3.1 Simple transfers

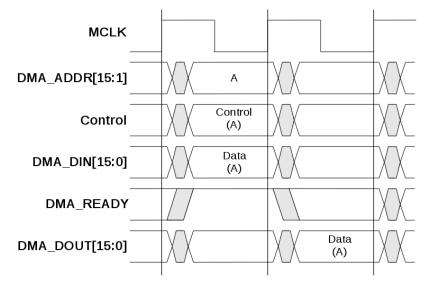

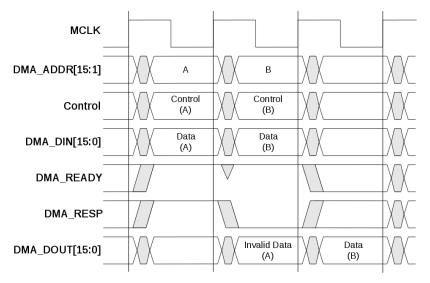

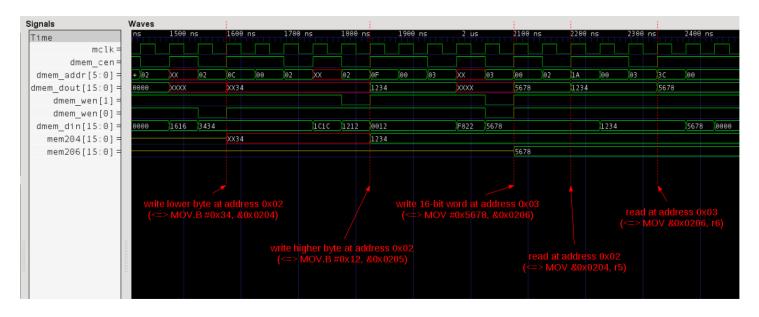

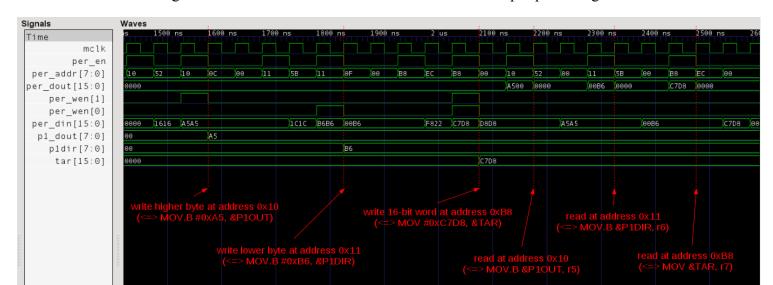

The following figure shows the simplest transfer, one with no wait states.

In a simple transfer with no wait states:

- The DMA master drives the address, control signals and write data onto the bus after the rising edge of MCLK.

- The openMSP430 ressource (pmem/dmem/peripheral) then samples the address, control and write data information on the next rising edge of the clock.

- For read access, after the openMSP430 ressource has sampled the address and control it can start to drive the read data and this is sampled by the DMA master on the third rising edge of the clock.

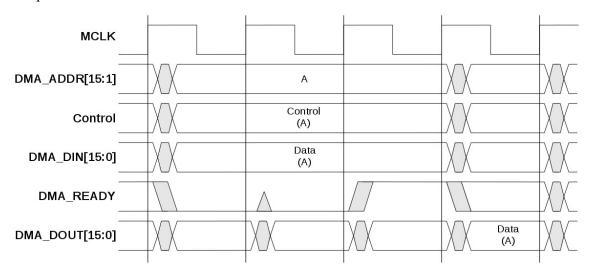

#### 3.2 Transfer with wait states

The openMSP430 can insert wait states into any transfer, as shown in the following figure, which extends the transfer by two clock cycles, thus taking additional time for completion.

For both read and write operations the DMA master must hold the address, control and write data stable throughout the extended cycles.

**Note:** wait states are inserted by the openMSP430 if the CPU is currently busy reading or writing to the same ressource that the DMA controller also wants to access.

# 3.3 Multiple transfers

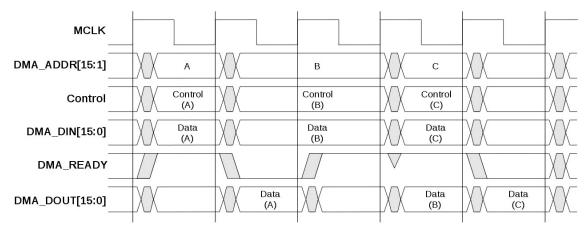

The following figure shows three transfers to unrelated addresses, A, B & C.

We can here observe:

- the transfers to addresses A and C are both zero wait state.

- the transfer to address B is one wait state.

- the read data from A is available during the **first** clock cycle when the address and control B are applied.

- the read data from B is available during the clock cycle when the address and control C are applied.

# 3.4 Transfer response

The following figure shows two transfers to unrelated addresses, A & B.

We can here observe:

- the transfer to address A returns an ERROR response (note that transfer returning an ERROR response **never** have wait states).

- the transfer to address B is a regular transfer (i.e. OKAY response) without wait state.

**Note:** an ERROR response are generated if the transfer address lays between the program and data memories, where nothing is mapped.

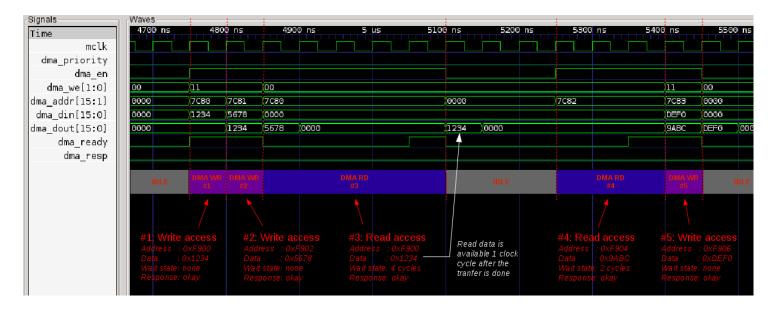

### 3.5 Priority control

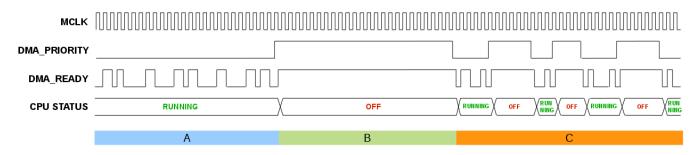

#### 3.5.1 Data rate control

The DMA\_PRIORITY control signal is available to the DMA master for controlling the application data rate requirements.

- When CLEARED, DMA transfers have a fixed lower priority than the CPU. This

means that depending on the exact kind of instructions currently executed by the

CPU, the completion time of the DMA transfers cannot be predicted (i.e. DMA

transfers are completed only when the CPU is not accessing the trageted

ressource).

- When SET, DMA transfers have a **fixed higher priority** over the CPU. This means that the CPU will will stop execution and give the full bandwidth to the DMA controller. In that scenario, DMA transfers complete in a single clock cycle (i.e. without any wait states), as the targeted ressources are always available (i.e. the CPU is not executing).

- If the application requirements need something in between (namely a minimum DMA transfer data-rate with reduced effect on the firmware exection), then the DMA master can dynamically change the DMA PRIORITY as required.

These scenario are illustrated in the following figure.

We can here observe:

• Phase A illustrates LOW-PRIORITY transfers. Less DMA transfer are completed during that time as shown by the number of wait states.

- Phase **B** illustrates HIGH-PRIORITY transfers. DMA transfers are completed with each clock cycle (i.e. no wait state).

- Phase C illustrates MIXED-PRIORITY transfers where the DMA controller is dynamically adjusting the priority to achieve its target minimum data-rate.

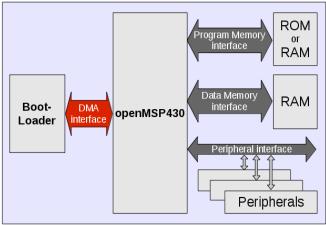

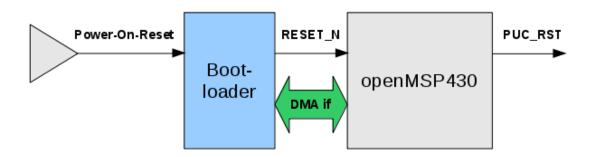

#### 3.5.2 Bootloader case

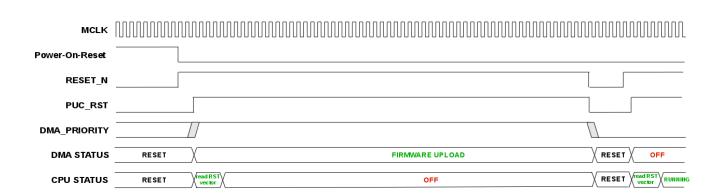

In general, the purpose of a bootloader is to initialize the program memory at startup (i.e after Power-On-Reset).

DMA transfers driven by the bootloader should therefore be performed in HIGH-PRIORITY mode, as the CPU should not start executing instructions on a non-initialized memory.

Once the memory initialization is completed, a reset pulse should be generated by the bootloader to make sure the CPU re-fetches the new RESET vector from the program memory.

A bootloader could be for example be connected as following:

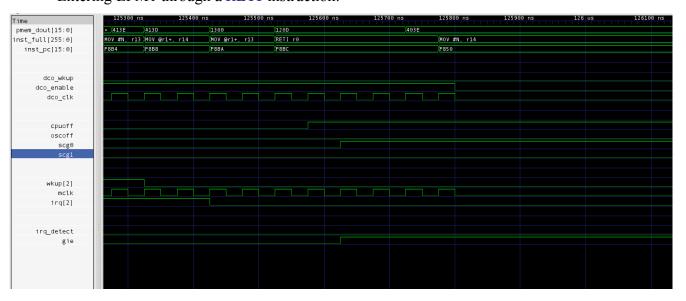

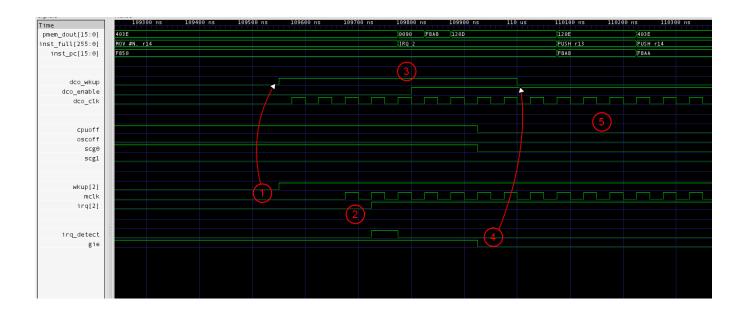

The bootloading sequence is illustrated in the following figure:

# 4. ASIC Implementation

#### 4.1 Clock domains

If the ASIC low power options are enabled, it is possible to perform DMA accesses when the main CPU is in **any** Low-Power-Mode (LPMx).

However, in order to avoid unnecessary power consumption while restoring the clocks for the DMA transfer, the MCLK system clock has been split into two clock domains.

- MCLK\_CPU: clocks the CPU core itself, namely the frontend and execution logic. When the CPU is in LPMx mode, this clock is ALWAYS OFF, even if a DMA transfer is currently on going.

- MCLK\_DMA: clocks the rest of the system (excluding the DBG interface) and gives access to the 64kB memory adddress range to the DMA master. This clock is restored in LPMx modes by asserting the DMA WKUP pin.

This table summarizes the clock operating modes:

| Clock Name | CPU is Active  | CPU in Low- | Power-Mode |

|------------|----------------|-------------|------------|

| Clock Name | CF U is Active | DMA_WKUP=0  | DMA_WKUP=1 |

| MCLK_CPU   | ON             | OFF         | OFF        |

| MCLK_DMA   | ON             | OFF         | ON         |

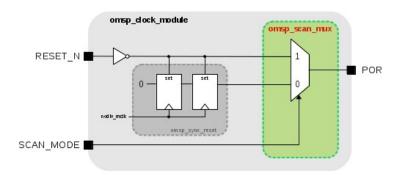

Clock domains are illustrated in the following diagram:

# 4.2 DMA wakeup

As shown in the "Peripherals" chapter, the Basic-Clock-Module has several control registers giving some flexibility to the firmware as to which clocks are restored when the DMA\_WKUP pin is asserted.

| Register | Address |      |     |     | Е   | Bit Fields   |              |                |                |

|----------|---------|------|-----|-----|-----|--------------|--------------|----------------|----------------|

| Name     | Address | 7    | 6   | 5   | 4   | 3            | 2            | 1              | 0              |

| BCSTL1   | 0x0006  | unus | sed | DIV | VAx | DMA_<br>SCG1 | DMA_<br>SCG0 | DMA_<br>OSCOFF | DMA_<br>CPUOFF |

• DMA\_SCG1 : Restore SMCLK with DMA wakeup

• **DMA SCG0** : Restore DCO oscillator with DMA wakeup

• **DMA\_OSCOFF** : Restore LFXT oscillator with DMA wakeup

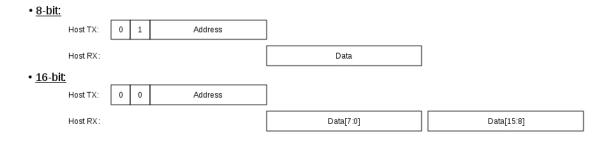

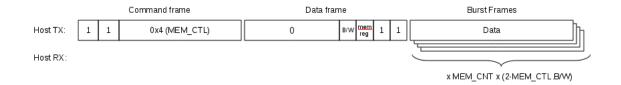

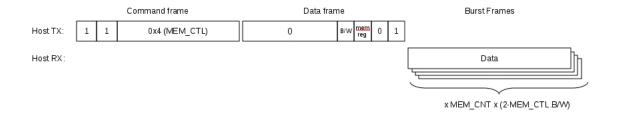

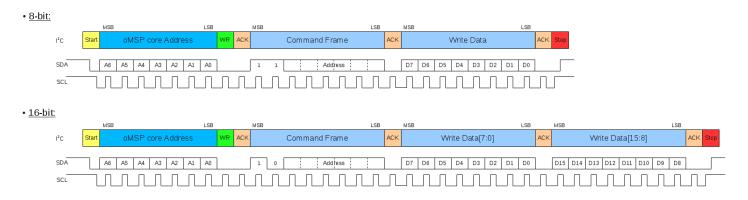

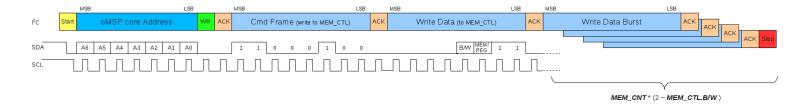

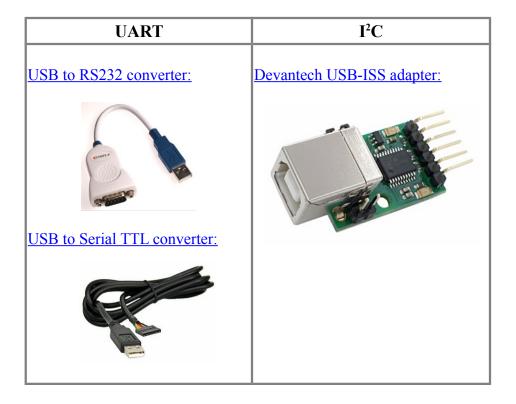

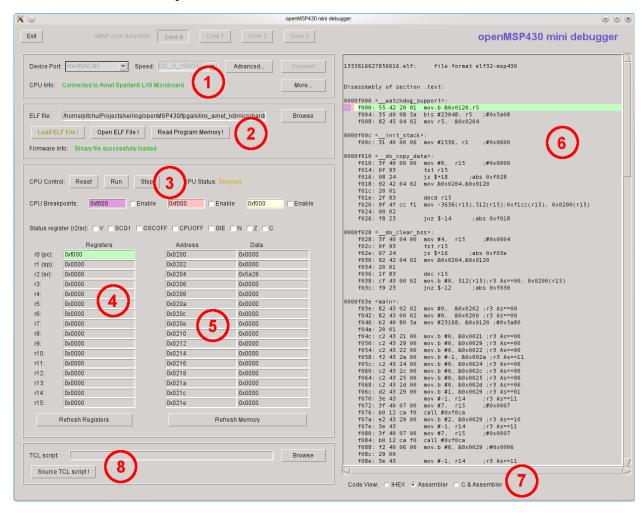

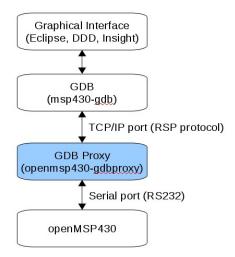

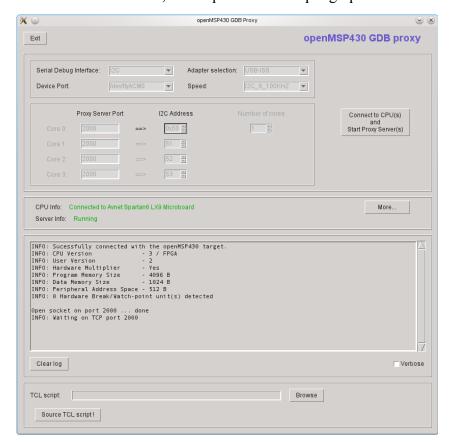

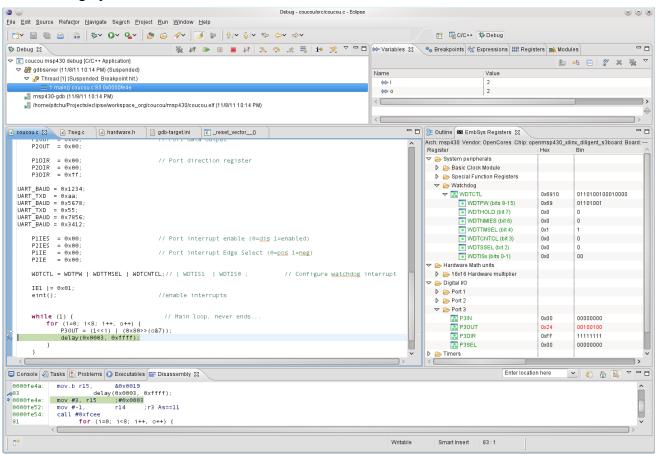

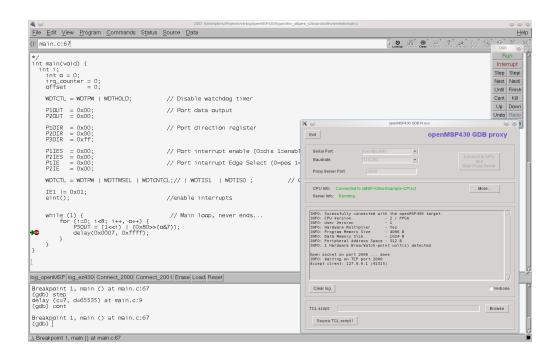

• **DMA\_CPUOFF** : Restore MCLK\_DMA with DMA wakeup