## openMSP430

an MSP430 clone....

Author: Olivier GIRARD olgirard@gmail.com

Rev. 1.4 January 12, 2010

## **Revision History**

| Rev | Date                             | Author | Description                                     |

|-----|----------------------------------|--------|-------------------------------------------------|

| 1.0 | August 4th, 2009                 | GIRARD | First version.                                  |

| 1.1 | August 30th, 2009                | GIRARD | Replaced "openMSP430.inc" with                  |

|     |                                  |        | "openMSP430_defines.v"                          |

| 1.2 | December 27 <sup>th</sup> , 2009 | GIRARD | - Update file and directory description for hte |

|     |                                  |        | FPGA projects (in particular, add the Altera    |

|     |                                  |        | project).                                       |

|     |                                  |        | - Diverse minor updates.                        |

| 1.3 | December 29 <sup>th</sup> , 2009 | GIRARD | - Renamed the "rom_*" ports to "pmem_*".        |

|     |                                  |        | - Renamed the "ram_*" ports to "dmem_*".        |

|     |                                  |        | - Renamed the "ROM_AWIDTH" Verilog              |

|     |                                  |        | define to "PMEM_AWIDTH".                        |

|     |                                  |        | - Renamed the "RAM_AWIDTH" Verilog              |

|     |                                  |        | define to "DMEM_AWIDTH".                        |

|     |                                  |        | - Prefixed all the verilog sub-modules of the   |

|     |                                  |        | openMSP430 core with "omsp_".                   |

|     |                                  |        | - Diverse minor updates                         |

| 1.4 | January 12 <sup>th</sup> , 2010  | GIRARD | - Added the "Integration and                    |

|     |                                  |        | Connectivity"section.                           |

|     |                                  |        |                                                 |

|     |                                  |        |                                                 |

|     |                                  |        |                                                 |

|     |                                  |        |                                                 |

## **Contents**

| 1. OVERVIEW                       | <u>1</u>  |

|-----------------------------------|-----------|

| 2. CORE                           | <u>3</u>  |

| 3. SERIAL DEBUG INTERFACE         | <u>15</u> |

| 4. INTEGRATION AND CONNECTIVITY   | <u>27</u> |

| 5. SOFTWARE DEVELOPMENT TOOLS     | <u>39</u> |

| 6. FILE AND DIRECTORY DESCRIPTION | 48        |

## **Overview**

## Introduction

The openMSP430 is a synthesizable 16bit microcontroller core written in Verilog. It is compatible with Texas Instruments' MSP430 microcontroller family and can execute the code generated by an MSP430 toolchain in a cycle accurate way.

The core comes with some peripherals (GPIO, Timer A, generic templates) and a Serial Debug Interface for in-system software development.

## **Download**

Click <u>here</u> to download the complete tar archive of the project (OpenCores account required).

The following SVN command can be run from a console (or <u>GUI</u>):

svn export http://opencores.org/ocsvn/openmsp430/openmsp430/trunk/ openmsp430

To keep yourself informed about project updates, you can subscribe to the following <u>RSS</u> feed.

## **Features & Limitations**

## **Features**

- Core:

- Full instruction set support.

- All addressing modes are supported.

- IRQ and NMI support.

- Power saving modes functionality is supported.

- Configurable memory size for both program and data.

- Serial Debug Interface (Nexus class 3).

- FPGA friendly (single clock domain, no clock gate).

- Small size (uses ~43% of a XC3S200 Xilinx Spartan-3).

#### • Peripherals:

- · Basic Clock Module.

- Watchdog.

- Timer A.

- GPIO (port 1 to 6).

### Limitations

- Core:

- Instructions can't be executed from the data memory.

- · Peripherals:

- Basic clock module doesn't offer the full functionality of a real MSP430.

## Links

Development has been performed using the following freely available (excellent) tools:

- <u>Icarus Verilog</u>: Verilog simulator.

- GTKWave Analyzer: Waveform viewer.

- MSPGCC: GCC toolchain for the Texas Instruments MSP430 MCUs.

- ISE WebPACK: Xilinx's FPGA synthesis tool.

#### A few MSP430 links:

- Wikipedia: MSP430

- TI: MSP430x1xx Family User's Guide

## Legal information

MSP430 is a trademark of Texas Instruments, Inc. This project is not affiliated in any way with Texas Instruments. All other product names are trademarks or registered trademarks of their respective owners.

## 2.

## Core

#### Table of content

- 1. Introduction

- 2. Design

- <u>2.1 Core</u>

- 2.1.1 Design structure

- 2.1.2 Limitations

- 2.1.3 Configuration

- 2.1.4 Pinout

- 2.1.5 Instruction Cycles and Lengths

- 2.1.6 Serial Debug Interface

- 2.2 Peripherals

- 2.2.1 Basic Clock Module

- 2.2.2 Watchdog Timer

- 2.2.3 Digital I/O

- 2.2.4 Timer A

## 1. Introduction

The openMSP430 is a 16-bit microcontroller core compatible with TI's MSP430 family (note that the extended version of the architecture, the MSP430X, isn't supported by this IP). It is based on a Von Neumann architecture, with a single address space for instructions and data.

This design has been implemented to be FPGA friendly. Therefore, the core doesn't contain any clock gate and has only a single clock domain. As a consequence, the clock management block has a few limitations.

This IP doesn't contain the instruction and data memory blocks internally (these are technology dependent hard macros which are connected to the IP during chip

integration). However the core is fully configurable in regard to the supported RAM and/or ROM sizes.

In addition to the CPU core itself, several peripherals are also provided and can be easily connected to the core during integration.

## 2. Design

## **2.1** Core

#### 2.1.1 Design structure

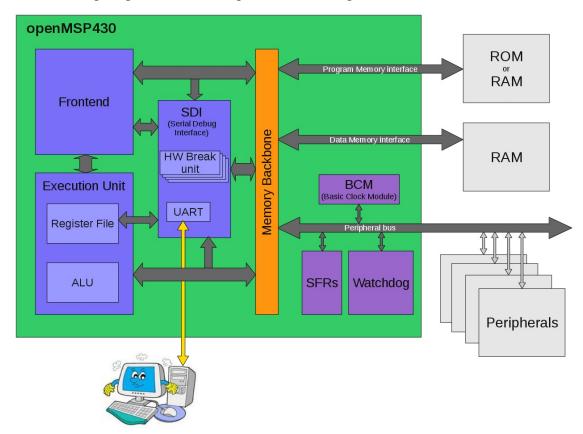

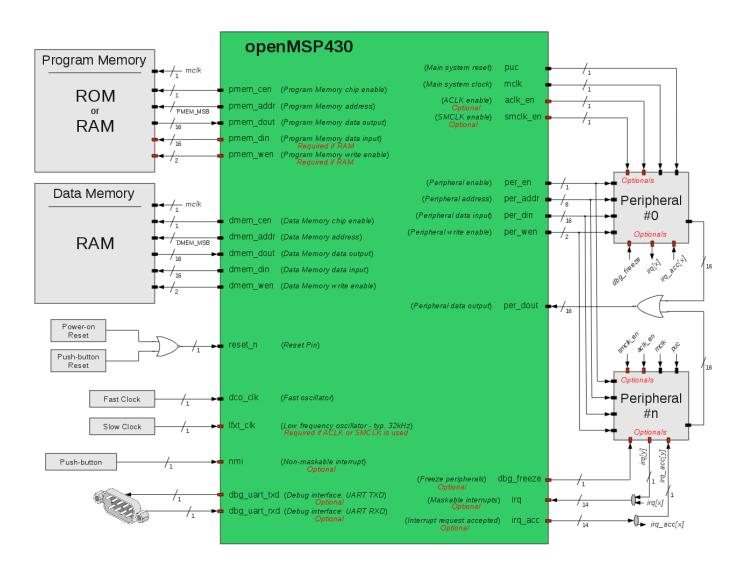

The following diagram shows the openMSP430 design structure:

- **Frontend**: This module performs the instruction Fetch and Decode tasks. It also contains the execution state machine.

- **Execution unit**: Containing the ALU and the register file, this module executes the current decoded instruction according to the execution state.

- **Serial Debug Interface**: Contains all the required logic for a Nexus class 3 debugging unit (without trace). Communication with the host is done with a standard 8N1 serial interface.

- **Memory backbone**: This block performs a simple arbitration between the frontend and execution-unit for program, data and peripheral memory access.

- **Basic Clock Module**: Generates the ACLK and SMCLK enable signals.

- SFRs: The Special Function Registers block contains diverse configuration registers (NMI, Watchdog, ...).

- **Watchdog**: Although it is a peripheral, the watchdog is permanently included in the core because of its tight links with the NMI interrupts and the PUC reset generation.

#### 2.1.2 Limitations

The known core limitations are the following:

- Instructions can't be executed from the data memory.

- SCG0 is not implemented (turns off DCO).

- MCLK can't be divided and can only have DCO\_CLK as source (see <u>Basic Clock Module</u> section).

#### 2.1.3 Configuration

It is possible to configure the openMSP430 core through the "openMSP430\_defines.v" file located in the *rtl* directory (see <u>file and directory description</u>).

Two parameters can be adjusted by the user in order to define the program and data memory sizes:

```

// Program Memory Size

// 9 -> 1 kB

// 10 -> 2 kB

// 11 -> 4 kB

// 12 -> 8 kB

// 13 -> 16 kB

// 14 -> 32 kB

`define PMEM_AWIDTH 10

// Data Memory Size

// 6 -> 128 B

// 7 -> 256 B

// 8 -> 512 B

// 9 -> 1 kB

// 10 -> 2 kB

// 10 -> 2 kB

// 11 -> 4 kB

// 12 -> 8 kB

// 13 -> 16 kB

// 12 -> 8 kB

// 13 -> 16 kB

// 13 -> 16 kB

// 14 -> 32 kB

`define DMEM_AWIDTH 6

```

**Note:** Program and data memories **SHOULD NOT** be both set to 32 kB.

The following parameters define if the debug interface should be included or not and how many hardware breakpoint units should be included.

```

// REMOTE DEBUGGING INTERFACE CONFIGURATION

// Include Debug interface

`define DBG EN

// Debug interface selection

// `define DBG_UART -> Enable UART (8N1) debug interface

// `define DBG_JTAG -> DON'T UNCOMMENT, NOT SUPPORTED

`define DBG UART

//`define DBG JTAG

// Number of hardware breakpoints (each unit contains 2 hw address breakpoints)

// `define DBG_HWBRK_0 -> Include hardware breakpoints unit 0

// `define DBG_HWBRK_1 -> Include hardware breakpoints unit 1

// `define DBG_HWBRK_2 -> Include hardware breakpoints unit 2

// `define DBG_HWBRK_3 -> Include hardware breakpoints unit 3

`define DBG HWBRK 0

`define DBG_HWBRK_1

`define DBG_HWBRK_2

`define DBG_HWBRK_3

```

**Note:** Since the hardware breakpoint units are relatively big, it is recommended to include as many as you plan to use. These units are particularly useful if your instruction memory is a ROM (i.e. when you can't use software breakpoints) or if you want to be able to stop the CPU whenever some particular data addresses are accessed.

All remaining defines located in this file are system constants and should not be edited.

#### **2.1.4 Pinout**

The full pinout of the openMSP430 core is provided in the following table:

| Port Name | Direction | Width | Description                             |  |  |

|-----------|-----------|-------|-----------------------------------------|--|--|

|           | Clocks    |       |                                         |  |  |

| dco_clk   | Input     | 1     | Fast oscillator (fast clock), CPU clock |  |  |

| lfxt_clk  | Input     | 1     | Low frequency oscillator (typ. 32kHz)   |  |  |

| mclk      | Output    | 1     | Main system clock                       |  |  |

| aclk_en   | Output    | 1     | ACLK enable                             |  |  |

| smclk_en  | Output    | 1     | SMCLK enable                            |  |  |

| Resets    |           |       |                                         |  |  |

| puc          | Output  | 1                         | Main system reset                                                 |  |  |  |

|--------------|---------|---------------------------|-------------------------------------------------------------------|--|--|--|

| reset_n      | Input 1 |                           | Reset Pin (low active)                                            |  |  |  |

| Interrupts   |         |                           |                                                                   |  |  |  |

| irq          | Input   | 14                        | Maskable interrupts (one-hot signal)                              |  |  |  |

| nmi          | Input   | 1                         | Non-maskable interrupt (asynchronous)                             |  |  |  |

| irq_acc      | Output  | 14                        | Interrupt request accepted (one-hot signal)                       |  |  |  |

|              |         | Program M                 | emory interface                                                   |  |  |  |

| pmem_addr    | Output  | `PMEM_AWIDTH <sup>1</sup> | Program Memory address                                            |  |  |  |

| pmem_cen     | Output  | 1                         | Program Memory chip enable (low active)                           |  |  |  |

| pmem_din     | Output  | 16                        | Program Memory data input (optional <sup>2</sup> )                |  |  |  |

| pmem_dout    | Input   | 16                        | Program Memory data output                                        |  |  |  |

| pmem_wen     | Output  | 2                         | Program Memory write enable (low active) (optional <sup>2</sup> ) |  |  |  |

|              |         | Data Men                  | nory interface                                                    |  |  |  |

| dmem_addr    | Output  | `DMEM_AWIDTH <sup>1</sup> | Data Memory address                                               |  |  |  |

| dmem_cen     | Output  | 1                         | Data Memory chip enable (low active)                              |  |  |  |

| dmem_din     | Output  | 16                        | Data Memory data input                                            |  |  |  |

| dmem_dout    | Input   | 16                        | Data Memory data output                                           |  |  |  |

| dmem_wen     | Output  | 2                         | Data Memory write enable (low active)                             |  |  |  |

|              |         | External Per              | ipherals interface                                                |  |  |  |

| per_addr     | Output  | 8                         | Peripheral address                                                |  |  |  |

| per_din      | Output  | 16                        | Peripheral data input                                             |  |  |  |

| per_dout     | Input   | 16                        | Peripheral data output                                            |  |  |  |

| per_en       | Output  | 1                         | Peripheral enable (high active)                                   |  |  |  |

| per_wen      | Output  | 2                         | Peripheral write enable (high active)                             |  |  |  |

|              |         | Serial De                 | bug interface                                                     |  |  |  |

| dbg_freeze   | Output  | 1                         | Freeze peripherals                                                |  |  |  |

| dbg_uart_txd | Output  | 1                         | Debug interface: UART TXD                                         |  |  |  |

| dbg_uart_rxd | Input   | 1                         | Debug interface: UART RXD                                         |  |  |  |

$<sup>^1\!\!:</sup>$  This parameter is declared in the "openMSP430\_defines.v" file and defines the RAM/ROM size.

<sup>2</sup>: These two optional ports can be connected whenever the program memory is a RAM. This will allow the user to load a program through the serial debug interface and to use software breakpoints.

#### 2.1.5 Instruction Cycles and Lengths

The number of CPU clock cycles required for an instruction depends on the instruction format and the addressing modes used, not the instruction itself.

In the following tables, the number of cycles refers to the main clock (MCLK). Differences with the original MSP430 are highlighted in green (the original value being red).

#### • Interrupt and Reset Cycles

| Action                       | No. of Cycles | <b>Length of Instruction</b> |

|------------------------------|---------------|------------------------------|

| Return from interrupt (RETI) | 5             | 1                            |

| Interrupt accepted           | 6             | _                            |

| WDT reset                    | 4             | -                            |

| Reset (!RST/NMI)             | 4             | -                            |

#### • Format-II (Single Operand) Instruction Cycles and Lengths

| Addressing Mode | No. of Cycle        | Longth of Instruction |       |                       |  |

|-----------------|---------------------|-----------------------|-------|-----------------------|--|

| Addressing Mode | RRA, RRC, SWPB, SXT | PUSH CALL             |       | Length of Instruction |  |

| Rn              | 1                   | 3                     | 3 (4) | 1                     |  |

| @Rn             | 3                   | 4                     | 4     | 1                     |  |

| @Rn+            | 3                   | 4 (5)                 | 4 (5) | 1                     |  |

| #N              | N/A                 | 4                     | 5     | 2                     |  |

| X(Rn)           | 4                   | 5                     | 5     | 2                     |  |

| EDE             | 4                   | 5                     | 5     | 2                     |  |

| &EDE            | 4                   | 5                     | 5     | 2                     |  |

#### • Format-III (Jump) Instruction Cycles and Lengths

All jump instructions require one code word, and take two CPU cycles to execute, regardless of whether the jump is taken or not.

## • Format-I (Double Operand) Instruction Cycles and Lengths

| <b>Addressing Mode</b> |       | No. of Cycles | Length of Instruction |  |

|------------------------|-------|---------------|-----------------------|--|

| Src                    | Dst   | No. of Cycles | Length of that action |  |

|                        | Rm    | 1             | 1                     |  |

|                        | PC    | 2             | 1                     |  |

| Rn                     | x(Rm) | 4             | 2                     |  |

|                        | EDE   | 4             | 2                     |  |

|                        | &EDE  | 4             | 2                     |  |

|                        | Rm    | 2             | 1                     |  |

|                        | PC    | 3 (2)         | 1                     |  |

| @Rn                    | x(Rm) | 5             | 2                     |  |

|                        | EDE   | 5             | 2                     |  |

|                        | &EDE  | 5             | 2                     |  |

|                        | Rm    | 2             | 1                     |  |

|                        | PC    | 3             | 1                     |  |

| @Rn+                   | x(Rm) | 5             | 2                     |  |

|                        | EDE   | 5             | 2                     |  |

|                        | &EDE  | 5             | 2                     |  |

|                        | Rm    | 2             | 2                     |  |

|                        | PC    | 3             | 2                     |  |

| #N                     | x(Rm) | 5             | 3                     |  |

|                        | EDE   | 5             | 3                     |  |

|                        | &EDE  | 5             | 3                     |  |

|                        | Rm    | 3             | 2                     |  |

|                        | PC    | 3 (4)         | 2                     |  |

| x(Rn)                  | x(Rm) | 6             | 3                     |  |

|                        | EDE   | 6             | 3                     |  |

|                        | &EDE  | 6             | 3                     |  |

| EDE                    | Rm    | 3             | 2                     |  |

|                        | PC    | 3 (4)         | 2                     |  |

|                        | x(Rm) | 6             | 3                     |  |

|      | EDE   | 6 | 3 |

|------|-------|---|---|

|      | &EDE  | 6 | 3 |

|      | Rm    | 3 | 2 |

|      | PC    | 3 | 2 |

| &EDE | x(Rm) | 6 | 3 |

|      | EDE   | 6 | 3 |

|      | &EDE  | 6 | 3 |

### 2.1.6 Serial Debug Interface

All the details about the Serial Debug Interface are located here.

## 2.2 Peripherals

In addition to the CPU core itself, several peripherals are also provided and can be easily connected to the core during integration.

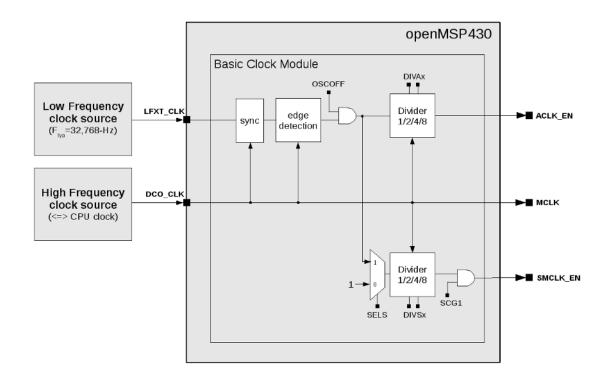

#### 2.2.1 Basic Clock Module

In order to make an FPGA implementation as simple as possible (ideally, a non-designer should be able to do it), clock gates are not used in the design and neither are clock muxes.

With these constrains, the Basic Clock Module is implemented as following:

**Note**: CPUOFF doesn't switch MCLK off and will instead bring the CPU state machines in an IDLE state while MCLK will still be running.

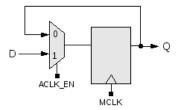

In order to 'clock' a register with ACLK or SMCLK, the following structure needs to be implemented:

The following Verilog code would implement a counter clocked with SMCLK:

```

reg [7:0] test_cnt;

always @ (posedge mclk or posedge puc)

if (puc) test_cnt <= 8'h00;</pre>

```

```

else if (smclk_en) test_cnt <= test_cnt + 8'h01;</pre>

```

#### **Register Description**

- DCOCTL: Not implemented

- BCSCTL1:

- BCSCTL1[7:6]: Unused

- BCSCTL1[5:4]: DIVAx

- BCSCTL1[4:0]: Unused

- BCSCTL2:

- BCSCTL2[7:4]: Unused

- BCSCTL2[3] : SELS

- BCSCTL2[2:1]: DIVSx

- BCSCTL2[0] : Unused

#### 2.2.2 Watchdog Timer

100% of the features advertised in the MSP430x1xx Family User's Guide (Chapter 10) have been implemented.

### 2.2.3 Digital I/O

100% of the features advertised in the MSP430x1xx Family User's Guide (Chapter 9) have been implemented.

The following Verilog parameters will enable or disable the corresponding ports in order to save area (i.e. FPGA utilization):

```

parameter P1_EN = 1'b1; // Enable Port 1

parameter P2_EN = 1'b1; // Enable Port 2

parameter P3_EN = 1'b0; // Enable Port 3

parameter P4_EN = 1'b0; // Enable Port 4

parameter P5_EN = 1'b0; // Enable Port 5

parameter P6_EN = 1'b0; // Enable Port 6

```

They can be updated as following during the module instantiation (here port 1, 2 and 3 are enabled):

The full pinout of the GPIO module is provided in the following table:

| Port Name  | Direction       | Width     | Description                           |  |  |  |

|------------|-----------------|-----------|---------------------------------------|--|--|--|

|            | Clocks & Resets |           |                                       |  |  |  |

| mclk       | Input           | 1         | Main system clock                     |  |  |  |

| puc        | Input           | 1         | Main system reset                     |  |  |  |

|            |                 | In        | terrupts                              |  |  |  |

| irq_port1  | Output          | 1         | Port 1 interrupt                      |  |  |  |

| irq_port2  | Output          | 1         | Port 2 interrupt                      |  |  |  |

|            | Exte            | ernal Per | ripherals interface                   |  |  |  |

| per_addr   | Input           | 8         | Peripheral address                    |  |  |  |

| per_din    | Input           | 16        | Peripheral data input                 |  |  |  |

| per_dout   | Output          | 16        | Peripheral data output                |  |  |  |

| per_en     | Input           | 1         | Peripheral enable (high active)       |  |  |  |

| per_wen    | Input           | 2         | Peripheral write enable (high active) |  |  |  |

|            |                 |           | Port 1                                |  |  |  |

| p1_din     | Input           | 8         | Port 1 data input                     |  |  |  |

| p1_dout    | Output          | 8         | Port 1 data output                    |  |  |  |

| p1_dout_en | Output          | 8         | Port 1 data output enable             |  |  |  |

| p1_sel     | Output          | 8         | Port 1 function select                |  |  |  |

|            |                 |           | Port 2                                |  |  |  |

| p2_din     | Input           | 8         | Port 2 data input                     |  |  |  |

| p2_dout    | Output          | 8         | Port 2 data output                    |  |  |  |

| p2_dout_en | Output          | 8         | Port 2 data output enable             |  |  |  |

| p2_sel     | Output          | 8         | Port 2 function select                |  |  |  |

|            |                 |           | Port 3                                |  |  |  |

| p3_din     | Input           | 8         | Port 3 data input                     |  |  |  |

| p3_dout    | Output          | 8         | Port 3 data output                    |  |  |  |

| p3_dout_en | Output | 8 | Port 3 data output enable |

|------------|--------|---|---------------------------|

|            |        |   | 1                         |

| p3_sel     | Output | 8 | Port 3 function select    |

|            |        |   | Port 4                    |

| p4_din     | Input  | 8 | Port 4 data input         |

| p4_dout    | Output | 8 | Port 4 data output        |

| p4_dout_en | Output | 8 | Port 4 data output enable |

| p4_sel     | Output | 8 | Port 4 function select    |

|            |        |   | Port 5                    |

| p5_din     | Input  | 8 | Port 5 data input         |

| p5_dout    | Output | 8 | Port 5 data output        |

| p5_dout_en | Output | 8 | Port 5 data output enable |

| p5_sel     | Output | 8 | Port 5 function select    |

|            |        |   | Port 6                    |

| p6_din     | Input  | 8 | Port 6 data input         |

| p6_dout    | Output | 8 | Port 6 data output        |

| p6_dout_en | Output | 8 | Port 6 data output enable |

| p6_sel     | Output | 8 | Port 6 function select    |

## **2.2.4** Timer A

100% of the features advertised in the MSP430x1xx Family User's Guide (Chapter 11) have been implemented.

The full pinout of the Timer A module is provided in the following table:

| Port Name  | Direction              | Width | Description                       |  |  |  |

|------------|------------------------|-------|-----------------------------------|--|--|--|

|            | Clocks, Resets & Debug |       |                                   |  |  |  |

| mclk       | Input                  | 1     | Main system clock                 |  |  |  |

| aclk_en    | Input                  | 1     | ACLK enable (from CPU)            |  |  |  |

| smclk_en   | Input                  | 1     | SMCLK enable (from CPU)           |  |  |  |

| inclk      | Input                  | 1     | INCLK external timer clock (SLOW) |  |  |  |

| taclk      | Input                  | 1     | TACLK external timer clock (SLOW) |  |  |  |

| puc        | Input                  | 1     | Main system reset                 |  |  |  |

| dbg_freeze | Input                  | 1     | Freeze Timer A counter            |  |  |  |

| Interrupts             |        |        |                                         |  |  |

|------------------------|--------|--------|-----------------------------------------|--|--|

| irq_ta0                | Output | 1      | Timer A interrupt: TACCR0               |  |  |

| irq_ta1                | Output | 1      | Timer A interrupt: TAIV, TACCR1, TACCR2 |  |  |

| irq_ta0_acc            | Input  | 1      | Interrupt request TACCR0 accepted       |  |  |

|                        |        | Extern | al Peripherals interface                |  |  |

| per_addr               | Input  | 8      | Peripheral address                      |  |  |

| per_din                | Input  | 16     | Peripheral data input                   |  |  |

| per_dout               | Output | 16     | Peripheral data output                  |  |  |

| per_en                 | Input  | 1      | Peripheral enable (high active)         |  |  |

| per_wen                | Input  | 2      | Peripheral write enable (high active)   |  |  |

|                        |        | Cap    | ture/Compare Unit 0                     |  |  |

| ta_cci0a               | Input  | 1      | Timer A capture 0 input A               |  |  |

| ta_cci0b               | Input  | 1      | Timer A capture 0 input B               |  |  |

| ta_out0                | Output | 1      | Timer A output 0                        |  |  |

| ta_out0_en             | Output | 1      | Timer A output 0 enable                 |  |  |

|                        |        | Cap    | ture/Compare Unit 1                     |  |  |

| ta_cci1a               | Input  | 1      | Timer A capture 1 input A               |  |  |

| ta_cci1b               | Input  | 1      | Timer A capture 1 input B               |  |  |

| ta_out1                | Output | 1      | Timer A output 1                        |  |  |

| ta_out1_en             | Output | 1      | Timer A output 1 enable                 |  |  |

| Capture/Compare Unit 2 |        |        |                                         |  |  |

| ta_cci2a               | Input  | 1      | Timer A capture 2 input A               |  |  |

| ta_cci2b               | Input  | 1      | Timer A capture 2 input B               |  |  |

| ta_out2                | Output | 1      | Timer A output 2                        |  |  |

| ta_out2_en             | Output | 1      | Timer A output 2 enable                 |  |  |

**Note**: for the same reason as with the Basic Clock Module, the two additional clock inputs (TACLK and INCLK) are internally synchronized with the MCLK domain. As a consequence, TACLK and INCLK should be at least 2 times slowlier than MCLK, and if these clock are used toghether with the Timer A output unit, some jitter might be observed on the generated output. If this jitter is critical for the application, ACLK and INCLK should idealy be derivated from DCO\_CLK.

## **Serial Debug Interface**

#### Table of content

- 1. Introduction

- 2. Debug Unit

- 2.1 Register Mapping

- 2.2 CPU Control/Status Registers

- 2.2.1 CPU ID

- 2.2.2 CPU CTL

- 2.2.3 CPU STAT

- 2.3 Memory Access Registers

- 2.3.1 MEM CTL

- 2.3.2 MEM ADDR

- 2.3.3 MEM DATA

- 2.3.4 MEM CNT

- 2.4 Hardware Breakpoint Unit Registers

- 2.4.1 BRKx CTL

- 2.4.2 BRKx STAT

- 2.4.3 BRKx ADDR0

- 2.4.4 BRKx ADDR1

- 3 Debug Communication Interface: UART

- 3.1 Serial communication protocol: 8N1

- 3.2 Synchronization frame

- 3.3 Read/Write access to the debug registers

- 3.3.1 Command Frame

- 3.3.2 Write access

- 3.3.3 Read access

- 3.4 Read/Write burst implementation for the CPU Memory access

- 3.4.1 Write Burst access

- 3.4.2 Read Burst access

## 1. Introduction

The original MSP430 from TI provides a serial debug interface to give a simple path to software development. In that case, the communication with the host computer is typically build on a JTAG or Spy-Bi-Wire serial protocol. However, the global debug architecture from the MSP430 is unfortunately poorly documented on the web (and is also probably tightly linked with the internal core architecture).

A custom module has therefore been implemented for the openMSP430. The communication with the host is done with a simple RS232 cable (8N1 serial protocol) and the debug unit provides all the required features for Nexus Class 3 debugging (beside trace), namely:

- CPU control (run, stop, step, reset).

- Software & hardware breakpoint support.

- Memory read/write on-the-fly (no need to halt execution).

- CPU registers read/write on-the-fly (no need to halt execution).

## 2. Debug Unit

## 2.1 Register Mapping

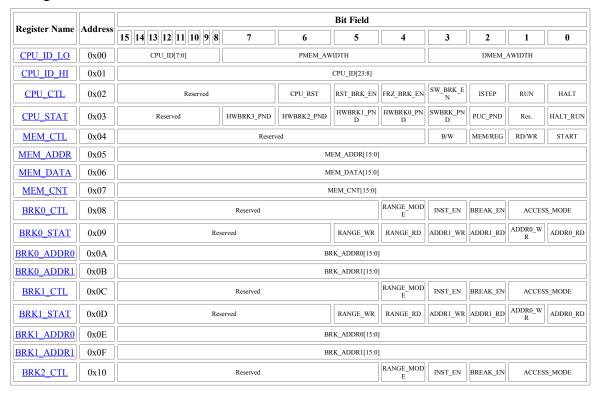

The following table summarize the complete debug register set accessible through the debug communication interface:

| BRK2_STAT  | 0x11 | Reserved        | RANGE_WR      | RANGE_RD       | ADDR1_WR | ADDR1_RD | ADDR0_W<br>R | ADDR0_RD |

|------------|------|-----------------|---------------|----------------|----------|----------|--------------|----------|

| BRK2_ADDR0 | 0x12 | BRK_ADDR0[15:0] |               |                |          |          |              |          |

| BRK2_ADDR1 | 0x13 | BRK_ADDR1[15:0] |               |                |          |          |              |          |

| BRK3_CTL   | 0x14 | Reserved        |               | RANGE_MOD<br>E | INST_EN  | BREAK_EN | ACCES        | S_MODE   |

| BRK3_STAT  | 0x15 | Reserved        | RANGE_WR      | RANGE_RD       | ADDR1_WR | ADDR1_RD | ADDR0_W<br>R | ADDR0_RD |

| BRK3_ADDR0 | 0x16 | BRK_ADDR0[15:0] |               |                |          |          |              |          |

| BRK3_ADDR1 | 0x17 | BR              | K_ADDR1[15:0] |                |          |          |              |          |

## **2.2 CPU Control/Status Registers**

## 2.2.1 CPU\_ID

This 32 bit read-only register holds the ID of the implemented openMSP430 as well as the program and data memory size information.

| Danistan Nama | A .d.d  | Bit Field                             |  |  |  |  |

|---------------|---------|---------------------------------------|--|--|--|--|

| Register Name | Address | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |  |  |  |  |

| CPU_ID_LO     | 0x00    | CPU_ID[7:0] PMEM_AWIDTH DMEM_AWIDTH   |  |  |  |  |

| CPU_ID_HI     | 0x01    | CPU_ID[23:7]                          |  |  |  |  |

• **CPU ID** : Set by default to 0x4D5350 (ascii code for "*MSP*")

• PMEM\_AWIDTH: Program memory address width for the current implementation. The ROM or RAM size is then equal to 2PMEM\_AWIDTH

• **DMEM\_AWIDTH**: Data memory address width for the current implementation. The RAM size is then equal to 2<sup>DMEM\_AWIDTH</sup>

## **2.2.2 CPU\_CTL**

This 8 bit read-write register is used to control the CPU and to configure some basic debug features. After a POR, this register is set to 0x00.

| Dogistor Nome | Address | Bit Field |         |            |            |           |       |     |      |  |  |

|---------------|---------|-----------|---------|------------|------------|-----------|-------|-----|------|--|--|

| Register Name | Address | 7         | 6       | 5          | 4          | 3         | 2     | 1   | 0    |  |  |

| CPU_CTL       | 0x02    | Res.      | CPU_RST | RST_BRK_EN | FRZ_BRK_EN | SW_BRK_EN | ISTEP | RUN | HALT |  |  |

• CPU\_RST : Setting this bit to 1 will activate the PUC reset. Setting it back to

0 will release it.

• RST BRK EN : If set to 1, the CPU will automatically break after a PUC

occurrence.

• FRZ\_BRK\_EN : If set to 1, the timers and watchdog are frozen when the CPU is

halted.

• **SW BRK EN** : Enables the software breakpoint detection.

• ISTEP<sup>1</sup> : Writing 1 to this bit will perform a single instruction step if the

CPU is halted.

•  $RUN^1$  : Writing 1 to this bit will get the CPU out of halt state.

• **HALT**<sup>1</sup> : Writing 1 to this bit will put the CPU in halt state.

#### **2.2.3 CPU STAT**

This 8 bit read-write register gives the global status of the debug interface. After a POR, this register is set to 0x00.

| Dogistor Nome | Address               |            | Bit Field  |            |            |           |         |      |          |  |  |

|---------------|-----------------------|------------|------------|------------|------------|-----------|---------|------|----------|--|--|

| Register Name | Register Name Address | 7          | 6          | 5          | 4          | 3         | 2       | 1    | 0        |  |  |

| CPU_STAT      | 0x03                  | HWBRK3_PND | HWBRK2_PND | HWBRK1_PND | HWBRK0_PND | SWBRK_PND | PUC_PND | Res. | HALT_RUN |  |  |

• HWBRK3\_PND : This bit reflects if one of the Hardware Breakpoint Unit 3 status

bit is set (i.e. BRK3\_STAT≠0).

• HWBRK2\_PND : This bit reflects if one of the Hardware Breakpoint Unit 2 status

bit is set (i.e. BRK2\_STAT≠0).

• HWBRK1 PND : This bit reflects if one of the Hardware Breakpoint Unit 1 status

bit is set (i.e. BRK1 STAT≠0).

• HWBRK0 PND : This bit reflects if one of the Hardware Breakpoint Unit 0 status

bit is set (i.e. BRK0 STAT≠0).

• **SWBRK PND** : This bit is set to 1 when a software breakpoint occurred. It can be

cleared by writing 1 to it.

• PUC PND : This bit is set to 1 when a PUC reset occurred. It can be cleared

by writing 1 to it.

• **HALT RUN** : This read-only bit gives the current status of the CPU:

**0** - CPU is running.

1 - CPU is stopped.

<sup>1:</sup>this field is write-only and always reads back 0.

## 2.3 Memory Access Registers

The following four registers enable single and burst read/write access to both CPU-Registers and full memory address range.

In order to perform an access, the following sequences are typically done:

- single read access (MEM\_CNT=0):

- 1. set MEM ADDR with the memory address (or register number) to be read

- 2. set MEM\_CTL (in particular RD/WR=0 and START=1)

- 3. read MEM DATA

- single write access (MEM\_CNT=0):

- set MEM\_ADDR with the memory address (or register number) to be written

- 2. set MEM DATA with the data to be written

- 3. set MEM CTL (in particular RD/WR=1 and START=1)

- burst read/write access (MEM CNT≠0):

- burst access are optimized for the communication interface used (i.e. for the UART). The burst sequence are therefore described in the corresponding section (3.4 Read/Write burst implementation for the CPU Memory access)

#### **2.3.1** MEM\_CTL

This 8 bit read-write register is used to control the Memory and CPU-Register read/write access. After a POR, this register is set to 0x00.

| Dogistov Nomo | Address | Bit Field |     |         |       |       |  |  |  |

|---------------|---------|-----------|-----|---------|-------|-------|--|--|--|

| Register Name | Auuress | 7 6 5 4   | 3   | 2       | 1     | 0     |  |  |  |

| MEM_CTL       | 0x04    | Reserved  | B/W | MEM/REG | RD/WR | START |  |  |  |

- **B/W** : **0** 16 bit access.

- 1 8 bit access (not valid for CPU-Registers).

- MEM/REG : 0 Memory access.

- 1 CPU-Register access.

- **RD/WR** : **0** Read access.

- 1 Write access.

- START : 0- Do nothing

- 1 Initiate memory transfer.

#### **2.3.2 MEM\_ADDR**

This 16 bit read-write register specifies the Memory or CPU-Register address to be used for the next read/write transfer. After a POR, this register is set to 0x0000.

**Note:** in case of burst (i.e. MEM\_CNT\neq 0), this register specifies the first address of the burst transfer and will be incremented automatically as the burst goes (by 1 for 8-bit access and by 2 for 16-bit access).

| Dogistov Nama | A ddmogg | Bit Field                             |

|---------------|----------|---------------------------------------|

| Register Name | Address  | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

| MEM_ADDR      | 0x05     | MEM_ADDR[15:0]                        |

• **MEM\_ADDR** : Memory or CPU-Register address to be used for the next read/write transfer.

#### **2.3.3 MEM\_DATA**

This 16 bit read-write register specifies (wr) or receive (rd) the Memory or CPU-Register data for the the next transfer. After a POR, this register is set to 0x0000.

| D . A NI      |         | Bit Field                             |

|---------------|---------|---------------------------------------|

| Register Name | Address | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

| MEM_DATA      | 0x06    | MEM_DATA[15:0]                        |

• **MEM\_DATA** : if MEM\_CTL.WR - data to be written during the next write transfer.

if MEM CTL.RD - updated with the data from the read transfer

### **2.3.4 MEM CNT**

This 16 bit read-write register controls the burst access to the Memory or CPU-Registers. If set to 0, a single access will occur, otherwise, a burst will be performed. The burst being optimized for the communication interface, more details are given there. After a POR, this register is set to 0x0000.

| Dogistar Nama | Address | Bit Field                             |

|---------------|---------|---------------------------------------|

| Register Name | Audress | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

| MEM_CNT       | 0x07    | MEM_CNT[15:0]                         |

• MEM CNT : =0 - a single access will be performed with the next transfer.

$\neq 0$  - specifies the burst size for the next transfer (i.e number of data access). This field will be automatically decremented as the burst goes.

## 2.4 Hardware Breakpoint Unit Registers

Depending on the <u>defines</u> located in the "openMSP430\_defines.v" file, up to four hardware breakpoint units can be included in the design. These units can be individually controlled with the following registers.

### 2.4.1 BRKx\_CTL

This 8 bit read-write register controls the hardware breakpoint unit x. After a POR, this register is set to 0x00.

| Dogistov Name | Addusss                   | Address Bit Field |            |         |          |       |         |  |  |

|---------------|---------------------------|-------------------|------------|---------|----------|-------|---------|--|--|

| Register Name | Address                   | 7 6 5             | 4          | 3       | 2        | 1     | 0       |  |  |

| BRKx_CTL      | 0x08, 0x0C,<br>0x10, 0x14 | Reserved          | RANGE_MODE | INST_EN | BREAK_EN | ACCES | SS_MODE |  |  |

• RANGE\_MODE : 0 - Address match on BRK\_ADDR0 or BRK\_ADDR1 (normal

mode)

1 - Address match on BRK\_ADDR0→BRK\_ADDR1 range

(range mode)

• **INST\_EN** : **0** - Checks are done on the execution unit (data flow).

1 - Checks are done on the frontend (instruction flow).

• **BREAK EN** : **0** - Watchpoint mode enable (don't stop on address match).

1 - Breakpoint mode enable (stop on address match).

• ACCESS MODE : 00 - Disabled

01 - Detect read access.

10 - Detect write access.

11 - Detect read/write access

Note: '10' & '11' modes are not supported on the instruction flow

#### 2.4.2 BRKx STAT

This 8 bit read-write register gives the status of the hardware breakpoint unit x. Each status bit can be cleared by writing 1 to it. After a POR, this register is set to 0x00.

| Dagistar Nama | Address                   | Bit Field |      |          |          |          |          |          |          |

|---------------|---------------------------|-----------|------|----------|----------|----------|----------|----------|----------|

| Register Name | Address                   | 7         | 6    | 5        | 4        | 3        | 2        | 1        | 0        |

| BRKx_STAT     | 0x09, 0x0D,<br>0x11, 0x15 | Rese      | rved | RANGE_WR | RANGE_RD | ADDR1_WR | ADDR1_RD | ADDR0_WR | ADDR0_RD |

- RANGE\_WR: This bit is set whenever the CPU performs a write access within the BRKx\_ADDR0→BRKx\_ADDR1 range (valid if RANGE\_MODE=1 and ACCESS MODE[1]=1).

- RANGE\_RD : This bit is set whenever the CPU performs a read access within the BRKx\_ADDR0→BRKx\_ADDR1 range (valid if RANGE\_MODE=1 and ACCESS MODE[0]=1).

- ADDR1\_WR: This bit is set whenever the CPU performs a write access at the BRKx\_ADDR1 address (valid if RANGE\_MODE=0 and ACCESS MODE[1]=1).

- ADDR1\_RD : This bit is set whenever the CPU performs a read access at the BRKx\_ADDR1 address (valid if RANGE\_MODE=0 and ACCESS MODE[0]=1).

- ADDR0\_WR: This bit is set whenever the CPU performs a write access at the BRKx\_ADDR0 address (valid if RANGE\_MODE=0 and ACCESS\_MODE[1]=1).

- ADDR0\_RD : This bit is set whenever the CPU performs a read access at the BRKx\_ADDR0 address (valid if RANGE\_MODE=0 and ACCESS MODE[0]=1).

## 2.4.3 BRKx\_ADDR0

This 16 bit read-write register holds the value which is compared against the address value currently present on the program or data address bus. After a POR, this register is set to 0x0000.

| Register Name | Address                   | Bit Field  15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|---------------|---------------------------|--------------------------------------------------|

| BRKx_ADDR0    | 0x0A, 0x0E,<br>0x12, 0x16 | BRK_ADDR0[15:0]                                  |

• **BRK\_ADDR0** : Value compared against the address value currently present on the program or data address bus.

#### **2.4.4 BRKx ADDR1**

This 16 bit read-write register holds the value which is compared against the address value currently present on the program or data address bus. After a POR, this register is set to 0x0000.

| Register Name | Addresses                 | Bit Field  15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|---------------|---------------------------|--------------------------------------------------|

| BRKx_ADDR1    | 0x0B, 0x0F,<br>0x13, 0x17 | BRK_ADDR1[15:0]                                  |

• **BRK\_ADDR1** : Value compared against the address value currently present on the program or data address bus.

## 3. Debug Communication Interface: UART

With its UART interface, the openMSP430 debug unit can communicate with the host computer using a simple RS232 cable (connected to the <u>dbg\_uart\_txd</u> and <u>dbg\_uart\_rxd</u> ports of the IP).

Using an standard <u>USB to RS232 adaptor</u>, the interface provides a reliable communication link up to 1,5Mbps.

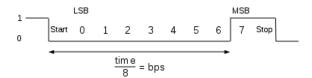

## 3.1 Serial communication protocol: 8N1

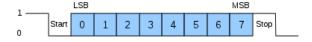

There are plenty tutorials on Internet regarding RS232 based protocols. However, here is quick recap about 8N1 (1 Start bit, 8 Data bits, No Parity, 1 Stop bit):

As you can see in the above diagram, data transmission starts with a Start bit, followed by the data bits (LSB sent first and MSB sent last), and ends with a "Stop" bit.

## 3.2 Synchronization frame

After a POR, the Serial Debug Interface expects a synchronization frame from the host computer in order to determine the communication speed (i.e. the baud rate).

The synchronization frame looks as following:

As you can see, the host simply sends the 0x80 value. The openMSP430 will then measure the time between the falling and rising edge, divide it by 8 and automatically deduce the baud rate it should use to properly communicate with the host.

**Important note**: if you want to change the communication speed between two debugging sessions, the openMSP430 needs to go over a POR cycle and a new synchronization frame needs to be send.

## 3.3 Read/Write access to the debug registers

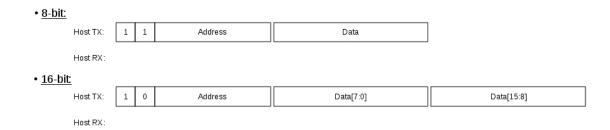

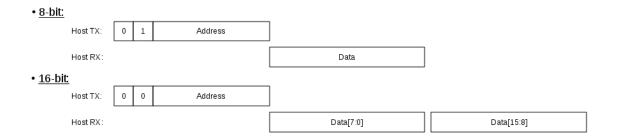

In order to perform a read / write access to a debug register, the host needs to send a command frame to the openMSP430.

In case of write access, this command frame will be followed by 1 or 2 data frames and in case of read access, the openMSP430 will send 1 or 2 data frames after receiving the command.

#### 3.3.1 Command Frame

The command frame looks as following:

| 7  | 6   | 5       | 4 | 3 | 2 | 1 | 0 |

|----|-----|---------|---|---|---|---|---|

| WR | B/W | Address |   |   |   |   |   |

• WR : Perform a Write access when set. Read otherwise.

• B/W : Perform a 8-bit data access when set (one data frame). 16-bit otherwise (two data frame).

• Address: Debug register address.

#### 3.3.2 Write access

A write access transaction looks like this:

#### 3.3.3 Read access

A read access transaction looks like this:

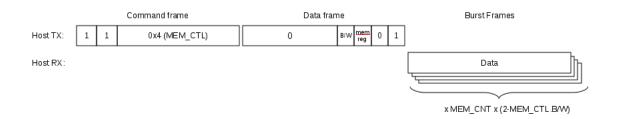

## 3.4 Read/Write burst implementation for the CPU Memory access

In order to optimize the data burst transactions for the UART, read/write access are not done by reading or writing the MEM\_DATA register.

Instead, the data transfer starts immediately after the MEM\_CTL.START bit has been set.

#### 3.4.1 Write Burst access

A write burst transaction looks like this:

## 3.4.2 Read Burst access

A read burst transaction looks like this:

# Integration and Connectivity

### **Table of content**

- <u>1. Overview</u>

- 2. Clocks

- <u>3. Resets</u>

- 4. Program Memory

- <u>5. Data Memory</u>

- <u>6. Peripherals</u>

- 7. Interrupts

- 8. Serial Debug Interface

## 1. Overview

This chapter aims to give a comprehensive description of all openMSP430 core interfaces in order to facilitates its integration within an ASIC or FPGA.

The following diagram shows an overview of the openMSP430 core connectivity:

The full pinout of the core is summarized in the following table.

| Port Name                      | Direction                | Width                     | Description                             |  |  |  |

|--------------------------------|--------------------------|---------------------------|-----------------------------------------|--|--|--|

| Clocks                         |                          |                           |                                         |  |  |  |

| dco_clk                        | Input                    | 1                         | Fast oscillator (fast clock), CPU clock |  |  |  |

| lfxt_clk                       | Input                    | 1                         | Low frequency oscillator (typ. 32kHz)   |  |  |  |

| mclk                           | Output                   | 1                         | Main system clock                       |  |  |  |

| aclk_en                        | Output                   | 1                         | ACLK enable                             |  |  |  |

| smclk_en                       | Output                   | 1                         | SMCLK enable                            |  |  |  |

|                                |                          | Resets                    | S                                       |  |  |  |

| puc                            | Output                   | 1                         | Main system reset                       |  |  |  |

| reset_n                        | Input                    | 1                         | Reset Pin (low active)                  |  |  |  |

|                                | Program Memory interface |                           |                                         |  |  |  |

| pmem_addr                      | Output                   | 'PMEM AWIDTH <sup>1</sup> | Program Memory address                  |  |  |  |

| pmem_cen                       | Output                   | 1                         | Program Memory chip enable (low         |  |  |  |

| pmem_din                       | Output                   | 16                        | Program Memory data input               |  |  |  |

| pmem_dout                      | Input                    | 16                        | Program Memory data output              |  |  |  |

| pmem_wen                       | Output                   | 2                         | Program Memory write enable (low        |  |  |  |

| Data Memory interface          |                          |                           |                                         |  |  |  |

| dmem_addr                      | Output                   | 'DMEM AWIDTH <sup>1</sup> | Data Memory address                     |  |  |  |

| dmem_cen                       | Output                   | 1                         | Data Memory chip enable (low active)    |  |  |  |

| dmem_din                       | Output                   | 16                        | Data Memory data input                  |  |  |  |

| dmem_dout                      | Input                    | 16                        | Data Memory data output                 |  |  |  |

| dmem_wen                       | Output                   | 2                         | Data Memory write enable (low active)   |  |  |  |

| External Peripherals interface |                          |                           |                                         |  |  |  |

| per_addr                       | Output                   | 8                         | Peripheral address                      |  |  |  |

| per_din                        | Output                   | 16                        | Peripheral data input                   |  |  |  |

| per_dout                       | Input                    | 16                        | Peripheral data output                  |  |  |  |

| per_en                         | Output                   | 1                         | Peripheral enable (high active)         |  |  |  |

| per_wen                        | Output                   | 2                         | Peripheral write enable (high active)   |  |  |  |

| Interrupts             |        |                                     |                                       |  |  |

|------------------------|--------|-------------------------------------|---------------------------------------|--|--|

| irq                    | Input  | 14                                  | Maskable interrupts (one-hot signal)  |  |  |

| <u>nmi</u>             | Input  | 1                                   | Non-maskable interrupt (asynchronous) |  |  |

| irq_acc                | Output | Interrupt request accepted (one-hot |                                       |  |  |

| Serial Debug interface |        |                                     |                                       |  |  |

| dbg_freeze             | Output | 1                                   | Freeze peripherals                    |  |  |

| dbg_uart_txd           | Output | 1                                   | Debug interface: UART TXD             |  |  |

| dbg_uart_rxd           | Input  | 1                                   | Debug interface: UART RXD             |  |  |

<sup>&</sup>lt;sup>1</sup>: This parameter is declared in the "openMSP430\_defines.v" file and defines the RAM/ROM size.

## 2. Clocks

The different clocks in the design are managed by the Basic Clock Module:

- DCO\_CLK: this input port is typically connected to a PLL, RC oscillator or any clock resource the target FPGA might provide.

From a synthesis tool perspective (ISE, Quartus, Libero, Design Compiler...), this the only port where a clock needs to be declared.

- LFXT\_CLK: if ACLK\_EN or SMCLK\_EN are going to be used in the project (for example through the Watchdog or TimerA peripherals), then this port needs to be connected to a clock running at least two time slower as DCO\_CLK (typically 32kHz). It can be connected to 0 or 1 otherwise.

- MCLK: the main system clock drives the complete openMSP430 clock domain, including program/data memories and the peripheral interfaces.

- ACLK\_EN / SMCLK\_EN: these two clock enable signals can be used in order to

emulate the original ACLK and SMCLK from the MSP430 specification.

An example of this can be found in the Watchdog and TimerA modules, where it

is implemented as following:

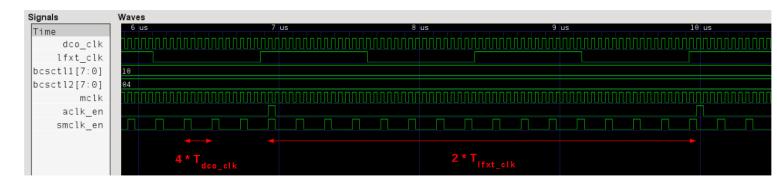

As an illustration, the following waveform shows the different clocks where the software running on the openMSP430 configures the BCSCTL1 and BCSCTL2 registers so that *ACLK\_EN* and *SMCLK\_EN* are respectively running at *LFXT\_CLK/2* and *DCO\_CLK/4*.

#### 3 Resets

- **RESET\_N**: this input port is typically connected to a board push button and is generally combined with the system power-on-reset.

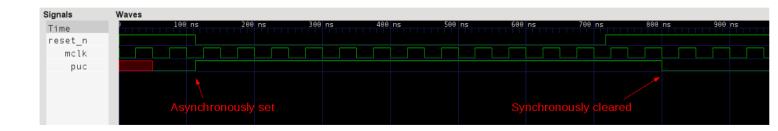

- **PUC**: the Power-Up-Clear signal is asynchronously set with the reset pin (*RESET\_N*), the watchdog reset or the serial debug interface reset. In order to get clean timings, it is synchronously cleared with MCLK's falling edge. As a general rule, this signal should be used as the reset of the *MCLK* clock domain.

The following waveform illustrates this:

## 4. Program Memory

Depending on the project needs, the program memory can be either implemented as a ROM or RAM.

If a ROM is selected then the *PMEM\_DIN* and *PMEM\_WEN* ports won't be connected. In that case, the software debug capabilities are limited because the serial debug interface can only use hardware breakpoints in order to stop the program execution. In addition, updating the software will require a reprogramming of the FPGA.

If the program memory is a RAM, the developer gets full flexibility regarding software debugging. The serial debug interface can be used to update the program memory and software breakpoints can be used.

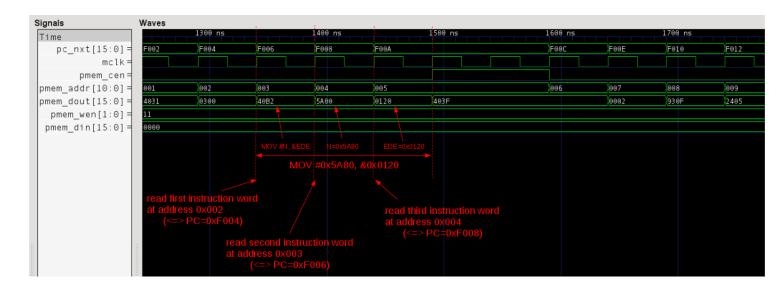

That said, the protocol between the openMSP430 and the program memory is quite standard. Signal description goes as following:

- **PMEM\_CEN**: when this signal is active, the read/write access will be executed with the next *MCLK* rising edge. Note that this signal is LOW ACTIVE.

- **PMEM\_ADDR**: Memory address of the 16 bit word which is going to be accessed.

**Note:** in order to calculate the core logical address from the program memory physical address, the formula goes as following: LOGICAL@=2\*PHYSICAL@+0x10000-PMEM SIZE

- **PMEM\_DOUT**: the memory output word will be updated with every valid read/write access (i.e. *PMEM\_DOUT* is not updated if *PMEM\_CEN*=1).

- PMEM\_WEN: this signal selects which byte should be written during a valid access. PMEM\_WEN[0] will activate a write on the lower byte, PMEM\_WEN[1] a write on the upper byte. Note that these signals are LOW ACTIVE.

- **PMEM\_DIN**: the memory input word will be written with the valid write access according to the *PMEM\_WEN* value.

The following waveform illustrates some read accesses of the program memory (write access are illustrated in the data memory section):

## 5. Data Memory

The data memory is always implemented as a RAM.

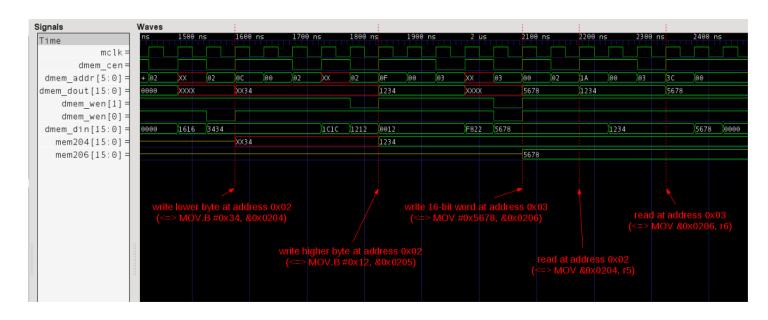

The protocol between the openMSP430 and the data memory is the same as the one of the program memory. Therefore, the signal description is the same:

- **DMEM\_CEN**: when this signal is active, the read/write access will be executed with the next *MCLK* rising edge. Note that this signal is LOW ACTIVE.

- **DMEM\_ADDR**: Memory address of the 16 bit word which is going to be accessed.

**Note:** in order to calculate the core logical address from the data memory physical address, the formula goes as following: LOGICAL@=2\*PHYSICAL@+0x200

- **DMEM\_DOUT**: the memory output word will be updated with every valid read/write access (i.e. *DMEM\_DOUT* is not updated if *DMEM\_CEN*=1).

- DMEM\_WEN: this signal selects which byte should be written during a valid access. DMEM\_WEN[0] will activate a write on the lower byte, DMEM\_WEN[1] a write on the upper byte. Note that these signals are LOW ACTIVE.

- **DMEM\_DIN**: the memory input word will be written with the valid write access according to the *DMEM WEN* value.

The following waveform illustrates some read/write access to the data memory:

### 6. Peripherals

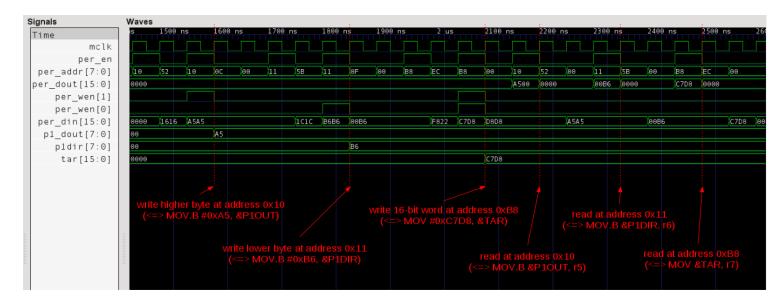

The protocol between the openMSP430 core and its peripherals is the exactly same as the one with the data and program memories in regards to write access and differs slightly for read access.

On the connectivity side, the specificity is that the read data bus of all peripherals should be ORed together before being connected to the core, as showed in the diagram of the <u>Overview</u> section.

From the logical point of view, during a read access, each peripheral outputs the combinatorial value of its read mux and returns 0 if it doesn't contain the addressed register. On the waveforms, this translates by seeing the register value on *PER\_DOUT* while *PER\_EN* is valid and not one clock cycle afterwards as it is the case with the program and data memories.

In any case, it is recommended to use the templates provided with the core in order to develop your own custom peripherals.

The signal description therefore goes as following:

- **PER\_EN**: when this signal is active, read access are executed during the current *MCLK* cycle while write access will be executed with the next *MCLK* rising edge. Note that this signal is HIGH ACTIVE.

- **PER\_ADDR**: peripheral register address of the 16 bit word which is going to be accessed.

- **Note:** in order to calculate the core logical address from the peripheral register physical address, the formula goes as following: *LOGICAL*@=2\**PHYSICAL*@

- **PER\_DOUT**: the peripheral output word will be updated with every valid read/write access, it will be set to 0 otherwise.

- **PER\_WE**: this signal selects which byte should be written during a valid access. PER\_WEN[0] will activate a write on the lower byte, PER\_WEN[1] a write on the upper byte. Note that these signals are HIGH ACTIVE.

- **PER\_DIN**: the peripheral input word will be written with the valid write access according to the *PER\_WEN* value.

The following waveform illustrates some read/write access to the peripheral registers:

# 7. Interrupts

As with the original MSP430, the interrupt priorities of the openMSP430 are fixed in hardware accordingly to the connectivity of the *NMI* and *IRQ* ports. If two interrupts are pending simultaneously, the higher priority interrupt will be serviced first.

The following table summarize this:

| Interrupt Port | Vector address | Priority     |

|----------------|----------------|--------------|

| RESET_N        | 0xFFFE         | 15 (highest) |

| NMI            | 0xFFFC         | 14           |

| IRQ[13]        | 0xFFFA         | 13           |

| IRQ[12]        | 0xFFF8         | 12           |

| IRQ[11]        | 0xFFF6         | 11           |

| IRQ[10]        | 0xFFF4         | 10           |

| IRQ[9]         | 0xFFF2         | 9            |

| IRQ[8]         | 0xFFF0         | 8            |

| IRQ[7]         | 0xFFEE         | 7            |

| IRQ[6] | 0xFFEC | 6          |

|--------|--------|------------|

| IRQ[5] | 0xFFEA | 5          |

| IRQ[4] | 0xFFE8 | 4          |

| IRQ[3] | 0xFFE6 | 3          |

| IRQ[2] | 0xFFE4 | 2          |

| IRQ[1] | 0xFFE2 | 1          |

| IRQ[0] | 0xFFE0 | 0 (lowest) |

The signal description goes as following:

- NMI: The Non-Maskable Interrupt has higher priority than other IRQs and is masked by the NMIIE bit instead of GIE.

It is internally synchronized to the *MCLK* domain and can therefore be connected to any asynchronous signal of the chip (which could for example be a pin of the FPGA). If unused, this signal should be connected to 0.

- **IRQ**: The standard interrupts can be connected to any signal coming from the *MCLK* domain (typically a peripheral). Priorities can be chosen by selecting the proper bit of the *IRQ* bus as shown in the table above. Unused interrupts should be connected to 0.

- **Note**: *IRQ[10]* is internally connected to the Watchdog interrupt. If this bit is also used by an external peripheral, they will both share the same interrupt vector.

- IRQ\_ACC: Whenever an interrupt request is serviced, some peripheral automatically clear their pending flag in hardware. In order to do so, the IRQ\_ACC bus can be used by using the bit matching the corresponding IRQ bit. An example of this is shown in the implementation of the TACCR0 Timer A interrupt.

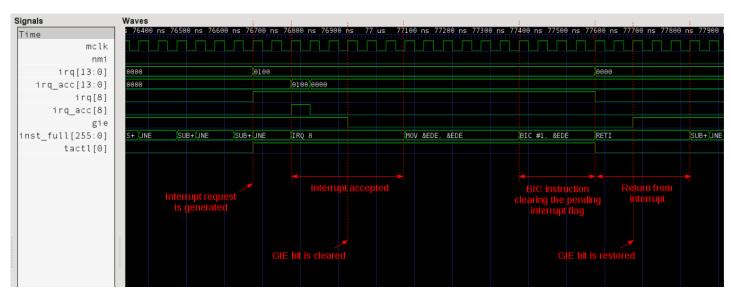

The following waveform illustrates a TAIV interrupt issued by the Timer-A, which is connected to *IRQ[8]*:

### 8. Serial Debug Interface

The serial debug interface module provides a two-wires communication bus for remote debugging and an additional freeze signal which might be useful for some peripherals.

- **DBG\_FREEZE**: this signal will be set whenever the debug interface stops the CPU (and if the *FRZ\_BRK\_EN* field of the <u>CPU\_CTL</u> debug register is set). As its name implies, the purpose of *DBG\_FREEZE* is to freeze a peripheral whenever the CPU is stopped by the software debugger. For example, it is used by the Watchdog timer in order to stop its free-running counter. This prevents the CPU from being reseted by the watchdog every times the user stops the CPU during a debugging session.

- DBG\_UART\_TXD / DBG\_UART\_RXD: these signals are typically connected to an RS-232 transceiver and will allow a PC to communicate with the openMSP430 core.

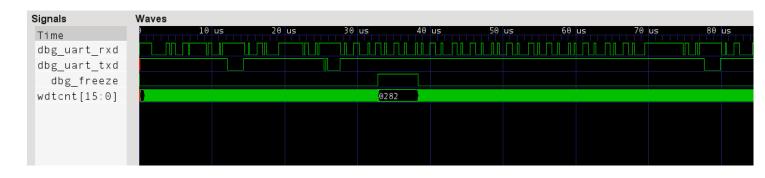

The following waveform shows some communication traffic on the serial bus:

# Software Development Tools

#### **Table of content**

- 1. Introduction

- 2. openmsp430-loader

- 3. openmsp430-minidebug

- <u>4. openmsp430-gdbproxy</u>

- 5. MSPGCC Toolchain

- 5.1 Some notes regarding msp430-gdb

- 5.2 CPU selection for msp430-gcc

#### 1. Introduction

Building on the serial debug interface capabilities provided by the openMSP430, three small utility programs are provided:

- **openmsp430-loader:** a simple command line boot loader.

- openmsp430-minidebug: a minimalistic debugger with simple GUI.

- **openmsp430-gdbproxy:** GDB Proxy server to be used together with MSP430-GDB and the Eclipse, DDD, or Insight graphical front-ends.

All these software development tools have been developed in TCL/TK and were successfully tested on both Linux and Windows XP.

**Note:** in order to be able to directly execute the scripts, <u>TCL/TK</u> needs to be installed on your system. Optionally for Windows users, the scripts have been turned into single-file binary executable programs using <u>freeWrap</u>.

#### 2. openmsp430-loader

This simple program allows the user to load the openMSP430 program memory with an executable file (ELF format) provided as argument.

It is typically used in conjunction with '*make*' in order to automatically load the program after the compile step (see '*Makefile*' from software examples provided with the project's FPGA implementation).

The program can be called with the following syntax:

```

openmsp430-loader.tcl [-device <communication device>] [-baudrate <communication speed>] <elf-file>

Examples: openmsp430-loader.tcl -device /dev/ttyUSB0 -baudrate 9600 leds.elf openmsp430-loader.tcl -device COM2: -baudrate 38400 ta_uart.elf

```

These screenshots show the script in action under Linux and Windows:

```

■ ○ leds:bash

File Edit View Scrollback Bookmarks Settings Help

[1006] [pitchu.hebus: leds]$

[1006] [pitchu.hebus: leds]$

[1006] [pitchu.hebus: leds]$ openmsp430-loader.tcl -device /dev/ttyUSB0 -baudrate 115200 leds.elf

Connecting with the openMSP430 (/dev/ttyUSB0, 115200 bps)... done

Connected: target device has 4096B ROM and 1024B RAM

Load ROM... done

Verify ROM... done

[1006] [pitchu.hebus: leds]$

[1006] [pitchu.hebus: leds]$

[1006] [pitchu.hebus: leds]$

[1006] [pitchu.hebus: leds]$

[1006] [pitchu.hebus: leds]$

```

```

C:\openmsp430\tools\bin\

Connected: target device has 4096B ROM and 1024B RAM

Load ROM... done

Uerify ROM... done

C:\openmsp430\tools\bin\

C:\openmsp430\tools\bin\

C:\openmsp430\tools\bin\

C:\openmsp430\tools\bin\openmsp430\cools\bin\

Connected: target device has 4096B ROM and 1024B RAM

Load ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

Uerify ROM... done

```

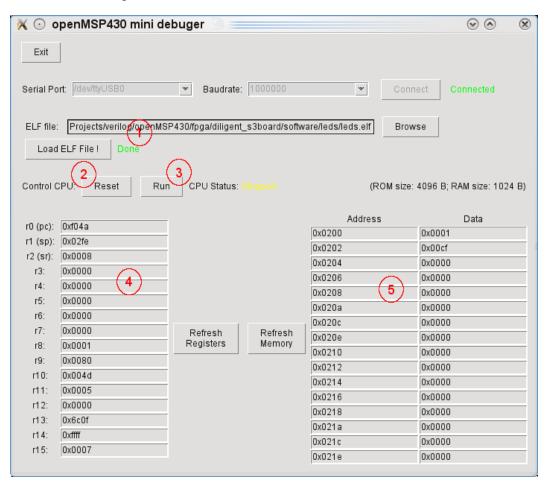

# 3. openmsp430-minidebug

This small program provides a minimalistic graphical interface enabling simple interaction with the openMSP430:

As you can see from the screenshot, it allows the following actions:

- (1) Load the program memory with an ELF file

- (2) Reset the CPU

- (3) Stop/Start the program execution

- (4) Read/Write access of the CPU registers

- (5) Read/Write access of the whole memory range (program, data, peripherals)

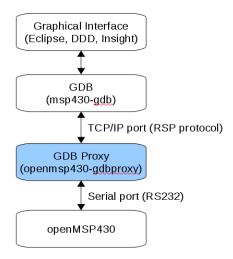

# 4. openmsp430-gdbproxy

The purpose of this program is to replace the '*msp430-gdbproxy*' utility provided by the mspgcc toolchain.

Typically, a GDB proxy creates a local port for gdb to connect to, and handles the communication with the target hardware. In our case, it is basically a bridge between the RSP communication protocol from GDB and the serial debug interface from the openMSP430.

Schematically the communication flow looks as following:

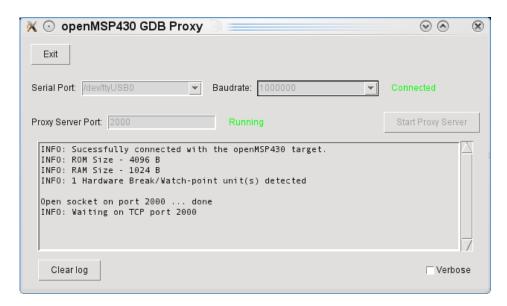

Like the original '*msp430-gdbproxy*' program, '*openmsp430-gdbproxy*' can be controlled from the command line. However, it also provides a small graphical interface:

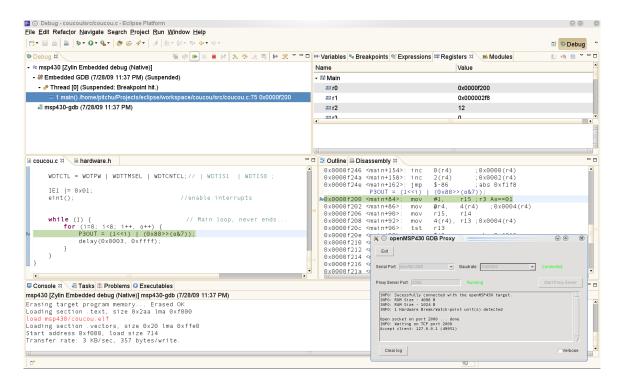

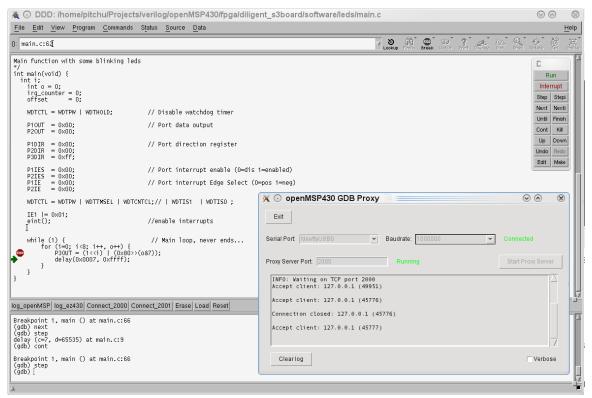

These two additional screenshots show the script in action together with the Eclipse and DDD graphical frontends:

**Tip:** There are several tutorials on Internet explaining how to configure Eclipse for the MSP430. As an Eclipse newbie, I found the followings quite helpful:

- <u>Use Eclipse and mspgcc The easy way</u> (English)

- MSP430 Entwicklungumgebung (German)

#### 5. MSPGCC Toolchain

#### 5.1 Some notes regarding msp430-gdb

As of today (July 2009), the GDB port for the MSP430 has some problems (here).

The stepping over function is not available and the backtrace and finish commands don't work properly.

There is fortunately a <u>patch</u> existing, and until it is included into GDB, I can only recommend to recompile GDB with it (I didn't try it for Windows but it is quite straight forward to do for Linux).

#### 5.2 CPU selection for msp430-gcc

The following table aims to help selecting the proper **-mmcu** option for the **msp430-gcc** call.

Note that the program memory size should imperatively match the openMSP430 configuration.

| -mmcu option              | Program<br>Memory | Data<br>Memory |  |

|---------------------------|-------------------|----------------|--|

| Program                   | Memory Size: 1    | l kB           |  |

| msp430x110                | 1 kB              | 128 B          |  |

| msp430x1101               | 1 kB              | 128 B          |  |

| msp430x2001               | 1 kB              | 128 B          |  |

| msp430x2002               | 1 kB              | 128 B          |  |

| msp430x2003               | 1 kB              | 128 B          |  |

| msp430x2101               | 1 kB              | 128 B          |  |

| Program Memory Size: 2 kB |                   |                |  |

| msp430x1111               | 2 kB              | 128 B          |  |

| msp430x2011  | 2 kB           | 128 B |

|--------------|----------------|-------|

| msp430x2012  | 2 kB           | 128 B |

| msp430x2013  | 2 kB           | 128 B |

| msp430x2111  | 2 kB           | 128 B |

| msp430x2112  | 2 kB           | 128 B |

| msp430x311   | 2 kB           | 128 B |

| Program      | Memory Size: 4 | kB    |

| msp430x112   | 4 kB           | 256 B |

| msp430x1121  | 4 kB           | 256 B |

| msp430x1122  | 4 kB           | 256 B |

| msp430x122   | 4 kB           | 256 B |

| msp430x1222  | 4 kB           | 256 B |

| msp430x2122  | 4 kB           | 256 B |

| msp430x2121  | 4 kB           | 256 B |

| msp430x312   | 4 kB           | 256 B |

| msp430x412   | 4 kB           | 256 B |

| Program      | Memory Size: 8 | B kB  |

| msp430x123   | 8 kB           | 256 B |

| msp430x133   | 8 kB           | 256 B |

| msp430x313   | 8 kB           | 256 B |

| msp430x323   | 8 kB           | 256 B |

| msp430x413   | 8 kB           | 256 B |

| msp430x423   | 8 kB           | 256 B |

| msp430xE423  | 8 kB           | 256 B |

| msp430xE4232 | 8 kB           | 256 B |

| msp430xW423  | 8 kB           | 256 B |

| msp430x1132  | 8 kB           | 256 B |

| msp430x1232  | 8 kB           | 256 B |

| msp430x1331  | 8 kB           | 256 B |

| msp430x2131  | 8 kB           | 256 B |

| msp430x2132  | 8 kB           | 256 B |

| msp430x2232  | 8 kB           | 512 B |

| msp430x2234  | 8 kB           | 512 B |

|              |                |       |

| msp430x233   | 8 kB                       | 1024 B |  |  |  |  |

|--------------|----------------------------|--------|--|--|--|--|

| msp430x2330  | 8 kB                       | 1024 B |  |  |  |  |

| Program I    | Program Memory Size: 16 kB |        |  |  |  |  |

| msp430x4250  | 16 kB                      | 256 B  |  |  |  |  |

| msp430xG4250 | 16 kB                      | 256 B  |  |  |  |  |

| msp430x135   | 16 kB                      | 512 B  |  |  |  |  |

| msp430x1351  | 16 kB                      | 512 B  |  |  |  |  |

| msp430x155   | 16 kB                      | 512 B  |  |  |  |  |

| msp430x2252  | 16 kB                      | 512 B  |  |  |  |  |

| msp430x2254  | 16 kB                      | 512 B  |  |  |  |  |

| msp430x315   | 16 kB                      | 512 B  |  |  |  |  |

| msp430x325   | 16 kB                      | 512 B  |  |  |  |  |

| msp430x415   | 16 kB                      | 512 B  |  |  |  |  |

| msp430x425   | 16 kB                      | 512 B  |  |  |  |  |

| msp430xE425  | 16 kB                      | 512 B  |  |  |  |  |

| msp430xW425  | 16 kB                      | 512 B  |  |  |  |  |

| msp430xE4252 | 16 kB                      | 512 B  |  |  |  |  |

| msp430x435   | 16 kB                      | 512 B  |  |  |  |  |

| msp430x4351  | 16 kB                      | 512 B  |  |  |  |  |

| msp430x235   | 16 kB                      | 2048 B |  |  |  |  |

| msp430x2350  | 16 kB                      | 2048 B |  |  |  |  |

| Program 1    | Memory Size: 3             | 2 kB   |  |  |  |  |

| msp430x4270  | 32 kB                      | 256 B  |  |  |  |  |

| msp430xG4270 | 32 kB                      | 256 B  |  |  |  |  |

| msp430x147   | 32 kB                      | 1024 B |  |  |  |  |

| msp430x1471  | 32 kB                      | 1024 B |  |  |  |  |

| msp430x157   | 32 kB                      | 1024 B |  |  |  |  |

| msp430x167   | 32 kB                      | 1024 B |  |  |  |  |

| msp430x2272  | 32 kB                      | 1024 B |  |  |  |  |

| msp430x2274  | 32 kB                      | 1024 B |  |  |  |  |

| msp430x337   | 32 kB                      | 1024 B |  |  |  |  |

| msp430x417   | 32 kB                      | 1024 B |  |  |  |  |

| msp430x427   | 32 kB                      | 1024 B |  |  |  |  |

| 32 kB | 1024 B                                                               |

|-------|----------------------------------------------------------------------|

| 32 kB | 1024 B                                                               |

| 32 kB | 2048 B                                                               |

| 32 kB | 4096 B                                                               |

| 32 kB | 4096 B                                                               |

|       | 32 kB<br>32 kB<br>32 kB<br>32 kB<br>32 kB<br>32 kB<br>32 kB<br>32 kB |

# File and Directory Description

#### **Table of content**

- 1. Introduction

- 2. Directory structure: openMSP430 core

- 3. Directory structure: FGPA projects

- 3.1 Xilinx Spartan 3 example

- 3.2 Altera Cyclone II example

- 4. Directory structure: Software Development Tools

#### 1. Introduction

To simplify the integration of this IP, the directory structure is based on the OpenCores recommendations.

# 2. Directory structure: openMSP430 core

| e               | openMSP430 Core top level directory |  |

|-----------------|-------------------------------------|--|

| bench           | Top level testbench directory       |  |

| verilog         |                                     |  |

| tb_openMSP430.v | Testbench top level module          |  |

| ram.v           | RAM verilog model                   |  |

|     | registers.v            | Connections to Core internals for easy debugging                                                                 |  |

|-----|------------------------|------------------------------------------------------------------------------------------------------------------|--|

|     | dbg_uart_tasks.v       | UART tasks for the serial debug interface                                                                        |  |

|     | msp_debug.v            | Testbench instruction decoder and ASCII chain generator for easy debugging                                       |  |