## FPGA to VGA monitor

## A-Hardware setup

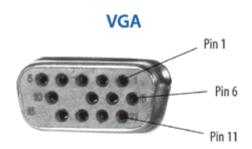

#### Pinout of the VGA graphic card connector:

| Pin | Signal       | Pin | Signal          |

|-----|--------------|-----|-----------------|

| 1   | Red          | 9   | NO CONNECTION   |

| 2   | Green        | 10  | Sync Return     |

| 3   | Blue         | 11  | ID Bit 0        |

| 4   | ID Bit 2     | 12  | ID Bit 1        |

| 5   | Ground       | 13  | Horizontal Sync |

| 6   | Red Shield   | 14  | Vertical Sync   |

| 7   | Green Shield | 15  | NO CONNECTION   |

| 8   | Blue Shield  |     |                 |

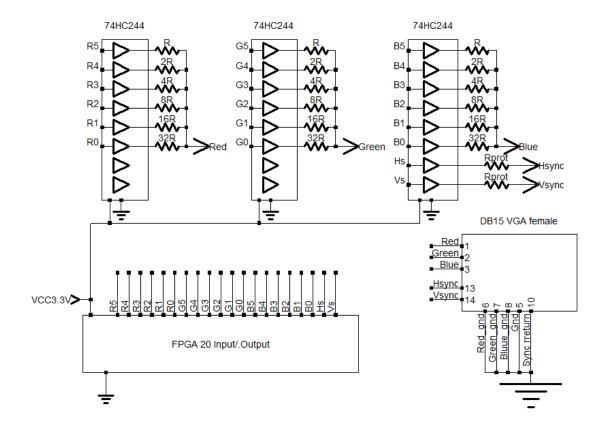

Schematic of the adapter card:

#### Components for the adapter card:

We use small SN74HCT244PWR (TSSOP pitch 0.65). Resistors will be 0603.

Rprot resistors on HSync, VSync can protect against unexpected currents, i take 100 ohm.

DAC (Digital to analog converter) resistors for 5-5-5 RGB:

(Taken from "OLIMEX LOW COST LCD-TO-VGA ADAPTER" <a href="http://olimex.wordpress.com/2012/06/12/low-cost-lcd-to-vga-adapter/">http://olimex.wordpress.com/2012/06/12/low-cost-lcd-to-vga-adapter/</a>)

| theorical value | Approx. value available |

|-----------------|-------------------------|

| R=549 ohm       | 560                     |

| 2R=1050 ohm     | 1K1                     |

| 4R=2180 ohm     | 2K2                     |

| 8R=4370 ohm     | 4K3                     |

| 16R=8660 ohm    | 9K1                     |

| 32R=17800 ohm   | 18K                     |

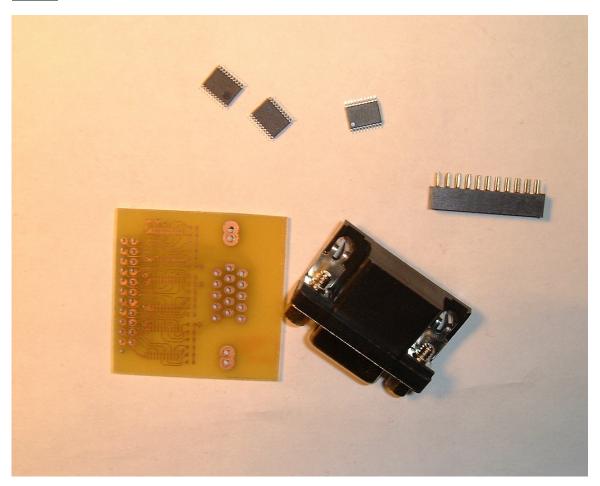

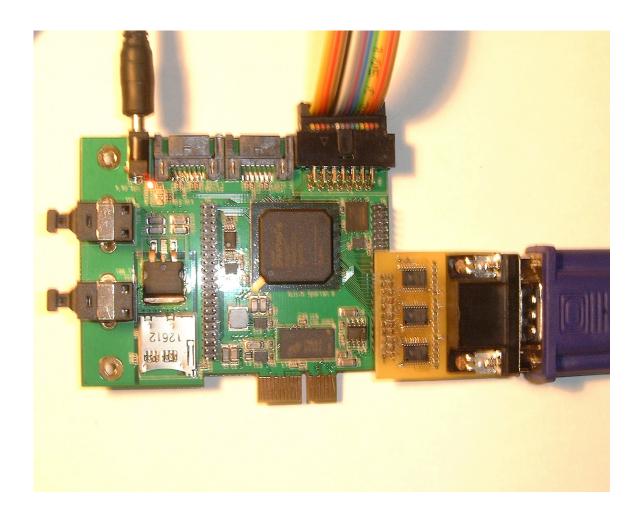

#### Photos:

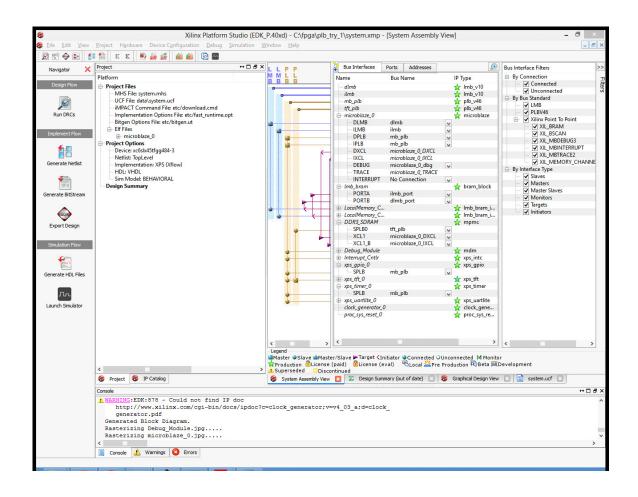

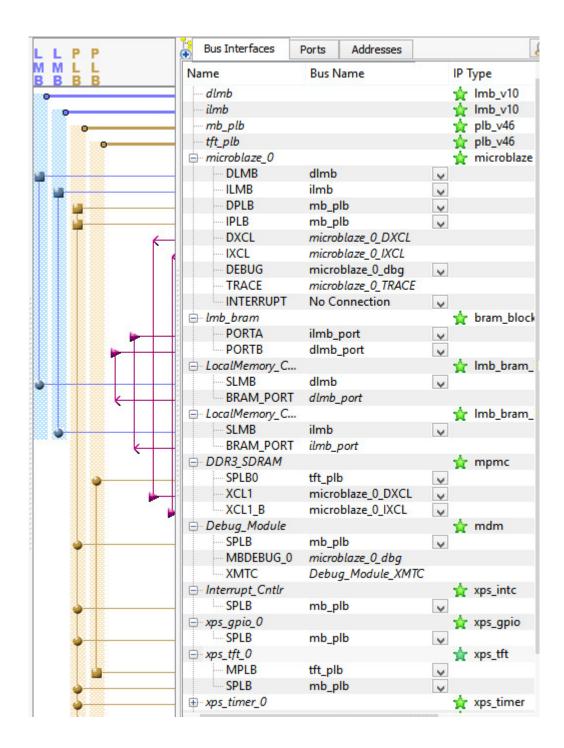

# B-Building the Microblaze processor with xps tft core in Xilinx Platform studio

A graphic controller core for LCD and VGA is available with Xilinx Platform Studio.

Unfortunately this core is available only in old PLB bus on Spartan 6 (It is available as AXI bus peripheral for other FPGA family).

So, i have entirely redesigned a new Microblaze project using the PLBv4.3 bus.

The DDR3 memory has 2 ports

- -Processor port

- -video frame buffer port

The xps\_tft core access the video frame buffer directly with the DDR3 video port.

The xps\_tft has 2 bus

- -Slave PLB for internal registers

- -Master PLB 64bit for frame buffer access

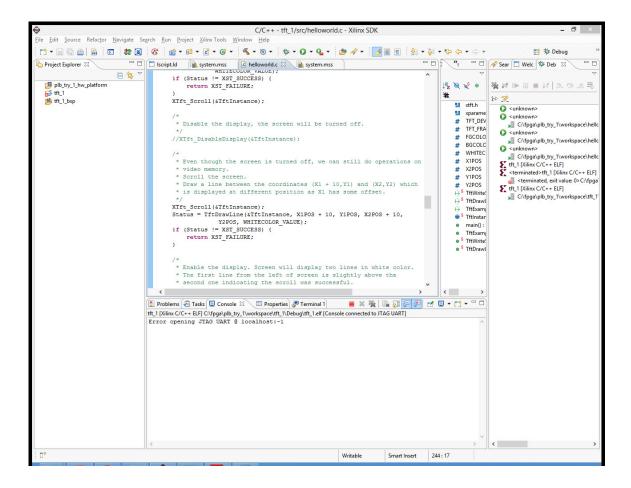

## C-Building the sample application in Xilinx SDK

```

(DK)

C/C++-tft_1/src/h

File Edit Source Refactor Navigate Search Run Project Xilinx Tools Window Help

☐ Iscript.ld

Project Explorer 🔀

helloworld.c 🖂

system.mss

WILLECOLOK VALUE);

Workspace

if (Status != XST SUCCESS) {

plb_try_1_hw_platform

return XST FAILURE;

tft_1_bsp

XTft_Scroll(&TftInstance);

* Disable the display, the screen will

//XTft DisableDisplay(&TftInstance);

* Even though the screen is turned off

* video memory.

* Scroll the screen.

* Draw a line between the coordinates

* is displayed at different position a

XTft Scroll(&TftInstance);

Status = TftDrawLine(&TftInstance, X1PO

Y2POS, WHITECOLOR_VALUE);

if (Status != XST_SUCCESS) {

return XST FAILURE;

```

The application is generated by simply pasting the tft example (xtft\_example.c) inside the default "hello world" application.

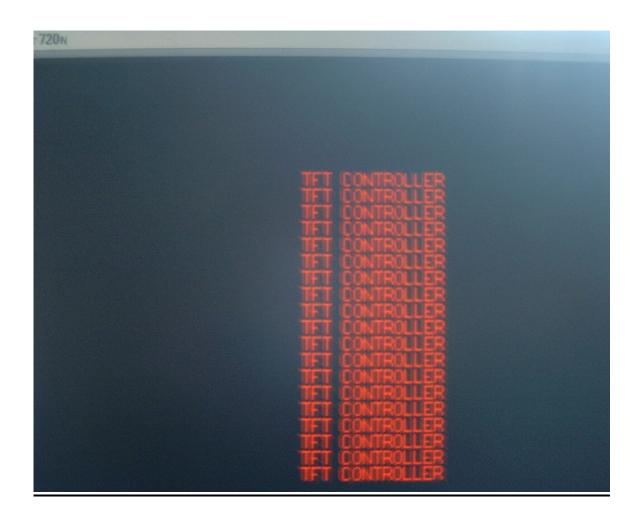

### D-Running the sample app

A sample application demonstrating the Xilinx tft support library and xps\_tft core is found with EDK iunstallation (C:\Xilinx\14.3\ISE\_DS\EDK\sw\XilinxProcessorIPLib\drivers\tft\_v3\_01\_a \examples\xtft\_example.c)