# **FT64**

# Overview

FT64 is a two-way superscalar processing core capable of executing up to two instructions per clock cycle. The core features register renaming to avoid data hazards. The core has the following features:

- 64 register sets

- 32 general purpose scalar registers

- 32 general purpose floating-point registers

- 32 general purpose vector registers, length 63

- register renaming

- speculative loading

- 32 bit fixed instruction format

- 64 bit data width

- powerful branch prediction with target buffer (BTB)

- return address prediction (RSB)

- bus interface unit

- instruction and data caches

- Vector and SIMD operations

- fine-grained simultaneous multi-threading (SMT)

- dual ALU's, one flow control unit, one memory unit, one floating point unit

# History

FT64 is a work-in-progress beginning in July 2017. FT64 originated from RiSC-16 by Dr. Bruce Jacob. RiSC-16 evolved from the Little Computer (LC-896) developed by Peter Chen at the University of Michigan. See the comment in FT64.v. FT64 is the author's fifth attempt at a 64 bit ISA. Other attempts including Raptor64, Thor, FISA64, and DSD9. The author has tried to be innovative with this design borrowing ideas from a number of other processing cores. Berkeley's RiSC-V has had an influence on this core.

# Goals

One of the primary goals for the development of this core was the implementation of a register renaming mechanism. The author also wanted a stream-lined core as a starting place.

Implementing many features of the Thor core using a fixed 32 bit instruction set.

Easy implementation of a compiler.

Eventual implementation as a four-way superscalar processing core.

# **Register Sets**

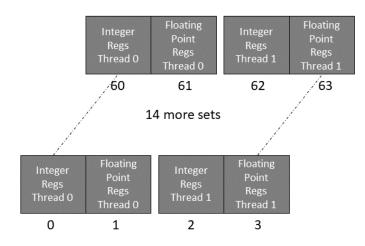

There are 64 sets of 32 general purpose registers in the architecture. The odd registers sets may be used as floating-point registers for the even register set. When SMT is turned on register sets are used in pairs. The following is an illustration of register set usage.

On reset register set #0 is selected to be the operating register set. On interrupt every fourth register sets #4 to #28 will be selected according to the level of the interrupt.

| Machine State     | Register Set Selected                   |

|-------------------|-----------------------------------------|

| BRK / RESET       | 0                                       |

| IRQ 1             | 4                                       |

| IRQ 2             | 8                                       |

| IRQ 3             | 12                                      |

| IRQ 4             | 16                                      |

| IRQ 5             | 20                                      |

| IRQ 6             | 24                                      |

| IRQ 7             | 28                                      |

| Normal Operations | according to rs field in control reg #0 |

There is just a single set of vector registers.

# **Register Usage Convention**

R0 always has the value zero in all register sets. r29 is the link register used implicitly by the call instruction.

| Register | Description / Suggested Usage     | Saver  |

|----------|-----------------------------------|--------|

| rO       | always reads as zero              |        |

| r1-r2    | return values / exception         | caller |

| r3-r10   | temporaries                       | caller |

| r11-r17  | register variables                | callee |

| r18-r22  | function arguments                | caller |

| r23      | assembler usage                   |        |

| r24      | type number / function argument   | caller |

| r25      | class pointer / function argument | caller |

| r26      | thread pointer                    | callee |

| r27      | global pointer                    |        |

| r28      | exception link register           | caller |

| r29      | return address / link register    | caller |

| r30      | base / frame pointer              | callee |

| r31      | stack pointer (hardware)          | callee |

The ISA supports up to 32 vector registers of length 63. There is only a single set of vector registers.

| Register   |                                  |

|------------|----------------------------------|

| v0 to v31  | general purpose vector registers |

| vm0 to vm7 | vector mask registers            |

The register file has six read ports and two write ports.

## Notes:

The register set is implemented with block ram resources in the FPGA. In order to get byte write strobes for the registers it was possible to accommodate a large number of registers. Elucidating, the block rams in use provided 4096 eight-bit wide registers per block ram. Regardless of the number of registers actually used there was still a provision for 4096. All these available registers were put to good use as multiple register sets and vectored registers.

The register set currently selected is determined by the rs field in the machine status register (0x044).

Internally to the core a single register file is in use that uses a 12-bit register code:

| 11             | 6 | 5 | 4 0                             |

|----------------|---|---|---------------------------------|

| Register Set   |   | 0 | General Purpose Register number |

| Vector element |   | 1 | Vector register number          |

To conserve hardware which would otherwise be quite large, the bypassing logic looks at only the six least significant bits, plus bits 6, and 7 of the register code for bypassing purposes. This allows it to differentiate between different general purpose registers, floating-point, thread 0 and thread 1 registers, and vector registers. This meets bypass logic requirements in most circumstances.

The core does not provide bypass logic between different elements of the same vector register. It only provides bypassing at the vector register number level. Normally this is not a problem because vector elements are processed independently.

Similarly, the core does not provide bypassing between register sets of the general purpose registers outside of checking thread register pairs. Switching the register set should be followed by a synchronization operation to ensure contents of the previous instructions are updated before the new use.

There are only 63 usable elements to each vector register. Register codes for the 64<sup>th</sup> element are used to access the vector mask registers.

| 11 | 6 | 5 | 4 | 3 | 2        | 0            |

|----|---|---|---|---|----------|--------------|

| 63 |   | 1 | ( | C | mask reg | ister number |

This is hidden from the ISA and may be implemented differently in the future.

On reset register set #0 is selected.

# **Program Counter**

The program counter identifies which instruction to execute. The program counter increments by four with the least significant two bits always zero. The increment may be overridden using one of the flow control instructions. The program counter addresses 32 bit instruction parcels.

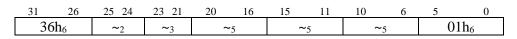

| 63                       | 2 | 1 | 0  |

|--------------------------|---|---|----|

| Address <sub>[632]</sub> |   | 0 | )2 |

# Notes:

There are actually two program counters in use by the core, one for each fetch buffer, and each one normally increments by eight. The second program counter always follows the first one, incremented by four, so that it addresses the next instruction word. There are a couple of reasons to use two counters. One is to avoid an adder delay that would be present on the output of a single counter if only one counter were used. A second reason for two counters is that they may be used independently for simultaneous multi-threading (SMT). When SMT is on each program counter operates independently and increments by four instead of eight.

# SMT

The core is capable of fine-grained SMT (simultaneous multi-threading) operation. With SMT there are two possible threads of execution each of which operates at about ½ the performance of a single thread. For some applications it may be desirable to use SMT in order to increase the overall performance of the system. The core fetches from two different execution threads simultaneously. When enabled the core's program counters operate independently. One half of the fetch buffers are used for each of two possible threads of execution.

# Notes:

For simplicity, on a branch miss the entire fetch buffer is flushed and reloaded with instructions from the target address. This includes instructions for both threads of execution. Both threads may miss at the same time and the fetch buffer will only be reloaded once.

# **Vector Chaining**

The vector chain bit in control register #0 controls the priority of queueing vector instructions when there are two vector instructions available to queue. If vector chaining is on then one element from each vector instruction will queue. If vector chaining is off then two elements from the first vector instruction will queue. Vector chaining may improve performance depending on the instruction mix. For instance if there is a multiply followed by an add under normal circumstances multiplication of the next vector element can't proceed until the instruction is finished. Without vector chaining the add can't proceed until the multiply is done. With vector chaining the add can be performed at the same time as the multiply, hiding some of the latency of the multiply operation.

# Caches

The core has both instruction and data caches in order to improve performance.

The instruction cache is a two level cache (L1, L2) allowing better performance. The first level cache is four way associative, the second level cache is four-way set associative. L1 is 2kB in size and made from distributed ram in order to get single cycle performance. L1 is organized as 64 lines of 32 bytes. L2 is 16kB in size implemented with block ram. L2 is organized as 512 lines of 32 bytes. The L1 instruction cache is dual read ported to allow two instructions to be fetched at one time.

The data cache is organized as 512 lines of 32 bytes (16kB) and implemented with block ram. Access to the data cache is multicycle. The data cache has three read ports allowing three load operations to be in progress at the same time. Stores write through to memory. There is only a single write port on the data cache.

#### **Uncached Data Area**

The address range \$FFDxxxxx is an uncached data area. This area is reserved for I/O devices. The data cache may also be disabled in control register zero. There is also a set of load instructions that bypass the data cache. These are called load volatile (LVx) instructions.

# **Fetch Buffers**

There are two fetch buffers each of which holds a pair of instructions. When a fetch buffer becomes empty it is loaded with new instructions from the cache.

# **Branch Predictor**

The branch predictor is a (2, 2) correlating predictor. The branch history is maintained in a 512 entry history table. It has four read ports for predicting branch outcomes, one port for each instruction in the fetch buffer. The branch predictor may be disabled by a bit in control register zero. When disabled all branches are predicted as not taken, unless specified otherwise in the branch instruction. A statically predicted branch does not use the branch predictor instead the prediction is based on the setting of the prediction bits in the branch instruction.

The CC64 compiler has a notation for representing static branch predictions in high level code. Refer to the CC64 compiler documentation for the exact notation used.

To conserve hardware the branch predictor uses a fifo that can queue up to two branch outcomes at the same time. Outcomes are removed from the fifo one at a time and used to update the branch history table which has only a single write port. In an earlier implementation of the branch predictor, two write ports were provided on the history table. This turned out to be relatively large compared to it's usefulness.

Correctly predicting a branch turns the branch into a single cycle operation. During execution of the branch instruction the address of the following instruction queued is checked against the address depending on the branch outcome. If the address does not match what is expected then the queue will be flushed and new instructions loaded from the correct program path.

# **Branch Target Buffer (BTB)**

The core has a 1k entry branch target buffer for predicting the target address of flow control instructions where the address is calculated and potentially unknown at time of fetch. Instructions covered by the BTB include jump-and-link, interrupt return and breakpoint instructions and branches to targets contained in a register.

# **Return Address Stack Predictor (RSB)**

There is an address predictor for return addresses which can in some cases can eliminate the flushing of the instruction queue when a return instruction is executed. The RET instruction is detected in the fetch stage of the core and a predicted return address used to fetch instructions following the return. JAL instructions using the link register as the source are also treated as return instructions. The return address stack predictor has a stack depth of 32 entries. On stack overflow or underflow the prediction will be wrong, however performance will be no worse than not having a predictor. The return address stack predictor checks the address of the instruction queued following the RET against the address fetched for the RET instruction to make sure that the address corresponds.

There is a separate RSB for each thread while operating with SMT turned on.

# **Instruction Queue**

The instruction queue is an eight-entry re-ordering buffer (ROB). The instruction queue tracks an instructions progress and provides a holding place for operands and results. Each instruction in queue may be in one of a number of different states. The core will not enqueue an instruction unless there is room for two or more instructions in the queue. It will not enqueue two instructions unless there is room for three or more instructions in the queue. The core waits for an additional queue slot to become available in order to prevent the core from becoming deadlocked by a flow control instruction which waits until the next instruction queues before being issued.

# **Queueing of Flow Control Operations**

Flow control operations are not done until sometime after the next instruction queues. This is necessary to determine address miss-predicts during the flow control operation. Waiting until the next instruction queues avoids the problem of false mis-predictions. A consequence of waiting for the next instruction to queue is that flow control operations may only issue from one of the first seven queue slots relative to the head of the queue.

# **Operating Levels**

The core has eight operating levels. The highest operating level is operating level zero which is called the machine operating level. Operating level zero has complete access to the machine. Other operating levels may have more restricted access. When an interrupt occurs the operating level is set to the machine level. The core vectors to an address depending on the current operating level.

| 7 | 7 to 255 | user       |

|---|----------|------------|

| 6 | 6        | supervisor |

| 5 | 5        | supervisor |

| 4 | 4        | supervisor |

| 3 | 3        | supervisor |

| 2 | 2        | supervisor |

| 1 | 1        | hypervisor |

| 0 | 0        | machine    |

#### **Switching Operating Levels**

The operating level is automatically switched to the machine level when an interrupt occurs. The BRK instruction may be used to switch operating levels. The REX instruction may also be used by an interrupt handler to switch the operating level to a lower level. The RTI instruction will switch the operating level back to what it was prior to the interrupt.

#### **Privilege Levels**

The core supports a 256 level privilege level system. Privilege level zero is assigned to operating mode zero. Privilege level one is assigned to operating level one. Privilege levels 2 to 6 are assigned to their corresponding operating level. The remaining privilege levels are assigned to operating level seven.

## **Control and Status Registers**

#### Control Register Zero (CSR #000)

This register contains a bit to enable protected mode.

| 63 | 62 |  | 33 | 32  | 30  | 17  | 16  | 1514 | 13 | 8 | 7 | 1 | 0  |

|----|----|--|----|-----|-----|-----|-----|------|----|---|---|---|----|

| D  | ~  |  | ~  | bpe | dce | SNR | SMT | 0    | ~  |   |   |   | Pe |

D: debug mode status. this bit is set during an interrupt routine if the processor was in debug mode when the interrupt occurred.

PE: Protected Mode enable: 1 = enabled, 0 = disabled.

DCE: data cache enable: 1=enabled, 0 = disabled

bpe: branch predictor enable: 1=enabled, 0=disabled

SMT: simultaneous multi-threading enable 1 = enabled, 0 = disabled (0 default).

SNR: sequence number reset, 1 = reset, automatically clears

Disabling the data cache is useful for some codes with large data sets to prevent cache loading of values that are used infrequently. The instruction cache may not be disabled.

Disabling branch prediction will significantly affect the cores performance, but may be useful for debugging. Disabling branch prediction causes all branches to be predicted as not-taken (unless determined otherwise by the instruction). No entries will be updated in the branch history table if the branch predictor is disabled.

This register supports bit set / clear CSR instructions.

#### HARTID (0x001)

This register contains a number that is externally supplied on the hartid\_i input bus to represent the hardware thread id or the core number.

#### TICK (0x002)

This register contains a tick count of the number of clock cycles that have passed since the last reset.

### PCR Paging Control (CSR 0x003)

This register controls the paged memory management unit. A more detailed description is available under the section on memory management.

#### AEC Arithmetic Exception Control (CSR 0x004)

This register has controls to enable arithmetic exceptions and status bits to indicate the occurrence of exception conditions.

| Exception Occurrence |     |     |     |     |     | E  | Exceptior | ı Enable | •   |     |     |

|----------------------|-----|-----|-----|-----|-----|----|-----------|----------|-----|-----|-----|

| 63                   | 36  | 35  | 34  | 33  | 32  | 31 | 4         | 3        | 2   | 1   | 0   |

| 37                   |     |     |     |     |     | 5  |           |          |     |     |     |

|                      | DIV | MUL | ASL | SUB | ADD |    | DIV       | MUL      | ASL | SUB | ADD |

#### CAUSE (0x006)

This register contains a code indicating the cause of an exception or interrupt. The break handler will examine this code in order to determine what to do. Only the low order 16 bits are implemented. The high order bits read as zero and are not updateable.

## BADADDR (CSR 0x007)

This register contains the effective address for a load / store operation that caused a memory management exception or a bus error. Note that the address of the instruction causing the exception is available in the EPC register.

#### PCR2 Paging Control (CSR 0x008)

This register controls the paged memory management unit. A more detailed description is available under the section on memory management.

#### Scratch (CSR 0x009)

This register is available for scratchpad use. It is typically swapped with a GPR during exception processing.

### SEMA (CSR 0x00C) Semaphores

This register is available for system semaphore or flag use. The least significant bit is tied to the reservation address status input (rb\_i). It will be set if a SWC instruction was successful. The least significant bit is also cleared automatically when an interrupt (BRK) or interrupt return (RTI) instruction is executed. Any one of the remaining bits may also be cleared by an RTI instruction. This could be a busy status bit for the interrupt routine. Bits in this CSR may be set or cleared with one of the CSRxx instructions. This register has individual bit set / clear capability.

### SBL (CSR 0x00E)

The SBL register contains the address representing the lower bound of the stack. If an address is formed using one of the stack indexing registers (stack pointer r31 or base pointer r30) is lower than the SBL a stack fault occurs. This represents a stack overflow condition.

### SBU (CSR 0x00F)

The SBU register contains the address representing the upper bound of the stack. If an address is formed using one of the stack indexing registers (stack pointer r31 or base pointer r30) is higher than the SBU a stack fault occurs. This represents a stack underflow condition.

# FSTAT (CSR 0x014) Floating Point Status and Control Register

The floating point status and control register may be read using the CSR instruction. Unlike other

CSR's the control register has its own dedicated instructions for update. See the section on

floating point instructions for more information.

| Bit               |        | Symbol     | Description                                                                                |

|-------------------|--------|------------|--------------------------------------------------------------------------------------------|

| 31:29             | RM     | rm         | rounding mode                                                                              |

| 28                | E5     | inexe      | - inexact exception enable                                                                 |

| 27                | E4     | dbzxe      | - divide by zero exception enable                                                          |

| 26                | E3     | underxe    | - underflow exception enable                                                               |

| 25                | E2     | overxe     | - overflow exception enable                                                                |

| 24                | E1     | invopxe    | - invalid operation exception enable                                                       |

| 23                | NS     | ns         | - non standard floating point indicator                                                    |

| <b>Result Sta</b> | atus   |            |                                                                                            |

| 22                |        | fractie    | - the last instruction (arithmetic or conversion) rounded                                  |

|                   |        |            | intermediate result (or caused a disabled overflow exception)                              |

| 21                | RA     | rawayz     | rounded away from zero (fraction incremented)                                              |

| 20                | SC     | С          | denormalized, negative zero, or quiet NaN                                                  |

| 19                | SL     | neg <      | the result is negative (and not zero)                                                      |

| 18                | SG     | pos >      | the result is positive (and not zero)                                                      |

| 17                | SE     | zero =     | the result is zero (negative or positive)                                                  |

| 16                | SI     | inf ?      | the result is infinite or quiet NaN                                                        |

| Exceptior         | n Occu | rrence     |                                                                                            |

| 15                | X6     | swt        | {reserved} - set this bit using software to trigger an invalid                             |

|                   |        |            | operation                                                                                  |

| 14                | X5     | inerx      | - inexact result exception occurred (sticky)                                               |

| 13                | X4     | dbzx       | - divide by zero exception occurred                                                        |

| 12                | X3     | underx     | - underflow exception occurred                                                             |

| 11                | X2     | overx      | - overflow exception occurred                                                              |

| 10                | X1     | giopx      | - global invalid operation exception – set if any invalid operation exception has occurred |

| 9                 | GX     | gx         | - global exception indicator – set if any enabled exception has                            |

|                   |        |            | happened                                                                                   |

| 8                 | SX     | sumx       | - summary exception – set if any exception could occur if it was                           |

|                   |        |            | enabled                                                                                    |

|                   |        |            | - can only be cleared by software                                                          |

| Exception         | n Type | Resolution |                                                                                            |

| 7                 | X1T    | cvt        | - attempt to convert NaN or too large to integer                                           |

| б                 | X1T    | sqrtx      | - square root of non-zero negative                                                         |

| 5 | X1T | NaNCmp   | - comparison of NaN not using unordered comparison |

|---|-----|----------|----------------------------------------------------|

|   |     |          | instructions                                       |

| 4 | X1T | infzero  | - multiply infinity by zero                        |

| 3 | X1T | zerozero | - division of zero by zero                         |

| 2 | X1T | infdiv   | - division of infinities                           |

| 1 | X1T | subinfx  | - subtraction of infinities                        |

| 0 | X1T | snanx    | - signaling NaN                                    |

# DBADx (CSR 0x018 to 0x01B) Debug Address Register

These registers contain addresses of instruction or data breakpoints.

| 63 |                         | 0 |

|----|-------------------------|---|

|    | Address <sub>63.0</sub> |   |

# DBCR (CSR 0x01C) Debug Control Register

This register contains bits controlling the circumstances under which a debug interrupt will occur.

| bits                             |                                                               |               |  |  |  |  |  |  |

|----------------------------------|---------------------------------------------------------------|---------------|--|--|--|--|--|--|

| 3 to 0                           | Enables a specific debug address register to do address m     | atching. If   |  |  |  |  |  |  |

|                                  | the corresponding bit in this register is set and the address |               |  |  |  |  |  |  |

|                                  | (instruction or data) matches the address in the debug add    | lress         |  |  |  |  |  |  |

|                                  | register then a debug interrupt will be taken.                |               |  |  |  |  |  |  |

| 17, 16                           | This pair of bits determine what should match the debug       | address       |  |  |  |  |  |  |

|                                  | register zero in order for a debug interrupt to occur.        |               |  |  |  |  |  |  |

|                                  | 17:16                                                         |               |  |  |  |  |  |  |

| 00 match the instruction address |                                                               |               |  |  |  |  |  |  |

|                                  | 01 match a data store address                                 |               |  |  |  |  |  |  |

|                                  | 10 reserved                                                   |               |  |  |  |  |  |  |

|                                  | 11 match a data load or store address                         |               |  |  |  |  |  |  |

| 19, 18                           | This pair of bits determine how many of the address bits      | need to       |  |  |  |  |  |  |

|                                  | match in order to be considered a match to the debug add      | ress          |  |  |  |  |  |  |

|                                  | register. These bits are ignored when matching instruction    | n addresses,  |  |  |  |  |  |  |

|                                  | which are always half-word aligned.                           |               |  |  |  |  |  |  |

|                                  | 19:18                                                         | Size          |  |  |  |  |  |  |

|                                  | 00 all bits must match                                        | byte          |  |  |  |  |  |  |

|                                  | 01 all but the least significant bit should match             | char          |  |  |  |  |  |  |

|                                  | 10 all but the two LSB's should match                         | half          |  |  |  |  |  |  |

|                                  | 11 all but the three LSB's should match                       | word          |  |  |  |  |  |  |

| 23 to 20                         | Same as 16 to 19 except for debug address register one.       |               |  |  |  |  |  |  |

| 27 to 24                         | Same as 16 to 19 except for debug address register two.       |               |  |  |  |  |  |  |

| 31 to 28                         | Same as 16 to 19 except for debug address register three.     |               |  |  |  |  |  |  |

| 55 to 62                         | These bits are a history stack for single stepping mode. A    | n exception   |  |  |  |  |  |  |

|                                  | will automatically disable single stepping mode and record    | rd the single |  |  |  |  |  |  |

|                                  | step mode state on stack. Returning from an exception po      | ps the        |  |  |  |  |  |  |

|                                  | single step mode state from the stack.                        |               |  |  |  |  |  |  |

| 63                               | This bit enables SSM (single stepping mode)                   |               |  |  |  |  |  |  |

#### DBSR (CSR 0x01D) - Debug Status Register

This register contains bits indicating which addresses matched. These bits are set when an address match occurs, and must be reset by software.

| bit     |                                |

|---------|--------------------------------|

| 0       | matched address register zero  |

| 1       | matched address register one   |

| 2       | matched address register two   |

| 3       | matched address register three |

| 63 to 4 | not used, reserved             |

#### CAS (CSR 0x02C) Compare and Swap

This register is to support the compare and swap (CAS) instruction. If the value in the addressed memory location identified by the CAS instruction is equal to the value in the CAS register, then the source register is written to the memory location, and the source register is loaded with the value 1. Otherwise if the value in the addressed memory location doesn't match the value in this register, then value at the memory location is loaded into the CAS register, and the source register is set to zero. No write to memory occurs if the match fails.

| 63 |                       | 0 |

|----|-----------------------|---|

|    | Value <sub>63.0</sub> |   |

# TVEC (0x030 to 0x037)

These registers contain the address of the exception handling routine for a given operating level. TVEC[0] (0x030) is used directly by hardware to form an address of the interrupt routine. The lower eight bits of TVEC[0] are not used. The lower bits of the interrupt address are determined from the operating level. For the other registers the two low order bits of the address must be zero in order to keep the program counter aligned on a half-word address. TVEC[1] to TVEC[7] are used by the REX instruction.

### IM\_STACK (0x040)

This register contains the interrupt mask stack. When an exception or interrupt occurs this register is shifted to the left and the current status copied to the low order bits, when an RTI instruction is executed this register is shifted to the right and the status bits copied from the low order bits of the register. On RTI the last stack entry is set to seven masking all interrupts on stack underflow. Only the low order 24 bits of the register are implemented.

#### OL\_STACK (0x041)

This register contains the operating level stack. When an exception or interrupt occurs this register is shifted to the left and the current status copied to the low order bits, when an RTI instruction is executed this register is shifted to the right and the status bits copied from the low order bits of the register. On RTI the last stack entry is set to zero which will select the machine operating level on stack underflow. Only the low order 24 bits of the register are implemented.

# PL\_STACK (0x042)

This register contains the privilege level stack. When an exception or interrupt occurs this register is shifted to the left and the current status copied to the low order bits, when an RTI instruction is executed this register is shifted to the right and the status bits copied from the low order bits of the register. On RTI the last stack entry will be set to zero which will select privilege level zero on stack underflow.

#### RS\_STACK (0x043)

This register contains the register set selection stack. When an exception or interrupt occurs this register is shifted to the left and the current status copied to the low order bits, when an RTI instruction is executed this register is shifted to the right and the status bits copied from the low

order bits of the register. On RTI the last stack entry will be set to eight which will select register set #8 on stack underflow.

### STATUS (0x044)

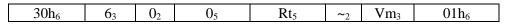

This register contains the interrupt mask, operating level, and privilege level.

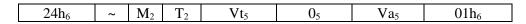

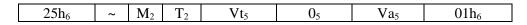

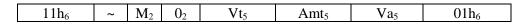

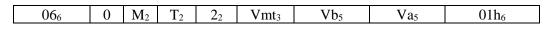

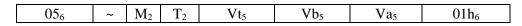

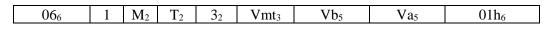

| 63     | 6261 | 60 56  | 55       | 5452 | 5150   | 4948            | 47 32       | 27 24             | 2320 | 19 14           | 13 6   | 53              | 20              |

|--------|------|--------|----------|------|--------|-----------------|-------------|-------------------|------|-----------------|--------|-----------------|-----------------|

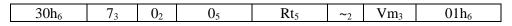

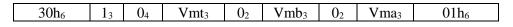

| $SD_1$ | ~2   | $VM_5$ | $MPRV_1$ | ~3   | $XS_2$ | FS <sub>2</sub> | <b>~</b> 16 | Thrd <sub>1</sub> | ~4   | RS <sub>6</sub> | $PL_8$ | OL <sub>3</sub> | IM <sub>3</sub> |

#### $VM_5$

These bits control virtual memory options. Note that multiple options may be present at the same time. At reset all the bits are set to zero.

| Bit | Indicates                            |  |

|-----|--------------------------------------|--|

| 0   | 1 = single bound                     |  |

| 1   | 1 = separate program and data bounds |  |

| 2   | 1 = lot protection system            |  |

| 3   | 1 = simplified paged unit            |  |

| 4   | 1 = paging unit                      |  |

#### **MPRV**

This bit when true (1) causes memory operations to use the first stack privilege level when evaluating privilege and protection rules. (Bits 0 to 13 in the status reg).

### $FS_2$

These two bits can be used to keep track of the floating point register state.

## $XS_2$

These two bits can be used to keep track of an additional core extension state.

#### $Thrd_1$

The currently executing hardware thread.

IRQ[42..40]

The level of interrupt that caused the hardware BRK.

#### VCA

(bit 32) This bit indicates that vector chaining was active prior to an exception.

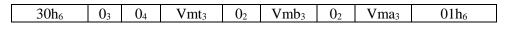

#### VE\_HOLD (0x045)

This register contains the currently executing vector element number for fetch buffers #0 and #1. Source and target element numbers are stored independently. Normally the source and target elements are the same, however they may be different if a vector compress instruction is executing. If the vector register set is switched during exception processing this register should be saved and restored.

| 63 | 54  | 53 | 48 | 47 | 38 | 37 | 32 | 31 | 22 | 21 | 16  | 15 | 6 | 5  | 0   |

|----|-----|----|----|----|----|----|----|----|----|----|-----|----|---|----|-----|

| ~  | ~ V |    | t1 |    | ~  | ve | s1 |    | ~  | ve | et0 | ~  | • | ve | es0 |

#### **EPC** (0x048 to 0x4F)

This sets of registers contains the interrupt or exception stack of the program counter register. The top of the stack is register 0x48. When an interrupt or exception occurs register 0x48 to 0x4E are copied to the next register and the program counter is placed into register 0x48. When an RTI instruction is executed the program counter is loaded from register 0x048 and registers 0x048 to 0x047 are loaded with the next register. Register 0x04F is loaded with the address of the break handler so that in the event of an underflow the break handler will be executed.

#### CODEBUF (0x080 to 0x0BF)

This register range is for access to 64 adaptable code buffers. The code buffers are used by the EXEC instruction in order to execute code which may change at run-time.

## **TIME (0x7E0)**

The TIME register corresponds to the wall clock real time. This register can be used to compute the current time based on a known reference point. The register value will typically be a fixed number of seconds offset from the real wall clock time. The lower 32 bits of the register are driven by the tm\_clk\_i clock time base input which is independent of the cpu clock. The tm\_clk\_i input is a fixed frequency used for timing that cannot be less than 10MHz. The low order 32 bits represent the fraction of one second. The upper 32 bits represent seconds passed. For example if the tm\_clk\_i frequency is 100MHz the low order 32 bits should count from 0 to 99,999,999 then cycle back to 0 again. When the low order 32 bits cycle back to 0 again, the upper 32 bits of the register is incremented. The upper 32 bits of the register represent the number of seconds passed since an arbitrary point in the past.

Note that this register has a fixed time basis, unlike the TICK register whose frequency may vary with the cpu clock. The cpu clock input may vary in frequency to allow for performance and power adjustments.

# **INSTRET (0x7E1)**

This register contains a count of the number of instructions retired (successfully completed) by the core.

## INFO (0x7F0 to 0x7FF)

This set of registers contains general information about the core including the manufacturer name, cpu class and name, and model number.

# Exceptions

# **External Interrupts**

There is very little difference between an externally generated exception and an internally generated one. An externally caused exception will force a BRK instruction into the instruction stream. The BRK instruction contains a cause code identifying the external interrupt source.

# **Effect on Machine Status**

The operating mode is always switched to the machine mode on exception. It's up to the machine mode code to redirect the exception to a lower operating mode when desired. Further exceptions at the same or lower interrupt level are disabled automatically. Machine mode code must enable interrupts at some point. This can be done automatically when the exception is redirected to a lower level by the REX instruction. The RTI instruction will also automatically enable further machine level exceptions.

For a hardware interrupt the register set is set to the level of the hardware interrupt (0 to 7). For a software exception register set #8 is selected. Individual registers from alternate register sets may be selected with the  $\underline{MOV}$  instruction.

# **Exception Stack**

The program counter and status bits are pushed onto an internal stack when an exception occurs. This stack is only eight entries deep as that is the maximum amount of nesting that can occur. Further nesting of exceptions can be achieved by saving the state contained in the exception registers.

# **Exception Vectoring**

Exceptions are handled through a vector table. The vector table has eight entries, one for each operating level the core may be running at. The location of the vector table is determined by TVEC[0]. If the core is operating at level four for instance and an interrupt occurs vector table address number four is used for the interrupt handler. Note that the interrupt automatically switches the core to operating level zero, privilege level zero. An exception handler at the machine level may redirect exceptions to a lower level handler identified in one of the vector registers. More specific exception information is supplied in the cause register.

| Operating<br>Level | Address (If TVEC[0]<br>contains \$FFFC0000) |                                             |

|--------------------|---------------------------------------------|---------------------------------------------|

| 0                  | \$FFFC0000                                  | Handler for operating level zero interrupt  |

| 1                  | \$FFFC0020                                  |                                             |

| 2                  | \$FFFC0040                                  |                                             |

| 3                  | \$FFFC0060                                  |                                             |

| 4                  | \$FFFC0080                                  |                                             |

| 5                  | \$FFFC00A0                                  |                                             |

| 6                  | \$FFFC00C0                                  |                                             |

| 7                  | \$FFFC00E0                                  | handler for operating level seven interrupt |

# Reset

The core begins executing instructions at address \$FFFC0100. All registers are in an undefined state. Register set #8 is selected.

# **Exception Cause Codes**

The following table outlines the cause code for a given purpose. These codes are specific to FT64. Under the HW column an 'x' indicates that the exception is internally generated by the processor; the cause code is hard-wired to that use. An 'e' indicates an externally generated interrupt, the usage may vary depending on the system.

| Cause |       | HW | Description               |

|-------|-------|----|---------------------------|

| Code  |       |    |                           |

| 0     |       |    |                           |

| 1     |       |    |                           |

| 2     |       |    | FMTK Scheduler            |

| 432   |       | e  |                           |

| 433   | KRST  | e  | Keyboard reset interrupt  |

| 434   | MSI   | e  | Millisecond Interrupt     |

| 435   | TICK  | e  | FMTK Tick Interrupt       |

|       |       |    |                           |

| 463   | KBD   | e  | Keyboard interrupt        |

| 480   | SSM   | х  | single step               |

| 481   | DBG   | х  | debug exception           |

| 482   | TGT   | х  | call target exception     |

| 483   | MEM   | Х  | memory fault              |

| 484   | IADR  | х  | bad instruction address   |

| 485   | UNIMP | х  | unimplemented instruction |

| 486   | FLT   | Х  | floating point exception  |

| 487   | CHK   | х  | bounds check exception    |

| 488   | DBZ   | х  | divide by zero            |

| 489   | OFL   | Х  | overflow                  |

| 493   | FLT   | х  | floating point exception  |

| 497   | EXF   | х  | Executable fault          |

| 498   | DWF   | х  | Data write fault          |

| 499   | DRF   | Х  | data read fault           |

| 500   | SGB   | Х  | segment bounds violation  |

| 501   | PRIV  | Х  | privilege level violation |

|       |       |    |                           |

|       |       |    |                           |

| 504   | STK   | Х  | stack fault               |

| 505   | CPF   | Х  | code page fault           |

| 506   | DPF   | Х  | data page fault           |

| 508   | DBE   | Х  | data bus error            |

| 509   | IBE   | Х  | instruction bus error     |

| 510   | NMI   | Х  | Non-maskable interrupt    |

|       |       |    |                           |

# Simplified Paged Memory Management Unit

# **Overview**

One option for memory management is a simplified paged memory management unit. Memory management by the MMU includes virtual to physical address mapping and read/write/execute permissions. The MMU divides memory into 64kB or 4MiB pages depending on the setting in PCR2.

# 64kiB pages

Processor address bits 16 to 25 are used as a ten bit index into a mapping table to find the physical page. The MMU remaps the ten address bits into a sixteen bit value used as address bits 16 to 31 when accessing a physical address. The lower sixteen bits of the address pass through the MMU unchanged. The maximum amount of memory that may be mapped in the MMU is 64MiB per map out of a pool of 4GiB. Addresses with the most significant six bits set are not mapped.

# 4MiB pages

Some tasks require a lot of memory and a 64MB map isn't sufficient. For instance, while in machine mode the core requires access to the entire address range. A memory page size of 4MiB may be selected by setting the bit corresponding to the memory map in PCR2.

Processor address bits 22 to 31 are used as a ten bit index into a mapping table to find the physical page. The MMU remaps the ten address bits into a ten bit value used as address bits 22 to 31 when accessing a physical address. The lower 22 bits of the address pass through the MMU unchanged. The maximum amount of memory that may be mapped in the MMU is 4GiB per map out of a pool of 4GiB. Addresses with the most significant six bits set are not mapped.

# **Map Tables**

The mapping tables for memory management are stored directly in the MMU rather than being stored in main memory as is commonly done. The MMU supports up to 64 independent mapping tables. Only a single mapping table may be active at one time. The active mapping table is set in the paging control register (CSR #3) bits 0 to 5 - called the operate key. Mapping tables may be shared between tasks.

# Map Caching / TLB

There isn't a need for a TLB or ATC as the entire mapping table is contained in the MMU. A TLB isn't required. Address mapping is still only two cycles.

# **Operate Key**

The operate key controls which mapping table is actively mapping the memory space. The operate key is located in CSR #3 bits 0 to 5. The operate key is similar to an ASID (address space identifier). The operate key is also used as part of the cores cache tags. When the operate key changes due to a task switch, the cache does not have to be invalidated.

# Access Key

The MMU mapping tables are present at I/O address \$FFDC4000 to \$FFDC4FFF. All the mapping tables share the same I/O space. Only one mapping table is visible in the address space at one time. Which table is visible is controlled by an access key. The access key is located in the paging control register (CSR #3) bits 8 to 13.

# **Address Pass-through**

Addresses pass through the MMU unaltered until the mapping enable bit is set. Until mapping is enabled, the physical address will match the virtual address. Additionally address bits 0 to 15 pass through the MMU unaltered.

# **Mapping Table Layout**

|     | D20 | D19 | D18 | D17 | D16 | D15  | D14  | D13  | D12  | D11  | D10  | D9   | D8   | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| 000 | S1  | S0  | W   | R   | Х   | PA31 | PA30 | PA29 | PA28 | PA27 | PA26 | PA25 | PA24 | PA23 | PA22 | PA21 | PA20 | PA19 | PA18 | PA17 | PA16 |

| 004 | S1  | S0  | W   | R   | Х   | PA31 | PA30 | PA29 | PA28 | PA27 | PA26 | PA25 | PA24 | PA23 | PA22 | PA21 | PA20 | PA19 | PA18 | PA17 | PA16 |

|     |     |     |     |     |     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| FFC | S1  | S0  | W   | R   | Х   | PA31 | PA30 | PA29 | PA28 | PA27 | PA26 | PA25 | PA24 | PA23 | PA22 | PA21 | PA20 | PA19 | PA18 | PA17 | PA16 |

|     |     |     |     |     |     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

PAnn = physical address

X = executable page indicator.

W = writeable data page indicator.

R = readable data page indicator.

Note the low order six bits are not used for 4MiB pages.

S1,S0 = two bits for program use

# PCR- Paging Control Register Layout

| 0  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>v</b>   |           |    |      |    |    |    |                  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|----|------|----|----|----|------------------|

| 31 | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |           | 14 | 13   | 8  | 76 | 5  | 0                |

| PE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ~18        |           |    | AKey | /6 | ~  | OK | Key <sub>6</sub> |

| DE | $D_{2,2} = E_{2,2} + L_{1,2} + L_{1$ | amphilad O | 1 1. 1 1) |    |      |    |    |    |                  |

PE = Paging Enable (1=enabled, 0 = disabled) AKey = Access Key

OKey = Operate Key

# PCR2 – Page Size

This register controls the memory page size. Each bit in the register corresponds to a memory map. Memory may be paged in either 64kiB or 4MiB pages. All pages in a map have the same size.

# Latency

The address map operation when enabled has two cycles of latency. In the case of instructions address translation only takes place on a cache miss when the cache needs to be loaded from main memory.

# **Instruction Set Description**

# **Formats**

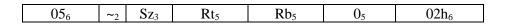

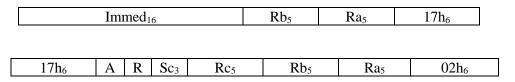

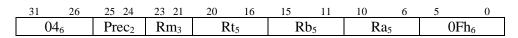

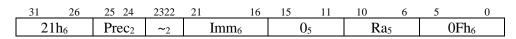

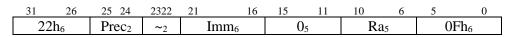

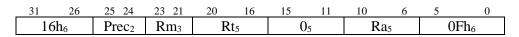

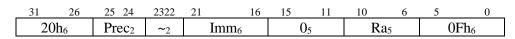

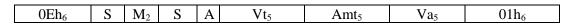

Instructions have a fixed 32 bit format. There are only a handful of different instruction formats. The opcode, Ra, Rb, and Rc fields always occur in the same place in an instruction to simplify decoding and keep the register read address which is needed prior to enqueue at a fixed decoding location. The Rt field is allowed to float around to make the instruction encoding easier. In a pipelined processor there is usually at least one clock cycle before Rt is used meaning it has time to be shifted around before it's use.

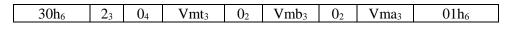

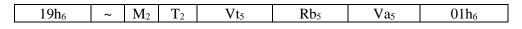

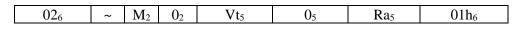

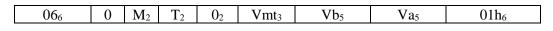

|                                                     | In                                     | nmed <sub>16</sub> |                       |                                  | Rt <sub>5</sub>    | Ra <sub>5</sub> | Opcode <sub>6</sub>   | RI   |

|-----------------------------------------------------|----------------------------------------|--------------------|-----------------------|----------------------------------|--------------------|-----------------|-----------------------|------|

| Funct <sub>4</sub>                                  | Funct <sub>4</sub> Immed <sub>12</sub> |                    |                       |                                  |                    | Ra <sub>5</sub> | Opcode <sub>6</sub>   | RI12 |

| Funct <sub>6</sub>                                  |                                        | -2 5               | Sz3                   | Rt <sub>5</sub>                  | Rb <sub>5</sub>    | Ra <sub>5</sub> | Opcode <sub>6</sub>   | RR   |

| 016                                                 |                                        | $\sim_2$           | Sz <sub>3</sub>       | Funct <sub>5</sub>               | Rt <sub>5</sub>    | Ra <sub>5</sub> | Opcode <sub>6</sub>   | R1   |

| Funct <sub>6</sub>                                  |                                        | Funct <sub>4</sub> | E                     | Rt <sub>5</sub>                  | Rb <sub>5</sub>    | Ra <sub>5</sub> | Opcode <sub>6</sub>   | SR   |

| Funct <sub>6</sub>                                  |                                        | Funct <sub>4</sub> |                       | Immed <sub>6</sub>               | Rt <sub>5</sub>    | Ra <sub>5</sub> | Opcode <sub>6</sub>   | SI   |

| Funct <sub>4</sub>                                  | Ν                                      | le <sub>6</sub>    |                       | $Mb_6$                           | Rt <sub>5</sub>    | Ra <sub>5</sub> | Opcode <sub>6</sub>   | BF   |

| Di                                                  | $sp_{10}$                              |                    | $P_2$                 | Cond <sub>4</sub>                | Rb <sub>5</sub>    | Ra <sub>5</sub> | Opcode <sub>5</sub> D | BD   |

| Di                                                  | sp <sub>10</sub>                       |                    | <b>P</b> <sub>2</sub> | Cond <sub>3</sub>                | Bitno <sub>6</sub> | Ra <sub>5</sub> | Opcode <sub>5</sub> D | BB   |

| ~5                                                  | <b>P</b> <sub>2</sub>                  | Co                 | nd4                   | $Rc_5$                           | Rb <sub>5</sub>    | Ra <sub>5</sub> | Opcode <sub>6</sub>   | BR   |

| Funct <sub>6</sub>                                  | Funct <sub>6</sub> Fn <sub>3</sub> S   |                    | $Sc_2$                | Rt <sub>5</sub> /Rc <sub>5</sub> | Rb <sub>5</sub>    | Ra <sub>5</sub> | Opcode <sub>6</sub>   | MX   |

| Op <sub>2</sub> OL <sub>3</sub> Regno <sub>11</sub> |                                        |                    |                       | 1                                | $Rt_5$             | Ra <sub>5</sub> | Opcode <sub>6</sub>   | CSR  |

|                                                     |                                        |                    | A                     | Address <sub>26</sub>            |                    |                 | Opcode <sub>6</sub>   | JC   |

| Funct <sub>6</sub>                                  | Prec <sub>2</sub>                      | Rr                 | n <sub>3</sub>        | Rt <sub>5</sub>                  | Rb <sub>5</sub>    | Ra <sub>5</sub> | Opcode <sub>6</sub>   | FLT  |

There are a handful of additional formats primarily for control type instructions. See the particular instruction for the exact format used and additional information.

| Format | Instruction Group                                          |

|--------|------------------------------------------------------------|

| RI     | register-immediate and load / store with displacement      |

| RI12   | register-immediate 12, set and load volatile instructions. |

| RR     | register-register, two source registers                    |

| R1     | single source register                                     |

| SR     | shift register-register                                    |

| SI     | shift register-immediate                                   |

| BF     | bitfield                                                   |

| BD     | branch with displacement                                   |

| BB     | branch on bit set / clear                                  |

| BR     | branch to register                                         |

| MX     | memory indexed                                             |

| CSR    | control and status register access                         |

| JC     | jump and call                                              |

| FLT    | floating-point                                             |

# **Operation Sizes**

Many instructions have an option to process data in sub-word data sizes including bytes, chars, and half-words. Typically, sized operations are supported only with register-register instructions. Instructions using immediate values always operate on whole words.

# SIMD

Single instruction multiple data operations treat the 64 bit operands as multiple independent lanes of data depending on the size selected. For a half-word size the operands are treated as two independent 32 bit operands. For a character size the operands are treated as four independent 16 bit operands. SIMD operations are selected by setting the parallel operation bit in the instruction (the most significant bit of the size field).

# **Arithmetic Operations**

Arithmetic operations include addition, subtraction, comparison, multiplication and division.

# **Logical Operations**

Logical operations include bitwise and, or, and exclusive or. Inverted logical ops are also available for register instruction forms (nand, nor, and exnor).

# **Memory Operations**

Memory operations include loads and stores of bytes, words or half-words. There isn't yet a full complement of memory operations in order to keep the size of the core smaller. The core can perform loads and stores using indexed addressing.

#### Loads

Loads may execute speculatively. They may occur out of program order. A load will be issued provided there is no address overlap with a previous memory operation.

#### Stores

Stores will not be issued by the core until it is known that the store can be guaranteed to execute. Unlike a load, a store cannot be executed speculatively. This means no prior instruction will exception and no change of control flow will take place before the store. Stores always write through to memory. A store instruction can't be committed to the machine state until exceptions are checked for during the store operation. Until the operation to memory is complete the store can't commit. However, the store operation is marked as "done" as soon as it's issued so that other instructions may continue to execute. Much of the latency of a store operation is then hidden.

## **Control Flow Instructions**

Control flow instructions include call, return, jumps and branches, breakpoint and return instructions. All controls transfers take place at the fetch stage of the processor and if a predicted fetch direction turns out to be incorrect it is corrected during the execution stage of the instruction.

#### Call

Call instruction flow transfer takes place immediately in the fetch stage of the core. The call return address is pushed onto the return address stack predictor. When the call instruction executes the return address is stored in the return address register.

### Return

Return instructions are predicted during the fetch stage of the core using a return address predictor. The return instruction is also capable of adjusting the stack pointer.

# **Conditional Branches**

Conditional branches are predicted using a (2,2) correlating branch predictor.

#### Breakpoint

Breakpoint instructions cause some of the cores state to be stored on internal stacks. The stored state includes the program counter, interrupt mask, privilege level, and operating level. The internal stacks are eight entries deep; this is the maximum amount of nesting that can occur. The breakpoint instruction specifies a number of instruction words to skip over to determine point of return.

#### **Exception (breakpoint) Return**

The exception return instruction unstacks the state previously stacked by a breakpoint instruction.

#### **Clock cycles**

The clock cycles indicated are only approximate. An attempt has been made to give a relative indication between instructions of the clocks required. The core hasn't under gone significant timing measurements. Many common instructions which can execute in only ½ of a clock cycle, for example add and subtract, indicate a clock cycle time of 1. A number of instructions have single cycle execution times because they may only execute on ALU #0.

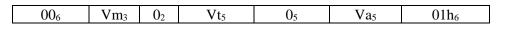

# **ABS – Absolute Value**

# **Description:**

This instruction takes the absolute value of a register and places the result in a target register.

# **Instruction Format:**

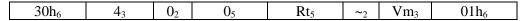

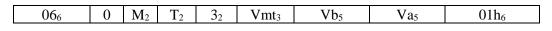

| $01_6$ ~2 Sz <sub>3</sub> 4 <sub>5</sub> | Rt <sub>5</sub> | Ra <sub>5</sub> | 02h <sub>6</sub> |

|------------------------------------------|-----------------|-----------------|------------------|

|------------------------------------------|-----------------|-----------------|------------------|

# Clock Cycles: 1

# Execution Units: ALU #0 only

# **Operation:**

If Ra < 0Rt = -Raelse Rt = Ra

Exceptions: none

Notes:

| Sz <sub>3</sub> |               |

|-----------------|---------------|

| 0               | Byte          |

| 1               | Char          |

| 2               | Half          |

| 3               | Word          |

| 4               | Byte Parallel |

| 5               | Char Parallel |

| 6               | Half Parallel |

| 7               | Word          |

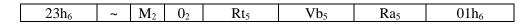

# **ADD - Addition**

# Description:

Add two values. The first operand must be in a register. The second operand may be in a register or may be an immediate value specified in the instruction.

Instruction Format:

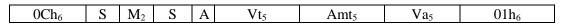

| Immed   | Rt₅  | Ra <sub>5</sub> | 04h6  |

|---------|------|-----------------|-------|

| minedio | 1115 | itus            | 04110 |

| _ |     |            |    |                 |                 | 0      |        |         |

|---|-----|------------|----|-----------------|-----------------|--------|--------|---------|

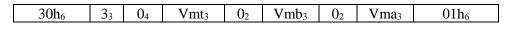

|   | 046 | <b>~</b> 1 | Ov | Sz <sub>3</sub> | Rt <sub>5</sub> | $Rb_5$ | $Ra_5$ | $02h_6$ |

| Ov |                                                            |

|----|------------------------------------------------------------|

| 0  | no overflow                                                |

| 1  | overflow exception if overflow occurred and enabled in AEC |

Overflow works properly only on 64 bit values.

Instruction Format:

This format performs the 'add' operation with an immediate value to one of four quadrants of the target register. It may be used to build a 64 bit constant in a register. The immediate is sign extended to 64 bits then shifted by 0, 16, 32 or 48 bits to the left.

|  | Immed <sub>16</sub> | Rt <sub>5</sub> | 13 | <b>Q</b> <sub>2</sub> | 1Ah <sub>6</sub> |

|--|---------------------|-----------------|----|-----------------------|------------------|

|--|---------------------|-----------------|----|-----------------------|------------------|

| Q2 | Bits     |

|----|----------|

| 0  | 0 to 15  |

| 1  | 16 to 31 |

| 2  | 32 to 47 |

| 3  | 48 to 63 |

# Clock Cycles: 0.5

**Execution Units:** All ALU's

**Exceptions:**

The immediate form of the instruction will not cause an exception. The registered form of the instruction may cause an overflow exception if enabled in the AEC register.

Notes:

For sub-word forms the part of the register updated corresponds to the size selected. For instance, if a byte operation is specified then only the low order eight bits of the target register is updated, the remaining bits hold their current value. For parallel operation forms the registers are treated as

if they were a group of registers corresponding to the size selected. And the same operation is performed on each part of the register. For parallel forms the entire register is updated.

| Sz <sub>3</sub> |               |

|-----------------|---------------|

| 0               | Byte          |

| 1               | Char          |

| 2               | Half          |

| 3               | Word          |

| 4               | Byte Parallel |

| 5               | Char Parallel |

| 6               | Half Parallel |

| 7               | Word          |

# **AMO – Atomic Memory Operation**

Description:

The atomic memory operations read from memory addressed by the Ra register and store the value in Rt. As a second step the value from memory is combined with the value in register Rb according to one of the available functions then stored back into the memory addressed by Ra.

Instruction Format:

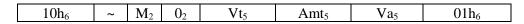

| Funct_6AR $Sz_3$ $Rt_5$ $Rb_5$ $Rational State$ | $1_5$ $2Fh_6$ |

|-------------------------------------------------|---------------|

Instruction Format (immediate operand):

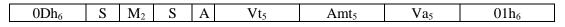

| Funct <sub>6</sub> | А | R | SZ3 | Imm <sub>5</sub> | Rt <sub>5</sub> | Ra <sub>5</sub> | $2Fh_6$ |

|--------------------|---|---|-----|------------------|-----------------|-----------------|---------|

| 1 uneto            |   |   | 025 | mmy              | Itt.            | ituj            | 21 110  |

| Funct <sub>6</sub> | Mnemonic | Operation<br>Performed |                                                                |

|--------------------|----------|------------------------|----------------------------------------------------------------|

| 01                 | swap     | swap                   | memory[Ra] = Rb                                                |

| 04                 | add      | addition               | memory[Ra] = memory[Ra] + Rb                                   |

| 08                 | and      | bitwise and            | memory[Ra] = memory[Ra] & Rb                                   |

| 09                 | or       | bitwise or             | memory[Ra] = memory[Ra]   Rb                                   |

| 0A                 | xor      | bitwise exclusive or   | memory[Ra] = memory[Ra] ^ Rb                                   |

| 0C                 | shl      | shift left             | memory[Ra] = memory[Ra] << Rb                                  |

| 0D                 | shr      | shift right            | memory[Ra] = memory[Ra] >> Rb                                  |

| 1C                 |          |                        | memory[De]memory[De] < Dh 9 memory[De]                         |

|                    | min      | minimum                | <pre>memory[Ra] = memory[Ra] &lt; Rb ? memory[Ra] : Rb</pre>   |

| 1D                 | max      | maximum                | <pre>memory[Ra] = memory[Ra] &gt;Rb ? memory[Ra] : Rb</pre>    |

| 1E                 | minu     | minimum unsigned       | <pre>memory[Ra] = memory[Ra] &lt; Rb ? memory[Ra] : Rb</pre>   |

| 1F                 | maxu     | maximum<br>unsigned    | <pre>memory[Ra] = memory[Ra] &gt; Rb ? memory[Ra] : Rb</pre>   |

| 20                 | swapi    | swap                   | memory[Ra] = imm                                               |

| 24                 | addi     | addition               | memory[Ra] = memory[Ra] + imm                                  |

| 28                 | andi     | bitwise and            | memory[Ra] = memory[Ra] & imm                                  |

| 29                 | ori      | bitwise or             | memory[Ra] = memory[Ra]   imm                                  |

| 2A                 | xori     | bitwise exclusive or   | memory[Ra] = memory[Ra] ^ imm                                  |

| 2C                 | shli     | shift left             | memory[Ra] = memory[Ra] << imm                                 |

| 2D                 | shri     | shift right            | memory[Ra] = memory[Ra] >> imm                                 |

|                    |          |                        |                                                                |

| 3C                 | mini     | minimum                | <pre>memory[Ra] = memory[Ra] &lt; imm ? memory[Ra] : imm</pre> |

| 3D | maxi  | maximum | memory[Ra] = memory[Ra] > imm ? |

|----|-------|---------|---------------------------------|

|    |       |         | memory[Ra] : imm                |

| 3E | minui | minimum | memory[Ra] = memory[Ra] < imm ? |

|    |       |         | memory[Ra] : imm                |

| 3F | maxui | maximum | memory[Ra] = memory[Ra] > imm ? |

|    |       |         | memory[Ra] : imm                |

| Sz <sub>2</sub> |      |

|-----------------|------|

| 0               | Byte |

| 1               | Char |

| 2               | Half |

| 3               | Word |

Acquire and release bits determine the ordering of memory operations.

A = acquire - 1 = no following memory operations can take place before this one

R = release - 1 = this memory operation cannot take place before prior ones.

All combinations of A, R are allowed.

# AND – Bitwise And

Description:

Perform a bitwise 'and' operation between operands.

Instruction Format:

The immediate value is sign extended on the left before use.

| Immed <sub>16</sub> | Rt <sub>5</sub> | Ra <sub>5</sub> | $08h_6$ |

|---------------------|-----------------|-----------------|---------|

|---------------------|-----------------|-----------------|---------|

Rt = Ra & Rb

| 086 | ~2 | Sz <sub>3</sub> | Rt <sub>5</sub> | Rb <sub>5</sub> | Ra <sub>5</sub> | $02h_6$ |