# **UART2BUS Open Source**

# **Verificaiton Plan**

# **Opencores.com**

Hangahl.

VLSI Verification Engineer

#### **Table of Contents**

| About the Document                   | 3  |

|--------------------------------------|----|

| Description                          | 3  |

| References                           | 3  |

| Log Details                          | 3  |

| Design Specifications                |    |

| Design Port-list                     | 4  |

| Features                             |    |

| System Behavioral Description        | 7  |

| Verification Levels & Required Tools | 8  |

| Verification Levels                  | 8  |

| Required Tools                       | 8  |

| Environment Configurations           | 8  |

| Methodology & Test Scenario          |    |

| Methodology                          | 9  |

| Testing Scenario                     | 12 |

| Coverage Requirements                | 16 |

|                                      |    |

#### **Index of Tables**

| Log details                | 3 |

|----------------------------|---|

| Design Port-List           |   |

| Environment Configurations |   |

| Transaction Attributes     |   |

| UART Tests                 |   |

|                            |   |

#### **Index of Figures**

| Design Entity          | 4 |

|------------------------|---|

| TestBench Architecture | 9 |

# **About the Document**

### Description

This document describes the verification plan used to verify UART2BUS Open-cores project Released by Moti Litochevski

#### References

- Bruce Wile, John Goss, Wolfgang Roesner Comprehensive Functional Verification The Complete Industry Cycle Systems on Silicon (2005).

- System Verilog For Verification a guide to learning the test-bench language features by Chris Spear Gregory J Tumbash (2012).

- A Practical Guide to Adopting the Universal Verification Methodology (UVM) by Sharon Rosenberg, Kathleen Meade Cadence Design Systems (2010).

### Log Details

| Table 1: Log | details |

|--------------|---------|

|--------------|---------|

| Version | Date              | Editor                                | Description                                                   |  |

|---------|-------------------|---------------------------------------|---------------------------------------------------------------|--|

| 1       | December 23, 2015 | Hany Salah                            | Document creation                                             |  |

|         |                   |                                       | Add Design Entity                                             |  |

| 2       | December 24, 2015 | Hany Salah                            | Add Design Specifications                                     |  |

|         |                   |                                       | Add System Behavioral Description                             |  |

|         |                   |                                       | Modify Design Entity                                          |  |

| 3       | December 25, 2015 | Hany Salah                            | Improve System Behavioral Description                         |  |

|         |                   |                                       | Modify Design Specifications                                  |  |

| 4       | December 29, 2015 | Hany Salah                            | Modify System Behavioral Description.                         |  |

|         |                   |                                       | Create Test Plan.                                             |  |

| 5       | December 30, 2015 | Hany Salah                            | Iany SalahImprove Test Plan (UART Features).                  |  |

| 6       | December 31, 2015 | Hany Salah • Add Transaction Content. |                                                               |  |

| 7       | January 01, 2016  | Hany Salah                            | • Improve Test Plan (Non UART Features &                      |  |

|         |                   |                                       | Combined Tests & change the tests                             |  |

|         |                   |                                       | serialization).                                               |  |

| 8       | January 11, 2016  | Hany Salah                            | Add Buad Rate Testbench calculations.                         |  |

|         |                   |                                       | Modify System Behavioral Description                          |  |

| 9       | January 19, 2016  | Hany Salah                            | <ul><li>Add UART specifications (start, stop bits).</li></ul> |  |

| 10      | January 24, 2016  | Hany Salah                            | Divide UART fields into commands                              |  |

|         |                   |                                       | Add Environment Configurations                                |  |

| Version | Date             | Editor     |   | Description                       |

|---------|------------------|------------|---|-----------------------------------|

| 11      | January 29, 2016 | Hany Salah | • | Modify Test Plan                  |

|         |                  |            | ٠ | Modify Environment Configurations |

# **Design Specifications**

#### **Design Port-list**

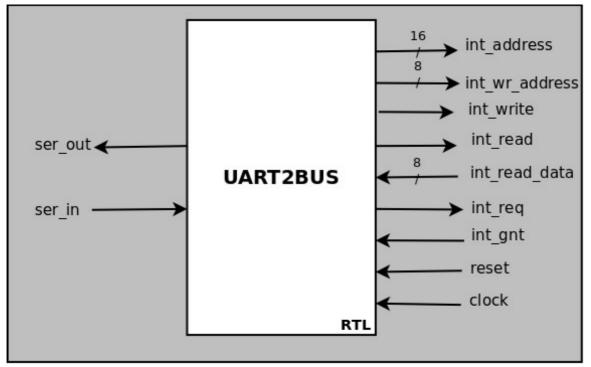

figure 1: Design Entity

| Name        | Polarity | Width  | Direction | Description                    |

|-------------|----------|--------|-----------|--------------------------------|

| clock       |          | 1-bit  | IN        | Global Core Clock signal       |

| reset       | high     | 1-bit  | IN        | Global Core Asynchronous Reset |

| int_address |          | 16-bit | OUT       | Address Bus To Register File   |

| int_wr_data |          | 8-bit  | OUT       | Write Data To Register File    |

| int_write   | high     | 1-bit  | OUT       | Write Control To Register File |

| int_read    | high     | 1-bit  | OUT       | Read Control To Register File  |

| int_rd_data |          | 8-bit  | IN        | Data Read From Register File   |

| int_req     | high     | 1-bit  | OUT       | Request Internal bus access    |

| int_gnt     | high     | 1-bit  | IN        | Grant Internal bus access      |

| ser_in      |          | 1-bit  | IN        | Serial Data Input              |

#### Table 2: Design Port-List

| Name    | Polarity | Width | Direction | Description        |

|---------|----------|-------|-----------|--------------------|

| ser_out |          | 1-bit | OUT       | Serial Data Output |

#### **Features**

- UART Commands are divided into fields and each field includes one byte or more.

- Each byte is sent in between two standard bits; start and stop.

- Start bit is zero while the stop bit is one.

- Support two modes of operation

- Text mode command

- All values are in HEX format.

- Space is represented as 0x20

- Tab is represented as 0x09

- LF is represented as 0x0A

- CR is represented as 0x0D

- Both spaces and tabs are considered as white spaces.

- Both LF and CR are considered as End Of Line (EOL).

- Includes only two commands; address read and address write commands

- Address read command

- 'R' or 'r'.

- White space single or multiple

- Address to read in 4-digit HEX

- CR or LF character

- On the reception of EOL characters, the core will read the given address and transmit the read value in two HEX character followed by both LF and CR.

- Address write command

- $\circ$  'W' or 'w'.

- White space single or multiple

- Data to write in 2-digit HEX

- White space single or multiple

- Address to write 4-digit Hex

- CR or LF character

- On the reception of EOL characters, the core will write the received data to the given address. No transmission is sent back to the sender.

- Binary mode command

- Support single command with configurable number of bytes

- The first Byte is full of zeros as indicator to the binary command.

- The second Byte is as following

- Bits [7:6]: not used.

- Bits [5:4]: represent the command type

- 2'b00<sup>1</sup>: NOP Command, Send ACK if requested.

- 2'b01: Read Command.

- 2'b10: Write Command.

- 2'b11: Invalid.

- Bits [3:2]: not used.

- Bits [1]<sup>2</sup>: Auto Increment Enable

- 1'b0: Auto Increment Enable.

- 1'b1: Auto Increment Disable.

- Bits [0]: ACK Flag

- 1'b0: Send no acknowledge byte at the command completion

- 1'b1: Send acknowledge byte at the command completion

- The third byte is used to hold the address high byte.

- The forth byte is used to hold the address low byte.

- The fifth byte is used to represent the length of buffer to read or write data.

- "0" Value indicates maximum buffer length which is 256 bytes.

- The bytes numbered from 6 to (length-1) hold the data and its number should be equal to the fifth byte content<sup>3</sup>.

- In response to binary command, the responder should react as following.

- The byte numbered from 1 to data length which is indicated by the request command is filled with the requested data<sup>4</sup>.

- The following byte is the acknowledge<sup>5</sup> one and contain the value of 0x5A.

1 NOP Command would be used to verify that the core responds to UART.

- 2 Auto Increment is often used when reading a buffer from RAM. Otherwise, it's more convenient to turn auto increment off.

- 3 This field exists only in write commands.

- 4 This byte exists only is respond to read commands.

- 5 This byte exists only in case of acknowledge request in the command.

#### **System Behavioral Description**

UART2BUS module is designed to act as either transmitter or receiver. The main clock that the core uses could be calculated from the following relationship

$BaudFrequency = \frac{16 * BaudRate}{gcd(GlobalClockFrequecy, 16 * BaudRate)}$

Where the buad frequency is the actual clock frequency that synchronize both the transmitter and receiver through any data transfer.

Both ser\_out & ser\_in are high in idel state. Each line is only driven by one driver. When its driver is going to start communication, it pulls it down for one baud clock cycle. It's defined as start bit. After that the sent data will be forced bit by bit<sup>6</sup>. And finally one or two stop bits are followed the last bit. The actual number of stop bits is configured through the VIP configurations, and they all are 1's. UART2BUS polling the ser\_in port to capture either the ASCII of 'r', 'R', 'w' and 'W' or the full zero byte otherwise DUT make no response.

In case that the first captured field includes the ASCII of either 'R' or 'r', the DUT expects the next field includes either single or multiple white spaces and then capture the following two fields as the command address. Core wait the following character to be one of EOL and responds with the read data in two hex characters followed by CR and LF characters. Each byte of the sent data should be packed between start and stop bit(s) Any miss-order or non-expected input, core should make no response.

In case that the first field includes the ASCII of either 'W' or 'w', the DUT expects the next field includes either single or multiple white spaces and then capture the following field as the command data. Then it also expects the following field to be single or multiple spaces to capture the next word to be the command address. Finally, core wait the following character to be one of EOL. Any miss-order or non-expected input, core should make no response.

In case that the first field includes zero byte, the DUT capture the following byte. Through this byte, the core detect the command type. In case of invalid command, the core should make no response even if the acknowledge request is activated. The DUT capture the following byte as an address high byte and capture the next byte as an address low byte. The next byte determine the actual data length in bytes. In case of write command, the data bytes follow the length byte. But in case of read command, the command is ended at the end of length byte. Then the core should respond with serial bytes of data equal to the length field in the command. Also according to the acknowledge request bit in the command, the core should follow the data bytes with the unified acknowledge byte.

Regardless of the received command mode or command type, The core will assert int\_req and then wait till int\_gnt signal assertion and then release int\_req. If the received command is write, the core will load int\_address port with the command address and assert int\_write signal and load int\_wr\_data with the data corresponding to the loaded address and then deactivate int\_write signal to terminate bus usage. If the data includes more than one byte, the core would load int\_wr\_data

6 Starting with either the MSB or the LSB is configured through the VIP configurations.

port with successive bytes every clock cycle concurrently with increment the port address content and keep int\_write signal activated till finalize the data transmission. If the received command is read, the core will load int\_address port with the command address and assert int\_read signal. The core should wait the requested data on the next clock cycle and then disable int\_read to terminate the bus usage. If the requested data includes more than one byte, the incremental address will be loaded to the address port every clock cycle and the corresponding data will be captured through the following clock cycle and so on.

# **Verification Levels & Required Tools**

#### **Verification Levels**

• The verification strategy would be black box strategy

#### **Required Tools**

- Sublime Text editor or any other text editor.

- Questasim Advanced Verification CAD

- Universal Verification Methodology package

#### **Environment Configurations**

| Field               | Description                                                           | Possible Choices                                                       |

|---------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|

| Active Edge         | The active clock edge at which, the data is changed on the UART buses | <ul><li> Positive Edge</li><li> Negative Edge</li></ul>                |

| First Bit           | Represent the sequence through which the byte is serialized           | <ul><li>Most Significant bit</li><li>Least Significant bit</li></ul>   |

| Data Mode           | The data representation through the text commands                     | <ul><li>ASCII</li><li>Binary</li></ul>                                 |

| Number of stop bits | The number of stop bits sent after the latest bit of each byte        | <ul><li> One bit</li><li> Two bits</li></ul>                           |

| Number of bits      | The number of bits through each field transfer                        | <ul><li>Seven bits</li><li>Eight bits</li></ul>                        |

| Parity Mode         | The used parity type through each byte.                               | <ul><li> Parity Off</li><li> Parity Even</li><li> Parity Odd</li></ul> |

Table 3: Environment Configurations

| Field             | Description                                                                                                   | Possible Choices |

|-------------------|---------------------------------------------------------------------------------------------------------------|------------------|

| Response Time     | Represent the maximum allowable time through which DUT should respond to the driven request.                  | No limitations   |

| False Data Enable | Enable force false data on the output port within<br>the read command through the both modes; text,<br>binary | • Yes<br>• No    |

# Methodology & Test Scenario

#### Methodology

#### **Test-Bench Architecture**

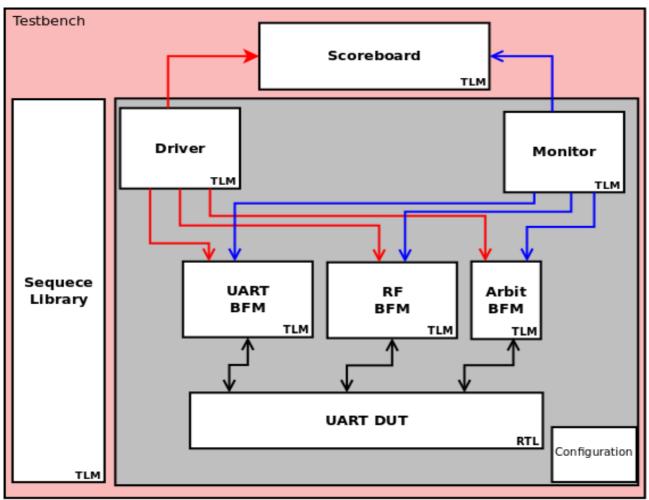

We proposed the following test-bench architecture to verify the functionality of UART2BUS module.

figure 2: TestBench Architecture

- We provide C++ code besides the test-bench to calculate baud frequency to facilitate the usage of UART test-bench.

- Our test-bench will operate on 40 MHz as global clock and 115.2 KHz as baud rate. And then the D-baud frequency is 144 Hz.

- Scoreboard receives transaction from driver and then check the tested address in the register file.

- Bus Functional Model BFM includes three different blocks that are described below

- <u>UART BFM</u>: That act as another UART device and talk with DUT through the two protocol signals.

- <u>RF BFM</u>: That act as memory of 64K bytes and talk with DUT through non-protocol signals

- <u>Arbiter BFM</u>: That act as internal bus arbiter.

#### **Transaction Attributes**

We propose the following transaction attributes so that we could implement our test plan

Table 4: Transaction Attributes

| Туре                   | Identifier    | Description                                                                                                                                                                                                                |

|------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enumerate              | mode          | Represents the mode of command to be one of the following<br>options {text, command, wrong}. Wrong command mode is used<br>to send a tricky fault command to test our DUT.                                                 |

| Byte                   | prefix_wrong  | Represents the wrong prefix that is used in case of wrong mode selection.                                                                                                                                                  |

| Enumerate              | space_type1   | Represents the type of the used white space in the first field to be<br>one of the following options {single, tab, wrong}. Wrong type<br>also is used to push tricky byte in the text mode.                                |

| Enumerate              | space_type2   | Represents the type of the used white space in the second field to<br>be one of the following options {single, tab, wrong}. Wrong type<br>also is used to push tricky byte in the text mode.                               |

| Byte                   | space_wrong1  | Could hold all the 8-bit values except {single or tab} and is used<br>in case of space_type is wrong as the first wrong white space.                                                                                       |

| Byte                   | space_wrong2  | Could hold all the 8-bit values except {single or tab} and is used<br>in case of space_type is wrong as the second wrong white space.                                                                                      |

| Dynamic Array of Bytes | _data         | Could hold all possible values and its length is constrained to be equal to length_data.                                                                                                                                   |

| Dynamic Array of Bytes | false_data    | Used in case of driving inconsiderable data into the serial output<br>port while the DUT reply the read request command. It could<br>hold all possible values and its length is constrained to be equal<br>to length_data> |

| Integer Unsigned       | length_data   | Only in range of [1:256] and equal 1 in case of text command mode.                                                                                                                                                         |

| Enumerate              | false_data_en | Enable forcing false data within the read command.                                                                                                                                                                         |

| Туре      | Identifier  | Description                                                                                                                                       |

|-----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Enumerate | eol_type    | Represents the type of end of line used to be one of the following choices {cr, lf, wrong}. Wrong type is also used to push DUT in tricky manner. |

| Byte      | eol_wrong   | Could hold all 8-bit values except {cr or lf} and is used in case of eol_type is wrong.                                                           |

| Word      | address     | Could hold all the possible values.                                                                                                               |

| Enumerate | command     | Represents the command either to be one of the following choices {read, write, NOP}                                                               |

| Enumerate | ack_req     | Represents the acknowledge request {yes, no}                                                                                                      |

| Enumerate | inc_req     | Represents the incremental address feature request {yes, no}                                                                                      |

| Enumerate | char_type   | Represents the type of prefix in text mode either to be {capital, small}.                                                                         |

| Enumerate | arbit       | Represents the internal bus state either {accept, refuse}                                                                                         |

| Time      | Time before | Idle Time before the main command start.                                                                                                          |

| Time      | Time after  | Idle Time After the finish byte of the main command.                                                                                              |

# **Testing Scenario**

#### Simple Tests

Simple tests include single command per test in one mode which aim to make sure that the design perform the basic operations correctly.

| S.N | Feature                         | <b>Test Procedures</b>                               |

|-----|---------------------------------|------------------------------------------------------|

|     | Wr                              | rite in Text Mode                                    |

| 1   | Could write only a single byte. | 1. Apply UART write request using capital W.         |

|     | • 'W' or 'w'                    | 2. Apply UART write request using small w.           |

|     | • Single space or Tab.          | 3. Apply UART write request using single space only. |

|     | • Data                          | 4. Apply UART write request using tab only.          |

|     | • Single space or Tab.          | 5. Apply UART write request using both single space  |

|     | Address                         | and tab.                                             |

|     | • EOL character                 | 6. Apply UART write request using one wrong spaces   |

|     |                                 | 7. Apply UART write request using two wrong spaces   |

|     |                                 | 8. Apply UART write request to address 0.            |

|     |                                 | 9. Apply UART write request to full range address.   |

|     |                                 | 10. Apply UART write request with data equal 0.      |

|     |                                 | 11. Apply UART write request with full range data.   |

|     |                                 | 12. Apply UART write request using different EOL     |

|     |                                 | character.                                           |

|     |                                 | 13. Apply UART Write request using wrong prefix      |

|     | Re                              | ead in Text Mode                                     |

| 2   | Could read only a single byte   | 1. Apply UART read request using capital R.          |

|     | • 'R' or 'r'.                   | 2. Apply UART read request using small r.            |

|     | • Single space or tab.          | 3. Apply UART read request using single space.       |

|     | • Address                       | 4. Apply UART read request using tab.                |

|     | • EOL                           | 5. Apply UART read request using both space and tab  |

|     | And the response should be      | 6. Apply UART read request using one wrong space.    |

|     | • the read data immediately     | 7. Apply UART read request using two wrong spaces    |

|     | • both LF & CR                  | 8. Apply UART read request to address 0.             |

|     |                                 | 9. Apply UART read request to full range address.    |

|     |                                 | 10. Apply UART read request with data equal 0.       |

|     |                                 | 11. Apply UART read request with full range data.    |

|     |                                 | 12. Apply UART read request using different EOL      |

| S.N | Feature                                                                                         | Test Procedures                                                                                                     |

|-----|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|     |                                                                                                 | character.                                                                                                          |

|     |                                                                                                 | 13. Apply UART read request using wrong prefixe                                                                     |

|     | NOP in Col                                                                                      | nmand Mode                                                                                                          |

| 3   | Could send NOP command with acknowledge request.                                                | 1. Apply UART NOP command with acknowledge bit request and right command mode prefix.                               |

|     | • Unified Prefix                                                                                | 2. Apply UART NOP command with wrong command                                                                        |

|     | • Answer should be only a unified                                                               | prefix and acknowledge request.                                                                                     |

|     | acknowledge character.                                                                          | 3. Apply several UART NOP command to different                                                                      |

|     | • The address content shouldn't be affected.                                                    | locations with different data lengths.                                                                              |

| 4   | Could send NOP command with non<br>acknowledge request acknowledge request<br>• Unified Prefix. | <ol> <li>Apply UART NOP command with non-<br/>acknowledge bit request and right command mode<br/>prefix.</li> </ol> |

|     | • No answer should be exist.                                                                    | 2. Apply UART NOP command with wrong command                                                                        |

|     | • The address content shouldn't be                                                              | prefix and non-acknowledge request.                                                                                 |

|     | affected regardless of command data.                                                            | 3. Apply several UART NOP command to different locations with different data lengths and non-acknowledge request.   |

|     | Write in Col                                                                                    | mmand Mode                                                                                                          |

| 5   | Could send write command including                                                              | 1. Apply UART write command with wrong prefix.                                                                      |

|     | <ul><li>Unified Prefix</li><li>16-bit address.</li></ul>                                        | <ol> <li>Apply UART write commands to different<br/>addresses.</li> </ol>                                           |

|     | <ul><li>Data length varies from 1 to 256 bytes.</li><li>Incremental address ability.</li></ul>  | 3. Apply UART write commands with several data lengths                                                              |

|     | Acknowledge request.                                                                            | 4. Apply UART write command to address 0 with random data.                                                          |

|     |                                                                                                 | 5. Apply UART write command to address 0xFFFF with random data.                                                     |

|     |                                                                                                 | 6. Apply UART write command with acknowledge request.                                                               |

|     |                                                                                                 | 7. Apply UART write command with non-<br>acknowledge request.                                                       |

|     |                                                                                                 | 8. Apply UART write command including single byte                                                                   |

|     |                                                                                                 | 9. Apply UART write command including non-<br>incremental address bit.                                              |

|     |                                                                                                 | 10. Apply UART write command including                                                                              |

| S.N | Feature                                                                                                                                                                                                       | Test Procedures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|     | incremental address bit.                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|     | Read in Co.                                                                                                                                                                                                   | mmand Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 6   | <ul> <li>Could send read command including</li> <li>Unified Prefix.</li> <li>16-bit addresses.</li> <li>The length of requested data would vary from 1 to 256 bytes.</li> <li>Acknowledge request.</li> </ul> | <ol> <li>Apply UART read command with wrong prefix.</li> <li>Apply UART read commands to different<br/>addresses.</li> <li>Apply UART read commands with several data<br/>lengths</li> <li>Apply UART read command to address 0 with<br/>random data.</li> <li>Apply UART read command to address 0xFFFF<br/>with random data.</li> <li>Apply UART read command with acknowledge<br/>request.</li> <li>Apply UART read command with non-acknowledge<br/>request.</li> <li>Apply UART read command including single byte.</li> <li>Apply UART read command including non-<br/>incremental address bit.</li> <li>Apply UART read command including<br/>incremental address bit.</li> </ol> |  |

|     | Inter                                                                                                                                                                                                         | incremental address bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 7   | Should request to access the internal bus and wait for grant                                                                                                                                                  | <ol> <li>Apply UART read or write commands and give the UART the bus grant.</li> <li>Apply UART read or write commands and give no agreement to access internal bus</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|     | Invalid C                                                                                                                                                                                                     | Commands <sup>7</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 8   | Make no response towards invalid commands                                                                                                                                                                     | <ol> <li>Apply Invalid UART command in form of write<br/>binary command.</li> <li>Apply Invalid UART command in form of read<br/>binary command.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

#### **Combined Tests**

Combined tests include more than one command per test and aim to put the DUT into highly complicated processes. And also verify the bus functional model besides the DUT.

7 Invalid commands in frame similar to binary command frame

| S.N | Feature                                    | <b>Test Procedures</b>                  |

|-----|--------------------------------------------|-----------------------------------------|

| 9   | Able To receive commands in text mode and  | 1. Apply read command in text mode.     |

|     | command mode without reconfiguration       | 2. Apply write command in command mode. |

|     |                                            | 3. Apply read command in command mode.  |

|     |                                            | 4. Apply write command in text mode.    |

| 10  | Able to distinguish between the valid and  | 1. Apply four valid commands            |

|     | invalid commands and also able to miss the | 2. Apply invalid command                |

|     | invalid commands in series of valid        | 3. Apply valid command.                 |

|     | commands from different types and modes.   | 4. Apply two invalid commands           |

|     |                                            | 5. Apply valid command                  |

# **Coverage Requirements**