## UoS educational processor - Architecture

# **UoS Educational CPU Architecture**

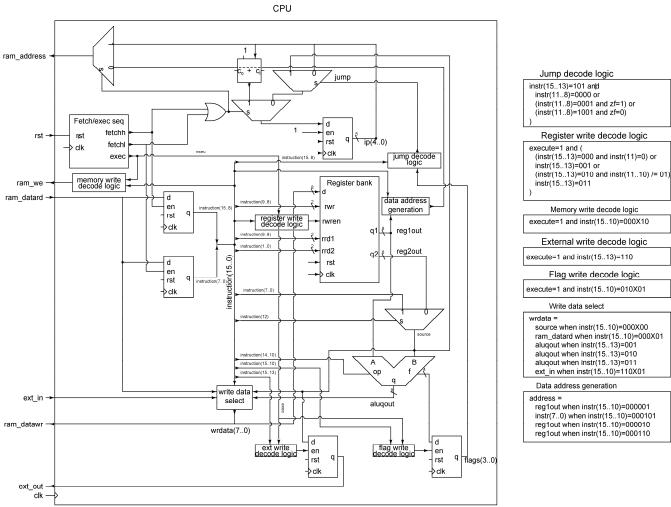

### **CPU**

source when instr(15..10)=000X00 aluqout when instr(15..10)=000X01 aluqout when instr(15..13)=001 aluqout when instr(15..13)=010 aluqout when instr(15..13)=010 aluqout when instr(15..13)=011 ext in when instr(15..10)=110X01

#### Data address generation

reg1out when instr(15..10)=000001 instr(7..0) when instr(15..10)=000101 reg1out when instr(15..10)=000010 reg1out when instr(15..10)=000110

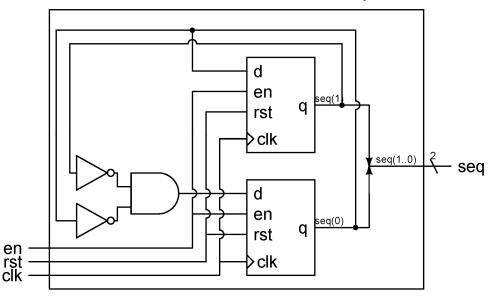

# Instruction fetch/execute state sequence

Instruction fetch/execute state sequence

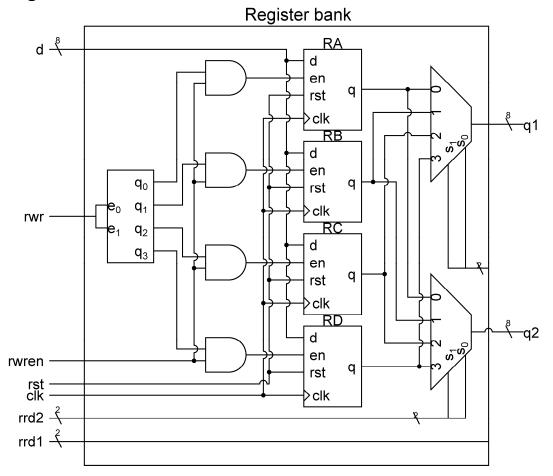

# UoS educational processor - Architecture Register bank

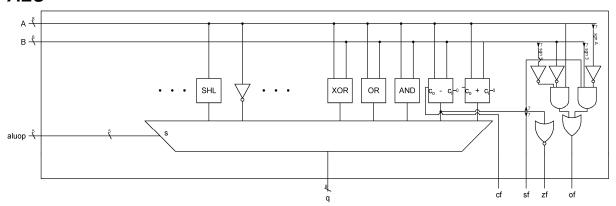

# ALU

Aluop are the 5-bit instruction(14 downto 10). The multiplexer is configured as follows:

| 115 th the troin (1 : the Willes 10). The interpretation is con- |          |

|------------------------------------------------------------------|----------|

| aluop                                                            | Function |

| 01X00                                                            | add      |

| 01X01                                                            | sub      |

| 01X10                                                            | and      |

| 01X11                                                            | or       |

| 10X00                                                            | xor      |

| 10X01                                                            | N/A      |

| 11000                                                            | not      |

| 11001                                                            | shr      |

| 11010                                                            | ror      |

| 11011                                                            | asr      |

| 11100                                                            | rl       |