# Digital Systems and Microprocessor Design (H7068)

# 8.2. Inside UoS Educational Processor

Daniel Roggen d.roggen@sussex.ac.uk

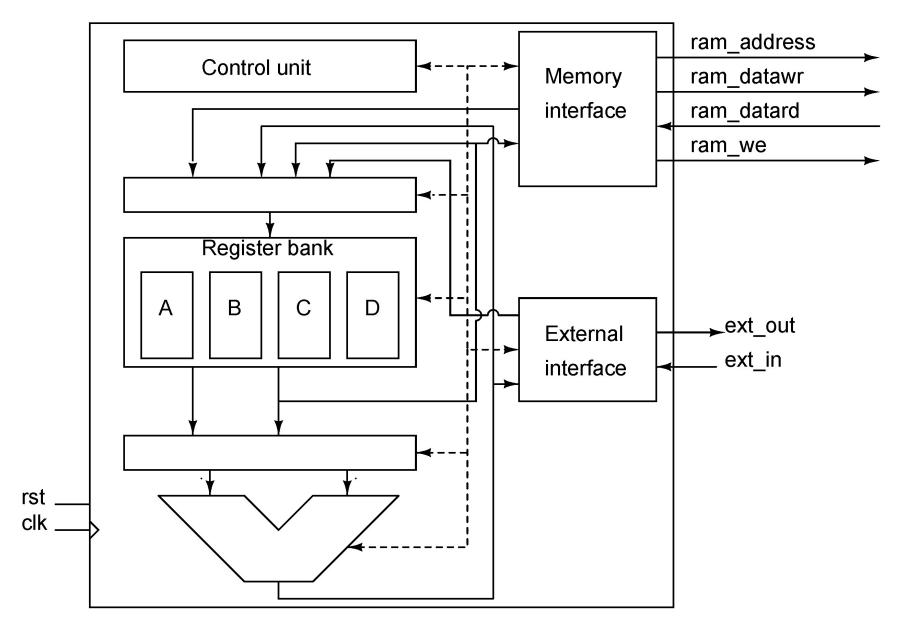

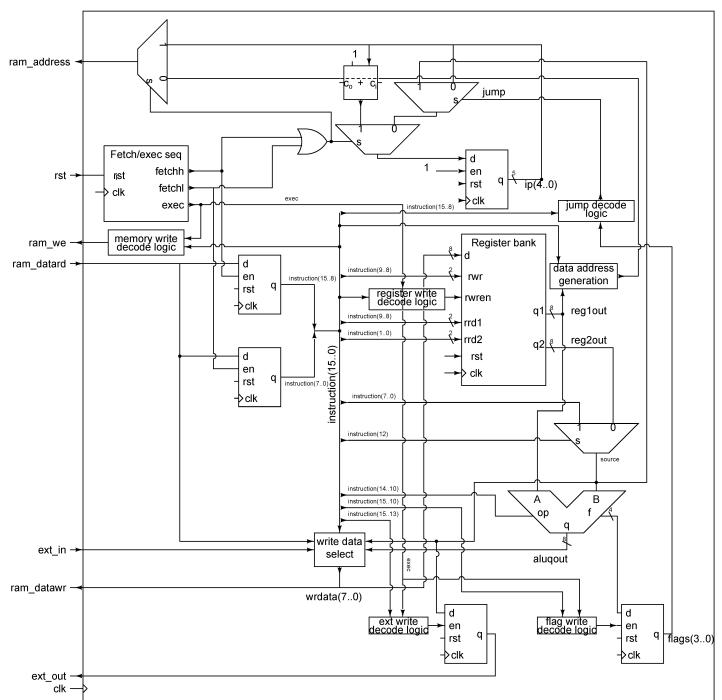

#### Architecture

|  |        | 1 |

|--|--------|---|

|  |        |   |

|  |        |   |

|  |        |   |

|  |        |   |

|  |        |   |

|  |        |   |

|  |        |   |

|  |        |   |

|  | 198.32 |   |

|  |        |   |

|  |        |   |

|  |        |   |

|  |        |   |

# **VHDL** files

- cpu.vhd:

- cpusequencer.vhd:

- cpuregbank.vhd:

- cpualu.vhd:

top file for CPU fetch/execute sequence register file ALU

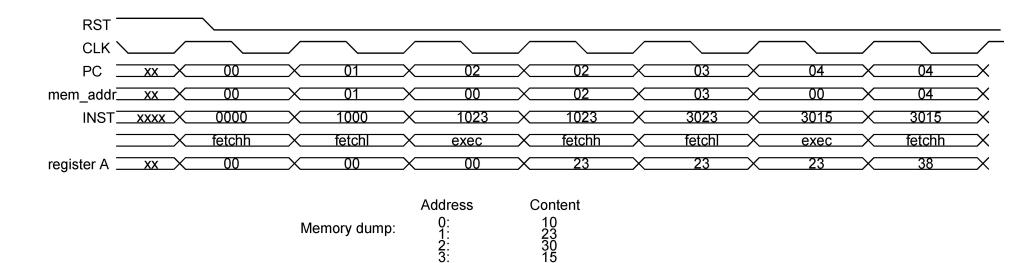

- 3 clock cycles per instruction

- Fetch high

- Fetch low

- Execute...

- Circuit must organize this sequence

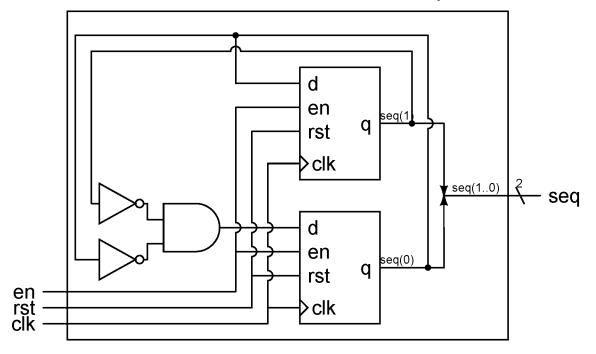

In cpusequencer.vhd

Instruction fetch/execute state sequence

• Up counter until 2 (10b): 00=fetchh, 01=fetchl, 10=exec

```

entity cpusequencer is

port(

clk : in STD_LOGIC;

rst : in STD_LOGIC;

en : in STD_LOGIC;

seq : out STD_LOGIC_VECTOR(1 downto 0)

);

end cpusequencer;

```

- clk: clock

- rst: reset

- en: enable (currently not used: always wired to 1)

- seq: 2-bit code for fetchh, fetchl, exec

| process(clk)                      | clock in sensitivity list                                                |  |  |  |  |  |  |

|-----------------------------------|--------------------------------------------------------------------------|--|--|--|--|--|--|

| -                                 |                                                                          |  |  |  |  |  |  |

| begin<br>if rising_edge(clk) then | All happens on rising clock edge                                         |  |  |  |  |  |  |

| if rst='1' then<br>s<="00";       | Reset                                                                    |  |  |  |  |  |  |

| else                              | Normal behavior: if enabled,                                             |  |  |  |  |  |  |

| if en='1' then                    | increment and wrap around at 2                                           |  |  |  |  |  |  |

| if s="10"                         | then                                                                     |  |  |  |  |  |  |

| s ·                               | <= "00";                                                                 |  |  |  |  |  |  |

| else                              |                                                                          |  |  |  |  |  |  |

| S ·                               | <= s+1;                                                                  |  |  |  |  |  |  |

| end if;                           | • VHDL does additions with '+'!                                          |  |  |  |  |  |  |

| end if;                           | • Not taught in this module.                                             |  |  |  |  |  |  |

| <pre>end if;</pre>                | <ul> <li>Synthesizer chooses an</li> </ul>                               |  |  |  |  |  |  |

| <pre>end if;</pre>                | implementation on its own                                                |  |  |  |  |  |  |

| end process;                      | Choice not critical here with 2                                          |  |  |  |  |  |  |

| seq <= s;                         | bits; with more bits specific<br>adder architectures may be<br>preferred |  |  |  |  |  |  |

- Reminder: move instruction

- Always operation between dst and src, with result in dst

- Let's consider what to read from our register bank:

- The register defined by dst and src (even if we deal with an immediate-this is handled elsewhere

| Instructions instruction(158) |    |     |    |   |      |      |    | Instruction(70) |   |   |   |    |    |   |   |   |

|-------------------------------|----|-----|----|---|------|------|----|-----------------|---|---|---|----|----|---|---|---|

| Move                          | Or | 000 | de |   | dd#m | sd#m | dr | eg              |   |   |   | SI | rc |   |   |   |

| mov r, r                      | 0  | 0   | 0  | 0 | 0    | 0    | r  | r               | - | _ | I | -  | _  | _ | r | r |

| mov r, i                      | 0  | 0   | 0  | 1 | 0    | 0    | r  | r               | i | i | i | i  | i  | i | i | i |

| mov r, [r]                    | 0  | 0   | 0  | 0 | 0    | 1    | r  | r               | - | - | I | I  | -  | - | ۲ | r |

| mov r, [i]                    | 0  | 0   | 0  | 1 | 0    | 1    | r  | r               | i | i | i | i  | i  | i | i | i |

| mov [r], r                    | 0  | 0   | 0  | 0 | 1    | 0    | r  | r               | - | _ | - | -  | _  | - | r | r |

| mov [r], i                    | 0  | 0   | 0  | 1 | 1    | 0    | r  | r               | i | i | i | i  | i  | i | i | i |

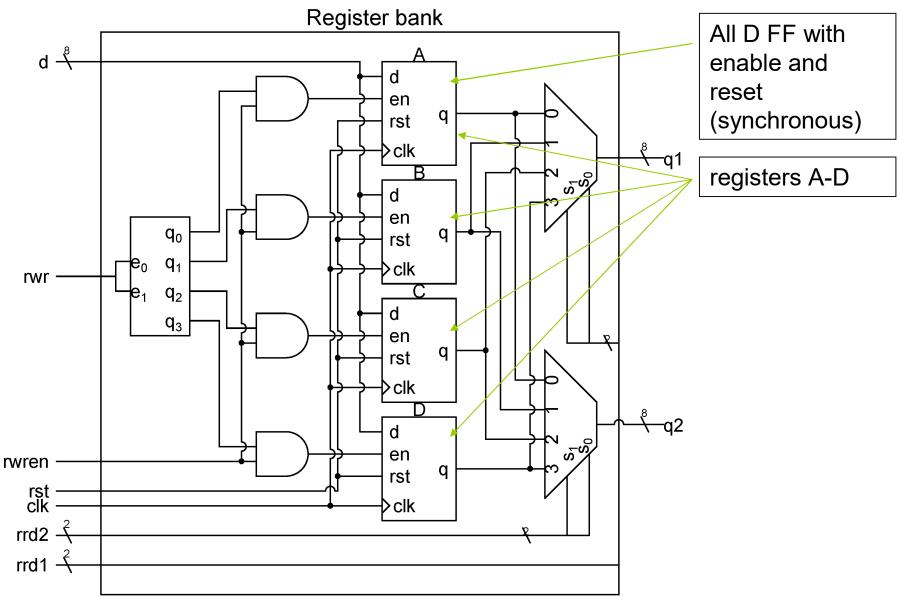

| entity cpuregbank is                               | register to read from<br>(the 2 bits come from                     |  |  |  |  |  |

|----------------------------------------------------|--------------------------------------------------------------------|--|--|--|--|--|

| port(                                              | src or dst in the                                                  |  |  |  |  |  |

| clk : in STD_LOGIC;                                | instruction!)                                                      |  |  |  |  |  |

| <pre>rrd1 : in STD_LOGIC_VECTOR(1 downto 0);</pre> |                                                                    |  |  |  |  |  |

| <pre>rrd2 : in STD_LOGIC_VECTOR(1 downto 0);</pre> | register to write to                                               |  |  |  |  |  |

| <pre>rwr : in STD_LOGIC_VECTOR(1 downto 0);</pre>  | (always dst)                                                       |  |  |  |  |  |

| <pre>rwren : in STD_LOGIC;</pre>                   |                                                                    |  |  |  |  |  |

| <pre>rst : in STD_LOGIC;</pre>                     | rwren: enable write                                                |  |  |  |  |  |

| <pre>d : in STD_LOGIC_VECTOR(7 downto 0);</pre>    | d: data to write                                                   |  |  |  |  |  |

| <pre>q1 : out STD_LOGIC_VECTOR(7 downto 0);</pre>  | outputs of the register                                            |  |  |  |  |  |

| <pre>q2 : out STD_LOGIC_VECTOR(7 downto 0);</pre>  | bank                                                               |  |  |  |  |  |

| Only for debugging                                 |                                                                    |  |  |  |  |  |

| dbg_qa : out STD_LOGIC_VECTOR(7 downto (           | D);                                                                |  |  |  |  |  |

| dbg_qb : out STD_LOGIC_VECTOR(7 downto (           | )<br>This would not be here                                        |  |  |  |  |  |

| dbg_qc : out STD_LOGIC_VECTOR(7 downto (           | in a "production"                                                  |  |  |  |  |  |

| dbg_qd : out STD_LOGIC_VECTOR(7 downto (           | processor: here to                                                 |  |  |  |  |  |

| );<br>end cpuregbank;                              | display the content of<br>the register on the 7<br>segment display |  |  |  |  |  |

| <pre>architecture Behavioral of cpuregbank is     signal enables: STD_LOGIC_VECTOR(3 downto 0);     signal qa,qb,qc,qd: STD_LOGIC_VECTOR(7 downto 0); begin</pre> | enable each register<br>q: output of each<br>register |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| <pre>ra: entity work.dffre generic map (N=&gt;8) port map(clk=&gt;clk,en=&gt;enables(0),rst=&gt;rst,d=&gt;d,q=&gt;qa);</pre>                                      | Instantiate a register                                |

| rb: entity work.dffre generic map (N=>8) port<br>map(clk=>clk,en=>enables(1),rst=>rst,d=>d,q=>qb);                                                                | with reset and enable.                                |

| <pre>rc: entity work.dffre generic map (N=&gt;8) port map(clk=&gt;clk,en=&gt;enables(2),rst=&gt;rst,d=&gt;d,q=&gt;qc);</pre>                                      | Generic map:<br>parameterized register.               |

| rd: entity work.dffre generic map (N=>8) port                                                                                                                     |                                                       |

map(clk=>clk,en=>enables(3),rst=>rst,d=>d,q=>qd);

2-4 decoder: when write is enabled one of the register is enabled for write

first output multiplexer

with rwr select

- enables <="0001" and rwren&rwren&rwren when "00",

- "0010" and rwren&rwren&rwren when "01",

- "0100" and rwren&rwren&rwren when "10",

"1000" and rwren&rwren&rwren when others;

with rrd2 select

q2 <= qa when "00",

qb when "01",

qc when "10",

qd when others;

second output multiplexer

### Register

| entity dffre is                | generic: useful to create components that can be |  |  |  |  |  |  |  |

|--------------------------------|--------------------------------------------------|--|--|--|--|--|--|--|

| generic (N : integer);         |                                                  |  |  |  |  |  |  |  |

| port(                          | parameterized                                    |  |  |  |  |  |  |  |

| clk : in STD_LOGIC;            |                                                  |  |  |  |  |  |  |  |

| <pre>en : in STD_LOGIC;</pre>  |                                                  |  |  |  |  |  |  |  |

| <pre>rst: in STD_LOGIC;</pre>  |                                                  |  |  |  |  |  |  |  |

| d : in STD_LOGIC_VECTOR(N-1    | . downto 0);                                     |  |  |  |  |  |  |  |

| $q$ : out STD_LOGIC_VECTOR (N- | 1 downto 0)                                      |  |  |  |  |  |  |  |

| );                             |                                                  |  |  |  |  |  |  |  |

| end dffre;                     | Here N is the number of bits of the D flip-flop  |  |  |  |  |  |  |  |

architecture Behavioral of dffre is

begin

process(clk)

begin

| 20y=                     |                    |

|--------------------------|--------------------|

| if rising_edge(clk) then | all on rising edge |

| if rst='1' then          | synchronous reset  |

| q<=(others=>'0')         | ;                  |

| else                     |                    |

| if en='1' then           |                    |

| q<=d;                    | copy if enabled    |

| end if;                  |                    |

| end if;                  |                    |

| end if;                  |                    |

end process;

In the component declaration:

```

entity entity_name is

generic (generic list);

port (port list);

end entity_name;

```

In the component instantiation:

label: entity work.comp\_name

generic map (generic\_association\_list)

port map (port\_association\_list);

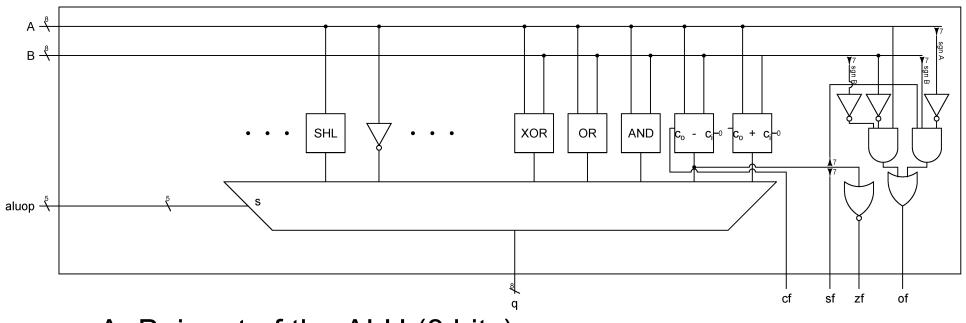

ALU

- A, B: input of the ALU (8 bits)

- aluop: operation to perform (5 bits)

- bit 14 to bit 10 of instruction to identify the type of operation

- (part opcode and part other bits of the instruction)

- Implemented as multiplexer

- flags as discrete logic

# ALU

| Instructions |    | instruction(158) |    |                    |     |    |    |    | Instruction(70) |   |   |    |   |   |   | ) |

|--------------|----|------------------|----|--------------------|-----|----|----|----|-----------------|---|---|----|---|---|---|---|

| ALU 2 op     | oľ | 000              | de | $\overline{R}$ / I | ALU | op | dr | eg |                 |   |   | SI | c |   |   |   |

| add r, r     | 0  | 0                | 1  | 0                  | 0   | 0  | r  | r  | -               | - | - | -  | Ι | - | r | r |

| add r, i     | 0  | 0                | 1  | 1                  | 0   | 0  | r  | r  | i               | i | i | i  | i | i | i | i |

|              |    |                  |    |                    |     |    |    |    |                 |   |   |    |   |   |   |   |

| xor r, r     | 0  | 1                | 0  | 0                  | 0   | 0  | r  | r  | -               | - | - | _  | - | - | r | r |

| Test     | opco<br>de |   | ALU op dr<br>eg |   |   |   |   | mm<br>eg | ed | it | e | / |   |   |

|----------|------------|---|-----------------|---|---|---|---|----------|----|----|---|---|---|---|

| cmp r, r | 0 1 0      | 0 | 0               | 1 | r | r | - | -        | -  | -  | I | I | r | r |

| cmp r, i | 0 1 0      | 1 | 0               | 1 | r | r | i | i        | i  | i  | i | i | i | i |

| Instructions                                                         |    | instruction(158) |    |        |   |   |    |      | I | inst | tru | ct | ion | (7. | . 0 | ) |

|----------------------------------------------------------------------|----|------------------|----|--------|---|---|----|------|---|------|-----|----|-----|-----|-----|---|

| ALU 1 op                                                             | or | 000              | de | ALU op |   |   | dr | dreg |   |      |     |    |     |     |     |   |

| not r                                                                | 0  | 1                | 1  | 0      | 0 | 0 | r  | r    | - | _    | _   | _  | _   | _   | _   | - |

| shr r                                                                | 0  | 1                | 1  | 0      | 0 | 1 | r  | r    | _ | _    | -   | _  | -   | -   | I   | - |

| ···· Only the bits in red are necessary to define the ALU operation! |    |                  |    |        |   |   |    |      |   |      |     |    |     |     |     |   |

17

| A | L | U |

|---|---|---|

|   |   |   |

| entity cpualu is                                 |           |

|--------------------------------------------------|-----------|

| port (                                           |           |

| clk : in STD_LOGIC;                              |           |

| <pre>rst : in STD_LOGIC;</pre>                   |           |

| <pre>op : in STD_LOGIC_VECTOR(4 downto 0);</pre> |           |

| <pre>a : in STD_LOGIC_VECTOR(7 downto 0);</pre>  | Input A,B |

| <pre>b : in STD_LOGIC_VECTOR(7 downto 0);</pre>  |           |

| <pre>q : out STD_LOGIC_VECTOR(7 downto 0);</pre> | Output    |

| <pre>f : out STD_LOGIC_VECTOR(3 downto 0)</pre>  |           |

| );                                               | Flags     |

|                                                  |           |

- end cpualu;

- Flags are always returned, but only used if the instruction is "cmp": control unit stores the flag in a flag register

### ALU

```

r <= a+b when op(4 downto 3)="01" and op(1 downto 0)="00" else

sub(7 downto 0) when op(4 downto 3)="01" and op(1 downto 0)="01" else

a and b when op(4 downto 3)="01" and op(1 downto 0)="10" else

a or b when op(4 downto 3)="01" and op(1 downto 0)="11" else

a xor b when op(4 downto 3)="10" and op(1 downto 0)="00" else

not a when op(4 downto 0)="11000" else

'0'&a(7 downto 1) when op(4 downto 0)="11001" else

a(0)&a(7 downto 1) when op(4 downto 0)="11010" else

a(7)&a(7 downto 1) when op(4 downto 0)="11011" else

a(6 downto 0)&a(7) when op(4 downto 0)="1100" else

"00000000";

```

- Multiplexer

- Can you recognize an instruction?

- Add is 001000rr ----rr

- Oľ 001100rr iiiiiii

- (in red op)

- Therefore we react is op(4..3)=01 and op(1..0)=00

```

sf <= sub(7);

zf <= not(sub(7) or sub(6) or sub(5) or sub(4) or sub(3) or sub(2) or sub(1) or

sub(0));

cf <= sub(8);

ovf <= (not a(7) and b(7) and sub(7)) or (a(7) and not b(7) and not sub(7));</pre>

```

q<=r;

Combine flags in a vector

- Sign flag is bit 7 of the subtraction

- Zero flag obtained by oring

- Carry flag is bit 8 of the subtration (only 8 bits are returned but subtraction done on 9 bits to obtain the carry)

- Overflow flag: triggers when the result flips sign:

- positive minus negative must give positive

- negative minus positive must give negative

- Otherwise it's an overflow

#### Top level CPU entity

| entity cpu is  |                                                           |                    |  |  |  |  |  |  |

|----------------|-----------------------------------------------------------|--------------------|--|--|--|--|--|--|

| generic(N : ir | nteger);                                                  |                    |  |  |  |  |  |  |

| port(          |                                                           |                    |  |  |  |  |  |  |

|                | clk : in STD_LOGIC;                                       | External interface |  |  |  |  |  |  |

|                | rst : in STD_LOGIC;                                       | External interface |  |  |  |  |  |  |

|                | <pre>ext_in : in STD_LOGIC_VECTOR(7 downto</pre>          | 0);                |  |  |  |  |  |  |

|                | <pre>ext_out : out STD_LOGIC_VECTOR(7 downt</pre>         | :o 0);             |  |  |  |  |  |  |

|                | <pre>ram_we : out STD_LOGIC;</pre>                        |                    |  |  |  |  |  |  |

|                | <pre>ram_address : out STD_LOGIC_VECTOR(N-1</pre>         | downto 0);         |  |  |  |  |  |  |

|                | <pre>ram_datawr : out STD_LOGIC_VECTOR(7 downto 0);</pre> |                    |  |  |  |  |  |  |

|                | <pre>ram_datard : in STD_LOGIC_VECTOR(7 dow</pre>         | nto 0);            |  |  |  |  |  |  |

|                | Only for debugging                                        | Memory interface   |  |  |  |  |  |  |

|                | dbg_qa : out STD_LOGIC_VECTOR(7 downto                    | -                  |  |  |  |  |  |  |

|                | dbg_qb : out STD_LOGIC_VECTOR(7 downto                    | 0);                |  |  |  |  |  |  |

|                | dbg_qc : out STD_LOGIC_VECTOR(7 downto                    | 0);                |  |  |  |  |  |  |

|                | dbg_qd : out STD_LOGIC_VECTOR(7 downto                    | 0);                |  |  |  |  |  |  |

|                | dbg_instr : out STD_LOGIC_VECTOR(15 do                    | wnto 0);           |  |  |  |  |  |  |

|                | dbg_seq : out STD_LOGIC_VECTOR(1 downt                    | co 0);             |  |  |  |  |  |  |

|                | dbg_flags : out STD_LOGIC_VECTOR(3 down                   | nto 0)             |  |  |  |  |  |  |

| );             |                                                           |                    |  |  |  |  |  |  |

end cpu;

# CPU: instantiating the register bank

comp\_regs: entity work.cpuregbank port map(

| clk=>clk,rst=>rst,                           | 1st register is "dst"    |  |  |  |  |

|----------------------------------------------|--------------------------|--|--|--|--|

| <pre>rrd1=&gt;instruction(9 downto 8),</pre> | 2nd register is "src"    |  |  |  |  |

| <pre>rrd2=&gt;instruction(1 downto 0),</pre> |                          |  |  |  |  |

| <pre>rwr=&gt;instruction(9 downto 8),</pre>  | write register is "dst " |  |  |  |  |

| rwren=>regwren,                              | Controls the write       |  |  |  |  |

| d=>wrdata,                                   |                          |  |  |  |  |

| <pre>ql=&gt;reglout,q2=&gt;reg2out);</pre>   | 1st and 2nd register     |  |  |  |  |

|                                              | output                   |  |  |  |  |

- The instruction set is designed to help the control unit

- Source and destination always in the same location in the instruction

- reg1out is the value in the "dst" register

- reg2out is the value in the "src" register

- It does not hurt to "wire up" src and dst to the register bank, even if the instruction does not use src/dst (the control unit handles that)

- Write only occurs with a Move or an ALU instruction!

#### CPU: instantiating fetch/execute

comp\_seq: entity work.cpusequencer port

map(clk=>clk,rst=>rst,en=>'1',seq=>seq);

| fetchh <=                                | '1' when seq="00" else                                         |  |  |

|------------------------------------------|----------------------------------------------------------------|--|--|

|                                          | '0' <i>;</i>                                                   |  |  |

| fetchl <=                                | '1' when seq="01" else                                         |  |  |

|                                          | 'O';                                                           |  |  |

| execute <= '1' when seq="10" else        |                                                                |  |  |

| '0';                                     |                                                                |  |  |

| <pre>fetch &lt;= fetchl or fetchh;</pre> |                                                                |  |  |

|                                          | Helper signals - not<br>mandatory but makes<br>reading simpler |  |  |

#### **CPU: fetch instruction**

```

comp_instrh: entity work.dffre generic map(N=>8)

port map(clk=>clk,rst=>rst,en=>fetchh,d=>ram_datard,

q=>instruction(15 downto 8));

```

```

comp_instrl: entity work.dffre generic map(N=>8) port

map(clk=>clk,rst=>rst,en=>fetchl,d=>ram_datard,

q=>instruction(7 downto 0));

```

- instruction is the 16-bit instruction read from memory

- It is 16-bit register realized by two 8-bit D flip-flops

- First flip-flop enabled on "fetch high"

- Second flip-flop enabled on "fetch low"

- ip is the address where the instruction is read from

- N-bit D flip-flop

- In the laboratory N is 5 bits (0...1F). It's a Design choice

- ipnext is the input of the D flip-flop

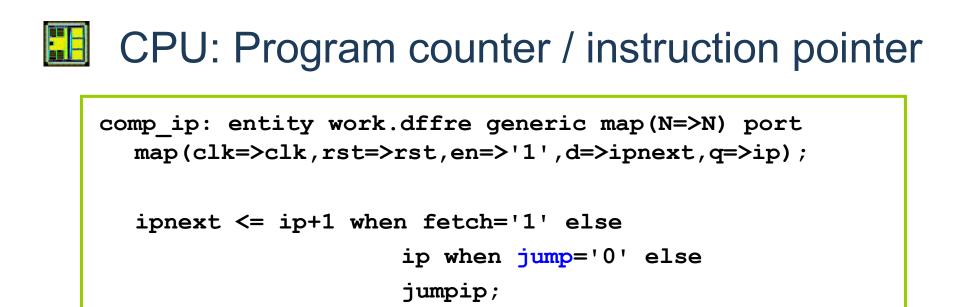

# CPU: Program counter / instruction pointer

```

comp_ip: entity work.dffre generic map(N=>N) port

map(clk=>clk,rst=>rst,en=>'1',d=>ipnext,q=>ip);

```

- When to write: at each clock cycle!

- What to write:

- Fetch (high or low): ipnext = ip+1

- Exec:

- ipnext does not change if the instruction is not a jump

- ipnext changes if it is an absolute jump, or a conditional jump with the condition valid

- (indicated by the signal jump)

#### **CPU:** Jump

| Instructions                          | in     | instruction(158) |   |                    |           |   |   | Instruction(70) |                |   |   |   |   |   |   |   |

|---------------------------------------|--------|------------------|---|--------------------|-----------|---|---|-----------------|----------------|---|---|---|---|---|---|---|

| Jump<br>Unsigned: JA,<br>JAE, JB, JBE | opcode |                  |   | $\overline{R}$ / I | Jump type |   |   |                 | immedite / reg |   |   |   |   |   |   |   |

| jmp r                                 | 1      | 0                | 1 | 0                  | 0         | 0 | 0 | 0               | -              | - | I | - | - | I | r | r |

| jmp i                                 | 1      | 0                | 1 | 1                  | 0         | 0 | 0 | 0               | i              | i | i | i | i | i | i | i |

| je/jz r                               | 1      | 0                | 1 | 0                  | 0         | 0 | 0 | 1               | -              | - | I | I | - | I | r | r |

| je/jz i                               | 1      | 0                | 1 | 1                  | 0         | 0 | 0 | 1               | i              | i | i | i | i | i | i | i |

| jne/jnz r                             | 1      | 0                | 1 | 0                  | 1         | 0 | 0 | 1               | -              | - | - | - | - | I | r | r |

| jne/jnz i                             | 1      | 0                | 1 | 1                  | 1         | 0 | 0 | 1               | i              | i | i | i | i | i | i | i |

| ja r                                  | 1      | 0                | 1 | 0                  | 0         | 0 | 1 | 0               | -              | - | - | - | - | I | r | r |

| ja i                                  | 1      | 0                | 1 | 1                  | 0         | 0 | 1 | 0               | i              | i | i | i | i | i | i | i |

| jb r                                  | 1      | 0                | 1 | 0                  | 1         | 0 | 1 | 1               | -              | - | - | - | - | - | r | r |

| jb i                                  | 1      | 0                | 1 | 1                  | 1         | 0 | 1 | 1               | i              | i | i | i | i | i | i | i |

- Unconditional jumps for 101x000 only

- Address is register or immediate: it is source defined before

### CPU: Jump

| <pre>jumpip &lt;= source(N-1 downto 0);</pre>                                      | Where to jump if we were to do it                                      |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| <pre>jump &lt;= '1' when instruction(15 downto   jumpconditionvalid='1' else</pre> | 13) = "101" and                                                        |

| '0';                                                                               | jump if there is a jump instruction<br>and the jump condition is valid |

| jumpconditionvalid <=                                                              | , , , , , , , , , , , , , , , , , , ,                                  |

| <pre>'1' when instruction(11 downto 8) =</pre>                                     | "0000" else                                                            |

| je/jz                                                                              | always valid (unconditional jump)                                      |

| <pre>'1' when instruction(11 downto 8) =</pre>                                     | "0001" and zf='1' else                                                 |

| jne/jnz<br>'1' when instruction(11 downto 8) =                                     | "1001" and zf='0' else                                                 |

| ja                                                                                 | Conditional jump when not zero: check the zero flag                    |

| <pre>'1' when instruction(11 downto 8) = cf='0' else</pre>                         | "OULU" and zf='U' and                                                  |

| jb                                                                                 |                                                                        |

| <pre>'1' when instruction(11 downto 8) = cf='1'</pre>                              | "1011" and zf='0' and                                                  |

| else '0';                                                                          | 28                                                                     |

# CPU: source (helper signal)

source <= reg2out when instruction(12)='0' else instruction(7 downto 0);

- Many instructions use a "source": Move, ALU, Jump, out

- All these instructions use as source:

- an immediate in the lower 8 bits of the instruction if R#/I=1

- a register (output of the register bank) if R#/I=0

- R#/I is always instruction(12)

- source takes care of providing the right source (immediate or register) using a multiplexer

- Either the immediate

- or the 2nd output of register bank (src)

# CPU: when to write to register

- regwren: helper signal indicating when to write to register (register file)

- Write to register only during execute cycle

- And:

- The instruction is a Move

- Or the instruction is ALU (but not "cmp")

- Or the instruction is In

```

execute=1 and (

(instr(15..13)=000 and instr(11)=0) or

instr(15..13)=001 or

(instr(15..13)=010 and instr(11..10) /= 01)

instr(15..13)=011

```

### CPU: what to write

- wrdata: helper signal containing the data to write:

- Data for memory and register write

- wrdata is connected to the register bank write input!

- What to write:

- Move direct instruction: the data to write is "source" (either immediate or register)

- Move from memory instr.: write what the memory chip provides

- ALU instruction: write the output of the ALU

- In instruction: write what is on the input of the external interface

#### wrdata =

source when instr(15..10)=000X00 ram\_datard when instr(15..10)=000X01 aluqout when instr(15..13)=001 aluqout when instr(15..13)=010 aluqout when instr(15..13)=011 ext\_in when instr(15..10)=110X01

### CPU: memory interface

- What to write (put on the data bus)?

- wrdata always

- What to put on the address bus?

• When to write?

### **CPU: memory interface**

```

ram_address <=

ip when fetch='1' else

reg2out(N-1 downto 0) when instruction(15 downto 10)="000001" else

instruction(N-1 downto 0) when instruction(15 downto 10)="000101" else

reglout(N-1 downto 0) when instruction(15 downto 10)="000110" else

reglout(N-1 downto 0) when instruction(15 downto 10)="000110" else

(others=>'0');

```

- Address:

- IP during the fetch cycles

- The content of the src register or of the immediate for a move from memory

- the content of the dst register for a move to memory

- Otherwise zero

- Explains why the first CPU lab showed always a zero on the address!

### CPU: when to write to memory?

- Move to memory during the exec cycle:

- mov [b],23h

```

ram_we <=

'1' when execute='1' and instruction(15 downto 13)="000"

and instruction(11 downto 10)="10"

else '0';</pre>

```

### **CPU: External interface**

- External interface output is an 8-bit D flip-flop

- When to write: during exec when instruction is "out"

- What to write: source (i.e. register or immediate)

```

comp_regextout :

entity work.dffre generic map (N=>8)

port map(clk=>clk,rst=>rst,en=>ext_wren,

d=>source,q=>ext_out);

ext_wren <=

'1' when execute='1' and instruction(15 downto 13) =

"110" and instruction(11 downto 10)="00"

else '0';</pre>

```

#### **CPU: flags**

- SF, CF, OF, ZF are stored in a 4-bit D flip-flop

- When to write: during exec and "cmp" instruction

- What to write: the flag output of the ALU

```

comp_flags: entity work.dffre

generic map(N=>4)

port map(clk=>clk,rst=>rst,en=>flagwren,d=>alufout,q=>flags);

flagwren <= '1' when execute='1' and instruction(15 downto</pre>

```

```

13)="010" and instruction(11 downto 10)="01"

else '0';

```

37

CPU

#### Jump decode logic

instr(15..13)=101 an(d instr(11..8)=0000 or (instr(11..8)=0001 and zf=1) or (instr(11..8)=1001 and zf=0)

#### Register write decode logic

| e | kecute=1 and (                        |

|---|---------------------------------------|

|   | (instr(1513)=000 and instr(11)=0) or  |

|   |                                       |

|   | instr(1513)=001 or                    |

|   | (instr(1513)=010 and instr(1110) /= 0 |

|   | instr(1513)=011                       |

| 1 |                                       |

Memory write decode logic

execute=1 and instr(15..10)=000X10

External write decode logic

execute=1 and instr(15..13)=110

#### Flag write decode logic

execute=1 and instr(15..10)=010X01

#### Write data select

#### wrdata =

source when instr(15..10)=000X00 ram\_datard when instr(15..10)=000X01 aluqout when instr(15..13)=001 aluqout when instr(15..13)=010 aluqout when instr(15..13)=011 ext\_in when instr(15..10)=110X01

#### Data address generation

#### address =

reg1out when instr(15..10)=000001 instr(7..0) when instr(15..10)=000101 reg1out when instr(15..10)=000010 reg1out when instr(15..10)=000110

### Summary

- Brief insight into the processor architecture

- Basic understanding of the control unit function:

- deciding what and when to "store" data in register

- Sufficient knowledge to perform the coursework assignment on:

- Modifying the instruction set (adding instruction)

- Tracing the state of key signals for a given instruction