## ZIP CPU SPECIFICATION

Dan Gisselquist, Ph.D. dgisselq (at) opencores.org

$\mathrm{May}\ 6,\ 2016$

Copyright (C) 2016, Gisselquist Technology, LLC

This project is free software (firmware): you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free Software Foundation, either version 3 of the License, or (at your option) any later version.

This program is distributed in the hope that it will be useful, but WITHOUT ANY WAR-RANTY; without even the implied warranty of MERCHANTIBILITY or FITNESS FOR A PAR-TICULAR PURPOSE. See the GNU General Public License for more details.

You should have received a copy of the GNU General Public License along with this program. If not, see <code>ihttp://www.gnu.org/licenses/</code>¿ for a copy.

## **Revision History**

| Rev. | Date       | Author                                            | Description                                       |  |  |  |  |

|------|------------|---------------------------------------------------|---------------------------------------------------|--|--|--|--|

| 0.9  | 4/20/2016  | Gisselquist                                       | Modified ISA: LDIHI replaced with MPY,            |  |  |  |  |

|      |            |                                                   | MPYU and MPYS replaced with MPYUHI, and           |  |  |  |  |

|      |            |                                                   | MPYSHI respectively. LOCK instruction now         |  |  |  |  |

|      |            |                                                   | permits an intermediate ALU operation.            |  |  |  |  |

| 0.8  | 1/28/2016  | Gisselquist                                       | Reduced complexity early branching                |  |  |  |  |

| 0.7  | 12/22/2015 | Gisselquist                                       | New Instruction Set Architecture                  |  |  |  |  |

| 0.6  | 11/17/2015 | Gisselquist                                       | Added graphics to illustrate pipeline discussion. |  |  |  |  |

| 0.5  | 9/29/2015  | Gisselquist Added pipelined memory access discuss |                                                   |  |  |  |  |

| 0.4  | 9/19/2015  | Gisselquist                                       | Added DMA controller, improved stall informa-     |  |  |  |  |

|      |            |                                                   | tion, and self–assessment info.                   |  |  |  |  |

| 0.3  | 8/22/2015  | Gisselquist                                       | First completed draft                             |  |  |  |  |

| 0.2  | 8/19/2015  | Gisselquist                                       | Still Draft, more complete                        |  |  |  |  |

| 0.1  | 8/17/2015  | Gisselquist                                       | Incomplete First Draft                            |  |  |  |  |

### Contents

|   |                                               | I                                                                                                                                                                                                                                                                                                                                    | Page                                                                                            |

|---|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 1 | 1.1<br>1.2                                    | Introduction                                                                                                                                                                                                                                                                                                                         | $\begin{array}{c} 1 \\ 1 \\ 3 \end{array}$                                                      |

| 2 | 2.11<br>2.12<br>2.13<br>2.14<br>2.15          | CPU Architecture Simplified Bus Register Set Instruction Format Instruction OpCodes Conditional Instructions Operand B Address Modes Modifying Conditions Move Operands Multiply Operations Divide Unit NOOP, BREAK, and Bus Lock Instruction Floating Point Derived Instructions Interrupt Handling Pipeline Stages Pipeline Stalls | 8<br>8<br>8<br>10<br>12<br>12<br>15<br>15<br>16<br>16<br>16<br>17<br>18<br>18<br>18<br>18<br>23 |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | Peripherals Interrupt Controller Counter Timer Watchdog Timer Bus Watchdog Jiffies Direct Memory Access Controller                                                                                                                                                                                                                   | 29<br>30<br>30<br>30<br>31<br>31                                                                |

| 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5               | Operation . System High . Traditional Interrupt Handling . Example: Idle Task . Example: Memory Copy . Example: Context Switch                                                                                                                                                                                                       | 33<br>34<br>34<br>35<br>38<br>38                                                                |

| 5 | 5.1<br>5.2                                    | Registers Peripheral Registers 5.1.1 Interrupt Controller(s) 5.1.2 Timer Register 5.1.3 Jiffies 5.1.4 Performance Counters 5.1.5 DMA Controller Debug Port Registers                                                                                                                                                                 | 44<br>45<br>45<br>46<br>46<br>46<br>47<br>47                                                    |

| <u>G1</u> | Gisselquist Technology, LLC | Specification | 2016/05/06 |

|-----------|-----------------------------|---------------|------------|

|           |                             |               |            |

| 6         | Wishbone Datasheets         |               | 51         |

| 7         | Clocks                      |               | 53         |

| 8         | I/O Ports                   |               | 54         |

| 9         | 9.1 The Good                |               | 56         |

|           | 9.3 The Next Generation     |               | 58         |

www.opencores.com Rev. 0.9

# **Figures**

| Figure               |                                                             | Page              |

|----------------------|-------------------------------------------------------------|-------------------|

|                      |                                                             |                   |

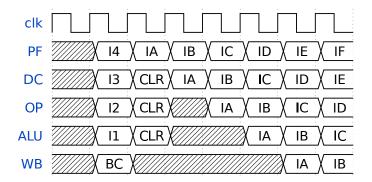

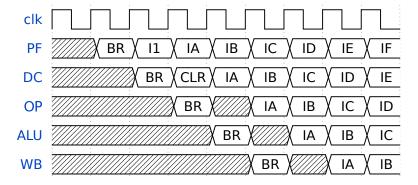

| 1.1                  | Zip CPU internal pipeline architecture                      |                   |

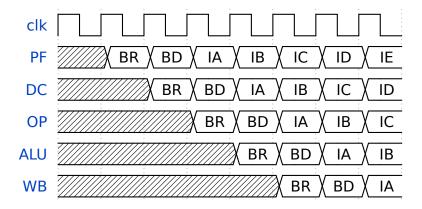

| 1.2                  | An Ideal Pipeline: One instruction per clock cycle          | . 5               |

| 1.3                  | Instructions wait for each other                            | . 5               |

| 1.4                  | Instructions proceed independently                          | . 5<br>. 5<br>. 5 |

| 1.5                  | A typical branch delay slot approach                        |                   |

| 1.6                  | The branch delay slot breaks with a slow memory             | . 6               |

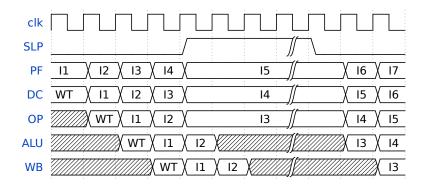

| 1.7                  | How the CPU halts when sleeping                             | . 7               |

| 1.8                  | Instructions can stack up behind a stalled instruction      |                   |

| 1.0                  | instructions can stack up beaming a standard instruction    | • •               |

| 2.1                  | Zip CPU Register File                                       | . 9               |

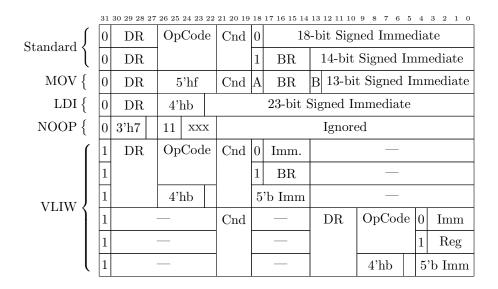

| $\frac{2.1}{2.2}$    | Zip Instruction Set Format                                  | . 11              |

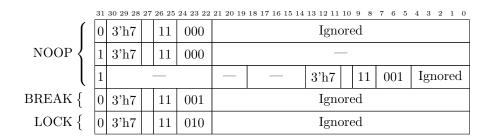

| $\overset{2.2}{2.3}$ | NOOD / Prook / LOCK Instruction Format                      | . 17              |

|                      | NOOP/Break/LOCK Instruction Format                          | . 11              |

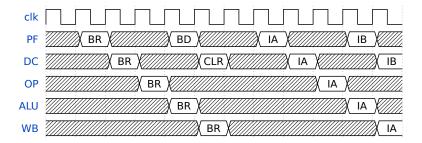

| 2.4                  | A conditional branch generates 4 stall cycles               | . 24              |

| 2.5                  | An expedited branch costs a single stall cycle              | . 24              |

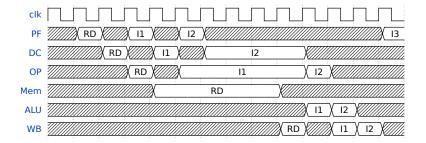

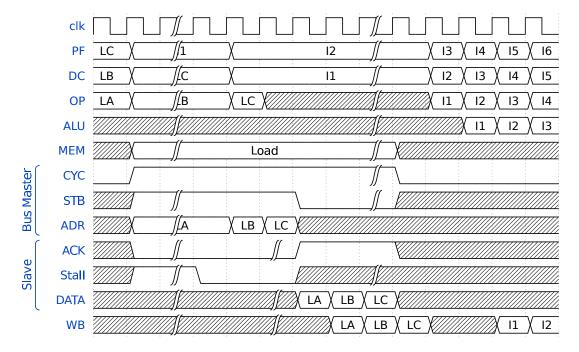

| 2.6                  | Pipeline handling of a load instruction                     | . 26              |

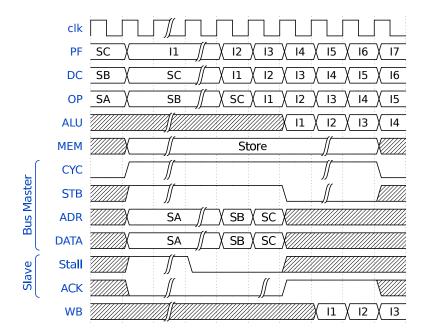

| 2.7                  | Pipeline handling of a store instruction                    | . 27              |

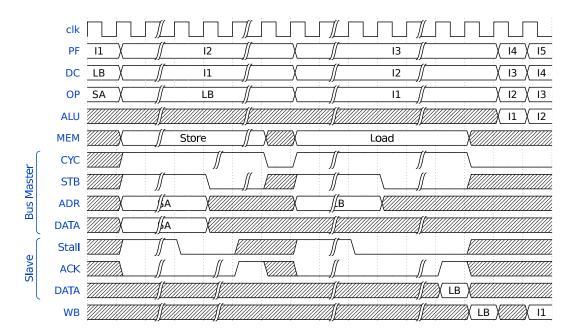

| 2.8                  | Pipeline handling of a store followed by a load instruction | . 28              |

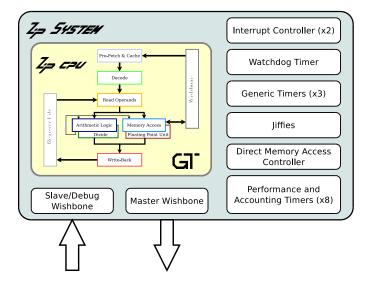

| 3.1                  | Zip System Peripherals                                      | . 30              |

## **Tables**

| Tab <u>le</u>                                                                       |                                                                                                                                                                                                                                                                                                                                                               | Page                                                                 |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11         | Condition Code Register Bit Assignment Zip CPU OpCodes Conditions for conditional operand execution An example of a double conditional VLIW Conditions Bit allocation for Operand B Modifying conditions Derived Instructions Derived Instructions, continued Derived Instructions, continued Derived Instructions, continued Derived Instructions, continued | . 13<br>. 14<br>. 14<br>. 14<br>. 15<br>. 19<br>. 20<br>. 21         |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12 | Executing an idle from supervisor mode                                                                                                                                                                                                                                                                                                                        | . 36<br>. 37<br>. 37<br>. 37<br>. 38<br>. 39<br>. 39<br>. 40<br>. 41 |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                         | Zip System Internal/Peripheral Registers Zip System Debug Registers Interrupt Controller Register Bits Timer Register Bits Jiffies Register Bits Counter Register Bits DMA Control Register Bits Debug Control Register Bits Debug Register Addresses                                                                                                         | . 44<br>. 45<br>. 46<br>. 46<br>. 47<br>. 48                         |

| $6.1 \\ 6.2$                                                                        | Wishbone Datasheet for the Debug Interface                                                                                                                                                                                                                                                                                                                    |                                                                      |

| 7.1                                                                                 | List of Clocks                                                                                                                                                                                                                                                                                                                                                | . 53                                                                 |

| 8.1<br>8.2<br>8.3                                                                   | CPU Master Wishbone I/O Ports                                                                                                                                                                                                                                                                                                                                 | . 55                                                                 |

### **Preface**

Many people have asked me why I am building the Zip CPU. ARM processors are good and effective. Xilinx makes and markets Microblaze, Altera Nios, and both have better toolsets than the Zip CPU will ever have. OpenRISC is also available, RISC–V may be replacing it. Why build a new processor?

The easiest, most obvious answer is the simple one: Because I can.

There's more to it, though. There's a lot that I would like to do with a processor, and I want to be able to do it in a vendor independent fashion. First, I would like to be able to place this processor inside an FPGA. Without paying royalties, ARM is out of the question. I would then like to be able to generate Verilog code, both for the processor and the system it sits within, that can run equivalently on both Xilinx and Altera chips, and that can be easily ported from one manufacturer's chipsets to another. Even more, before purchasing a chip or a board, I would like to know that my soft core works. I would like to build a test bench to test components with, and Verilator is my chosen test bench. This forces me to use all Verilog, and it prevents me from using any proprietary cores. For this reason, Microblaze and Nios are out of the question.

Why not OpenRISC? That's a hard question. The OpenRISC team has done some wonderful work on an amazing processor, and I'll have to admit that I am envious of what they've accomplished. I would like to port binutils to the Zip CPU, as I would like to port GCC and GDB. They are way ahead of me. The OpenRISC processor, however, is complex and hefty at about 4,500 LUTs. It has a lot of features of modern CPUs within it that ... well, let's just say it's not the little guy on the block. The Zip CPU is lighter weight, costing only about 2,300 LUTs with no peripherals, and 3,200 LUTs with some very basic peripherals.

My final reason is that I'm building the Zip CPU as a learning experience. The Zip CPU has allowed me to learn a lot about how CPUs work on a very micro level. For the first time, I am beginning to understand many of the Computer Architecture lessons from years ago.

To summarize: Because I can, because it is open source, because it is light weight, and as an exercise in learning.

Dan Gisselquist, Ph.D.

1.

### Introduction

The original goal of the Zip CPU was to be a very simple CPU. You might think of it as a poor man's alternative to the OpenRISC architecture. For this reason, all instructions have been designed to be as simple as possible, and the base instructions are all designed to be executed in one instruction cycle per instruction, barring pipeline stalls. Indeed, even the bus has been simplified to a constant 32-bit width, with no option for more or less. This has resulted in the choice to drop push and pop instructions, pre-increment and post-decrement addressing modes, and more.

For those who like buzz words, the Zip CPU is:

- A 32-bit CPU: All registers are 32-bits, addresses are 32-bits, instructions are 32-bits wide, etc.

- A RISC CPU. There is no microcode for executing instructions. All instructions are designed to be completed in one clock cycle.

- A Load/Store architecture. (Only load and store instructions can access memory.)

- Wishbone compliant. All peripherals are accessed just like memory across this bus.

- A Von-Neumann architecture. (The instructions and data share a common bus.)

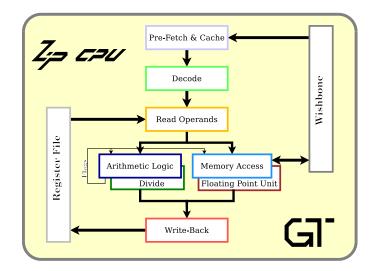

- A pipelined architecture, having stages for **Prefetch**, **Decode**, **Read-Operand**, a combined stage containing the **ALU**, **Memory**, **Divide**, and **Floating Point** units, and then the final **Write-back** stage. See Fig. 1.1 for a diagram of this structure.

- Completely open source, licensed under the GPL.<sup>1</sup>

The Zip CPU also has one very unique feature: the ability to do pipelined loads and stores. This allows the CPU to access on-chip memory at one access per clock, minus a stall for the initial access.

#### 1.1 Characteristics of a SwiC

Here, we shall define a soft core internal to an FPGA as a "System within a Chip," or a SwiC. SwiCs have some very unique properties internal to them that have influenced the design of the Zip CPU. Among these are the bus, memory, and available peripherals.

Most other approaches to soft core CPU's employ a Harvard architecture. This allows these other CPU's to have two separate bus structures: one for the program fetch, and the other for the memory.

<sup>&</sup>lt;sup>1</sup>Should you need a copy of the Zip CPU licensed under other terms, please contact me.

Figure 1.1: Zip CPU internal pipeline architecture

The Zip CPU is fairly unique in its approach because it uses a von Neumann architecture. This was done for simplicity. By using a von Neumann architecture, only one bus needs to be implemented within any FPGA. This helps to minimize real-estate, while maintaining a high clock speed. The disadvantage is that it can severely degrade the overall instructions per clock count.

Soft core's within an FPGA have an additional characteristic regarding memory access: it is slow. While memory on chip may be accessed at a single cycle per access, small FPGA's often have only a limited amount of memory on chip. Going off chip, however, is expensive. Two examples will prove this point. On the XuLA2 board, Flash can be accessed at 128 cycles per 32-bit word, or 64 cycles per subsequent word in a pipelined architecture. Likewise, the SDRAM chip on the XuLA2 board allows a 6 cycle access for a write, 10 cycles per read, and 2 cycles for any subsequent pipelined access read or write. Either way you look at it, this memory access will be slow and this doesn't account for any logic delays should the bus implementation logic get complicated.

As may be noticed from the above discussion about memory speed, a second characteristic of memory is that all memory accesses may be pipelined, and that pipelined memory access is faster than non–pipelined access. Therefore, a SwiC soft core should support pipelined operations, but it should also allow a higher priority subsystem to get access to the bus (no starvation).

As a further characteristic of SwiC memory options, on-chip cache's are expensive. If you want to have a minimum of logic, cache logic may not be the highest on the priority list.

In sum, memory is slow. While one processor on one FPGA may be able to fill its pipeline, the same processor on another FPGA may struggle to get more than one instruction at a time into the pipeline. Any SwiC must be able to deal with both cases: fast and slow memories.

A final characteristic of SwiC's within FPGA's is the peripherals. Specifically, FPGA's are highly reconfigurable. Soft peripherals can easily be created on chip to support the SwiC if necessary. As an example, a simple 30-bit peripheral could easily support reversing 30-bit numbers: a read from the peripheral returns it's bit—reversed address. This is cheap within an FPGA, but expensive in

instructions. Reading from another 16-bit peripheral might calculate a sine function, where the 16-bit address internal to the peripheral was the angle of the sine wave.

Indeed, anything that must be done fast within an FPGA is likely to already be done–elsewhere in the fabric. This leaves the CPU with the simple role of solely handling sequential tasks that need a lot of state.

This means that the SwiC needs to live within a very unique environment, separate and different from the traditional SoC. That isn't to say that a SwiC cannot be turned into a SoC, just that this SwiC has not been designed for that purpose.

#### 1.2 Lessons Learned

Now, however, that I've worked on the Zip CPU for a while, it is not nearly as simple as I originally hoped. Worse, I've had to adjust to create capabilities that I was never expecting to need. These include:

- External Debug: Once placed upon an FPGA, some external means is still necessary to debug this CPU. That means that there needs to be an external register that can control the CPU: reset it, halt it, step it, and tell whether it is running or not. My chosen interface includes a second register similar to this control register. This second register allows the external controller or debugger to examine registers internal to the CPU.

- Internal Debug: Being able to run a debugger from within a user process requires an ability to step a user process from within a debugger. It also requires a break instruction that can be substituted for any other instruction, and substituted back. The break is actually difficult: the break instruction cannot be allowed to execute. That way, upon a break, the debugger should be able to jump back into the user process to step the instruction that would've been at the break point initially, and then to replace the break after passing it.

- Incidentally, this break messes with the prefetch cache and the pipeline: if you change an instruction partially through the pipeline, the whole pipeline needs to be cleansed. Likewise if you change an instruction in memory, you need to make sure the cache is reloaded with the new instruction.

- Prefetch Cache: My original implementation, prefetch, had a very simple prefetch stage. Any time the PC changed the prefetch would go and fetch the new instruction. While this was perhaps this simplest approach, it cost roughly five clocks for every instruction. This was deemed unacceptable, as I wanted a CPU that could execute instructions in one cycle.

- My second implementation, pipefetch, attempted to make the most use of pipelined memory. When a new CPU address was issued, it would start reading memory in a pipelined fashion, and issuing instructions as soon as they were ready. This cache was a sliding window in memory. This suffered from some difficult performance problems, though. If the CPU was alternating between two diverse sections of code, both could never be in the cache at the same time–causing lots of cache misses. Further, the extra logic to implement this window cost an extra clock cycle in the cache implementation, slowing down branches.

The Zip CPU now has a third cache implementation, pfcache. This new implementation takes only a single cycle per access, but costs a full cache line miss on any miss. While configurable,

a full cache line miss might mean that the CPU needs to read 256 instructions from memory before it can execute the first one of them.

• Operating System: In order to support an operating system, interrupts and so forth, the CPU needs to support supervisor and user modes, as well as a means of switching between them. For example, the user needs a means of executing a system call. This is the purpose of the 'trap' instruction. This instruction needs to place the CPU into supervisor mode (here equivalent to disabling interrupts), as well as handing it a parameter such as identifying which O/S function was called.

My initial approach to building a trap instruction was to create an external peripheral which, when written to, would generate an interrupt and could return the last value written to it. In practice, this approach didn't work at all: the CPU executed two instructions while waiting for the trap interrupt to take place. Since then, I've decided to keep the rest of the CC register for that purpose so that a write to the CC register, with the GIE bit cleared, could be used to execute a trap. This has other problems, though, primarily in the limitation of the uses of the CC register. In particular, the CC register is the best place to put CPU state information and to "announce" special CPU features (floating point, etc). So the trap instruction still switches to interrupt mode, but the CC register is not nearly as useful for telling the supervisor mode processor what trap is being executed.

Modern timesharing systems also depend upon a **Timer** interrupt to handle task swapping. For the Zip CPU, this interrupt is handled external to the CPU as part of the CPU System, found in zipsystem.v. The timer module itself is found in ziptimer.v.

- Bus Errors: My original implementation had no logic to handle what would happen if the CPU attempted to read or write a non-existent memory address. This changed after I needed to troubleshoot a failure caused by a subroutine return to a non-existent address.

- My next problem bus problem was caused by a misbehaving peripheral. Whenever the CPU attempted to read from or write to this peripheral, the peripheral would take control of the wishbone bus and not return it. For example, it might never return an ACK to signal the end of the bus transaction. This led to the implementation of a wishbone bus watchdog that would create a bus error if any particular bus action didn't complete in a timely fashion.

- **Pipeline Stalls:** My original plan was to not support pipeline stalls at all, but rather to require the compiler to properly schedule all instructions so that stalls would never be necessary. After trying to build such an architecture, I gave up, having learned some things:

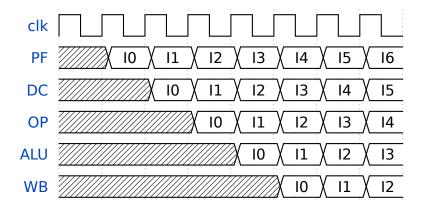

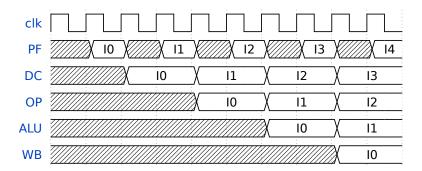

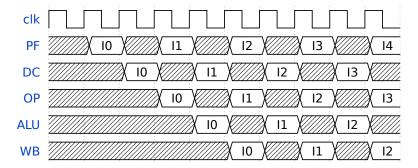

- First, and ideal pipeline might look something like Fig. 1.2. Notice that, in this figure, all the pipeline stages are complete and full. Every instruction takes one clock and there are no delays. However, as the discussion above pointed out, the memory associated with a SwiC may not allow single clock access. It may be instead that you can only read every two clocks. In that case, what shall the pipeline look like? Should it look like Fig. 1.3, where instructions are held back until the pipeline is full, or should it look like Fig. 1.4, where each instruction is allowed to move through the pipeline independently? For better or worse, the Zip CPU allows instructions to move through the pipeline independently.

One approach to avoiding stalls is to use a branch delay slot, such as is shown in Fig. 1.5. In this figure, instructions BR (a branch), BD (a branch delay instruction), are followed by

Figure 1.2: An Ideal Pipeline: One instruction per clock cycle

Figure 1.3: Instructions wait for each other

Figure 1.4: Instructions proceed independently

Figure 1.5: A typical branch delay slot approach

Figure 1.6: The branch delay slot breaks with a slow memory

instructions after the branch: IA, IB, etc. Since it takes a processor a clock cycle to execute a branch, the delay slot allows the processor to do something useful in that branch. The problem the Zip CPU has with this approach is, what happens when the pipeline looks like Fig. 1.6? In this case, the branch delay slot never gets filled in the first place, and so the pipeline squashes it before it gets executed. If not that, then what happens when handling interrupts or debug stepping: when has the CPU finished an instruction? When the BR instruction has finished, or must BD follow every BR? and, again, what if the pipeline isn't full? These thoughts killed any hopes of doing delayed branching.

So I switched to a model of discrete execution: Once an instruction enters into either the ALU or memory unit, the instruction is guaranteed to complete. If the logic recognizes a branch or a condition that would render the instruction entering into this stage possibly inappropriate (i.e. a conditional branch preceding a store instruction for example), then the pipeline stalls for one cycle until the conditional branch completes. Then, if it generates a new PC address, the stages preceding are all wiped clean.

Figure 1.7: How the CPU halts when sleeping

Figure 1.8: Instructions can stack up behind a stalled instruction

This model, however, generated too many pipeline stalls, so the discrete execution model was modified to allow instructions to go through the ALU unit and be canceled before writeback. This removed the stall associated with ALU instructions before untaken branches.

The discrete execution model allows such things as sleeping, as outlined in Fig. 1.7. If the CPU is put to "sleep," the ALU and memory stages stall and back up everything before them. Likewise, anything that has entered the ALU or memory stage when the CPU is placed to sleep continues to completion. To handle this logic, each pipeline stage has three control signals: a valid signal, a stall signal, and a clock enable signal. In general, a stage stalls if it's contents are valid and the next step is stalled. This allows the pipeline to fill any time a later stage stalls, as illustrated in Fig. 1.8. However, if a pipeline hazard is detected, a stage can stall in order to prevent the previous from moving forward.

This approach is also different from other pipeline approaches. Instead of keeping the entire pipeline filled, each stage is treated independently. Therefore, individual stages may move forward as long as the subsequent stage is available, regardless of whether the stage behind it is filled.

With that introduction out of the way, let's move on to the instruction set.

2.

### CPU Architecture

The Zip CPU supports a set of two operand instructions, where the second operand (always a register) is the result. The only exception is the store instruction, where the first operand (always a register) is the source of the data to be stored.

#### 2.1 Simplified Bus

The bus architecture of the Zip CPU is that of a simplified WISHBONE bus. It has been simplified in this fashion: all operations are 32-bit operations. The bus is neither little endian nor big endian. For this reason, all words are 32-bits. All instructions are also 32-bits wide. Everything has been built around the 32-bit word.

#### 2.2 Register Set

The Zip CPU supports two sets of sixteen 32-bit registers, a supervisor and a user set as shown in Fig. 2.1. The supervisor set is used in interrupt mode when interrupts are disabled, whereas the user set is used otherwise. Of this register set, the Program Counter (PC) is register 15, whereas the status register (SR) or condition code register (CC) is register 14. By convention, the stack pointer will be register 13 and noted as (SP)-although there is nothing special about this register other than this convention. Also by convention register 12 will point to a global offset table, and may be abbreviated as the (GBL) register. The CPU can access both register sets via move instructions from the supervisor state, whereas the user state can only access the user registers.

The status register is special, and bears further mention. As shown in Fig. 2.1, the lower 11 bits of the status register form a set of CPU state and condition codes. Writes to other bits of this register are preserved.

Of the condition codes, the bottom four bits are the current flags: Zero (Z), Carry (C), Negative (N), and Overflow (V). On those instructions that set the flags, these flags will be set based upon the output of the instruction. If the result is zero, the Z flag will be set. If the high order bit is set, the N flag will be set. If the instruction caused a bit to fall off the end, the carry bit will be set. Finally, if the instruction causes a signed integer overflow, the V flag will be set afterwards.

The next bit is a sleep bit. Set this bit to one to disable instruction execution and place the CPU to sleep, or to zero to keep the pipeline running. Setting this bit will cause the CPU to wait for an interrupt (if interrupts are enabled), or to completely halt (if interrupts are disabled). In order to prevent users from halting the CPU, only the supervisor is allowed to both put the CPU to sleep and disable interrupts. Any user attempt to do so will simply result in a switch to supervisor mode.

#### Zip CPU Register Set Supervisor Register Set User Register Set sR0 sR8 uR0 uR8 sR9 uR9 sR1 uR1 sR10 uR10 sR2 uR2 sR3 sR11 uR3 uR11 sR4 sR12 uR4 uR12 sR5 sSPuR5 uSP sR6 sCC uR6 uCC sR7 sPC uR7 uPC

Figure 2.1: Zip CPU Register File

| Bit # | Access | Description                                                    |  |

|-------|--------|----------------------------------------------------------------|--|

| 3113  | R/W    | Reserved for future uses                                       |  |

| 12    | R      | (Reserved for) Floating Point Exception                        |  |

| 11    | R      | Division by Zero Exception                                     |  |

| 10    | R      | Bus-Error Flag                                                 |  |

| 9     | R      | Trap, or user interrupt, Flag. Cleared on return to userspace. |  |

| 8     | R      | Illegal Instruction Flag                                       |  |

| 7     | R/W    | Break–Enable                                                   |  |

| 6     | R/W    | Step                                                           |  |

| 5     | R/W    | Global Interrupt Enable (GIE)                                  |  |

| 4     | R/W    | Sleep. When GIE is also set, the CPU waits for an interrupt.   |  |

| 3     | R/W    | Overflow                                                       |  |

| 2     | R/W    | Negative. The sign bit was set as a result of the last ALU in- |  |

|       |        | struction.                                                     |  |

| 1     | R/W    | Carry                                                          |  |

| 0     | R/W    | Zero. The last ALU operation produced a zero.                  |  |

Table 2.1: Condition Code Register Bit Assignment

The sixth bit is a global interrupt enable bit (GIE). When this sixth bit is a '1' interrupts will be enabled, else disabled. When interrupts are disabled, the CPU will be in supervisor mode, otherwise it is in user mode. Thus, to execute a context switch, one only need enable or disable interrupts. (When an interrupt line goes high, interrupts will automatically be disabled, as the CPU goes and deals with its context switch.) Special logic has been added to keep the user mode from setting the sleep register and clearing the GIE register at the same time, with clearing the GIE register taking precedence.

The seventh bit is a step bit. This bit can be set from supervisor mode only. After setting this bit, should the supervisor mode process switch to user mode, it would then accomplish one instruction in user mode before returning to supervisor mode. Then, upon return to supervisor mode, this bit will be automatically cleared. This bit has no effect on the CPU while in supervisor mode.

This functionality was added to enable a userspace debugger functionality on a user process, working through supervisor mode of course.

The eighth bit is a break enable bit. This controls whether a break instruction in user mode will halt the processor for an external debugger (break enabled), or whether the break instruction will simply send send the CPU into interrupt mode. Encountering a break in supervisor mode will halt the CPU independent of the break enable bit. This bit can only be set within supervisor mode.

This functionality was added to enable an external debugger to set and manage breakpoints.

The ninth bit is an illegal instruction bit. When the CPU tries to execute either a non-existant instruction, or an instruction from an address that produces a bus error, the CPU will (if implemented) switch to supervisor mode while setting this bit. The bit will automatically be cleared upon any return to user mode.

The tenth bit is a trap bit. It is set whenever the user requests a soft interrupt, and cleared on any return to userspace command. This allows the supervisor, in supervisor mode, to determine whether it got to supervisor mode from a trap or from an external interrupt or both.

#### 2.3 Instruction Format

All Zip CPU instructions fit in one of the formats shown in Fig. 2.2. The basic format is that some operation, defined by the OpCode, is applied if a condition, Cnd, is true in order to produce a result which is placed in the destination register, or DR. The load 23-bit signed immediate instruction (LDI) is different in that it accepts no conditions, and uses only a 4-bit opcode.

This is actually a second version of instruction set definition, given certain lessons learned. For example, the original instruction set had the following problems:

- 1. No opcodes were available for divide or floating point extensions to be made available. Although there was space in the instruction set to add these types of instructions, this instruction space was going to require extra logic to use.

- The carveouts for instructions such as NOOP and LDIHI/LDILO required extra logic to process.

- 3. The instruction set wasn't very compact. One bus operation was required for every instruction.

- 4. While the CPU supported multiplies, they were only 16x16 bit multiplies.

Figure 2.2: Zip Instruction Set Format

This second version was designed with two criteria. The first was that the new instruction set needed to be compatible, at the assembly language level, with the previous instruction set. Thus, it must be able to support all of the previous menumonics and more. This was achieved with the sole exception that instruction immediates are generally two bits shorter than before. (One bit was lost to the VLIW bit in front, another from changing from 4-bit to 5-bit opcodes.) Second, the new instruction set needed to be a drop-in replacement for the decoder, modifying nothing else. This was almost achieved, save for two issues: the ALU unit needed to be replaced since the OpCodes were reordered, and some condition code logic needed to be adjusted since the condition codes were renumbered as well. In the end, maximum reuse of the existing RTL (Verilog) code was achieved in this upgrade.

As of this second version of the Zip CPU instruction set, the Zip CPU also supports a very long instruction word (VLIW) set of instructions. These instruction formats pack two instructions into a single instruction word, trading immediate instruction space to do this, but in just about all other respects these are identical to two standard instructions. Other than instruction format, the only basic difference is that the CPU will not switch to interrupt mode in between the two instructions. Likewise a new job given to the assembler is that of automatically packing as many instructions as possible into the VLIW format. Where necessary to place both VLIW instructions on the same line, they will be separated by a vertical bar.

One belated change to the instruction set violates some of the above principles. This latter instruction set change replaced the LDIHI instruction with a 32-bit multiply instruction MPY, and then changed the two 16-bit multiply instructions MPYU and MPYS for MPYUHI and MPYSHI respectively. This creates a 32-bit multiply capability, while removing the 16-bit multiply that wasn't very useful. Further, the LDIHI instruction was being used primarily by the assembler and linker to create a 32-bit load immediate pair of instructions. This instruction set combination, LDIHI followed by LDILO

was replaced with an equivalent instruction set, BREV followed by LDILO, save that linking has been made more complicated in the process.

#### 2.4 Instruction OpCodes

With a 5-bit opcode field, there are 32-possible instructions as shown in Tbl. 2.2. Of these opcodes, the BREV and POPC are experimental, and may be replaced later, and two floating point instruction opcodes are reserved for future use.

#### 2.5 Conditional Instructions

Most, although not quite all, instructions may be conditionally executed. The 23-bit load immediate instruction, together with the NOOP, BREAK, and LOCK instructions are the only exception to this rule.

From the four condition code flags, eight conditions are defined for standard instructions. These are shown in Tbl. 2.3. There is no condition code for less than or equal, not C or not V—there just wasn't enough space in 3-bits. Conditioning on a non-supported condition is still possible, but it will take an extra instruction and a pipeline stall. (Ex: (Stall); TST \$4,CC; STO.NZ RO,(R1)) As an alternative, it is often possible to reverse the condition, and thus recovering those extra two clocks. Thus instead of CMP Rx,Ry; BNC label you can issue a CMP 1+Ry,Rx; BC label.

Conditionally executed instructions will not further adjust the condition codes, with the exception of CMP and TST instructions. Conditional CMP or TST instructions will adjust conditions whenever they are executed. In this way, multiple conditions may be evaluated without branches. For example, to do something if RO is one and R1 is two, one might try code such as Tbl. 2.4.

In the case of VLIW instructions, only four conditions are defined as shown in Tbl. 2.5. Further, the first bit is given a special meaning. If the first bit is set, the conditions apply to the second half of the instruction, otherwise the conditions will only apply to the first half of a conditional instruction. Of course, the other conditions are still available by mingling the non-VLIW instructions with VLIW instructions.

### 2.6 Operand B

Many instruction forms have a 19-bit source "Operand B" associated with them. This "Operand B" is shown in Fig. 2.2 as part of the standard instructions. This Operand B is either equal to a register plus a 14-bit signed immediate offset, or an 18-bit signed immediate offset by itself. This value is encoded as shown in Tbl. 2.6.

Fourteen and eighteen bit immediate values don't make sense for all instructions. For example, what is the point of an 18-bit immediate when executing a 16-bit multiply? Or a 16-bit load-immediate? In these cases, the extra bits are simply ignored.

VLIW instructions still use the same operand B, only there was no room for any instruction plus immediate addressing. Therefore, VLIW instructions have either a register or a 4-bit signed immediate as their operand B. The only exception is the load immediate instruction, which permits a 5-bit signed operand B.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>Although the space exists to extend this VLIW load immediate instruction to six bits, the 5-bit limit was chosen to simplify the disassembler. This may change in the future.

| OpCode  |        | Instruction                                         | Sets CC |

|---------|--------|-----------------------------------------------------|---------|

| 5'h00   | SUB    | Subtract                                            |         |

| 5'h01   | AND    | Bitwise And                                         |         |

| 5'h02   | ADD    | Add two numbers                                     |         |

| 5'h03   | OR     | Bitwise Or                                          | Y       |

| 5'h04   | XOR    | Bitwise Exclusive Or                                |         |

| 5'h05   | LSR    | Logical Shift Right                                 |         |

| 5'h06   | LSL    | Logical Shift Left                                  |         |

| 5'h07   | ASR    | Arithmetic Shift Right                              |         |

| 5'h08   | MPY    | 32x32 bit multiply                                  | Y       |

| 5'h09   | LDILO  | Load Immediate Low                                  | N       |

| 5'h0a   | MPYUHI | Upper 32 of 64 bits from an unsigned 32x32 multiply |         |

| 5'h0b   | MPYSHI | Upper 32 of 64 bits from a signed 32x32 multiply    | Y       |

| 5'h0c   | BREV   | Bit Reverse                                         |         |

| 5'h0d   | POPC   | Population Count                                    |         |

| 5'h0e   | ROL    | Rotate left                                         |         |

| 5'h0f   | MOV    | Move register                                       | N       |

| 5'h10   | CMP    | Compare                                             | Y       |

| 5'h11   | TST    | Test (AND w/o setting result)                       |         |

| 5'h12   | LOD    | Load from memory                                    | N       |

| 5'h13   | STO    | Store a register into memory                        |         |

| 5'h14   | DIVU   | Divide, unsigned                                    | Y       |

| 5'h15   | DIVS   | Divide, signed                                      |         |

| 5'h16/7 | LDI    | Load 23-bit signed immediate                        | N       |

| 5'h18   | FPADD  | Floating point add                                  |         |

| 5'h19   | FPSUB  | Floating point subtract                             |         |

| 5'h1a   | FPMPY  | Floating point multiply                             | Y       |

| 5'h1b   | FPDIV  | Floating point divide                               |         |

| 5'h1c   | FPCVT  | Convert integer to floating point                   |         |

| 5'h1d   | FPINT  | Convert to integer                                  |         |

| 5'h1e   |        | Reserved for future use                             |         |

| 5'h1f   |        | Reserved for future use                             |         |

| 5'h18   |        | NOOP (A-register $=$ PC)                            |         |

| 5'h19   |        | BREAK (A-register = PC)                             | N       |

| 5'h1a   |        | LOCK (A-register = PC)                              |         |

Table 2.2: Zip CPU OpCodes

STO.Z RO, (R2)

| Code | Mneumonic | Condition                                           |  |

|------|-----------|-----------------------------------------------------|--|

| 3'h0 | None      | Always execute the instruction                      |  |

| 3'h1 | .LT       | Less than ('N' set)                                 |  |

| 3'h2 | .Z        | Only execute when 'Z' is set                        |  |

| 3'h3 | .NZ       | Only execute when 'Z' is not set                    |  |

| 3'h4 | .GT       | Greater than ('N' not set, 'Z' not set)             |  |

| 3'h5 | . GE      | Greater than or equal ('N' not set, 'Z' irrelevant) |  |

| 3'h6 | .C        | Carry set (Also known as less-than unsigned)        |  |

| 3'h7 | .V        | Overflow set                                        |  |

Table 2.3: Conditions for conditional operand execution

```

CMP 1,R0 ; Condition codes are now set based upon R0-1 CMP.Z 2,R1 ; If R0 \neq 1, conditions are unchanged. ; If R0 = 1, conditions are set based upon R1-2. ;Now do something based upon the conjunction of both conditions. ; While we use the example of a STO, it could be any instruction.

```

Table 2.4: An example of a double conditional

| Code | Mneumonic | Condition                        |

|------|-----------|----------------------------------|

| 2'h0 | None      | Always execute the instruction   |

| 2'h1 | .LT       | Less than ('N' set)              |

| 2'h2 | .Z        | Only execute when 'Z' is set     |

| 2'h3 | .NZ       | Only execute when 'Z' is not set |

Table 2.5: VLIW Conditions

| 18 | 17 16 15 14                 | 13 12 | 11 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|-----------------------------|-------|-------|---|---|---|---|---|---|---|---|---|---|

| 0  | 18-bit Signed Immediate     |       |       |   |   |   |   |   |   |   |   |   |   |

| 1  | Reg 14-bit Signed Immediate |       |       |   |   |   |   |   |   |   |   |   |   |

Table 2.6: Bit allocation for Operand B

| Original    | Modified        | Name                                          |

|-------------|-----------------|-----------------------------------------------|

| CMP Rx,Ry   | CMP 1+Rx,Ry     | Less-than or equal (signed, Z or N set)       |

| BLE label   | BLT label       |                                               |

| CMP Rx,Ry   | CMP 1+Rx,Ry     | Less-than or equal unsigned                   |

| BLEU label  | BC label        |                                               |

| CMP Rx,Ry   | CMP Ry,Rx       | Greater-than unsigned                         |

| BGTU label  | BC label        |                                               |

| CMP Rx,Ry   | CMP 1+Ry,Rx     | Greater-than equal unsigned                   |

| BGEU label  | BC label        |                                               |

| CMP A+Rx,Ry | CMP (1-A)+Ry,Rx | Greater-than equal unsigned (with offset)     |

| BGEU label  | BC label        |                                               |

| CMP A, Ry   | LDI (A-1),Rx    | Greater-than equal comparison with a constant |

| BGEU label  | CMP Ry, Rx      |                                               |

|             | BC label        |                                               |

Table 2.7: Modifying conditions

#### 2.7 Address Modes

The Zip CPU supports two addressing modes: register plus immediate, and immediate address. Addresses are therefore encoded in the same fashion as Operand B's, shown above. Practically, the VLIW instruction set only offers register addressing, necessitating a non–VLIW instruction for most memory operations.

A lot of long hard thought was put into whether to allow pre/post increment and decrement addressing modes. Finding no way to use these operators without taking two or more clocks per instruction,<sup>2</sup> these addressing modes have been removed from the realm of possibilities. This means that the Zip CPU has no native way of executing push, pop, return, or jump to subroutine operations. Each of these instructions can be emulated with a set of instructions from the existing set.

### 2.8 Modifying Conditions

A quick look at the list of conditions supported by the Zip CPU and listed in Tbl. 2.3 reveals that the Zip CPU does not have a full set of conditions. In particular, only one explicit unsigned condition is supported. Therefore, Tbl. 2.7 shows examples of how these unsupported conditions can be created simply by adjusting the compare instruction, for no extra cost in clocks. Of course, if the compare originally had an immediate within it, that immediate would need to be loaded into a register in order to do some of these compares. This case is shown as the last case above.

<sup>&</sup>lt;sup>2</sup>The two clocks figure comes from the design of the register set, allowing only one write per clock. That write is either from the memory unit or the ALU, but never both.

#### 2.9 Move Operands

The previous set of operands would be perfect and complete, save only that the CPU needs access to non–supervisory registers while in supervisory mode. Therefore, the MOV instruction is special and offers access to these registers ... when in supervisory mode. To keep the compiler simple, the extra bits are ignored in non-supervisory mode (as though they didn't exist), rather than being mapped to new instructions or additional capabilities. The bits indicating which register set each register lies within are the A-User, marked 'A' in Fig. 2.2, and B-User bits, marked as 'B'. When set to a one, these refer to a user mode register. When set to a zero, these refer to a register in the current mode, whether user or supervisor. Further, because a load immediate instruction exists, there is no move capability between an immediate and a register: all moves come from either a register or a register plus an offset.

This actually leads to a bit of a problem: since the MOV instruction encodes which register set each register is coming from or moving to, how shall a compiler or assembler know how to compile a MOV instruction without knowing the mode of the CPU at the time? For this reason, the compiler will assume all MOV registers are supervisor registers, and display them as normal. Anything with the user bit set will be treated as a user register and displayed special. Since the CPU quietly ignores the supervisor bits while in user mode, anything marked as a user register will always be specific.

#### 2.10 Multiply Operations

The ZipCPU originally only supported 16x16 multiply operations. GCC, however, wanted 32x32-bit operations and building these from 16x16-bit multiplies is painful. Therefore, the ZipCPU was modified to support 32x32-bit multiplies.

In particular, the ZipCPU supports three separate 32x32-bit multiply instructions: MPY, MPYUHI, and MPYSHI. The first of these produces the low 32-bits of a 32x32-bit multiply result. The second two produce the upper 32-bits. The first, MPYUHI, produces the upper 32-bits assuming the multiply was unsigned, whereas the second assuming it was signed. Each multiply instruction is independent of each other in execution, although the compiler may use them quite dependently.

In an effort to maintain single clock pipeline timing, all three of these multiplies have been slowed down in logic. Thus, depending upon the setting of OPT\_MULTIPLY within cpudefs.v, the multiply instructions will either 1) cause an ILLEGAL instruction error, 2) take one additional clock, or 3) take two additional clocks.

#### 2.11 Divide Unit

The Zip CPU also has a divide unit which can be built alongside the ALU. This divide unit provides the Zip CPU with another two instructions that cannot be executed in a single cycle: DIVS, or signed divide, and DIVU, the unsigned divide. These are both 32-bit divide instructions, dividing one 32-bit number by another. In this case, the Operand B field, whether it be register or register plus immediate, constitutes the denominator, whereas the numerator is given by the other register.

The Divide is also a multi-clock instruction. While the divide is running, the ALU, any memory loads, and the floating point unit (if installed) will be idle. Once the divide completes, other units may continue.

Figure 2.3: NOOP/Break/LOCK Instruction Format

Of course, divides can have errors: division by zero. In the case of division by zero, an exception will be caused that will send the CPU either from user mode to supervisor mode, or halt the CPU if it is already in supervisor mode.

#### 2.12 NOOP, BREAK, and Bus Lock Instruction

Three instructions within the opcode list in Tbl. 2.2, are somewhat special. These are the NOOP, Break, and bus LOCK instructions. These are encoded according to Fig. 2.3, and have the following meanings:

The NOOP instruction is just that: an instruction that does not perform any operation. While many other instructions, such as a move from a register to itself, could also fit these roles, only the NOOP instruction guarantees that it will not stall waiting for a register to be available. For this reason, it gets its own place in the instruction set.

The BREAK instruction is useful for creating a debug instruction that will halt the CPU without executing. If in user mode, depending upon the setting of the break enable bit, it will either switch to supervisor mode or halt the CPU-depending upon where the user wishes to do his debugging.

Finally, the LOCK instruction was added in order to provide for atomic operations. The LOCK instruction only works in pipeline mode. It works by stalling the ALU pipeline stack until all prior stages are filled, and then it guarantees that once a bus cycle is started, the wishbone CYC line will remain asserted until the LOCK is deasserted. This allows the execution of one instruction that was waiting in the load operands pipeline stage, and one instruction that was waiting in the instruction decode stage. Further, if the instruction waiting in the decode stage was a VLIW instruction, then it may be possible to execute a third instruction.

This was originally written to implement an atomic test and set instruction, such as a LOCK followed by LOD (Rx), Ry and a STO Rz, (Rx), where Rz is initially set.

Other instructions using a VLIW instruction combining a single ALU instruction with a store, such as an atomic increment, or LOCK, LOD (Rx), Ry, ADD 1, Ry, STO Ry, (Rx), should be possible as well. Many of these combinations remain to be tested.

#### 2.13 Floating Point

Although the Zip CPU does not (yet) have a floating point unit, the current instruction set offers eight opcodes for floating point operations, and treats floating point exceptions like divide by zero errors. Once this unit is built and integrated together with the rest of the CPU, the Zip CPU will support 32–bit floating point instructions natively. Any 64–bit floating point instructions will still need to be emulated in software.

Until that time, of even after if the floating point unit is not installed, floating point instructions will trigger an illegal instruction exception, which may be trapped and then implemented in software.

#### 2.14 Derived Instructions

The Zip CPU supports many other common instructions, but not all of them are single cycle instructions. The derived instruction tables, Tbls. 2.8, 2.9, 2.10 and 2.11, help to capture some of how these other instructions may be implemented on the Zip CPU. Many of these instructions will have assembly equivalents, such as the branch instructions, to facilitate working with the CPU.

#### 2.15 Interrupt Handling

The Zip CPU does not maintain any interrupt vector tables. If an interrupt takes place, the CPU simply switches to interrupt mode. The supervisor code continues in this interrupt mode from where it left off before, after executing a return to userspace RTU instruction.

At this point, the supervisor code needs to determine first whether an interrupt has occurred, and then whether it is in interrupt mode due to an exception and handle each case appropriately.

#### 2.16 Pipeline Stages

As mentioned in the introduction, and highlighted in Fig. 1.1, the Zip CPU supports a five stage pipeline.

1. **Prefetch**: Reads instruction from memory and into a cache, if so configured. This stage is actually pipelined itself, and so it will stall if the PC ever changes. Stalls are also created here if the instruction isn't in the prefetch cache.

The Zip CPU supports one of three prefetch methods, depending upon a flag set at build time within the <code>cpudefs.v</code> file. The simplest is a non–cached implementation of a prefetch. This implementation is fairly small, and ideal for users of the Zip CPU who need the extra space on the FPGA fabric. However, because this non–cached version has no cache, the maximum number of instructions per clock is limited to about one per five.

The second prefetch module is a pipelined prefetch with a cache. This module tries to keep the instruction address within a window of valid instruction addresses. While effective, it is not a traditional cache implementation. One unique feature of this cache implementation, however, is that it can be cleared in a single clock. A disappointing feature, though, was that it needs an extra internal pipeline stage to be implemented.

| Mapped             | Actual                | Notes                                                |

|--------------------|-----------------------|------------------------------------------------------|

| ABS Rx             | TST -1,Rx             | Absolute value, depends upon derived NEG.            |

|                    | NEG.LT Rx             |                                                      |

| ADD Ra,Rx          | Add Ra,Rx             | Add with carry                                       |

| ADDC Rb, Ry        | ADD.C \$1,Ry          |                                                      |

|                    | Add Rb,Ry             |                                                      |

| BRA.Cond +/-\$Addr | ADD.cond \$Addr+PC,PC | Branch or jump on condition. Works for 18-bit        |

|                    |                       | signed address offsets.                              |

| BRA.Cond +/-\$Addr | LDI \$Addr,Rx         | Branch/jump on condition. Works for 23 bit ad-       |

|                    | ADD.cond Rx,PC        | dress offsets, but costs a register and an extra     |

|                    |                       | instruction. With LDIHI and LDILO this can           |

|                    |                       | be made to work anywhere in the 32-bit address       |

|                    |                       | space, but yet cost an additional instruction still. |

| BNC PC+\$Addr      | Test \$Carry,CC       | Example of a branch on an unsupported condition,     |

|                    | ADD.Z PC+\$Addr,PC    | in this case a branch on not carry                   |

| BUSY               | ADD \$-1,PC           | Execute an infinite loop                             |

| CLRF.NZ Rx         | XOR.NZ Rx,Rx          | Clear Rx, and flags, if the Z-bit is not set         |

| CLR Rx             | LDI \$0,Rx            | Clears Rx, leaves flags untouched. This instruc-     |

|                    | , , ,                 | tion cannot be conditional.                          |

| EXCH.W Rx          | ROL \$16,Rx           | Exchanges the top and bottom 16'bit words of Rx      |

| HALT               | Or \$SLEEP,CC         | This only works when issued in inter-                |

|                    | - ,                   | rupt/supervisor mode. In user mode this is           |

|                    |                       | simply a wait until interrupt instruction.           |

| INT                | LDI \$0,CC            | This is also known as a trap instruction             |

| IRET               | OR \$GIE,CC           | Also known as an RTU instruction (Return to          |

|                    | ,,                    | Userspace)                                           |

| JMP R6+\$Offset    | MOV \$Offset(R6),PC   |                                                      |

| LJMP \$Addr        | LOD (PC),PC           | Although this only works for an unconditional        |

| • • •              | Address               | jump, and it only works in a Von Neumann archi-      |

|                    |                       | tecture, this instruction combination makes for a    |

|                    |                       | nice combination that can be adjusted by a linker    |

|                    |                       | at a later time.                                     |

| JSR PC+\$Offset    | MOV \$1+PC,RO         | This is similar to the jump and link instructions    |

| 1 10 4011200       | ADD \$Offset,PC       | from other architectures, save only that it requires |

|                    |                       | a specific link instruction, also known as the MOV   |

|                    |                       | instruction on the left.                             |

|                    |                       | mon action on the left.                              |

Table 2.8: Derived Instructions

| Mapped          | Actual                 | Notes                                                      |

|-----------------|------------------------|------------------------------------------------------------|

| LDI.1 \$val,Rx  | LDIHI                  | Sadly, there's not enough instruction space to             |

|                 | (val>>16)&0x0ffff,     | load a complete immediate value into any regis-            |

|                 | Rx                     | ter. Therefore, fully loading any register takes           |

|                 | LDILO (\$val&0x0ffff), | Rxtwo cycles. The LDIHI (load immediate high) and          |

|                 |                        | LDILO (load immediate low) instructions have               |

|                 |                        | been created to facilitate this.                           |

|                 |                        | This is also the appropriate means for setting a           |

|                 |                        | register value to an arbitrary 32-bit value in a           |

|                 |                        | post–assembly link operation.                              |

| LOD.b \$addr,Rx | LDI \$addr,Ra          | This CPU is designed for 32'bit word length in-            |

|                 | LDI \$addr,Rb          | structions. Byte addressing is not supported by            |

|                 | LSR \$2,Ra             | the CPU or the bus, so it therefore takes more             |

|                 | AND \$3,Rb             | work to do.                                                |

|                 | LOD (Ra),Rx            | Note also that in this example, \$Addr is a byte-          |

|                 | LSL \$3,Rb             | wise address, where all other addresses in this doc-       |

|                 | SUB \$32,Rb            | ument are 32-bit wordlength addresses. For this            |

|                 | ROL Rb, Rx             | reason, we needed to drop the bottom two bits.             |

|                 | AND \$Offh,Rx          | This also limits the address space of character ac-        |

|                 |                        | cesses using this method from 16 MB down to                |

| LSL \$1,Rx      | LSL \$1,Ry             | 4MB. Logical shift left with carry. Note that the instruc- |

| LSLC \$1,Ry     | LSL \$1,Rx             | tion order is now backwards, to keep the condi-            |

| LDLO #1, hy     | OR.C \$1,Ry            | tions valid. That is, LSL sets the carry flag, so if       |

|                 | οιν. ο ψ1,ινη          | we did this the other way with Rx before Ry, then          |

|                 |                        | the condition flag wouldn't have been right for an         |

|                 |                        | OR correction at the end.                                  |

| LSR \$1,Rx      | CLR Rz                 | Logical shift right with carry                             |

| LSRC \$1,Ry     | LSR \$1,Ry             |                                                            |

|                 | LDIHI.C \$8000h,Rz     |                                                            |

|                 | LSR \$1,Rx             |                                                            |

|                 | OR Rz,Rx               |                                                            |

| NEG Rx          | XOR \$-1,Rx            |                                                            |

|                 | ADD \$1,Rx             |                                                            |

| NEG.C Rx        | MOV.C \$-1+Rx,Rx       |                                                            |

| MUUD            | XOR.C \$-1,Rx<br>NOOP  | While there are many operations that do nothing,           |

| NOOP            | NOOF                   | such as MOV Rx,Rx, or OR \$0,Rx, these opera-              |

|                 |                        | tions have consequences in that they might stall           |

|                 |                        | the bus if Rx isn't ready yet. For this reason, we         |

|                 |                        | have a dedicated NOOP instruction.                         |

| NOT Rx          | XOR \$-1,Rx            |                                                            |

| POP Rx          | LOD \$(SP),Rx          |                                                            |

|                 | ADD \$1,SP             |                                                            |

Table 2.9: Derived Instructions, continued

| PUSH Rx          | SUB \$1,SP<br>STO Rx,\$(SP)                                                                                                           | Note that for pipelined operation, it helps to coalesce all the SUB's into one command, and place the STO's right after each other. Further, to avoid a pipeline stall, the immediate value for the store must be zero.                                                                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PUSH Rx-Ry       | SUB $n,SP$<br>STO Rx, $S(SP)$<br>STO Ry, $(n-1)(SP)$                                                                                  | Multiple pushes at once only need the single subtract from the stack pointer. This derived instruction is analogous to a similar one on the Motoroloa 68k architecture, although the Zip Assembler does not support this instruction (yet). This instruction also supports pipelined memory access.                                                                      |

| RESET            | STO<br>\$1,\$watchdog(R12)<br>NOOP<br>NOOP                                                                                            | This depends upon the peripheral base address being preloaded into R12.  Another opportunity might be to jump to the reset address from within supervisor mode.                                                                                                                                                                                                          |

| RET              | MOV RO,PC                                                                                                                             | This depends upon the form of the JSR given on<br>the previous page that stores the return address<br>into R0.                                                                                                                                                                                                                                                           |

| STEP Rr,Rt       | LSR \$1,Rr<br>XOR.C Rt,Rr                                                                                                             | Step a Galois implementation of a Linear Feedback<br>Shift Register, Rr, using taps Rt                                                                                                                                                                                                                                                                                   |

| SEX.b Rx         | LSL 24,Rx<br>ASR 24,Rx                                                                                                                | Signed extend a byte into a full word.                                                                                                                                                                                                                                                                                                                                   |

| SEX.h Rx         | LSL 16,Rx<br>ASR 16,Rx                                                                                                                | Sign extend a half word into a full word.                                                                                                                                                                                                                                                                                                                                |

| STO.b Rx, \$addr | LDI \$addr,Ra LDI \$addr,Rb LSR \$2,Ra AND \$3,Rb SUB \$32,Rb LOD (Ra),Ry AND \$0ffh,Rx AND ~\$0ffh,Ry ROL Rb,Rx OR Rx,Ry STO Ry,(Ra) | This CPU and it's bus are <i>not</i> optimized for byte-wise operations.  Note that in this example, \$addr is a byte-wise address, whereas in all of our other examples it is a 32-bit word address. This also limits the address space of character accesses from 16 MB down to 4MB.F Further, this instruction implies a byte ordering, such as big or little endian. |

| SWAP Rx,Ry       | XOR Ry,Rx<br>XOR Rx,Ry<br>XOR Ry,Rx                                                                                                   | While no extra registers are needed, this example does take 3-clocks.                                                                                                                                                                                                                                                                                                    |

Table 2.10: Derived Instructions, continued

| TRAP #X       | LDI \$x,RO<br>AND ~\$GIE,CC                    | This works because whenever a user lowers the \$GIE flag, it sets a TRAP bit within the CC register. Therefore, upon entering the supervisor state, the CPU only need check this bit to know that it got there via a TRAP. The trap could be made conditional by making the LDI and the AND conditional. In that case, the assembler would quietly turn the LDI instruction into an LDILO and LDIHI pair, but the effect would be the same. |

|---------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TS Rx,Ry,(Rz) | LDI 1,Rx<br>LOCK<br>LOD (Rz),Ry<br>STO Rx,(Rz) | A test and set instruction. The LOCK instruction insures that the next two instructions lock the bus between the instructions, so no one else can use it. Thus guarantees that the operation is atomic.                                                                                                                                                                                                                                     |

| TST Rx        | TST \$-1,Rx                                    | Set the condition codes based upon Rx. Could also do a CMP \$0,Rx, ADD \$0,Rx, SUB \$0,Rx, etc, AND \$-1,Rx, etc. The TST and CMP approaches won't stall future pipeline stages looking for the value of Rx. (Future versions of the assembler may shorten this to a TST Rx instruction.)                                                                                                                                                   |

| WAIT          | Or \$GIE   \$SLEEP,CC                          | Wait until the next interrupt, then jump to supervisor/interrupt mode.                                                                                                                                                                                                                                                                                                                                                                      |

Table 2.11: Derived Instructions, continued

The third prefetch and cache module implements a more traditional cache. While the resulting code tends to be twice as fast as the pipelined cache architecture, this implementation uses a large amount of distributed FPGA RAM to be successful. This then inflates the Zip CPU's FPGA usage statistics.

- 2. **Decode**: Decodes an instruction into OpCode, register(s) to read, and immediate offset. This stage also determines whether the flags will be set or whether the result will be written back.

- 3. **Read Operands**: Read registers and apply any immediate values to them. There is no means of detecting or flagging arithmetic overflow or carry when adding the immediate to the operand. This stage will stall if any source operand is pending.

- 4. Split into one of four tracks: An **ALU** track which will accomplish a simple instruction, the **MemOps** stage which handles LOD (load) and STO (store) instructions, the **divide** unit, and the **floating point** unit.

- Loads will stall instructions in the decode stage until the entire pipeline until complete, lest a register be read in the read operands stage only to be updated unseen by the Load.

- Condition codes are available upon completion of the ALU, divide, or FPU stage.

- Issuing a non–pipelined memory instruction to the memory unit while the memory unit is busy will stall the entire pipeline.

- 5. Write-Back: Conditionally write back the result to the register set, applying the condition. This routine is quad-entrant: either the ALU, the memory, the divide, or the FPU may write back a register. The only design rule is that no more than a single register may be written back in any given clock.