NoC based MPSoC

Project maintainers

Details

Created: Jan 13, 2014

Updated: Jan 24, 2022

SVN Updated: Nov 9, 2023

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 3 reported / 2 solved

Other project properties

Language:Verilog

Development status:Mature

Additional info:FPGA proven

WishBone compliant: Yes

WishBone version: n/a

License: LGPL

ProNoC

NOTE:

The zip file downloaded from direct link in Latest Version menue is not the most updated version. Make sure you have downloaded the latest version of the ProNoC software via the SVN or git using the following command:

svn co https://opencores.org/ocsvn/an-fpga-implementation-of-low-latency-noc-based-mpsoc/an-fpga-implementation-of-low-latency-noc-based-mpsoc/trunk/ ProNoC/Or using git

git clone https://github.com/amonemi/ProNoC.gitProject Summary

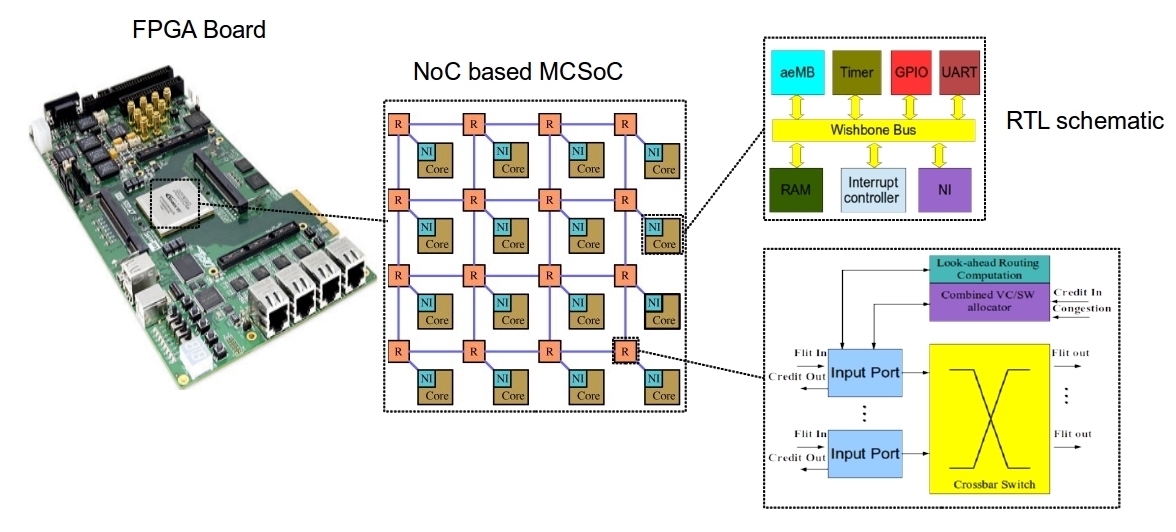

Prototype-network-on-chip (ProNoC) is an EDA tool that facilitates prototyping of custom heterogeneous NoC-based many-core-SoC (MCSoC). ProNoC is enhanced using a parameterizable virtual channel based low-latency NoC that is optimized for FPGA implementation. Moreover, ProNoC can also be used as a custom Wishbone bus based SoC generator (SoC without NoC) using available Intellectual Properties (IPs) in ProNoC library. The ProNoC IP library can be easily extended to support more IPs.

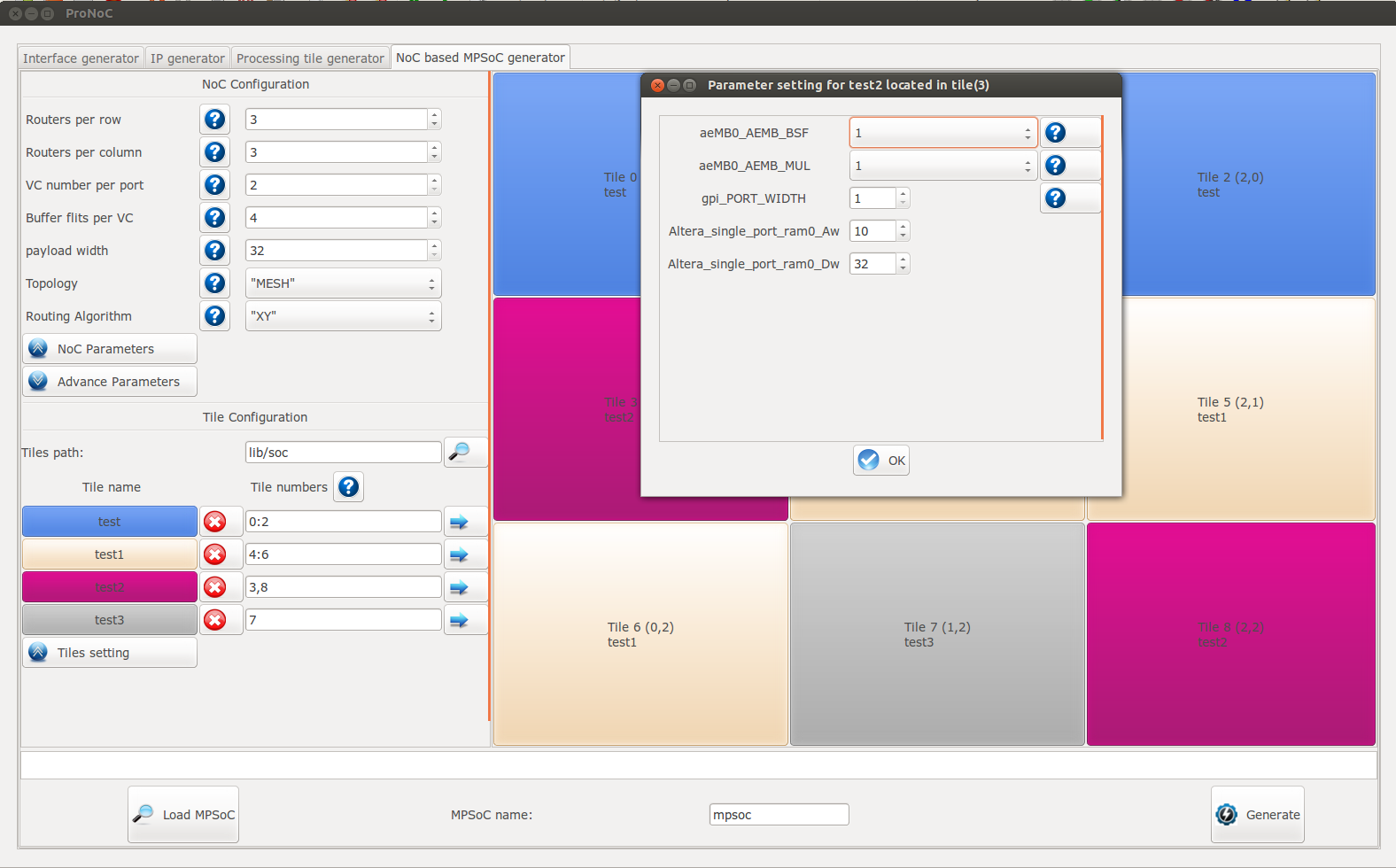

ProNoC GUI MCSoC Generator

Writing the whole RTL code of a complex heterogeneous MCSoC manually can be time-consuming and error-prone due to the huge number of possible configurations as well as high similarity among sub-components code portions. In order to facilitate the design of such complex systems, ProNoC, an open-source EDA tool that generates the complete heterogeneous customized NoC-based MCSoC RTL code is developed. The design effort increases when developing a heterogeneous MCSoC as each processing tile must be designed separately. To ease and speed up the development of such platform, a graphical user interface (GUI) is developed to generate a custom NoC-based MCSoC. The ProNoC GUI is written with Perl programming language and GTK2 library. ProNoC consists of four main windows corresponding to each layer in MCSoC design as follow.

- Interface Generator: The components interconnection is facilitated by defining the interface. Interface is the combination of several ports that provide specific functionality.

- IP Generator: The IP generator facilitates the process of making a library for each IP. An IP can either be a processor or a peripheral device such as memory, timer, bus or an interrupt controller. The IP generator reads the Verilog file containing the top-level module of the IP and user can define the number of interfaces and map them to the IP ports.

- Processing Tile Generator: The processing tile (PT) generator contains the list of all IPs that can be connected to each other using available defined interfaces. This integration tool provides some facilities such as automatic generation of interconnect logic and automatic Wishbone address setting. It also provides graphical interface for setting different IP parameters.

- NoC-based MCSoC Generator: The MCSoC generator facilitates the generation of a heterogeneous NoC-based MCSoC by providing GUI interface for setting the NoC’s and PTs’ parameters. It checks all processing tiles which have been previously generated using the PT generator and lists all the tiles containing the NI to connect to the NoC

NoC Specification

ProNoC presents an FPGA-optimized NoC-based MCSoC with ASIC-based NoC functionalities. The NoC specifications are as follow:

- Wormhole packet switching flow-control: Wormhole allows storing of different flits of the same packet in several routers along the path and requires low buffer.

- Virtual Channel(VC): ProNoC supports parameterizable number of VCs. All VCs that are located in the same input port of the router share one BRAM memory.

- Combined VC/switch allocator: combined allocator allows simultaneous allocation of VC and switch stages in the same clock cycle to reduce the router latency and cost.

- Non-atomic or atomic VC reallocation: In atomic VC reallocation, a free VC can be reallocated only when it is empty. whereas in non-atomic VC reallocation a non-empty VC can be reallocated once it receives the tail flit.

- NoC topology: Currently ProNoC supports foloowing topologies: Mesh, Torus, Ring, Line,Fattree,BinTree,Star and user defined custom topologies

- Different routing algorithm: ProNoC supports deterministic (DoR), partial adaptive (turn models and odd-even) and fully adaptive routing.

- Router pipeline stages: ProNoC NoC router has two pipeline stages. In the first stage three processes of look-ahead route computation, VC allocation and SW allocation are done in parallel. The second stage is switch traversal. ProNoC can also be configured with a static strength allocator (SSA), which allows packets traversing to the same direction pass NoC router withing 1-clk latency. Moreover, enabling SMART features allows a flit going in the same direction bypasses several routers in a single cycle.

- Hard-built QoS: provide Equality-of-Service (EoS) or Differential-Service (DS) as subsets of QoS for injected packets based on initial wait.

ProNoC NoC Simulator

The ProNoC NoC is developed in RTL using SystemVerilog HDL and it can be simulated using Verilator simulator. The ProNoC simulator provides the graphical user interface (GUI) for simulating different NoC configuration under different type traffic patterns:

- Synthetic

- Task-based

- Trace-based

How to Cite

If you found ProNoC useful please cite some of the following references in your publications:

- Alireza Monemi, et al. "PIugSMART: a pluggable open-source module to implement multihop bypass in networks-on-chip." Proceedings of the 15th IEEE/ACM International Symposium on Networks-on-Chip. 2021.

- A Monemi, F Khunjush, M Palesi, H Sarbazi-Azad, "An Enhanced Dynamic Weighted Incremental Technique for QoS Support in NoC" ACM Transactions on Parallel Computing (TOPC), pagesp 1–31,2020

- Alireza Monemi, Jia Wei Tang, Maurizio Palesi, Muhammad N. Marsono, "ProNoC: A low latency network-on-chip based many-core system-on-chip prototyping platform", Microprocessors and Microsystems, Volume 54, October 2017, Pages 60-74.

- Alireza Monemi, Chia Yee Ooi, Maurizio Palesi, and Muhammad Nadzir Marsono. "Low latency network-on-chip router using static straight allocator". In Proceedings of 3rd International Conference on Information Technology, Computer and Electrical Engineering, ICITACEE’16. IEEE, 2016.

- Alireza Monemi, Chia Yee Ooi, Muhammad Nadzir Marsono, and Maurizio Palesi. "Improved flow control for minimal fully adaptive routing in 2D mesh NoC". In Proceedings of the 9th International Workshop on Network on Chip Architectures, NoCArc’16, pages 9–14. ACM, 2016.

- Alireza Monemi, Chia Yee Ooi, and Muhammad Nadzir Marsono. "Low latency network-__on-chip router microarchitecture using request masking technique". International Journal of Reconfigurable Computing, 2015:2, 2015.

Additional Documentation

For more information and tutorials, please check following directories:

- "trunk/doc"

Bug reporting

For any bug or feedback reporting please contact me via alirezamonemi@opencores.org