Lightweight 8080 compatible core

Synthesizable Demos

A few synthesizable demos have been included with the project so it can be evaluated conveniently on a standard development board. All demos target terasIC's DE-1 development board but should be easy to port to other development boards and other FPGA brands -- the RTL is fairly portable.

The following are the demos available in VHDL language. As soon as possible this list will be updated to include the Verilog demos, or the demos adapted to use the Verilog core.

8080EXER Demo

8080EXER is an instruction exerciser that runs all the 8080 opcodes with a large number of parameter combinations. The program computes a CRC value for the CPU state after testing each block of CPU opcodes. That CRC value is then compared against the CRC value produced by an original, silicon i8080.If the CRC values match, it can safely be assumed that the core and the original 8080 behavior is identical.

The program was taken from this web. There you will find a more detailed explaination.

I have made the following modifications to the original CP/M version of 8080EXEC:

- Added code that emulates a few CP/M BDOS functions needed to output text.

- Adapted the code to work on the C2SB demo board within the l80soc module.

- Added the original Intel CRC values for comparison.

- Halted the program after the tests are done instead of returning to the (inexistent) CCP.

The source code is in a format compatible to CP/M M80 assembler and incompatible to TASM, AS80 and all other Windows and Linux 8080-compatible assemblers that I know about. Therefore it can only be compiled from within CP/M.

You can use SIMH for that. I will not include instructions but you can find plenty in SIMH web site.

File 'MAC.SUB', included with the project, is a CP/M 'batch' file that you can use to assemble the source with:

DO MAC 8080EXER

I hope this saves you the trouble to find and read M80 documentation...

At any rate, i have included the compiled HEX file so all you have to do is run the build.bat script. Or just use the pre-built obj_code_pkg.vhdl included.

Synthesis instructions:

Assuming you are using Quartus-2 and targetting a Terasic DE-1 dev board (for which the demo is tailored), you need to follow these steps:- Create a new project for the DE-1 board, (device EP2C20F484C7, etc.).

- Add the following vhdl files to the project:

- /vhdl/light8080.vhdl

- /vhdl/demos/c2sb/c2sb_soc.vhdl

- /vhdl/soc/*.vhdl

- Select file c2sb_soc.vhdl as 'top' entity.

- Configure dual-purpose pin nCEO as regular i/o (Device settings->Device and pin options->Dual-purpose pins).

- Import pin location constraints from file /vhdl/demos/c2sb/c2sb_pins.csv.

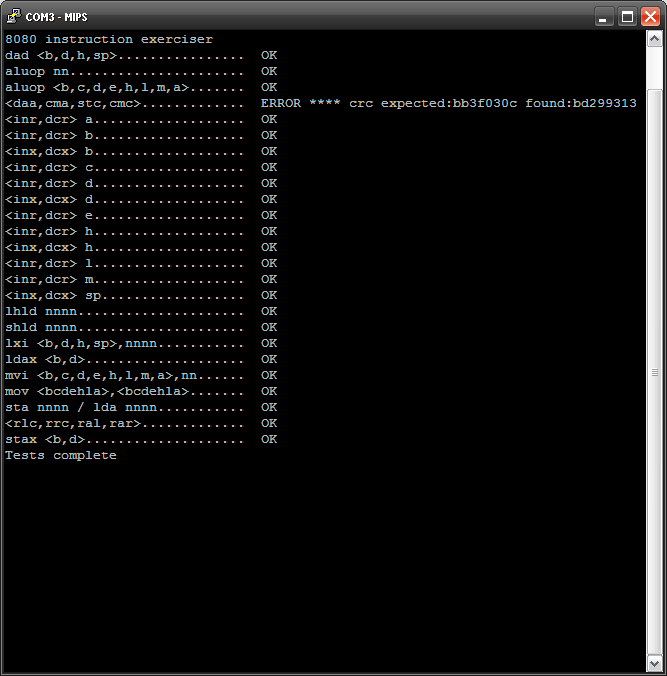

Here's what the execution of the program looks like:

The tests take about 11 minutes to complete on a 50MHz core.

As you can see, all instructions appear to be identical to the original Intel silicon, except for the DAA group.

The exerciser does not give you any hint about what's failing or what instruction is at fault; yet, the strongest suspect is DAA.

DAA is perhaps the darkest corner of the 8080; the documentation leaves so much unspecified that apparently even the NEC people that second-sourced the 8080 back in the day had trouble replicating its behavior.

Anyway, I think I will be able to build on the work done by some emulator developers and eventually DAA will be made 100 % compatible too.

A note on the execution speed

Running the tests on a DE-1 at 50MHz takes about 11 minutes. According to the 8080exer site, the tests take about 200 minutes on a 2MHz i8080. So, if the exerciser code could be taken as a representative benchmark, the light8080 core is about 37% slower than the original i8080 cycle for cycle -- because the instructions take more cycles in the core than in the original.

That is, a 50MHz light8080 runs as as fast as a 36 MHz i8080 at least for this code.

Altair 4K Basic Demo

Altair Basic is an early implementation of Basic (1975) for the 8080-based Altair computer. I have included in the project a demo running the unmodified binaries on the light8080 core. See instructions and status log below.Assuming you are using Quartus-2 and targetting a Terasic DE-1 dev board (for which the demo is tailored), you need to follow these steps:

- Create a new project for the DE-1 board, (device EP2C20F484C7, etc.).

- Add all the vhdl files in /vhdl/demos/4kbasic, plus the main cpu file light8080.vhdl, to your project.

- Select file c2sb_4kbasic_cpu.vhdl as 'top' entity.

- Configure dual-purpose pin nCEO as regular i/o (Device settings->Device and pin options->Dual-purpose pins)

- Import the pin location constraints from file /vhdl/demos/4kbasic/c2sb_4kbasic.csv

- Ready to go. Synthesize and program. It is advisable to have a terminal connected before loading the FPGA (19200/8/N/1).

Make sure you're using the last revision; some earlier revisions had a bug in the csv pin constraints file that misplaced the clock input.

Note that resetting the CPU does not reload the program (the program is stored in an initialized 4K RAM which is all the CPU can see). Once the program has started, the only way to cleanly restart it is reprogramming the FPGA. This is why the terminal should be connected before programming.

I admit this is a nasty hack but it saves me the need to build a bootloader. For this quick-and-dirty demo this limitation is acceptable.

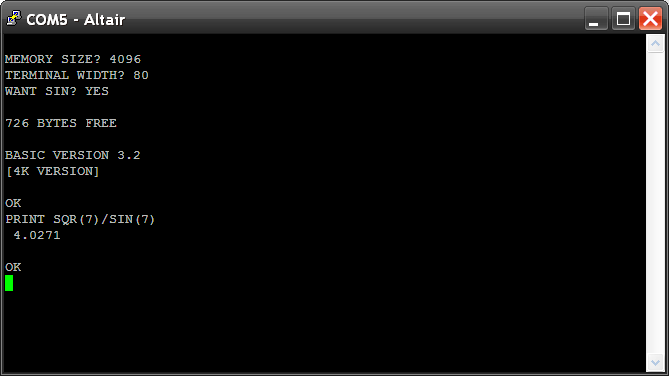

Right after startup the program will ask you a few configuration questions. See the picture below for a sample session. Remember the 4K Basic only uses caps letters and is a bit unforgiving by today's standards.

Here's a snapshot of a sample session on my terminal emulator (putty):

The fact that the floating point routines do work makes me think that the core works as an original 8080 and few bugs remain, if any. While not very useful in practice, the 4K Basic demo is a good confidence builder.

Here's a link to the Altair Basic manual.

This demo uses the bare CPU core, not the SoC, and the object code is hardcoded in an VHDL entity with no easy means to change for some other application's code. for these and other reasons, this is not a good starting point for a real application nor a good evaluation tool -- it's only good to show theat the core behaves like a real 8080 using original, vintage code.

'Hello World' Demo

The project includes a minimalistic 'Hello World' demo that is meant to be used to build a real application from, or at least as an usage example for the core and the SoC.The demo assembler source is in directory /sw/demos/hello (relative the the project root directory). This directory includes a DOS BATCH file which builds the program using TASM assembler (not included with this project but freely available), and then creates a VHDL entity holding the project object code as an VHDL constant.

The demo is meant to be run on a DE-1 board, for which a pre-built entity has been included in directory /sw/demos/c2sb. The project must synthesize all the VHDL files within that directory, plus the vhdl file generated by the build script in the source directory.

This demo showcases the use of the SoC, including a small UART and interrupt controller, nothing else.

© copyright 1999-2018 OpenCores.org, equivalent to Oliscience, all rights reserved. OpenCores®, registered trademark.