opb_usblite

Project maintainers

Details

Created: Jun 2, 2010

Updated: Jun 8, 2010

SVN Updated: Jun 9, 2010

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:VHDL

Development status:Alpha

Additional info:FPGA proven

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

opb_usblite - opb_uartlite replacement for Xilinx Microblaze processor written in VHDL and Verilog. The opb_usblite is compatible with the USB CDC profile and works with microsoft usbser virtual comport driver (VCD).

Implementation

The opb_usblite connects directly to the OPB bus. For users that are using the processor local bus (PLB) it is possible to add a PLB2OPB bridge. See the reference design for the Spartan 3E starter board.

There are a few generics to configure the behavior of the core.

C_SYSRST : std_logic := '1'; -- enable external reset

C_PHYMODE : std_logic := '1'; -- phy mode

C_VENDORID : std_logic_vector(15 downto 0) := X"1234"; -- VID

C_PRODUCTID : std_logic_vector(15 downto 0) := X"5678"; -- PID

C_VERSIONBCD : std_logic_vector(15 downto 0) := X"0200"; -- device version

C_SELFPOWERED : boolean := false; -- self or bus powered

C_RXBUFSIZE_BITS: integer range 7 to 12 := 10; -- size of rx buf (2^10 = 1024 bytes)

C_TXBUFSIZE_BITS: integer range 7 to 12 := 10 -- size of tx buf (2^10 = 1024 bytes)

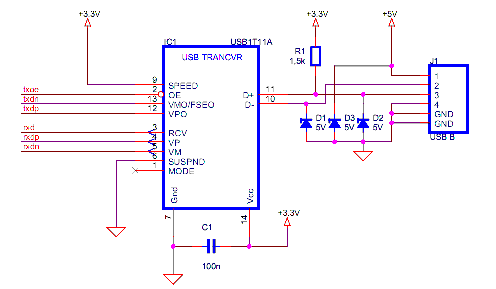

There are six I/O signals for connecting the core to an usb transceiver, e.g USB1T11A from Fairchild Semiconductor.

A schematic drawing in pdf format can be found here.

txdp : out std_logic; -- connect to VPO

txdn : out std_logic; -- connect to VMO/FSEO

txoe : out std_logic; -- connect to OE

rxd : in std_logic; -- connect to RCV

rxdp : in std_logic; -- connect to VP

rxdn : in std_logic -- connect to VM

The core consumes around 527 slices in a Spartan 3s500. In addition it also needs a 48MHz clock, easily generated by a DCM or clock generator core. It does not need to be synchronized with the processor clock. All signals crossing the clock domains are handled in the opb_usblite core. An example of a clock generator is found in the reference design.

Device utilization summary:

---------------------------

Selected Device : 3s500efg320-4

Number of Slices: 527 out of 4656 11%

Number of Slice Flip Flops: 396 out of 9312 4%

Number of 4 input LUTs: 962 out of 9312 10%

Number used as logic: 961

Number used as Shift registers: 1

Number of IOs: 118

Number of bonded IOBs: 0 out of 232 0%

Number of BRAMs: 3 out of 20 15%

Software/Drivers

There is a basic driver for microblaze designs included in the project. It is compatible with the drivers supplied for opb_uartlite in most aspects. In software settings in EDK just select opb_usblite as stdio. Although microsoft windows

is shipped with drivers for usb cdc devices it is necessary to supply an inf file with usb VID and PID information. Just point to the project supplied .inf file when the pnp manager is asking for a driver. Note that the usual bit rate, handshake etc. settings are not used and have no affect to the communication with the target.

ADDRESS MAP =========== RX FIFO base + $0 TX FIFO base + $4 CONTROL REG base + $8 STATUS REG base + $C CONTROL REG =========== -- Write Only -- bit 0 Reset_TX_FIFO -- not used -- bit 1 Reset_RX_FIFO -- not used -- bit 2 Dont'Care -- bit 3 Dont'Care -- bit 4 enable_rxinterrupts -- bit 5 Dont'Care -- bit 6 enable_txinterrupts -- bit 7 tx_enable -- not used STATUS REG ========== -- Read Only -- bit 0 rx_Data_Present -- bit 1 rx_Buffer_Full -- bit 2 tx_Buffer_Empty -- bit 3 tx_Buffer_Full -- bit 4 interrupt flag -- bit 5 not used always '0' -- bit 6 online flag -- bit 7 suspend flag

Misc

opb_usblite is using components by Rudolf Usselmann see

http://www.opencores.org/cores/usb_phy/

and Joris van Rantwijk see http://www.xs4all.nl/~rjoris/fpga/usb.html

MAKE SURE TO READ THEIR LICENSE TERMS BEFORE USING THIS IP-CORE