TCP/IP socket

Project maintainers

Details

Name: tcp_socket

Created: Nov 24, 2013

Updated: Jul 4, 2018

SVN Updated: Dec 23, 2013

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 2 reported / 0 solved

Created: Nov 24, 2013

Updated: Jul 4, 2018

SVN Updated: Dec 23, 2013

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 2 reported / 0 solved

Star18you like it: star it!

Other project properties

Category:Communication controller

Language:Verilog

Development status:Alpha

Additional info:Design done, FPGA proven

WishBone compliant: No

WishBone version: n/a

License: Others

Language:Verilog

Development status:Alpha

Additional info:Design done, FPGA proven

WishBone compliant: No

WishBone version: n/a

License: Others

Description

TCP Socket

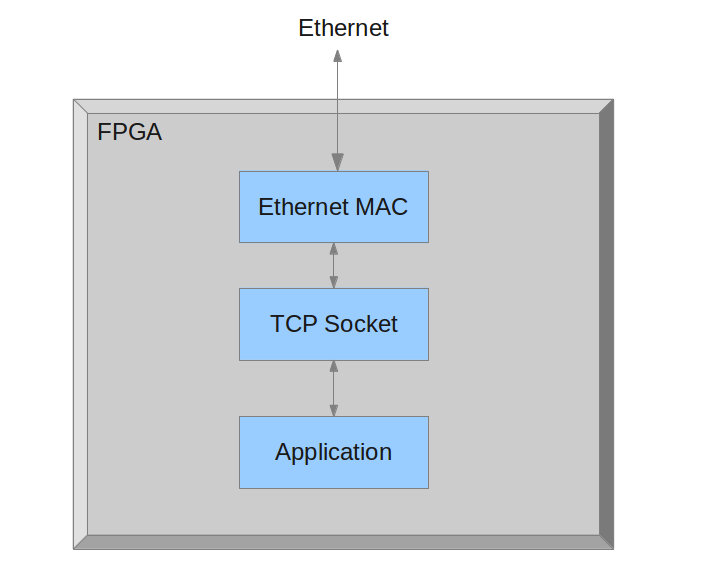

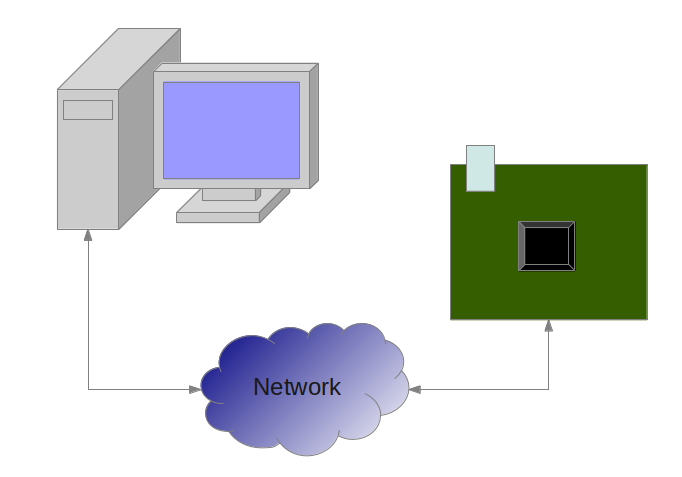

TCP Socket is a TCP/IP stack implementation. The core acts as a server, allowing a remote client to establish a bidirectional TCP socket connection directly to logic within your FPGA.

Features

- Easily add network connectivity to your FPGA

- No need for a soft CPU

- Small footprint (less than 800 LUTs in Spartan 6)

- Free Open Source Solution (MIT license)

- Connect to your FPGA with a web browser or telnet client

Implementation

TCP Socket is implemented in C, and is compiled into synthesisable Verilog using the Chips development environment (included). A precompiled Verilog module precompiled/server.v is also provided to get you up and running. For more details check out TCPIP.pdf.

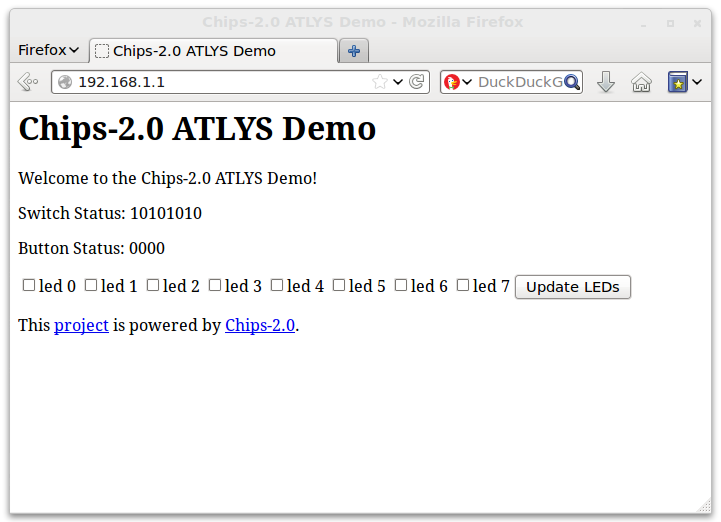

Demo

A simple web-app demo for the Digilent Atlys Spartan 6 development card is provided. This includes everything you need to get up and running, including the Ethernet MAC. If you want to give it a try, why not use the precompiled .bit file. For more details check out README.pdf.

© copyright 1999-2018 OpenCores.org, equivalent to Oliscience, all rights reserved. OpenCores®, registered trademark.