UART To SPI

Project maintainers

Details

Name: uart2spi

Created: Jan 15, 2013

Updated: Mar 2, 2018

SVN Updated: Dec 22, 2016

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 1 reported / 0 solved

Created: Jan 15, 2013

Updated: Mar 2, 2018

SVN Updated: Dec 22, 2016

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 1 reported / 0 solved

Star8you like it: star it!

Other project properties

Category:Communication controller

Language:Verilog

Development status:Mature

Additional info:

WishBone compliant: No

WishBone version: n/a

License: LGPL

Language:Verilog

Development status:Mature

Additional info:

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

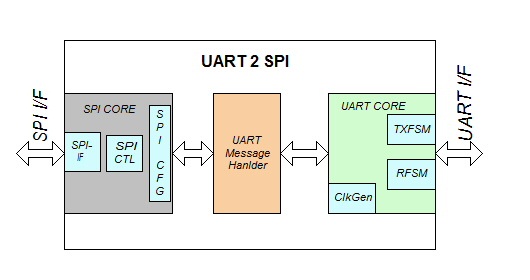

The UART to SPI IP Core include a simple command parser that can be used to access an internal bus of SPI via a UART interface. This IP can be used understand the SPI transaction protocol. The internal bus is designed with address bus of 16 bits and data bus of 8 bits. The core implements a very basic UART transmit & receive blocks which share a common baud rate generator and a command parser. The parser supports text mode of command parsing. Text mode commands are designed to be used with hyper terminal software and enable easy access to the internal bus.

Block Diagram

© copyright 1999-2018 OpenCores.org, equivalent to Oliscience, all rights reserved. OpenCores®, registered trademark.