Viterbi Decoder (AXI4-Stream compliant)

Viterbi Decoder (AXI4-Stream compliant)

Project maintainers

Details

Name: viterbi_decoder_axi4s

Created: Jan 16, 2012

Updated: Apr 16, 2015

SVN Updated: Feb 17, 2014

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 8 reported / 7 solved

Created: Jan 16, 2012

Updated: Apr 16, 2015

SVN Updated: Feb 17, 2014

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 8 reported / 7 solved

Star10you like it: star it!

Other project properties

Category:ECC core

Language:VHDL

Development status:Stable

Additional info:Design done, FPGA proven

WishBone compliant: No

WishBone version: n/a

License: GPL

Language:VHDL

Development status:Stable

Additional info:Design done, FPGA proven

WishBone compliant: No

WishBone version: n/a

License: GPL

Description

A fully configurable VHDL Viterbi decoder compliant with the AXI4-Stream interface. Most standards using convolutional codes like Wifi or GSM are easy to implement by configuring some generic parameters. The decoder supports a high throughput even on low-cost devices. See the User Guide for more information about the core.

Features

- Design-time configuration of encoder polynomials (different number of states and different code rates).

- Support for recursive and non-recursive convolutional codes.

- Windowing technique for reduced latency and memory requirements (with acquisition).

- Design-time configuration of quantization, maximum window size, RAM usage (distributed RAM vs. Block RAM).

- Run-time configuration of block length.

- Run-time configuration of window length and acquisition length.

- Block-to-block on-the-fly configuration.

- Comprehensive documentation available.

Benefits

- Configurable for most standards that apply convolutional codes (GSM, UMTS, CDMA, CDMA2000, WiMAX, WiFi, DAB, ...).

- Pipelined design for high payload throughputs (about 1 bit per clock cycle).

- AXI4-Stream interface for simple integration.

- Up to 250 MHz on Xilinx Virtex-6 FPGA (Speedgrade 1).

- Commercial support and licenses available.

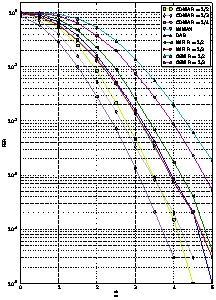

Communications Performance

Comparison for Viterbi communications performance in various standards.

Frame length is set to 400, while the LLR input bit length is 4 and no windowing is used.

Contact author

Creonic GmbH - Germany

Site: www.creonic.com

Tel: +49 631 3435988-0

© copyright 1999-2018 OpenCores.org, equivalent to Oliscience, all rights reserved. OpenCores®, registered trademark.