| 1 |

72 |

zero_gravi |

[](https://github.com/stnolting/neorv32)

|

| 2 |

2 |

zero_gravi |

|

| 3 |

37 |

zero_gravi |

# The NEORV32 RISC-V Processor

|

| 4 |

|

|

|

| 5 |

59 |

zero_gravi |

[](https://github.com/stnolting/neorv32/releases/tag/nightly)

|

| 6 |

60 |

zero_gravi |

[](https://stnolting.github.io/neorv32)

|

| 7 |

|

|

[](https://github.com/stnolting/neorv32/releases/tag/nightly)

|

| 8 |

|

|

[](https://stnolting.github.io/neorv32/ug)

|

| 9 |

59 |

zero_gravi |

[](https://stnolting.github.io/neorv32/sw/files.html)

|

| 10 |

67 |

zero_gravi |

[](https://gitter.im/neorv32/community?utm_source=badge&utm_medium=badge&utm_campaign=pr-badge&utm_content=badge)

|

| 11 |

2 |

zero_gravi |

|

| 12 |

64 |

zero_gravi |

1. [Overview](#1-Overview)

|

| 13 |

69 |

zero_gravi |

* [Key Features](#Project-Key-Features)

|

| 14 |

|

|

* [Status](#status)

|

| 15 |

64 |

zero_gravi |

2. [Processor/SoC Features](#2-NEORV32-Processor-Features)

|

| 16 |

69 |

zero_gravi |

* [FPGA Implementation Results](#FPGA-Implementation-Results---Processor)

|

| 17 |

64 |

zero_gravi |

3. [CPU Features](#3-NEORV32-CPU-Features)

|

| 18 |

69 |

zero_gravi |

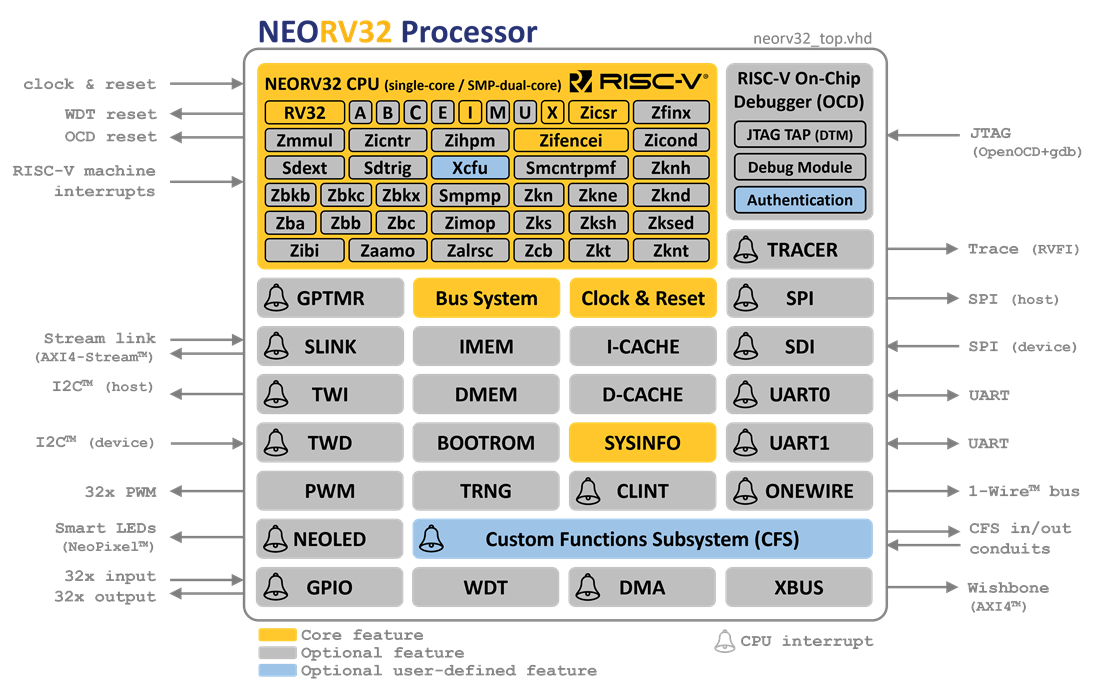

* [Available ISA Extensions](#Available-ISA-Extensions)

|

| 19 |

|

|

* [FPGA Implementation Results](#FPGA-Implementation-Results---CPU)

|

| 20 |

|

|

* [Performance](#Performance)

|

| 21 |

64 |

zero_gravi |

4. [Software Framework & Tooling](#4-Software-Framework-and-Tooling)

|

| 22 |

|

|

5. [**Getting Started**](#5-Getting-Started) :rocket:

|

| 23 |

2 |

zero_gravi |

|

| 24 |

|

|

|

| 25 |

60 |

zero_gravi |

|

| 26 |

64 |

zero_gravi |

## 1. Overview

|

| 27 |

2 |

zero_gravi |

|

| 28 |

72 |

zero_gravi |

|

| 29 |

54 |

zero_gravi |

|

| 30 |

71 |

zero_gravi |

The NEORV32 Processor is a **customizable microcontroller-like system on chip (SoC)** that is based on the

|

| 31 |

|

|

[RISC-V](https://riscv.org/) NEORV32 CPU.

|

| 32 |

59 |

zero_gravi |

The project is intended as auxiliary processor in larger SoC designs or as *ready-to-go* stand-alone

|

| 33 |

69 |

zero_gravi |

custom microcontroller that even fits into a Lattice iCE40 UltraPlus 5k low-power FPGA running at 24 MHz.

|

| 34 |

2 |

zero_gravi |

|

| 35 |

66 |

zero_gravi |

Special focus is paid on **execution safety** to provide defined and predictable behavior at any time.

|

| 36 |

|

|

Therefore, the CPU ensures that all memory access are acknowledged and no invalid/malformed instructions

|

| 37 |

69 |

zero_gravi |

are executed. Whenever an unexpected situation occurs the application code is informed via precise and resumable hardware exceptions.

|

| 38 |

66 |

zero_gravi |

|

| 39 |

70 |

zero_gravi |

:interrobang: Want to know more? Check out the [project's rationale](https://stnolting.github.io/neorv32/#_rationale).

|

| 40 |

61 |

zero_gravi |

|

| 41 |

72 |

zero_gravi |

:books: For detailed information take a look at the [NEORV32 online documentation](https://stnolting.github.io/neorv32/).

|

| 42 |

|

|

The latest _pdf_ versions can be found [here](https://github.com/stnolting/neorv32/releases/tag/nightly).

|

| 43 |

45 |

zero_gravi |

|

| 44 |

72 |

zero_gravi |

:label: The project's change log is available in [`CHANGELOG.md`](https://github.com/stnolting/neorv32/blob/main/CHANGELOG.md).

|

| 45 |

69 |

zero_gravi |

To see the changes between _official releases_ visit the project's [release page](https://github.com/stnolting/neorv32/releases).

|

| 46 |

11 |

zero_gravi |

|

| 47 |

71 |

zero_gravi |

:package: [**Exemplary setups**](https://github.com/stnolting/neorv32-setups) targeting

|

| 48 |

69 |

zero_gravi |

various FPGA boards and toolchains to get you started.

|

| 49 |

56 |

zero_gravi |

|

| 50 |

69 |

zero_gravi |

:kite: Supported by upstream [Zephyr OS](https://docs.zephyrproject.org/latest/boards/riscv/neorv32/doc/index.html) and FreeRTOS.

|

| 51 |

65 |

zero_gravi |

|

| 52 |

59 |

zero_gravi |

:bulb: Feel free to open a [new issue](https://github.com/stnolting/neorv32/issues) or start a

|

| 53 |

62 |

zero_gravi |

[new discussion](https://github.com/stnolting/neorv32/discussions) if you have questions, comments, ideas or if something is

|

| 54 |

67 |

zero_gravi |

not working as expected. Or have a chat on our [gitter channel](https://gitter.im/neorv32/community).

|

| 55 |

72 |

zero_gravi |

See how to [contribute](https://github.com/stnolting/neorv32/blob/main/CONTRIBUTING.md).

|

| 56 |

47 |

zero_gravi |

|

| 57 |

68 |

zero_gravi |

:rocket: Check out the [quick links below](#5-Getting-Started) or directly jump to the

|

| 58 |

60 |

zero_gravi |

[*User Guide*](https://stnolting.github.io/neorv32/ug/) to get started

|

| 59 |

59 |

zero_gravi |

setting up your NEORV32 setup!

|

| 60 |

51 |

zero_gravi |

|

| 61 |

2 |

zero_gravi |

|

| 62 |

59 |

zero_gravi |

### Project Key Features

|

| 63 |

15 |

zero_gravi |

|

| 64 |

70 |

zero_gravi |

- [x] all-in-one package: **CPU** plus **SoC** plus **Software Framework & Tooling**

|

| 65 |

64 |

zero_gravi |

- [x] completely described in behavioral, platform-independent VHDL - no primitives, macros, etc.

|

| 66 |

69 |

zero_gravi |

- [x] be as small as possible while being as RISC-V-compliant as possible

|

| 67 |

70 |

zero_gravi |

- [x] from zero to `printf("hello world!");` - completely open source and documented

|

| 68 |

64 |

zero_gravi |

- [x] easy to use even for FPGA/RISC-V starters – intended to work *out of the box*

|

| 69 |

22 |

zero_gravi |

|

| 70 |

69 |

zero_gravi |

|

| 71 |

|

|

### Status

|

| 72 |

|

|

|

| 73 |

|

|

[](https://github.com/stnolting/neorv32/releases)

|

| 74 |

|

|

[](https://stnolting.github.io/neorv32)

|

| 75 |

71 |

zero_gravi |

\

|

| 76 |

72 |

zero_gravi |

[](https://github.com/stnolting/neorv32/actions?query=workflow%3ADocumentation)

|

| 77 |

|

|

[](https://github.com/stnolting/neorv32/actions?query=workflow%3Ariscv-arch-test)

|

| 78 |

|

|

[](https://github.com/stnolting/neorv32/actions?query=workflow%3AProcessor)

|

| 79 |

69 |

zero_gravi |

|

| 80 |

59 |

zero_gravi |

[[back to top](#The-NEORV32-RISC-V-Processor)]

|

| 81 |

2 |

zero_gravi |

|

| 82 |

|

|

|

| 83 |

64 |

zero_gravi |

## 2. NEORV32 Processor Features

|

| 84 |

3 |

zero_gravi |

|

| 85 |

70 |

zero_gravi |

The NEORV32 Processor provides a full-featured microcontroller-like SoC build around the NEORV32 CPU. It is highly configurable

|

| 86 |

|

|

via generics to allow a flexible customization according to your needs. Note that all modules listed below are _optional_.

|

| 87 |

2 |

zero_gravi |

|

| 88 |

60 |

zero_gravi |

**Memory**

|

| 89 |

2 |

zero_gravi |

|

| 90 |

60 |

zero_gravi |

* processor-internal data and instruction memories ([DMEM](https://stnolting.github.io/neorv32/#_data_memory_dmem) /

|

| 91 |

|

|

[IMEM](https://stnolting.github.io/neorv32/#_instruction_memory_imem)) &

|

| 92 |

|

|

cache ([iCACHE](https://stnolting.github.io/neorv32/#_processor_internal_instruction_cache_icache))

|

| 93 |

70 |

zero_gravi |

* pre-installed bootloader ([BOOTLDROM](https://stnolting.github.io/neorv32/#_bootloader_rom_bootrom)) with serial user interface

|

| 94 |

68 |

zero_gravi |

* allows booting application code via UART or from external SPI flash

|

| 95 |

11 |

zero_gravi |

|

| 96 |

60 |

zero_gravi |

**Timers**

|

| 97 |

11 |

zero_gravi |

|

| 98 |

67 |

zero_gravi |

* machine system timer, 64-bit ([MTIME](https://stnolting.github.io/neorv32/#_machine_system_timer_mtime)), RISC-V spec. compatible

|

| 99 |

|

|

* general purpose 32-bit timer ([GPTMR](https://stnolting.github.io/neorv32/#_general_purpose_timer_gptmr))

|

| 100 |

60 |

zero_gravi |

* watchdog timer ([WDT](https://stnolting.github.io/neorv32/#_watchdog_timer_wdt))

|

| 101 |

11 |

zero_gravi |

|

| 102 |

69 |

zero_gravi |

**Input/Output**

|

| 103 |

56 |

zero_gravi |

|

| 104 |

60 |

zero_gravi |

* standard serial interfaces

|

| 105 |

|

|

([UART](https://stnolting.github.io/neorv32/#_primary_universal_asynchronous_receiver_and_transmitter_uart0),

|

| 106 |

|

|

[SPI](https://stnolting.github.io/neorv32/#_serial_peripheral_interface_controller_spi),

|

| 107 |

70 |

zero_gravi |

[TWI](https://stnolting.github.io/neorv32/#_two_wire_serial_interface_controller_twi))

|

| 108 |

60 |

zero_gravi |

* general purpose [GPIO](https://stnolting.github.io/neorv32/#_general_purpose_input_and_output_port_gpio) and

|

| 109 |

|

|

[PWM](https://stnolting.github.io/neorv32/#_pulse_width_modulation_controller_pwm)

|

| 110 |

70 |

zero_gravi |

* smart LED interface ([NEOLED](https://stnolting.github.io/neorv32/#_smart_led_interface_neoled)) to directly control NeoPixel(TM) LEDs

|

| 111 |

2 |

zero_gravi |

|

| 112 |

69 |

zero_gravi |

**SoC Connectivity**

|

| 113 |

47 |

zero_gravi |

|

| 114 |

59 |

zero_gravi |

* 32-bit external bus interface, Wishbone b4 compatible

|

| 115 |

|

|

([WISHBONE](https://stnolting.github.io/neorv32/#_processor_external_memory_interface_wishbone_axi4_lite))

|

| 116 |

72 |

zero_gravi |

* [wrapper](https://github.com/stnolting/neorv32/blob/main/rtl/system_integration/neorv32_SystemTop_axi4lite.vhd) for AXI4-Lite host interface

|

| 117 |

|

|

* [wrapper](https://github.com/stnolting/neorv32/blob/main/rtl/system_integration/neorv32_SystemTop_AvalonMM.vhd) for Avalon-MM host interface

|

| 118 |

64 |

zero_gravi |

* 32-bit stream link interface with up to 8 independent RX and TX links

|

| 119 |

61 |

zero_gravi |

([SLINK](https://stnolting.github.io/neorv32/#_stream_link_interface_slink))

|

| 120 |

|

|

* AXI4-Stream compatible

|

| 121 |

|

|

* external interrupt controller with up to 32 channels

|

| 122 |

|

|

([XIRQ](https://stnolting.github.io/neorv32/#_external_interrupt_controller_xirq))

|

| 123 |

60 |

zero_gravi |

|

| 124 |

|

|

**Advanced**

|

| 125 |

|

|

|

| 126 |

72 |

zero_gravi |

* on-chip debugger ([OCD](https://stnolting.github.io/neorv32/#_on_chip_debugger_ocd)) accessible via JTAG interface - compliant to

|

| 127 |

|

|

the "Minimal RISC-V Debug Specification Version 0.13.2" and compatible with **OpenOCD** + **gdb** and **Segger Embedded Studio**;

|

| 128 |

|

|

includes RISC-V _hardware trigger module_

|

| 129 |

60 |

zero_gravi |

* _true random_ number generator ([TRNG](https://stnolting.github.io/neorv32/#_true_random_number_generator_trng))

|

| 130 |

70 |

zero_gravi |

* execute in place module ([XIP](https://stnolting.github.io/neorv32/#_execute_in_place_module_xip)) to directly execute code from SPI flash

|

| 131 |

|

|

* custom functions subsystem ([CFS](https://stnolting.github.io/neorv32/#_custom_functions_subsystem_cfs))

|

| 132 |

72 |

zero_gravi |

for tightly-coupled custom accelerators and interfaces

|

| 133 |

|

|

* custom functions unit ([CFU](https://stnolting.github.io/neorv32/#_custom_functions_unit_cfu)) for up to 1024

|

| 134 |

|

|

_custom RISC-V instructions_

|

| 135 |

47 |

zero_gravi |

|

| 136 |

56 |

zero_gravi |

[[back to top](#The-NEORV32-RISC-V-Processor)]

|

| 137 |

47 |

zero_gravi |

|

| 138 |

56 |

zero_gravi |

|

| 139 |

60 |

zero_gravi |

### FPGA Implementation Results - Processor

|

| 140 |

47 |

zero_gravi |

|

| 141 |

68 |

zero_gravi |

The hardware resources used by a specific processor setup is defined by the implemented CPU extensions,

|

| 142 |

|

|

the configuration of the peripheral modules and some "glue logic".

|

| 143 |

|

|

Section [_FPGA Implementation Results - Processor Modules_](https://stnolting.github.io/neorv32/#_processor_modules)

|

| 144 |

64 |

zero_gravi |

of the online datasheet shows the resource utilization of each optional processor module to allow an

|

| 145 |

62 |

zero_gravi |

estimation of the actual setup's hardware requirements.

|

| 146 |

2 |

zero_gravi |

|

| 147 |

71 |

zero_gravi |

:bulb: The [`neorv32-setups`](https://github.com/stnolting/neorv32-setups) repository provides exemplary FPGA

|

| 148 |

72 |

zero_gravi |

setups targeting various FPGA boards and toolchains. The latest bitstreams and utilization reports for those setups

|

| 149 |

|

|

can be found in the assets of the [Implementation Workflow](https://github.com/stnolting/neorv32-setups/actions/workflows/Implementation.yml).

|

| 150 |

56 |

zero_gravi |

|

| 151 |

|

|

[[back to top](#The-NEORV32-RISC-V-Processor)]

|

| 152 |

47 |

zero_gravi |

|

| 153 |

56 |

zero_gravi |

|

| 154 |

47 |

zero_gravi |

|

| 155 |

64 |

zero_gravi |

## 3. NEORV32 CPU Features

|

| 156 |

47 |

zero_gravi |

|

| 157 |

70 |

zero_gravi |

The NEORV32 CPU implements the RISC-V 32-bit `rv32i` ISA with optional extensions (see below). It is compatible to subsets of the

|

| 158 |

72 |

zero_gravi |

*Unprivileged ISA Specification* [(Version 2.2)](https://github.com/stnolting/neorv32/blob/main/docs/references/riscv-spec.pdf)

|

| 159 |

|

|

and the *Privileged Architecture Specification* [(Version 1.12-draft)](https://github.com/stnolting/neorv32/blob/main/docs/references/riscv-privileged.pdf).

|

| 160 |

70 |

zero_gravi |

Compatibility is checked by passing the [official RISC-V architecture tests](https://github.com/riscv/riscv-arch-test).

|

| 161 |

56 |

zero_gravi |

|

| 162 |

66 |

zero_gravi |

The core is a little-endian Von-Neumann machine implemented as multi-cycle architecture.

|

| 163 |

72 |

zero_gravi |

However, the CPU's_front end (instruction fetch) and back end (instruction execution) can work independently to increase performance.

|

| 164 |

|

|

Currently, two privilege levels "machine-mode" and optional "user-mode" are supported. The CPU implements all three standard RISC-V machine

|

| 165 |

|

|

interrupts (MTI, MEI, MSI) plus 16 _fast interrupt requests_ as custom extensions.

|

| 166 |

61 |

zero_gravi |

It also supports **all** standard RISC-V exceptions (instruction/load/store misaligned address & bus access fault, illegal

|

| 167 |

66 |

zero_gravi |

instruction, breakpoint, environment calls).

|

| 168 |

23 |

zero_gravi |

|

| 169 |

68 |

zero_gravi |

:books: In-depth detailed information regarding the CPU can be found in the

|

| 170 |

|

|

[_Data Sheet: NEORV32 Central Processing Unit_](https://stnolting.github.io/neorv32/#_neorv32_central_processing_unit_cpu).

|

| 171 |

2 |

zero_gravi |

|

| 172 |

68 |

zero_gravi |

|

| 173 |

60 |

zero_gravi |

### Available ISA Extensions

|

| 174 |

2 |

zero_gravi |

|

| 175 |

60 |

zero_gravi |

Currently, the following _optional_ RISC-V-compatible ISA extensions are implemented (linked to the according

|

| 176 |

71 |

zero_gravi |

documentation section).

|

| 177 |

2 |

zero_gravi |

|

| 178 |

60 |

zero_gravi |

**RV32

|

| 179 |

|

|

[[`I`](https://stnolting.github.io/neorv32/#_i_base_integer_isa)/

|

| 180 |

|

|

[`E`](https://stnolting.github.io/neorv32/#_e_embedded_cpu)]

|

| 181 |

|

|

[[`A`](https://stnolting.github.io/neorv32/#_a_atomic_memory_access)]

|

| 182 |

66 |

zero_gravi |

[[`B`](https://stnolting.github.io/neorv32/#_b_bit_manipulation_operations)]

|

| 183 |

60 |

zero_gravi |

[[`C`](https://stnolting.github.io/neorv32/#_c_compressed_instructions)]

|

| 184 |

|

|

[[`M`](https://stnolting.github.io/neorv32/#_m_integer_multiplication_and_division)]

|

| 185 |

|

|

[[`U`](https://stnolting.github.io/neorv32/#_u_less_privileged_user_mode)]

|

| 186 |

|

|

[[`X`](https://stnolting.github.io/neorv32/#_x_neorv32_specific_custom_extensions)]

|

| 187 |

|

|

[[`Zfinx`](https://stnolting.github.io/neorv32/#_zfinx_single_precision_floating_point_operations)]

|

| 188 |

|

|

[[`Zicsr`](https://stnolting.github.io/neorv32/#_zicsr_control_and_status_register_access_privileged_architecture)]

|

| 189 |

66 |

zero_gravi |

[[`Zicntr`](https://stnolting.github.io/neorv32/#_zicntr_cpu_base_counters)]

|

| 190 |

|

|

[[`Zihpm`](https://stnolting.github.io/neorv32/#_zihpm_hardware_performance_monitors)]

|

| 191 |

60 |

zero_gravi |

[[`Zifencei`](https://stnolting.github.io/neorv32/#_zifencei_instruction_stream_synchronization)]

|

| 192 |

61 |

zero_gravi |

[[`Zmmul`](https://stnolting.github.io/neorv32/#_zmmul_integer_multiplication)]

|

| 193 |

72 |

zero_gravi |

[[`Zxcfu`](https://stnolting.github.io/neorv32/#_zxcfu_custom_instructions_extension_cfu)]

|

| 194 |

60 |

zero_gravi |

[[`PMP`](https://stnolting.github.io/neorv32/#_pmp_physical_memory_protection)]

|

| 195 |

63 |

zero_gravi |

[[`DEBUG`](https://stnolting.github.io/neorv32/#_cpu_debug_mode)]**

|

| 196 |

60 |

zero_gravi |

|

| 197 |

71 |

zero_gravi |

:warning: The `B`, `Zfinx` and `Zmmul` RISC-V are frozen and officially ratified but there is no

|

| 198 |

|

|

upstream gcc support yet. To circumvent this, the NEORV32 software framework provides _intrinsic libraries_ for the

|

| 199 |

|

|

`B` and `Zfinx` extensions.

|

| 200 |

60 |

zero_gravi |

|

| 201 |

56 |

zero_gravi |

[[back to top](#The-NEORV32-RISC-V-Processor)]

|

| 202 |

39 |

zero_gravi |

|

| 203 |

56 |

zero_gravi |

|

| 204 |

60 |

zero_gravi |

### FPGA Implementation Results - CPU

|

| 205 |

23 |

zero_gravi |

|

| 206 |

62 |

zero_gravi |

Implementation results for _exemplary_ CPU configuration generated for an **Intel Cyclone IV EP4CE22F17C6N FPGA**

|

| 207 |

69 |

zero_gravi |

using **Intel Quartus Prime Lite 20.1** ("balanced implementation, Slow 1200mV 0C Model").

|

| 208 |

2 |

zero_gravi |

|

| 209 |

72 |

zero_gravi |

| CPU Configuration (version [1.5.7.10](https://github.com/stnolting/neorv32/blob/main/CHANGELOG.md)) | LEs | FFs | Memory bits | DSPs | f_max |

|

| 210 |

69 |

zero_gravi |

|:------------------------|:----:|:----:|:----:|:-:|:-------:|

|

| 211 |

|

|

| `rv32i` | 806 | 359 | 1024 | 0 | 125 MHz |

|

| 212 |

|

|

| `rv32i_Zicsr_Zicntr` | 1729 | 813 | 1024 | 0 | 124 MHz |

|

| 213 |

|

|

| `rv32imac_Zicsr_Zicntr` | 2511 | 1074 | 1024 | 0 | 124 MHz |

|

| 214 |

2 |

zero_gravi |

|

| 215 |

71 |

zero_gravi |

:bulb: An incremental list of CPU extension's hardware utilization can found in the

|

| 216 |

68 |

zero_gravi |

[_Data Sheet: FPGA Implementation Results - CPU_](https://stnolting.github.io/neorv32/#_cpu).

|

| 217 |

62 |

zero_gravi |

|

| 218 |

56 |

zero_gravi |

[[back to top](#The-NEORV32-RISC-V-Processor)]

|

| 219 |

22 |

zero_gravi |

|

| 220 |

|

|

|

| 221 |

60 |

zero_gravi |

### Performance

|

| 222 |

56 |

zero_gravi |

|

| 223 |

69 |

zero_gravi |

The NEORV32 CPU is based on a two-stages pipeline architecture (fetch and execute).

|

| 224 |

61 |

zero_gravi |

The average CPI (cycles per instruction) depends on the instruction mix of a specific applications and also on the

|

| 225 |

|

|

available CPU extensions.

|

| 226 |

2 |

zero_gravi |

|

| 227 |

71 |

zero_gravi |

The following table shows the performance results (scores and average CPI) for exemplary CPU configurations executing

|

| 228 |

72 |

zero_gravi |

2000 iterations of the [CoreMark](https://github.com/stnolting/neorv32/blob/main/sw/example/coremark) CPU benchmark

|

| 229 |

|

|

(using plain GCC10 rv32i built-in libraries only!).

|

| 230 |

2 |

zero_gravi |

|

| 231 |

72 |

zero_gravi |

| CPU Configuration (version [1.5.7.10](https://github.com/stnolting/neorv32/blob/main/CHANGELOG.md)) | CoreMark Score | CoreMarks/MHz | Average CPI |

|

| 232 |

69 |

zero_gravi |

|:------------------------------------------------|:-----:|:----------:|:--------:|

|

| 233 |

|

|

| _small_ (`rv32i_Zicsr`) | 33.89 | **0.3389** | **4.04** |

|

| 234 |

|

|

| _medium_ (`rv32imc_Zicsr`) | 62.50 | **0.6250** | **5.34** |

|

| 235 |

|

|

| _performance_ (`rv32imc_Zicsr` + perf. options) | 95.23 | **0.9523** | **3.54** |

|

| 236 |

42 |

zero_gravi |

|

| 237 |

71 |

zero_gravi |

:bulb: More information regarding the CPU performance can be found in the

|

| 238 |

68 |

zero_gravi |

[_Data Sheet: CPU Performance_](https://stnolting.github.io/neorv32/#_cpu_performance).

|

| 239 |

2 |

zero_gravi |

|

| 240 |

56 |

zero_gravi |

[[back to top](#The-NEORV32-RISC-V-Processor)]

|

| 241 |

34 |

zero_gravi |

|

| 242 |

56 |

zero_gravi |

|

| 243 |

2 |

zero_gravi |

|

| 244 |

64 |

zero_gravi |

## 4. Software Framework and Tooling

|

| 245 |

60 |

zero_gravi |

|

| 246 |

72 |

zero_gravi |

* [core libraries](https://github.com/stnolting/neorv32/tree/main/sw/lib) for high-level usage of the provided functions and peripherals

|

| 247 |

60 |

zero_gravi |

* application compilation based on GNU makefiles

|

| 248 |

|

|

* gcc-based toolchain ([pre-compiled toolchains available](https://github.com/stnolting/riscv-gcc-prebuilt))

|

| 249 |

72 |

zero_gravi |

* [SVD file](https://github.com/stnolting/neorv32/tree/main/sw/svd) for advanced debugging and IDE integration

|

| 250 |

60 |

zero_gravi |

* bootloader with UART interface console

|

| 251 |

|

|

* runtime environment for handling traps

|

| 252 |

72 |

zero_gravi |

* several [example programs](https://github.com/stnolting/neorv32/tree/main/sw/example) to get started including CoreMark, FreeRTOS and Conway's Game of Life

|

| 253 |

69 |

zero_gravi |

* doxygen-based documentation, available on [GitHub pages](https://stnolting.github.io/neorv32/sw/files.html)

|

| 254 |

71 |

zero_gravi |

* supports implementation using open source tooling ([GHDL](https://github.com/ghdl/ghdl), Yosys, nextpnr, ...) - both, software and hardware can be

|

| 255 |

60 |

zero_gravi |

developed and debugged with open source tooling

|

| 256 |

69 |

zero_gravi |

* [continuous integration](https://github.com/stnolting/neorv32/actions) is available for:

|

| 257 |

60 |

zero_gravi |

* allowing users to see the expected execution/output of the tools

|

| 258 |

|

|

* ensuring specification compliance

|

| 259 |

|

|

* catching regressions

|

| 260 |

|

|

* providing ready-to-use and up-to-date bitstreams and documentation

|

| 261 |

|

|

|

| 262 |

69 |

zero_gravi |

:books: Want to know more? Check out [_Data Sheet: Software Framework_](https://stnolting.github.io/neorv32/#_software_framework).

|

| 263 |

|

|

|

| 264 |

60 |

zero_gravi |

[[back to top](#The-NEORV32-RISC-V-Processor)]

|

| 265 |

|

|

|

| 266 |

|

|

|

| 267 |

|

|

|

| 268 |

64 |

zero_gravi |

## 5. Getting Started

|

| 269 |

2 |

zero_gravi |

|

| 270 |

60 |

zero_gravi |

This overview provides some *quick links* to the most important sections of the

|

| 271 |

61 |

zero_gravi |

[online Data Sheet](https://stnolting.github.io/neorv32) and the

|

| 272 |

60 |

zero_gravi |

[online User Guide](https://stnolting.github.io/neorv32/ug).

|

| 273 |

2 |

zero_gravi |

|

| 274 |

59 |

zero_gravi |

### :electric_plug: Hardware Overview

|

| 275 |

2 |

zero_gravi |

|

| 276 |

72 |

zero_gravi |

* [Rationale](https://stnolting.github.io/neorv32/#_rationale) - NEORV32: why? how come? what for?

|

| 277 |

61 |

zero_gravi |

|

| 278 |

59 |

zero_gravi |

* [NEORV32 Processor](https://stnolting.github.io/neorv32/#_neorv32_processor_soc) - the SoC

|

| 279 |

|

|

* [Top Entity - Signals](https://stnolting.github.io/neorv32/#_processor_top_entity_signals) - how to connect to the processor

|

| 280 |

|

|

* [Top Entity - Generics](https://stnolting.github.io/neorv32/#_processor_top_entity_generics) - configuration options

|

| 281 |

61 |

zero_gravi |

* [Address Space](https://stnolting.github.io/neorv32/#_address_space) - memory layout and boot configuration

|

| 282 |

69 |

zero_gravi |

* [SoC Modules](https://stnolting.github.io/neorv32/#_processor_internal_modules) - available peripheral modules and memories

|

| 283 |

61 |

zero_gravi |

* [On-Chip Debugger](https://stnolting.github.io/neorv32/#_on_chip_debugger_ocd) - online & in-system debugging of the processor via JTAG

|

| 284 |

2 |

zero_gravi |

|

| 285 |

63 |

zero_gravi |

* [NEORV32 CPU](https://stnolting.github.io/neorv32/#_neorv32_central_processing_unit_cpu) - the CPU

|

| 286 |

59 |

zero_gravi |

* [RISC-V compatibility](https://stnolting.github.io/neorv32/#_risc_v_compatibility) - what is compatible to the specs. and what is not

|

| 287 |

66 |

zero_gravi |

* [Full Virtualization](https://stnolting.github.io/neorv32/#_full_virtualization) - hardware execution safety

|

| 288 |

59 |

zero_gravi |

* [ISA and Extensions](https://stnolting.github.io/neorv32/#_instruction_sets_and_extensions) - available RISC-V ISA extensions

|

| 289 |

|

|

* [CSRs](https://stnolting.github.io/neorv32/#_control_and_status_registers_csrs) - control and status registers

|

| 290 |

|

|

* [Traps](https://stnolting.github.io/neorv32/#_traps_exceptions_and_interrupts) - interrupts and exceptions

|

| 291 |

34 |

zero_gravi |

|

| 292 |

59 |

zero_gravi |

### :floppy_disk: Software Overview

|

| 293 |

12 |

zero_gravi |

|

| 294 |

72 |

zero_gravi |

* [Example Programs](https://github.com/stnolting/neorv32/tree/main/sw/example) - test program execution on your setup

|

| 295 |

59 |

zero_gravi |

* [Core Libraries](https://stnolting.github.io/neorv32/#_core_libraries) - high-level functions for accessing the processor's peripherals

|

| 296 |

72 |

zero_gravi |

* [Software Framework Documentation](https://stnolting.github.io/neorv32/sw/files.html) - _doxygen_-based documentation

|

| 297 |

59 |

zero_gravi |

* [Application Makefiles](https://stnolting.github.io/neorv32/#_application_makefile) - turning your application into an executable

|

| 298 |

|

|

* [Bootloader](https://stnolting.github.io/neorv32/#_bootloader) - the build-in NEORV32 bootloader

|

| 299 |

22 |

zero_gravi |

|

| 300 |

68 |

zero_gravi |

### :rocket: User Guide

|

| 301 |

31 |

zero_gravi |

|

| 302 |

69 |

zero_gravi |

* [Toolchain Setup](https://stnolting.github.io/neorv32/ug/#_software_toolchain_setup) - install and setup RISC-V gcc

|

| 303 |

60 |

zero_gravi |

* [General Hardware Setup](https://stnolting.github.io/neorv32/ug/#_general_hardware_setup) - setup a new NEORV32 EDA project

|

| 304 |

|

|

* [General Software Setup](https://stnolting.github.io/neorv32/ug/#_general_software_framework_setup) - configure the software framework

|

| 305 |

72 |

zero_gravi |

* [Application Compilation](https://stnolting.github.io/neorv32/ug/#_application_program_compilation) - compile an application using "make"

|

| 306 |

60 |

zero_gravi |

* [Upload via Bootloader](https://stnolting.github.io/neorv32/ug/#_uploading_and_starting_of_a_binary_executable_image_via_uart) - upload and execute executables

|

| 307 |

63 |

zero_gravi |

* [Application-Specific Processor Configuration](https://stnolting.github.io/neorv32/ug/#_application_specific_processor_configuration) - tailor the processor to your needs

|

| 308 |

64 |

zero_gravi |

* [Adding Custom Hardware Modules](https://stnolting.github.io/neorv32/ug/#_adding_custom_hardware_modules) - add _your_ custom hardware

|

| 309 |

60 |

zero_gravi |

* [Debugging via the On-Chip Debugger](https://stnolting.github.io/neorv32/ug/#_debugging_using_the_on_chip_debugger) - step through code *online* and *in-system*

|

| 310 |

63 |

zero_gravi |

* [Simulation](https://stnolting.github.io/neorv32/ug/#_simulating_the_processor) - simulate the whole SoC

|

| 311 |

|

|

* [Hello World!](https://stnolting.github.io/neorv32/ug/index.html#_hello_world) - run a quick _"hello world"_ simulation

|

| 312 |

56 |

zero_gravi |

|

| 313 |

60 |

zero_gravi |

### :copyright: Legal

|

| 314 |

|

|

|

| 315 |

72 |

zero_gravi |

[](https://github.com/stnolting/neorv32/blob/main/LICENSE)

|

| 316 |

69 |

zero_gravi |

[](https://doi.org/10.5281/zenodo.5018888)

|

| 317 |

60 |

zero_gravi |

|

| 318 |

69 |

zero_gravi |

* [Overview](https://stnolting.github.io/neorv32/#_legal) - license, disclaimer, limitation of liability for external links, proprietary notice, ...

|

| 319 |

|

|

* [Citing](https://stnolting.github.io/neorv32/#_citing) - citing information

|

| 320 |

72 |

zero_gravi |

* [Impressum](https://github.com/stnolting/neorv32/blob/main/docs/impressum.md) - imprint

|

| 321 |

69 |

zero_gravi |

|

| 322 |

70 |

zero_gravi |

This is an open-source project that is free of charge. Use this project in any way you like

|

| 323 |

72 |

zero_gravi |

(as long as it complies to the permissive [license](https://github.com/stnolting/neorv32/blob/main/LICENSE)).

|

| 324 |

70 |

zero_gravi |

Please quote it appropriately. :+1:

|

| 325 |

|

|

|

| 326 |

56 |

zero_gravi |

[[back to top](#The-NEORV32-RISC-V-Processor)]

|

| 327 |

36 |

zero_gravi |

|

| 328 |

56 |

zero_gravi |

|

| 329 |

71 |

zero_gravi |

---------------------------------------

|

| 330 |

22 |

zero_gravi |

|

| 331 |

69 |

zero_gravi |

**A big shout-out goes to the community and all the [contributors](https://github.com/stnolting/neorv32/graphs/contributors), who helped improving this project! :heart:**

|